Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                              |

|----------------------------|-----------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                                  |

| Speed                      | 180MHz                                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SAI, SDIO, SPI, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                   |

| Number of I/O              | 161                                                                                                 |

| Program Memory Size        | 2MB (2M x 8)                                                                                        |

| Program Memory Type        | FLASH                                                                                               |

| EEPROM Size                | -                                                                                                   |

| RAM Size                   | 384K x 8                                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                         |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                               |

| Oscillator Type            | Internal                                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                   |

| Mounting Type              | Surface Mount                                                                                       |

| Package / Case             | 216-TFBGA                                                                                           |

| Supplier Device Package    | 216-TFBGA (13x13)                                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f469nih6tr                             |

|                            |                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.1 Compatibility throughout the family

STM32F469xx devices are not compatible with other STM32F4xx devices.

*Figure 1* and *Figure 2* show incompatible board designs, respectively, for LQFP176 and LQFP208 packages (highlighted pins).

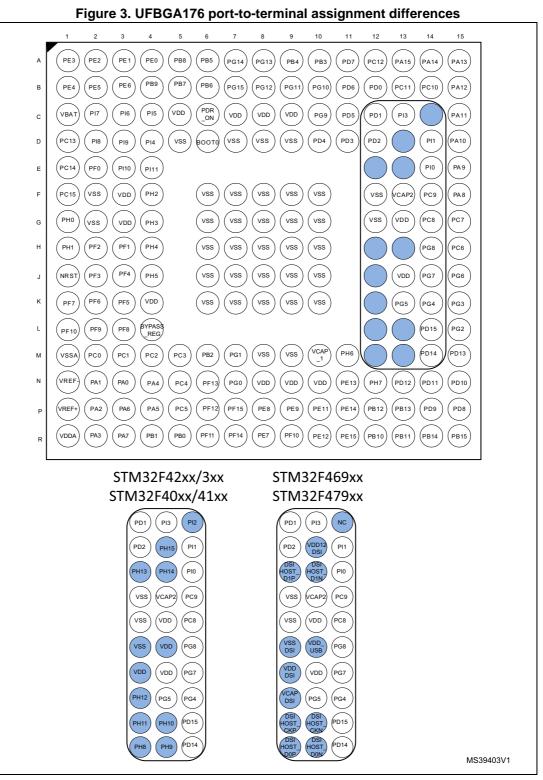

The UFBGA176 and TFBGA216 ballouts are compatible with other STM32F4xx devices, only few IO port pins are substituted, as shown in *Figure 3* and *Figure 4*.

The LQFP100, LQFP144 and UFBGA169 packages are incompatible with other STM32F4xx devices.

### 1.1.3 UFBGA176 package

1. The highlighted pins are substituted with dedicated DSI IO pins on STM32F469xx/479xx devices.

DocID028196 Rev 4

Like backup SRAM, the RTC and backup registers are supplied through a switch that is powered either from the  $V_{DD}$  supply when present or from the  $V_{BAT}$  pin.

### 2.22 Low-power modes

The devices support three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Stop mode

The Stop mode achieves the lowest power consumption while retaining the contents of SRAM and registers. All clocks in the 1.2 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled.

The voltage regulator can be put either in main regulator mode (MR) or in low-power mode (LPR). Both modes can be configured as follows (see *Table 5*):

- Normal mode (default mode when MR or LPR is enabled)

- Under-drive mode.

The device can be woken up from the Stop mode by any of the EXTI line (the EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm / wakeup / tamper / time stamp events, the USB OTG FS/HS wakeup or the Ethernet wakeup).

| Voltage regulator<br>configuration | Main regulator (MR)    | Low-power regulator (LPR) |

|------------------------------------|------------------------|---------------------------|

| Normal mode                        | MR ON                  | LPR ON                    |

| Under-drive mode                   | MR in under-drive mode | LPR in under-drive mode   |

Table 5. Voltage regulator modes in stop mode

### • Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.2 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, the SRAM and register contents are lost except for registers in the backup domain and the backup SRAM when selected.

The device exits the Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm / wakeup / tamper /time stamp event occurs.

The standby mode is not supported when the embedded voltage regulator is bypassed and the 1.2 V domain is controlled by an external power.

# 2.23 V<sub>BAT</sub> operation

The  $V_{BAT}$  pin allows to power the device  $V_{BAT}$  domain from an external battery, an external supercapacitor, or from  $V_{DD}$  when no external battery and an external supercapacitor are present.

### 2.24.1 Advanced-control timers (TIM1, TIM8)

The advanced-control timers (TIM1, TIM8) can be seen as three-phase PWM generators multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead times. They can also be considered as complete general-purpose timers. Their 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge- or center-aligned modes)

- One-pulse mode output

If configured as standard 16-bit timers, they have the same features as the general-purpose TIMx timers. If configured as 16-bit PWM generators, they have full modulation capability (0-100%).

The advanced-control timer can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

TIM1 and TIM8 support independent DMA request generation.

### 2.24.2 General-purpose timers (TIMx)

There are ten synchronizable general-purpose timers embedded in the STM32F46x devices (see *Table 6* for differences).

### • TIM2, TIM3, TIM4, TIM5

The STM32F46x include 4 full-featured general-purpose timers: TIM2, TIM5, TIM3, and TIM4.The TIM2 and TIM5 timers are based on a 32-bit auto-reload up/down counter and a 16-bit prescaler. The TIM3 and TIM4 timers are based on a 16-bit auto-reload up/down counter and a 16-bit prescaler. They all feature 4 independent channels for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input capture/output compare/PWMs on the largest packages.

The TIM2, TIM3, TIM4, TIM5 general-purpose timers can work together, or with the other general-purpose timers and the advanced-control timers TIM1 and TIM8 via the Timer Link feature for synchronization or event chaining.

Any of these general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4, TIM5 all have independent DMA request generation. They are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 4 hall-effect sensors.

### • TIM9, TIM10, TIM11, TIM12, TIM13, and TIM14

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM10, TIM11, TIM13, and TIM14 feature one independent channel, whereas TIM9 and TIM12 have two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers. They can also be used as simple time bases.

### 2.24.3 Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger and waveform generation. They can also be used as a generic 16-bit time base.

TIM6 and TIM7 support independent DMA request generation.

DocID028196 Rev 4

### 2.24.4 Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes.

### 2.24.5 Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

### 2.24.6 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard downcounter. It features:

- A 24-bit downcounter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source.

# 2.25 Inter-integrated circuit interface (I<sup>2</sup>C)

Up to three I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support the standard (up to 100 KHz), and fast (up to 400 KHz) modes. They support the 7/10-bit addressing mode and the 7-bit dual addressing mode (as slave). A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SMBus 2.0/PMBus.

The devices also include programmable analog and digital noise filters (see Table 7).

| Filter                           | Analog  | Digital                                                |

|----------------------------------|---------|--------------------------------------------------------|

| Pulse width of suppressed spikes | ≥ 50 ns | Programmable length from 1 to 15 I2C peripheral clocks |

### Table 7. Comparison of I2C analog and digital filters

# 2.26 Universal synchronous/asynchronous receiver transmitters (USART)

The devices embed four universal synchronous/asynchronous receiver transmitters (USART1, USART2, USART3 and USART6) and four universal asynchronous receiver transmitters (UART4, UART5, UART7, and UART8).

These six interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability. The USART1 and USART6 interfaces are able to

DocID028196 Rev 4

|         |         |          | Pin nı   | umber    |         |         |          |                                                      |           | S              |       | , ,                                                                                     |                         |

|---------|---------|----------|----------|----------|---------|---------|----------|------------------------------------------------------|-----------|----------------|-------|-----------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169 | WLCSP168 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin types | I/O structures | Notes | Alternate functions                                                                     | Additional<br>functions |

| 83      | 115     | A9       | C4       | A12      | 141     | 163     | A12      | PC12                                                 | I/O       | FT             | -     | TRACED3,<br>SPI3_MOSI/I2S3_SD,<br>USART3_CK, UART5_TX,<br>SDIO_CK, DCMI_D9,<br>EVENTOUT | -                       |

| 84      | 116     | C9       | E6       | B12      | 142     | 164     | B12      | PD0                                                  | I/O       | FT             | -     | CAN1_RX, FMC_D2,<br>EVENTOUT                                                            | -                       |

| 85      | 117     | C7       | A3       | C12      | 143     | 165     | C12      | PD1                                                  | I/O       | FT             | -     | CAN1_TX, FMC_D3,<br>EVENTOUT                                                            | -                       |

| 86      | 118     | B8       | C5       | D12      | 144     | 166     | D12      | PD2                                                  | I/O       | FT             | -     | TRACED2, TIM3_ETR,<br>UART5_RX, SDIO_CMD,<br>DCMI_D11, EVENTOUT                         | -                       |

| 87      | 119     | C8       | D6       | D11      | 145     | 167     | C11      | PD3                                                  | I/O       | FT             | -     | SPI2_SCK/I2S2_CK,<br>USART2_CTS, FMC_CLK,<br>DCMI_D5, LCD_G7,<br>EVENTOUT               | -                       |

| 88      | 120     | C6       | B4       | D10      | 146     | 168     | D11      | PD4                                                  | I/O       | FT             | -     | USART2_RTS, FMC_NOE,<br>EVENTOUT                                                        | -                       |

| 89      | 121     | B7       | C6       | C11      | 147     | 169     | C10      | PD5                                                  | I/O       | FT             | -     | USART2_TX, FMC_NWE,<br>EVENTOUT                                                         | -                       |

| -       | 122     | F8       | A4       | D8       | 148     | 170     | F8       | VSS                                                  | S         | -              | -     | -                                                                                       | -                       |

| -       | 123     | F7       | -        | C8       | 149     | 171     | E9       | VDD                                                  | S         | -              | -     | -                                                                                       | -                       |

| 90      | 124     | D7       | E7       | B11      | 150     | 172     | B11      | PD6                                                  | I/O       | FT             | -     | SPI3_MOSI/I2S3_SD,<br>SAI1_SD_A, USART2_RX,<br>FMC_NWAIT, DCMI_D10,<br>LCD_B2, EVENTOUT | -                       |

| 91      | -       | A8       | A5       | A11      | 151     | 173     | A11      | PD7                                                  | I/O       | FT             | -     | USART2_CK, FMC_NE1,<br>EVENTOUT                                                         | -                       |

| -       | -       | -        | -        | -        | -       | 174     | B10      | PJ12                                                 | I/O       | FT             | -     | LCD_G3, LCD_B0,<br>EVENTOUT                                                             | -                       |

| -       | -       | -        | -        | -        | -       | 175     | B9       | PJ13                                                 | I/O       | FT             | -     | LCD_G4, LCD_B1,<br>EVENTOUT                                                             | -                       |

| -       | -       | -        | -        | -        | -       | 176     | C9       | PJ14                                                 | I/O       | FT             | -     | LCD_B2, EVENTOUT                                                                        | -                       |

| -       | -       | -        | -        | -        | -       | 177     | D10      | PJ15                                                 | I/O       | FT             | -     | LCD_B3, EVENTOUT                                                                        | -                       |

| -       | 125     | E6       | D7       | C10      | 152     | 178     | D9       | PG9                                                  | I/O       | FT             | -     | USART6_RX,<br>QUADSPI_BK2_IO2,<br>FMC_NE2/FMC_NCE,<br>DCMI_VSYNC, EVENTOUT              | -                       |

| -       | 126     | E7       | C7       | B10      | 153     | 179     | C8       | PG10                                                 | I/O       | FT             | -     | LCD_G3, FMC_NE3,<br>DCMI_D2, LCD_B2,<br>EVENTOUT                                        | -                       |

| -       | 127     | B6       | B6       | В9       | 154     | 180     | B8       | PG11                                                 | I/O       | FT             | -     | ETH_MII_TX_EN/ETH_RMI<br>I_TX_EN, DCMI_D3,<br>LCD_B3, EVENTOUT                          | -                       |

Table 10. STM32F469xx pin and ball definitions (continued)

|         |         |          | Pin nu   | umber    |         |         |          | S S                                                  |                                                      |    |       |                                                                                                                                                     |                         |

|---------|---------|----------|----------|----------|---------|---------|----------|------------------------------------------------------|------------------------------------------------------|----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | LQFP144 | UFBGA169 | WLCSP168 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin types<br>I/O structures<br>Notes                 |    | Notes | Alternate functions                                                                                                                                 | Additional<br>functions |

| -       | 128     | A7       | A6       | B8       | 155     | 181     | C7       | PG12                                                 | I/O                                                  | FT | -     | SPI6_MISO,<br>USART6_RTS, LCD_B4,<br>FMC_NE4, LCD_B1,<br>EVENTOUT                                                                                   | -                       |

| -       | -       | A6       | E8       | A8       | 156     | 182     | В3       | PG13                                                 | I/O                                                  | FT | -     | TRACED0, SPI6_SCK,<br>USART6_CTS,<br>ETH_MII_TXD0/ETH_RMII<br>_TXD0, FMC_A24,<br>LCD_R0, EVENTOUT                                                   | -                       |

| -       | -       | -        | -        | A7       | 157     | 183     | A4       | PG14                                                 | TRACED1, SPI6_MOSI,<br>USART6_TX,<br>OUADSPI_BK2_IO3 |    | -     |                                                                                                                                                     |                         |

| -       | 129     | -        | B7       | D7       | 158     | 184     | F7       | VSS                                                  | S                                                    | -  | -     | -                                                                                                                                                   | -                       |

| -       | 130     | -        | A7       | C7       | 159     | 185     | E8       | VDD                                                  | S                                                    | I  | -     | -                                                                                                                                                   | -                       |

| -       | -       | -        | -        | -        | -       | 186     | D8       | PK3                                                  | I/O                                                  | FT | -     | LCD_B4, EVENTOUT                                                                                                                                    | -                       |

| -       | -       | -        | -        | -        | -       | 187     | D7       | PK4                                                  | I/O                                                  | FT | -     | LCD_B5, EVENTOUT                                                                                                                                    | -                       |

| -       | -       | -        | -        | -        | -       | 188     | C6       | PK5                                                  | I/O                                                  | FT | -     | LCD_B6, EVENTOUT                                                                                                                                    | -                       |

| -       | -       | -        | -        | -        | -       | 189     | C5       | PK6                                                  | I/O                                                  | FT | -     | LCD_B7, EVENTOUT                                                                                                                                    | -                       |

| -       | -       | -        | -        | -        | -       | 190     | C4       | PK7                                                  | I/O                                                  | FT | -     | LCD_DE, EVENTOUT                                                                                                                                    | -                       |

| -       | 131     | F6       | D8       | B7       | 160     | 191     | B7       | PG15                                                 | I/O                                                  | FT | -     | USART6_CTS,<br>FMC_SDNCAS,<br>DCMI_D13, EVENTOUT                                                                                                    | -                       |

| 92      | 132     | В5       | A8       | A10      | 161     | 192     | A10      | PB3(JTDO/TRA<br>CESWO)                               | I/O                                                  | FT | -     | JTDO/TRACESWO,<br>TIM2_CH2, SPI1_SCK,<br>SPI3_SCK/I2S3_CK,<br>EVENTOUT                                                                              | -                       |

| 93      | 133     | D6       | C8       | A9       | 162     | 193     | A9       | PB4(NJTRST)                                          | I/O                                                  | FT | -     | NJTRST, TIM3_CH1,<br>SPI1_MISO, SPI3_MISO,<br>I2S3ext_SD, EVENTOUT                                                                                  | -                       |

| 94      | 134     | D5       | B8       | A6       | 163     | 194     | A8       | PB5                                                  | I/O                                                  | FT | -     | TIM3_CH2, I2C1_SMBA,<br>SPI1_MOSI,<br>SPI3_MOSI/I2S3_SD,<br>CAN2_RX,<br>OTG_HS_ULPI_D7,<br>ETH_PPS_OUT,<br>FMC_SDCKE1,DCMI_D10,<br>LCD_G7, EVENTOUT | -                       |

| 95      | 135     | C5       | G8       | B6       | 164     | 195     | B6       | PB6                                                  | I/O                                                  | FT | -     | TIM4_CH1, I2C1_SCL,<br>USART1_TX, CAN2_TX,<br>QUADSPI_BK1_NCS,<br>FMC_SDNE1, DCMI_D5,<br>EVENTOUT                                                   | -                       |

Table 10. STM32F469xx pin and ball definitions (continued)

| Pin name | NOR/PSRAM/SRAM | NOR/PSRAM Mux | NAND16 | SDRAM  |

|----------|----------------|---------------|--------|--------|

| PF8      | -              | -             | -      | -      |

| PF9      | -              | -             | -      | -      |

| PF10     | -              | -             | -      | -      |

| PG6      | -              | -             | -      | -      |

| PG7      | -              | -             | INT    | -      |

| PE0      | NBL0           | NBL0          | -      | NBL0   |

| PE1      | NBL1           | NBL1          | -      | NBL1   |

| PI4      | NBL2           | -             | -      | NBL2   |

| PI5      | NBL3           | -             | -      | NBL3   |

| PG8      | -              | -             | -      | SDCLK  |

| PC0      | -              | -             | -      | SDNWE  |

| PF11     | -              | -             | -      | SDNRAS |

| PG15     | -              | -             | -      | SDNCAS |

| PH2      | -              | -             | -      | SDCKE0 |

| PH3      | -              | -             | -      | SDNE0  |

| PH6      | -              | -             | -      | SDNE1  |

| PH7      | -              | -             | -      | SDCKE1 |

| PH5      | -              | -             | -      | SDNWE  |

| PC2      | -              | -             | -      | SDNE0  |

| PC3      | -              | -             | -      | SDCKE0 |

| PB5      | -              | -             | -      | SDCKE1 |

| PB6      | -              | -             | -      | SDNE1  |

Table 11. FMC pin definition (continued)

| S   |

|-----|

| -   |

| _   |

| ~   |

| _   |

|     |

| ω   |

| N   |

| _   |

| Π.  |

| •   |

| -+- |

| 6   |

| ~   |

| G   |

|     |

| ~   |

| 6.2 |

| ×   |

|     |

|     |

Pinouts and pin description

|        |      | AF0 | AF1    | AF2          | AF3              | AF4      | AF5                   | AF6             | AF7                       | AF8                                | AF9                                            | AF10                                    | AF11              | AF12                         | AF13                 | AF14          | AF        |

|--------|------|-----|--------|--------------|------------------|----------|-----------------------|-----------------|---------------------------|------------------------------------|------------------------------------------------|-----------------------------------------|-------------------|------------------------------|----------------------|---------------|-----------|

| Р      | ort  | SYS | TIM1/2 | TIM3/4/<br>5 | TIM8/9/<br>10/11 | I2C1/2/3 | SPI1/2/3<br>/4/5/6    | SPI2/3/<br>SAI1 | SPI2/3/<br>USART<br>1/2/3 | USAR<br>T6/<br>UART<br>4/5/7/<br>8 | CAN1/2/<br>TIM12/<br>13/14/<br>QUAD<br>SPI/LCD | QUAD<br>SPI/OT<br>G2_HS<br>/OTG1<br>_FS | ETH               | FMC/<br>SDIO/<br>OTG2_<br>FS | DCMI/<br>DSI<br>HOST | LCD           | S         |

|        | P10  | -   | -      | TIM5_CH4     | -                | -        | SPI2_NSS/I<br>2S2_WS  | -               | -                         | -                                  | -                                              | -                                       | -                 | FMC_D24                      | DCMI_D13             | LCD_G5        | EVE       |

|        | PI1  | -   | -      | -            | -                | -        | SPI2_SCK/I<br>2S2_CK  | -               | -                         | -                                  | -                                              | -                                       | -                 | FMC_D25                      | DCMI_D8              | LCD_G6        | EVE<br>OL |

|        | Pl2  | -   | -      | -            | TIM8_CH4         | -        | SPI2_MISO             | I2S2ext_S<br>D  | -                         | -                                  | -                                              | -                                       | -                 | FMC_D26                      | DCMI_D9              | LCD_G7        | EVE       |

|        | PI3  | -   | -      | -            | TIM8_ETR         | -        | SPI2_MOSI<br>/I2S2_SD | -               | -                         | -                                  | -                                              | -                                       | -                 | FMC_D27                      | DCMI_D10             |               | EVE       |

|        | Pl4  | -   | -      | -            | TIM8_BKI<br>N    | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | FMC_NBL2                     | DCMI_D5              | LCD_B4        | EVE       |

|        | PI5  | -   | -      | -            | TIM8_CH1         | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | FMC_NBL3                     | DCMI_VS<br>YNC       | LCD_B5        | EVI       |

|        | PI6  | -   | -      | -            | TIM8_CH2         | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | FMC_D28                      | DCMI_D6              | LCD_B6        | EVI       |

|        | PI7  | -   | -      | -            | TIM8_CH3         | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | FMC_D29                      | DCMI_D7              | LCD_B7        | EVI       |

| Port I | PI8  | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | -                            | -                    |               | EVI       |

|        | P19  | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | CAN1_RX                                        | -                                       | -                 | FMC_D30                      | -                    | LCD_VSY<br>NC | EVE       |

|        | PI10 | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | ETH_MII_RX_<br>ER | FMC_D31                      | -                    | LCD_HSY<br>NC | EVE       |

|        | PI11 | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | LCD_G6                                         | OTG_HS<br>_ULPI<br>_DIR                 | -                 | -                            | -                    | -             | EVE       |

|        | PI12 | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | -                            | -                    | LCD_HSY<br>NC | EVE       |

|        | PI13 | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | -                            | -                    | LCD_VSY<br>NC | EVI       |

|        | PI14 | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | -                                              | -                                       | -                 | -                            | -                    | LCD_CLK       | EV<br>O   |

|        | PI15 | -   | -      | -            | -                | -        | -                     | -               | -                         | -                                  | LCD_G2                                         | -                                       | -                 | -                            | -                    | LCD_R0        | EVI<br>'O |

81/217

### 5.3.12 PLL spread spectrum clock generation (SSCG) characteristics

The spread spectrum clock generation (SSCG) feature allows to reduce electromagnetic interferences (see *Table 54*). It is available only on the main PLL.

| Symbol            | Parameter             | Min  | Тур | Max <sup>(1)</sup>  | Unit |

|-------------------|-----------------------|------|-----|---------------------|------|

| f <sub>Mod</sub>  | Modulation frequency  | -    | -   | 10                  | KHz  |

| md                | Peak modulation depth | 0.25 | -   | 2                   | %    |

| MODEPER * INCSTEP | -                     | -    | -   | 2 <sup>15</sup> – 1 | -    |

| Table 44. SSCG parameters constraint |

|--------------------------------------|

|--------------------------------------|

1. Guaranteed by design.

### Equation 1

The frequency modulation period (MODEPER) is given by the equation below:

```

MODEPER = round[f_{PLL \ IN} / \ (4 \times f_{Mod})]

```

$f_{\text{PLL}\ \text{IN}}$  and  $f_{\text{Mod}}$  must be expressed in Hz.

As an example:

If  $f_{PLL_IN} = 1$  MHz, and  $f_{MOD} = 1$  kHz, the modulation depth (MODEPER) is given by equation 1:

MODEPER = round

$$[10^{6}/(4 \times 10^{3})] = 250$$

Equation 2

Equation 2 allows to calculate the increment step (INCSTEP):

INCSTEP = round[

$$((2^{15}-1) \times md \times PLLN)/(100 \times 5 \times MODEPER)$$

]

$f_{VCO OUT}$  must be expressed in MHz.

With a modulation depth (md) =  $\pm 2$  % (4 % peak to peak), and PLLN = 240 (in MHz):

INCSTEP = round[ $((2^{15}-1) \times 2 \times 240)/(100 \times 5 \times 250)$ ] = 126md(quantitazed)%

An amplitude quantization error may be generated because the linear modulation profile is obtained by taking the quantized values (rounded to the nearest integer) of MODPER and INCSTEP. As a result, the achieved modulation depth is quantized. The percentage quantized modulation depth is given by the following formula:

$$md_{quantized}$$

% = (MODEPER × INCSTEP × 100 × 5)/ ((2<sup>15</sup> - 1) × PLLN)

As a result:

$md_{guantized}$ % =  $(250 \times 126 \times 100 \times 5)/((2^{15} - 1) \times 240) = 2.002\%$ (peak)

| Symbol            | Parameter           | Conditions                                  | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |  |  |

|-------------------|---------------------|---------------------------------------------|--------------------|-----|--------------------|------|--|--|

|                   |                     | Program/erase parallelism<br>(PSIZE) = x 8  | -                  | 16  | 32                 |      |  |  |

| t <sub>ME</sub>   | Mass erase time     | Program/erase parallelism<br>(PSIZE) = x 16 | -                  | 11  | 22                 |      |  |  |

|                   |                     | Program/erase parallelism<br>(PSIZE) = x 32 | -                  | 8   | 16                 |      |  |  |

| t <sub>BE</sub>   |                     | Program/erase parallelism<br>(PSIZE) = x 8  | -                  | 16  | 32                 | S    |  |  |

|                   | Bank erase time     | time Program/erase parallelism - 11         |                    |     |                    |      |  |  |

|                   |                     | Program/erase parallelism<br>(PSIZE) = x 32 | -                  | 8   | 16                 |      |  |  |

|                   |                     | 32-bit program operation                    | 2.7                | -   | 3.6                |      |  |  |

| V <sub>prog</sub> | Programming voltage | 16-bit program operation                    | 2.1                | -   | 3.6                | V    |  |  |

|                   |                     | 8-bit program operation                     | 1.7                | -   | 3.6                |      |  |  |

Table 50. Flash memory programming (continued)

1. Based on test during characterization.

2. The maximum programming time is measured after 100K erase operations.

|                                 |                                                  | eniory programming      | <u>,</u>           | <u> </u> |                    |      |

|---------------------------------|--------------------------------------------------|-------------------------|--------------------|----------|--------------------|------|

| Symbol                          | Parameter                                        | Conditions              | Min <sup>(1)</sup> | Тур      | Max <sup>(1)</sup> | Unit |

| t <sub>prog</sub>               | Double word programming                          |                         | -                  | 16       | 100 <sup>(2)</sup> | μs   |

| t <sub>ERASE16KB</sub>          | Sector (16 KB) erase time                        | $T_A = 0$ to +40 °C     | -                  | 230      | -                  |      |

| t <sub>ERASE64KB</sub>          | Sector (64 KB) erase time                        | V <sub>DD</sub> = 3.3 V | -                  | 490      | -                  | ms   |

| t <sub>ERASE128KB</sub>         | Sector (128 KB) erase time                       | V <sub>PP</sub> = 8.5 V | -                  | 875      | -                  |      |

| t <sub>ME</sub>                 | Mass erase time                                  |                         | -                  | 6.9      | -                  | S    |

| t <sub>BE</sub>                 | Bank erase time                                  | -                       | -                  | 6.9      | -                  | s    |

| V <sub>prog</sub>               | Programming voltage                              | -                       | 2.7                | -        | 3.6                | V    |

| V <sub>PP</sub>                 | V <sub>PP</sub> voltage range                    | -                       | 7                  | -        | 9                  | v    |

| I <sub>PP</sub>                 | Minimum current sunk on the $V_{\rm PP}$ pin     | -                       | 10                 | -        | -                  | mA   |

| t <sub>VPP</sub> <sup>(3)</sup> | Cumulative time during which $V_{PP}$ is applied | -                       | -                  | -        | 1                  | hour |

### Table 51. Flash memory programming with V<sub>PP</sub>

1. Guaranteed by design.

2. The maximum programming time is measured after 100K erase operations.

3.  $V_{PP}$  should only be connected during programming/erasing.

| Symbol                         | Parar                                                         | neter                                                            | Conditions                                                       | Min                               | Тур | Max | Unit  |

|--------------------------------|---------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------|-----|-----|-------|

|                                | FT, TTa and NR hysteresis                                     | ST I/O input                                                     | 1.7 V≤V <sub>DD</sub> ≤3.6 V                                     | 10%V <sub>DD</sub> <sup>(3)</sup> | -   | -   |       |

| V <sub>HYS</sub>               | BOOT0 I/O inpu                                                | t hysteresis                                                     | 1.75 V≤V <sub>DD</sub> ≤3.6 V, –<br>40 °C≤T <sub>A</sub> ≤105 °C | 0.1                               |     |     | V     |

|                                |                                                               |                                                                  | 1.7 V≤V <sub>DD</sub> ≤3.6 V,<br>0 °C≤T <sub>A</sub> ≤105 °C     | 0.1                               | -   | -   |       |

| L.                             | I/O input leakage current (4)                                 |                                                                  | $V_{SS} \leq V_{IN} \leq V_{DD}$                                 | -                                 | -   | ±1  | μA    |

| l <sub>lkg</sub>               | I/O FT input leal                                             | kage current <sup>(5)</sup>                                      | $V_{IN} = 5 V$                                                   | -                                 | -   | 3   | μΑ    |

| R <sub>PU</sub>                | Weak pull-up<br>equivalent<br>resistor <sup>(6)</sup>         | All pins<br>except for<br>PA10/PB12<br>(OTG_FS_ID,<br>OTG_HS_ID) | V <sub>IN</sub> = V <sub>SS</sub>                                | 30                                | 40  | 50  |       |

| resistor                       | 16313101                                                      | PA10/PB12<br>(OTG_FS_ID,<br>OTG_HS_ID)                           |                                                                  | 7                                 | 10  | 14  | - kΩ  |

| R <sub>PD</sub> do             | equivalent<br>resistor <sup>(7)</sup> PA10/PB12<br>(OTG_FS_II | weak pull-<br>down                                               | V <sub>IN</sub> = V <sub>DD</sub>                                | 30                                | 40  | 50  | - K22 |

|                                |                                                               | PA10/PB12<br>(OTG_FS_ID,<br>OTG_HS_ID)                           |                                                                  | 7                                 | 10  | 14  |       |

| C <sub>IO</sub> <sup>(8)</sup> | I/O pin capacita                                              | nce                                                              | -                                                                | -                                 | 5   | -   | pF    |

| Table 58. I/ | O static | characteristics | (continued) |

|--------------|----------|-----------------|-------------|

|--------------|----------|-----------------|-------------|

1. Guaranteed by design.

2. Tested in production.

3. With a minimum of 200 mV.

4. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins, Refer to Table 57

- 5. To sustain a voltage higher than VDD +0.3 V, the internal pull-up/pull-down resistors must be disabled. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins.Refer to *Table 57*

- 6. Pull-up resistors are designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimum (~10% order).

- 7. Pull-down resistors are designed with a true resistance in series with a switchable NMOS. This NMOS contribution to the series resistance is minimum (~10% order).

- 8. Hysteresis voltage between Schmitt trigger switching levels. Based on test during characterization.

| Symbol | Parameter                    | Test conditions                                             | Тур | Max <sup>(2)</sup> | Unit |  |  |  |  |

|--------|------------------------------|-------------------------------------------------------------|-----|--------------------|------|--|--|--|--|

| ET     | Total unadjusted error       | ( (0))                                                      | ±3  | ±4                 |      |  |  |  |  |

| EO     | Offset error                 | f <sub>ADC</sub> =18 MHz<br>V <sub>DDA</sub> = 1.7 to 3.6 V | ±2  | ±3                 |      |  |  |  |  |

| EG     | Gain error                   | $V_{\text{REF}}$ = 1.7 to 3.6 V                             | ±1  | ±3                 | LSB  |  |  |  |  |

| ED     | Differential linearity error | $V_{DDA} - V_{REF} < 1.2 V$                                 | ±1  | ±2                 |      |  |  |  |  |

| EL     | Integral linearity error     |                                                             | ±2  | ±3                 |      |  |  |  |  |

Table 77. ADC static accuracy at  $f_{ADC} = 18 \text{ MHz}^{(1)}$

1. Better performance could be achieved in restricted  $V_{\text{DD}}$ , frequency and temperature ranges.

2. Based on test during characterization.

| Symbol | Parameter                    | Test conditions                                                                | Тур  | Max <sup>(2)</sup> | Unit |

|--------|------------------------------|--------------------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       |                                                                                | ±2   | ±5                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> = 30 MHz,<br>R <sub>AIN</sub> < 10 kΩ,                        | ±1.5 | ±2.5               |      |

| EG     | Gain error                   | V <sub>DDA</sub> = 2.4 to 3.6 V,                                               | ±1.5 | ±3                 | LSB  |

| ED     | Differential linearity error | V <sub>REF</sub> = 1.7 to 3.6 V,<br>V <sub>DDA</sub> –V <sub>REF</sub> < 1.2 V | ±1   | ±2                 |      |

| EL     | Integral linearity error     |                                                                                | ±1.5 | ±3                 |      |

# Table 78. ADC static accuracy at $f_{ADC} = 30 \text{ MHz}^{(1)}$

1. Better performance could be achieved in restricted  $V_{\text{DD}}$ , frequency and temperature ranges.

2. Based on test during characterization.

| Symbol | Parameter                    | Test conditions                                                     | Тур | Max <sup>(2)</sup> | Unit |

|--------|------------------------------|---------------------------------------------------------------------|-----|--------------------|------|

| ET     | Total unadjusted error       |                                                                     | ±4  | ±7                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> =36 MHz,<br>V <sub>DDA</sub> = 2.4 to 3.6 V,       | ±2  | ±3                 |      |

| EG     | Gain error                   | V <sub>DDA</sub> = 2.4 to 3.6 V,<br>V <sub>REF</sub> = 1.7 to 3.6 V | ±3  | ±6                 | LSB  |

| ED     | Differential linearity error | $V_{DDA} - V_{REF} < 1.2 V$                                         | ±2  | ±3                 |      |

| EL     | Integral linearity error     |                                                                     | ±3  | ±6                 |      |

# Table 79. ADC static accuracy at $f_{ADC} = 36 \text{ MHz}^{(1)}$

1. Better performance could be achieved in restricted  $V_{\text{DD}},$  frequency and temperature ranges.

2. Based on test during characterization.

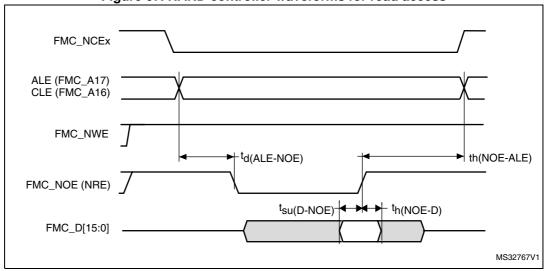

### NAND controller waveforms and timings

Figures 67 through 70 represent synchronous waveforms, and *Table 100* and *Table 101* provide the corresponding timings. The results shown in this table are obtained with the following FMC configuration:

- COM.FMC\_SetupTime = 0x01;

- COM.FMC\_WaitSetupTime = 0x03;

- COM.FMC\_HoldSetupTime = 0x02;

- COM.FMC\_HiZSetupTime = 0x01;

- ATT.FMC\_SetupTime = 0x01;

- ATT.FMC\_WaitSetupTime = 0x03;

- ATT.FMC\_HoldSetupTime = 0x02;

- ATT.FMC\_HiZSetupTime = 0x01;

- Bank = FMC\_Bank\_NAND;

- MemoryDataWidth = FMC\_MemoryDataWidth\_16b;

- ECC = FMC\_ECC\_Enable;

- ECCPageSize = FMC\_ECCPageSize\_512Bytes;

- TCLRSetupTime = 0;

- TARSetupTime = 0;

- Capacitive load C<sub>L</sub> = 30 pF.

In all timing tables, the  $T_{HCLK}$  is the HCLK clock period.

### Figure 67. NAND controller waveforms for read access

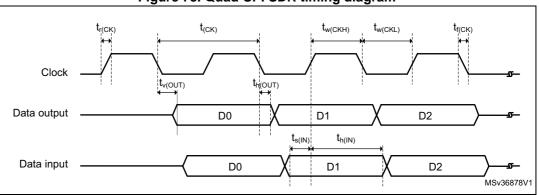

### 5.3.30 Quad-SPI interface characteristics

Unless otherwise specified, the parameters given in *Table 106* and *Table 107* for Quad-SPI are derived from tests performed under the ambient temperature,  $f_{AHB}$  frequency and  $V_{DD}$  supply voltage conditions summarized in Table xx, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Measurement points are done at CMOS levels: 0.5 V<sub>DD</sub>

Refer to *Section 5.3.20* for more details on the input/output alternate function characteristics.

| Symbol              | Parameter                | Parameter Test conditions                                                                                            |                        | Тур | Max                    | Unit |

|---------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------|-----|------------------------|------|

| F <sub>ck</sub>     | Qued SDL cleak frequency | $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}, \text{ C}_{\text{L}} = 20 \text{ pF}$                     | -                      | -   | 90                     |      |

| 1/t <sub>(CK)</sub> | Quad-SPI clock frequency | PI clock frequency $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}, \text{ C}_{\text{L}} = 15 \text{ pF}$ |                        | -   | 84                     | MHz  |

| t <sub>w(CKH)</sub> | Quad-SPI clock high time | -                                                                                                                    | t <sub>(CK)</sub> /2-1 | -   | t <sub>(CK)</sub> /2   |      |

| t <sub>w(CKL)</sub> | Quad-SPI clock low time  | -                                                                                                                    | t <sub>(CK)</sub> /2   | -   | t <sub>(CK)</sub> /2+1 |      |

| t <sub>s(IN)</sub>  | Data input set-up time   | -                                                                                                                    | 0.5                    | -   | -                      | ns   |

| t <sub>h(IN)</sub>  | Data input hold time     | -                                                                                                                    | 3                      | -   | -                      | 115  |

| t <sub>v(OUT)</sub> | Data output valid time   | -                                                                                                                    | -                      | 3   | 4                      |      |

| t <sub>h(OUT)</sub> | Data output hold time    | -                                                                                                                    | 2.5                    | -   | -                      |      |

1. Guaranteed based on test during characterization.

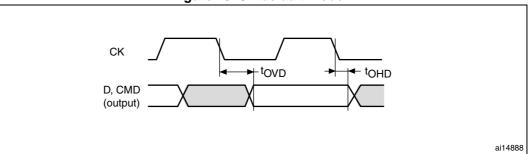

### Figure 73. Quad-SPI SDR timing diagram

### Figure 79. SD default mode

|                     | Table 110. Dynamic characteris          | tics: SD / MMC          | character | istics, V <sub>DD</sub> | = 2.7 to 3. | 6 V <sup>(1)</sup> |

|---------------------|-----------------------------------------|-------------------------|-----------|-------------------------|-------------|--------------------|

| Symbol              | Parameter                               | Conditions              | Min       | Тур                     | Max         | Unit               |

| f <sub>PP</sub>     | Clock frequency in data transfer mode   | -                       | 0         | -                       | 50          | MHz                |

| -                   | SDIO_CK/fPCLK2 frequency ratio          | -                       | -         | -                       | 8/3         | -                  |

| t <sub>W(CKL)</sub> | Clock low time                          | f -50 MHz               | 9.5       | 10.5                    | -           |                    |

| t <sub>W(CKH)</sub> | Clock high time                         | f <sub>pp</sub> =50 MHz | 8.5       | 9.5                     | -           | – ns               |

| CMD, D in           | puts (referenced to CK) in MMC and SE   | OHS mode                |           |                         |             |                    |

| t <sub>ISU</sub>    | Input setup time HS                     | 6 - FO MU-              | 2.0       | -                       | -           |                    |

| t <sub>IH</sub>     | Input hold time HS                      | f <sub>pp</sub> =50 MHz | 2.0       | -                       | -           | ns ns              |

| CMD, D ou           | tputs (referenced to CK) in MMC and S   | SD HS mode              |           |                         |             |                    |

| t <sub>OV</sub>     | Output valid time HS                    | £ 50 MUL                | -         | 13                      | 13.5        |                    |

| t <sub>OH</sub>     | Output hold time HS                     | f <sub>pp</sub> =50 MHz | 12.5      | -                       | -           | ns ns              |

| CMD, D in           | puts (referenced to CK) in SD default m | node                    |           |                         |             |                    |

| t <sub>ISUD</sub>   | Input setup time SD                     | ( 05 MH                 | 2.0       | -                       | -           |                    |

| t <sub>IHD</sub>    | Input hold time SD                      | f <sub>pp</sub> =25 MHz | 2.5       | -                       | -           | ns                 |

| CMD, D ou           | tputs (referenced to CK) in SD default  | mode                    |           | -                       |             |                    |

| t <sub>OVD</sub>    | Output valid default time SD            | 6 05 14                 | _         | 1.5                     | 2.0         |                    |

| t <sub>OHD</sub>    | Output hold default time SD             | f <sub>pp</sub> =25 MHz | 1.0       | -                       | -           | – ns               |

1. Guaranteed based on test during characterization.

| package mechanical data |             |        |       |                       |        |        |  |  |

|-------------------------|-------------|--------|-------|-----------------------|--------|--------|--|--|

| Symbol                  | millimeters |        |       | inches <sup>(1)</sup> |        |        |  |  |

| Symbol                  | Min         | Тур    | Max   | Min                   | Тур    | Max    |  |  |

| А                       | 0.525       | 0.555  | 0.585 | 0.0207                | 0.0219 | 0.0230 |  |  |

| A1                      | -           | 0.170  | -     | -                     | 0.0067 | -      |  |  |

| A2                      | -           | 0.380  | -     | -                     | 0.0150 | -      |  |  |

| A3 <sup>(2)</sup>       | -           | 0.025  | -     | -                     | 0.0010 | -      |  |  |

| b <sup>(3)</sup>        | 0.220       | 0.250  | 0.280 | 0.0087                | 0.0098 | 0.0110 |  |  |

| D                       | 4.856       | 4.891  | 4.926 | 0.1912                | 0.1926 | 0.1939 |  |  |

| Е                       | 5.657       | 5.692  | 5.727 | 0.2227                | 0.2241 | 0.2255 |  |  |

| е                       | -           | 0.400  | -     | -                     | 0.0157 | -      |  |  |

| e1                      | -           | 4.400  | -     | -                     | 0.1732 | -      |  |  |

| e2                      | -           | 5.200  | -     | -                     | 0.2047 | -      |  |  |

| F                       | -           | 0.2455 | -     | -                     | 0.0097 | -      |  |  |

| G                       | -           | 0.246  | -     | -                     | 0.0097 | -      |  |  |

| aaa                     | -           | -      | 0.100 | -                     | -      | 0.0039 |  |  |

| bbb                     | -           | -      | 0.100 | -                     | -      | 0.0039 |  |  |

| CCC                     | -           | -      | 0.100 | -                     | -      | 0.0039 |  |  |

| ddd                     | -           | -      | 0.050 | -                     | -      | 0.0020 |  |  |

| eee                     | -           | -      | 0.050 | -                     | -      | 0.0020 |  |  |

# Table 115. WLCSP168 - 168-pin, 4.891 x 5.692 mm, 0.4 mm pitch wafer level chip scalepackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating.

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

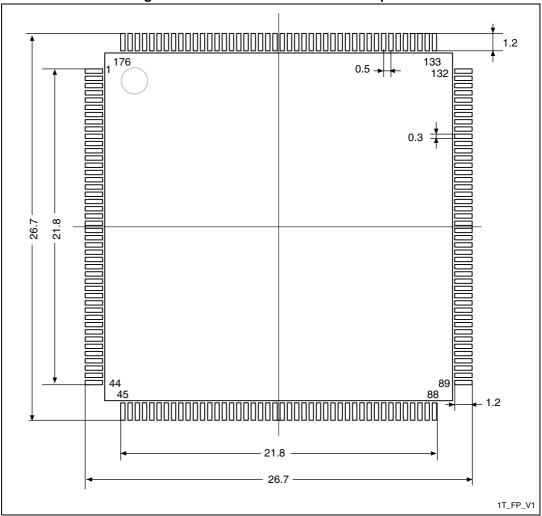

Figure 90. LQFP176 recommended footprint

<sup>1.</sup> Dimensions are expressed in millimeters.

|        | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|--------|-----------------------|--------|--------|

| Symbol | Min         | Тур    | Max    | Min                   | Тур    | Max    |

| С      | 0.090       | -      | 0.200  | 0.0035                | -      | 0.0079 |

| D      | 29.800      | 30.000 | 30.200 | 1.1732                | 1.1811 | 1.1890 |

| D1     | 27.800      | 28.000 | 28.200 | 1.0945                | 1.1024 | 1.1102 |

| D3     | -           | 25.500 | -      | -                     | 1.0039 | -      |

| E      | 29.800      | 30.000 | 30.200 | 1.1732                | 1.1811 | 1.1890 |

| E1     | 27.800      | 28.000 | 28.200 | 1.0945                | 1.1024 | 1.1102 |

| E3     | -           | 25.500 | -      | -                     | 1.0039 | -      |

| e      | -           | 0.500  | -      | -                     | 0.0197 | -      |

| L      | 0.450       | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000  | -      | -                     | 0.0394 | -      |

| k      | 0°          | 3.5°   | 7.0°   | 0°                    | 3.5°   | 7.0°   |

| CCC    | -           | -      | 0.080  | -                     | -      | 0.0031 |

# Table 120. LQFP208, 28 x 28 mm, 208-pin low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# Appendix A Recommendations when using internal reset OFF

When the internal reset is OFF, the following integrated features are no longer supported:

- The integrated power-on reset (POR) / power-down reset (PDR) circuitry is disabled.

- The brownout reset (BOR) circuitry must be disabled.

- The embedded programmable voltage detector (PVD) is disabled.

- V<sub>BAT</sub> functionality is no more available and VBAT pin should be connected to V<sub>DD</sub>.

- The over-drive mode is not supported.

# A.1 Operating conditions

### Table 124. Limitations depending on the operating power supply range

| Opera<br>pow<br>supp<br>rang               | er<br>oly | ADC<br>operation                     | Maximum<br>Flash<br>memory<br>access<br>frequency<br>with no wait<br>states<br>(f <sub>Flashmax</sub> ) | Maximum Flash<br>memory access<br>frequency with<br>wait states <sup>(1)(2)</sup> | I/O operation                           | Possible Flash<br>memory<br>operations        |

|--------------------------------------------|-----------|--------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------|

| V <sub>DD</sub> =1<br>2.1 V <sup>(3)</sup> | .7 to     | Conversion<br>time up to<br>1.2 Msps | 20 MHz <sup>(4)</sup>                                                                                   | 168 MHz with 8<br>wait states and<br>over-drive OFF                               | <ul> <li>No I/O compensation</li> </ul> | 8-bit erase and<br>program<br>operations only |

1. Applicable only when the code is executed from Flash memory. When the code is executed from RAM, no wait state is required.

2. Thanks to the ART accelerator and the 128-bit Flash memory, the number of wait states given here does not impact the execution speed from Flash memory since the ART accelerator allows to achieve a performance equivalent to 0 wait state program execution.

3. V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V, with the use of an external power supply supervisor (refer to Section 2.19.1: Internal reset ON).

4. Prefetch is not available. Refer to AN3430 application note for details on how to adjust performance and power.