# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                              |

|----------------------------|-----------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                                  |

| Speed                      | 180MHz                                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SAI, SDIO, SPI, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                   |

| Number of I/O              | 71                                                                                                  |

| Program Memory Size        | 1MB (1M × 8)                                                                                        |

| Program Memory Type        | FLASH                                                                                               |

| EEPROM Size                | -                                                                                                   |

| RAM Size                   | 384K x 8                                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                         |

| Data Converters            | A/D 14x12b; D/A 2x12b                                                                               |

| Oscillator Type            | Internal                                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                   |

| Mounting Type              | Surface Mount                                                                                       |

| Package / Case             | 100-LQFP                                                                                            |

| Supplier Device Package    | 100-LQFP (14x14)                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f469vgt6                               |

|                            |                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

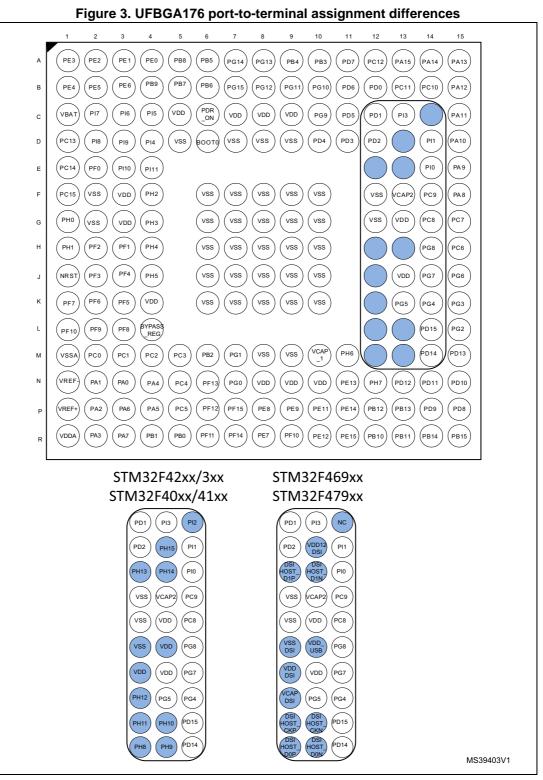

### 1.1.3 UFBGA176 package

1. The highlighted pins are substituted with dedicated DSI IO pins on STM32F469xx/479xx devices.

DocID028196 Rev 4

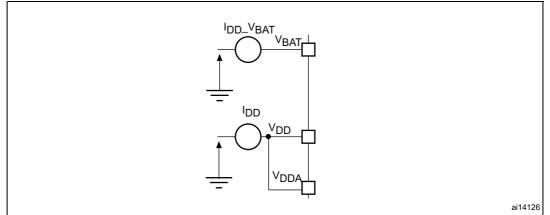

Like backup SRAM, the RTC and backup registers are supplied through a switch that is powered either from the  $V_{DD}$  supply when present or from the  $V_{BAT}$  pin.

## 2.22 Low-power modes

The devices support three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Stop mode

The Stop mode achieves the lowest power consumption while retaining the contents of SRAM and registers. All clocks in the 1.2 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled.

The voltage regulator can be put either in main regulator mode (MR) or in low-power mode (LPR). Both modes can be configured as follows (see *Table 5*):

- Normal mode (default mode when MR or LPR is enabled)

- Under-drive mode.

The device can be woken up from the Stop mode by any of the EXTI line (the EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm / wakeup / tamper / time stamp events, the USB OTG FS/HS wakeup or the Ethernet wakeup).

| Voltage regulator<br>configuration | Main regulator (MR)    | Low-power regulator (LPR) |

|------------------------------------|------------------------|---------------------------|

| Normal mode                        | MR ON                  | LPR ON                    |

| Under-drive mode                   | MR in under-drive mode | LPR in under-drive mode   |

Table 5. Voltage regulator modes in stop mode

#### • Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.2 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, the SRAM and register contents are lost except for registers in the backup domain and the backup SRAM when selected.

The device exits the Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm / wakeup / tamper /time stamp event occurs.

The standby mode is not supported when the embedded voltage regulator is bypassed and the 1.2 V domain is controlled by an external power.

## 2.23 V<sub>BAT</sub> operation

The  $V_{BAT}$  pin allows to power the device  $V_{BAT}$  domain from an external battery, an external supercapacitor, or from  $V_{DD}$  when no external battery and an external supercapacitor are present.

## 2.32 Secure digital input/output interface (SDIO)

An SD/SDIO/MMC host interface is available, that supports MultiMediaCard System Specification Version 4.2 in three different databus modes: 1-bit (default), 4-bit and 8-bit.

The interface allows data transfer at up to 48 MHz, and is compliant with the SD Memory Card Specification Version 2.0.

The SDIO Card Specification Version 2.0 is also supported with two different databus modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDIO/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

In addition to SD/SDIO/MMC, this interface is fully compliant with the CE-ATA digital protocol Rev1.1.

# 2.33 Ethernet MAC interface with dedicated DMA and IEEE 1588 support

The devices provide an IEEE-802.3-2002-compliant media access controller (MAC) for ethernet LAN communications through an industry-standard medium-independent interface (MII) or a reduced medium-independent interface (RMII). The microcontroller requires an external physical interface device (PHY) to connect to the physical LAN bus (twisted-pair, fiber, etc.). The PHY is connected to the device MII port using 17 signals for MII or 9 signals for RMII, and can be clocked using the 25 MHz (MII) from the microcontroller.

The devices include the following features:

- Supports 10 and 100 Mbit/s rates

- Dedicated DMA controller allowing high-speed transfers between the dedicated SRAM and the descriptors (see the STM32F4xx reference manual for details)

- Tagged MAC frame support (VLAN support)

- Half-duplex (CSMA/CD) and full-duplex operation

- MAC control sublayer (control frames) support

- 32-bit CRC generation and removal

- Several address filtering modes for physical and multicast address (multicast and group addresses)

- 32-bit status code for each transmitted or received frame

- Internal FIFOs to buffer transmit and receive frames. The transmit FIFO and the receive FIFO are both 2 Kbytes.

- Supports hardware PTP (precision time protocol) in accordance with IEEE 1588 2008 (PTP V2) with the time stamp comparator connected to the TIM2 input

- Triggers interrupt when system time becomes greater than target time

## 2.34 Controller area network (bxCAN)

The two CANs are compliant with the 2.0A and B (active) specifications with a bitrate up to 1 Mbit/s. They can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. Each CAN has three transmit mailboxes, two receive

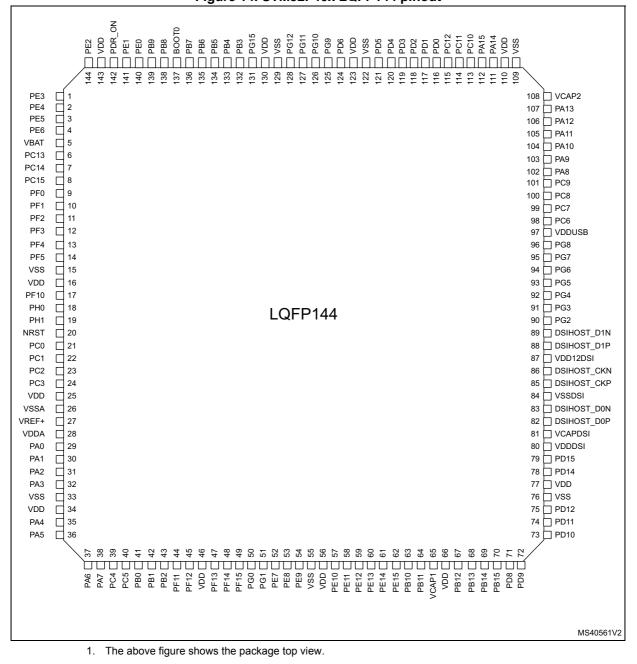

#### Figure 14. STM32F46x LQFP144 pinout

| Pin name | NOR/PSRAM/SRAM | NOR/PSRAM Mux | NAND16 | SDRAM  |

|----------|----------------|---------------|--------|--------|

| PF8      | -              | -             | -      | -      |

| PF9      | -              | -             | -      | -      |

| PF10     | -              | -             | -      | -      |

| PG6      | -              | -             | -      | -      |

| PG7      | -              | -             | INT    | -      |

| PE0      | NBL0           | NBL0          | -      | NBL0   |

| PE1      | NBL1           | NBL1          | -      | NBL1   |

| PI4      | NBL2           | -             | -      | NBL2   |

| PI5      | NBL3           | -             | -      | NBL3   |

| PG8      | -              | -             | -      | SDCLK  |

| PC0      | -              | -             | -      | SDNWE  |

| PF11     | -              | -             | -      | SDNRAS |

| PG15     | -              | -             | -      | SDNCAS |

| PH2      | -              | -             | -      | SDCKE0 |

| PH3      | -              | -             | -      | SDNE0  |

| PH6      | -              | -             | -      | SDNE1  |

| PH7      | -              | -             | -      | SDCKE1 |

| PH5      | -              | -             | -      | SDNWE  |

| PC2      | -              | -             | -      | SDNE0  |

| PC3      | -              | -             | -      | SDCKE0 |

| PB5      | -              | -             | -      | SDCKE1 |

| PB6      | -              | -             | -      | SDNE1  |

Table 11. FMC pin definition (continued)

| ST  |  |

|-----|--|

| M32 |  |

| F46 |  |

| 9xx |  |

Pinouts and pin description

|                 |           |      |             |        |              |                  | Т        | able 12.              | Alterna               | te funct                  | ion (cc                            | ontinued                                       | )                                       |                                    |                              |                      |               |               |

|-----------------|-----------|------|-------------|--------|--------------|------------------|----------|-----------------------|-----------------------|---------------------------|------------------------------------|------------------------------------------------|-----------------------------------------|------------------------------------|------------------------------|----------------------|---------------|---------------|

| 5               |           |      | AF0         | AF1    | AF2          | AF3              | AF4      | AF5                   | AF6                   | AF7                       | AF8                                | AF9                                            | AF10                                    | AF11                               | AF12                         | AF13                 | AF14          | AF15          |

|                 | P         | ort  | SYS         | TIM1/2 | TIM3/4/<br>5 | TIM8/9/<br>10/11 | I2C1/2/3 | SPI1/2/3<br>/4/5/6    | SPI2/3/<br>SAI1       | SPI2/3/<br>USART<br>1/2/3 | USAR<br>T6/<br>UART<br>4/5/7/<br>8 | CAN1/2/<br>TIM12/<br>13/14/<br>QUAD<br>SPI/LCD | QUAD<br>SPI/OT<br>G2_HS<br>/OTG1<br>_FS | ETH                                | FMC/<br>SDIO/<br>OTG2_<br>FS | DCMI/<br>DSI<br>HOST | LCD           | SYS           |

|                 |           | PC0  | -           | -      | -            | -                | -        | -                     | -                     | -                         | -                                  | -                                              | OTG_HS<br>_ULPI_ST<br>P                 | -                                  | FMC_SDN<br>WE                | -                    | LCD_R5        | EVENT<br>OUT  |

|                 |           | PC1  | TRACE<br>D0 | -      | -            | -                | -        | SPI2_MOSI<br>/I2S2_SD | SAI1_SD_<br>A         | -                         | -                                  | -                                              |                                         | ETH_MDC                            | -                            | -                    | -             | EVENT<br>OUT  |

|                 |           | PC2  | -           | -      | _            | -                | -        | SPI2_MISO             | l2S2ext_S<br>D        | -                         | -                                  | -                                              | OTG_HS<br>_ULPI_DI<br>_R                | ETH_MII_TXD<br>2                   | FMC_SDN<br>E0                | -                    | -             | EVENT<br>OUT  |

|                 |           | PC3  | -           | -      | -            | -                | -        | SPI2_MOSI<br>/I2S2_SD | -                     | -                         | -                                  | -                                              | OTG_HS<br>_ULPI_N<br>_XT                | ETH_MII_TX_<br>CLK                 | FMC_SDC<br>KE0               | -                    | -             | EVENT<br>OUT  |

| DocID028196 Rev |           | PC4  | -           | -      | -            | -                | -        | -                     | -                     | -                         | -                                  | -                                              | -                                       | ETH_MII_RXD<br>0/ETH_RMII_R<br>XD0 | FMC_SDN<br>E0                | -                    | -             | EVENT<br>OUT  |

| )28196          |           | PC5  | -           | -      | -            | -                | -        | -                     | -                     | -                         | -                                  | -                                              | -                                       | ETH_MII_RXD<br>1/ETH_RMII_R<br>XD1 | FMC_SDC<br>KE0               | -                    | -             | EVENT<br>OUT  |

| Rev 4           |           | PC6  | -           | -      | TIM3_CH1     | TIM8_CH1         | -        | I2S2_MCK              | -                     | -                         | USART6<br>_TX                      | -                                              | -                                       | -                                  | SDIO_D6                      | DCMI_D0              | LCD_HSY<br>NC | EVENT<br>OUT  |

| -               | Port<br>C | PC7  | -           | -      | TIM3_CH2     | TIM8_CH2         | -        | -                     | I2S3_MCK              | -                         | USART6<br>_RX                      | -                                              | -                                       | -                                  | SDIO_D7                      | DCMI_D1              | LCD_G6        | EVENT<br>OUT  |

|                 |           | PC8  | TRACE<br>D1 | -      | TIM3_CH3     | TIM8_CH3         | -        | -                     | -                     | -                         | USART6<br>_CK                      | -                                              | -                                       | -                                  | SDIO_D0                      | DCMI_D2              | -             | EVENT<br>OUT  |

|                 |           | PC9  | MCO2        | -      | TIM3_CH4     | TIM8_CH4         | I2C3_SDA | I2S_CKIN              | -                     | -                         | -                                  | QUADSPI_<br>BK1_IO0                            | -                                       | -                                  | SDIO_D1                      | DCMI_D3              | -             | EVENT<br>OUT  |

|                 |           | PC10 | -           | -      | -            | -                | -        | -                     | SPI3_SCK/<br>I2S3_CK  | USART3_<br>TX             | UART4_<br>TX                       | QUADSPI_<br>BK1_IO1                            | -                                       | -                                  | SDIO_D2                      | DCMI_D8              | LCD_R2        | EVENT<br>OUT  |

|                 |           | PC11 | -           | -      | -            | -                | -        | I2S3ext_SD            | SPI3_MIS<br>O         | USART3_<br>RX             | UART4_<br>RX                       | QUADSPI_<br>BK2_NCS                            | -                                       | -                                  | SDIO_D3                      | DCMI_D4              | -             | EVENT<br>OUT  |

|                 |           | PC12 | TRACE<br>D3 | -      | -            | -                | -        | -                     | SPI3_MOS<br>I/I2S3_SD | USART3_<br>CK             | UART5_<br>TX                       | -                                              | -                                       | -                                  | SDIO_CK                      | DCMI_D9              | -             | EVENT<br>OUT  |

|                 |           | PC13 | -           | -      | -            | -                | -        | -                     | -                     | -                         | -                                  | -                                              | -                                       | -                                  | -                            | -                    | -             | EVENT<br>OUT  |

| 7               |           | PC14 | -           | -      | -            | -                | -        | -                     | -                     | -                         | -                                  | -                                              | -                                       | -                                  | -                            | -                    | -             | EVENT<br>OUT  |

| 75/217          |           | PC15 | -           | -      | -            | -                | -        | -                     | -                     | -                         | -                                  | -                                              | -                                       | -                                  | -                            | -                    | -             | EVENT<br>'OUT |

### 5.1.7 Current consumption measurement

#### Figure 25. Current consumption measurement scheme

## 5.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 14*, *Table 15*, and *Table 16* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                            | Ratings                                                                                                           | Min                   | Max                  | Unit |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>  | (including v <sub>DDA</sub> , v <sub>DD</sub> , v <sub>DDUSB</sub> , v <sub>DDDSI</sub> and v <sub>BAT</sub> ), / |                       |                      |      |

|                                   | Input voltage on FT pins <sup>(2)</sup>                                                                           |                       | V <sub>DD</sub> +4.0 |      |

| V <sub>IN</sub>                   | Input voltage on TTa pins                                                                                         | V <sub>SS</sub> – 0.3 | 4.0                  | V    |

|                                   | Input voltage on any other pin                                                                                    | V <sub>SS</sub> - 0.3 | 4.0                  |      |

|                                   | Input voltage on BOOT pin                                                                                         | V <sub>SS</sub>       | 9.0                  |      |

| $ \Delta V_{DDx} $                | Variations between different $V_{DD}$ power pins                                                                  | -                     | 50                   | mV   |

| V <sub>SSX</sub> -V <sub>SS</sub> | $\langle V_{SS}  $ Variations between all the different ground pins <sup>(3)</sup>                                |                       | 50                   | 1110 |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage (human body model)                                                                | see Sectio            | n 5.3.18             |      |

| Table 14. Voltage | characteristics |

|-------------------|-----------------|

|-------------------|-----------------|

All main power (V<sub>DD</sub>, V<sub>DDA</sub>, V<sub>DDUSB</sub>, V<sub>DDDSI</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

V<sub>IN</sub> maximum value must always be respected. Refer to *Table 15* for the values of the maximum allowed injected current.

3. Including  $V_{REF-}$  pin

#### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load).

- All peripherals are disabled except if it is explicitly mentioned.

- The Flash memory access time is adjusted both to f<sub>HCLK</sub> frequency and V<sub>DD</sub> range (see *Table 18: Limitations depending on the operating power supply range*).

- When the regulator is OFF, the V<sub>12</sub> is provided externally, as described in *Table 17: General operating conditions.*

- The voltage scaling and over-drive mode are adjusted to f<sub>HCLK</sub> frequency as follows:

- Scale 3 for  $f_{HCLK} \le 120$  MHz

- Scale 2 for 120 MHz <  $f_{HCLK} \le 144$  MHz

- Scale 1 for 144 MHz <  $f_{HCLK} \le$  180 MHz. The over-drive is only ON at 180 MHz.

- The system clock is HCLK, f<sub>PCLK1</sub> = f<sub>HCLK</sub>/4, and f<sub>PCLK2</sub> = f<sub>HCLK</sub>/2.

- External clock frequency is 25 MHz and PLL is ON when f<sub>HCLK</sub> is higher than 25 MHz.

- The typical current consumption values are obtained for 1.7 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V voltage range and for ambient temperature T<sub>A</sub>= 25 °C unless otherwise specified.

- The maximum values are obtained for 1.7 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V voltage range and a maximum ambient temperature (T<sub>A</sub>), unless otherwise specified.

- For the voltage range 1.7 V  $\leq$  V<sub>DD</sub>  $\leq$  2.1 V the maximum frequency is 168 MHz.

| Symbol               | Parameter                           | Conditions                                              | Min | Тур  | Max  | Unit |

|----------------------|-------------------------------------|---------------------------------------------------------|-----|------|------|------|

|                      |                                     | f <sub>VCO_OUT</sub> = 500 MHz                          | -   | 0.55 | 0.70 |      |

| I <sub>DD(PLL)</sub> | PLL power consumption on $V_{DD12}$ | sumption on $V_{DD12}$ f <sub>VCO_OUT</sub> = 600 MHz - | -   | 0.65 | 0.80 | mA   |

|                      |                                     | f <sub>VCO_OUT</sub> = 1000 MHz                         | -   | 0.95 | 1.20 |      |

| Table 47. DSI-PLL | characteristics <sup>(1)</sup> | (continued) |

|-------------------|--------------------------------|-------------|

|-------------------|--------------------------------|-------------|

#### 5.3.15 MIPI D-PHY regulator characteristics

The parameters given in *Table 48* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

| Symbol               | Parameter                                                                                                              | Conditions                                   | Min  | Тур  | Мах                                                                                                                                                                            | Unit |

|----------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| V <sub>DD12DSI</sub> | 1.2 V internal voltage on V <sub>DD12DSI</sub>                                                                         | -                                            | 1.15 | 1.20 | 1.30                                                                                                                                                                           | V    |

| C <sub>EXT</sub>     | External capacitor on V <sub>CAPDSI</sub>                                                                              | -                                            | 1.1  | 2.2  | 3.3                                                                                                                                                                            | μF   |

| ESR                  | External Serial Resistor                                                                                               | -                                            | 0    | 25   | 600                                                                                                                                                                            | mΩ   |

| IDDDSIREG            | Regulator power consumption                                                                                            | -                                            | 100  | 120  | 125                                                                                                                                                                            | μA   |

|                      | DSI system (regulator, PLL and                                                                                         | Ultra Low Power Mode<br>(Reg. ON + PLL OFF)  | -    | 290  | 600                                                                                                                                                                            |      |

| I <sub>DDDSI</sub>   | D-PHY) current consumption on V <sub>DDDSI</sub>                                                                       | Stop State<br>(Reg. ON + PLL OFF)            | -    | 290  | 600                                                                                                                                                                            | μA   |

| 1                    | DSI system current consumption on                                                                                      | 10 MHz escape clock<br>(Reg. ON + PLL OFF)   | -    | 4.3  | 1.30<br>3.3<br>600<br>125<br>600                                                                                                                                               | mA   |

| IDDDSILP             | V <sub>DDDSI</sub> in LP mode communication <sup>(2)</sup>                                                             | 20 MHz escape clock<br>(Reg. ON + PLL OFF)   | -    | 4.3  | 5.0                                                                                                                                                                            | ША   |

|                      |                                                                                                                        | 300 Mbps - 1 data lane<br>(Reg. ON + PLL ON) | -    | 8.0  | 8.8                                                                                                                                                                            |      |

|                      | DSI system (regulator, PLL and                                                                                         | 300 Mbps - 2data lane<br>(Reg. ON + PLL ON)  | -    | 11.4 | 12.5                                                                                                                                                                           |      |

| I <sub>DDDSIHS</sub> | D-PHY) current consumption on V <sub>DDDSI</sub><br>in HS mode communication <sup>(3)</sup>                            | 500 Mbps - 1 data lane<br>(Reg. ON + PLL ON) | -    | 13.5 | 14.7                                                                                                                                                                           | mA   |

|                      |                                                                                                                        | 500 Mbps - 2data lane<br>(Reg. ON + PLL ON)  | -    | 18.0 | 19.6                                                                                                                                                                           |      |

|                      | DSI system (regulator, PLL and<br>D-PHY) current consumption on V <sub>DDDSI</sub><br>in HS mode with CLK like payload | 500 Mbps - 2data lane<br>(Reg. ON + PLL ON)  | -    | 21.4 | 1.30         3.3         600         125         600         600         5.0         5.0         8.8         12.5         14.7         19.6         23.3         -         160 |      |

| +                    | Startun dalay                                                                                                          | C <sub>EXT</sub> = 2.2 μF                    | -    | 110  | -                                                                                                                                                                              | 110  |

| t <sub>WAKEUP</sub>  | Startup delay                                                                                                          | C <sub>EXT</sub> = 3.3 μF                    | -    | -    | 160                                                                                                                                                                            | μs   |

| I <sub>INRUSH</sub>  | Inrush current on V <sub>DDDSI</sub>                                                                                   | External capacitor load at start             | -    | 60   | 200                                                                                                                                                                            | mA   |

## Table 48. DSI regulator characteristics<sup>(1)</sup>

1. Based on test during characterization.

2. Values based on an average traffic in LP Command Mode.

3. Values based on an average traffic (3/4 HS traffic & 1/4 LP) in Video Mode.

## 5.3.16 Memory characteristics

#### Flash memory

The characteristics are given at TA = -40 to 105 °C unless otherwise specified.

The devices are shipped to customers with the Flash memory erased.

| Symbol                | Parameter      | Conditions                                  | Min | Тур | Max | Unit |

|-----------------------|----------------|---------------------------------------------|-----|-----|-----|------|

| I <sub>DD</sub> Suppl |                | Write / Erase 8-bit mode, $V_{DD}$ = 1.7 V  | -   | 5   | -   |      |

|                       | Supply current | Write / Erase 16-bit mode, $V_{DD}$ = 2.1 V | -   | 8   | -   | mA   |

|                       |                | Write / Erase 32-bit mode, $V_{DD}$ = 3.3 V | -   | 12  | -   |      |

| Symbol                  | Parameter                  | Conditions                                       | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |  |

|-------------------------|----------------------------|--------------------------------------------------|--------------------|------|--------------------|------|--|

| t <sub>prog</sub>       | Word programming time      | Program/erase parallelism<br>(PSIZE) = x 8/16/32 | -                  | 16   | 100 <sup>(2)</sup> | μs   |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       |                    | 400  | 800                |      |  |

| t <sub>ERASE16KB</sub>  | Sector (16 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 300  | 600                | ms   |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 250  | 500                |      |  |

|                         | Sector (64 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 1200 | 2400               |      |  |

| t <sub>ERASE64KB</sub>  |                            | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 700  | 1400               | ms   |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 550  | 1100               |      |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 2    | 4                  |      |  |

| t <sub>erase128kb</sub> | Sector (128 KB) erase time | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 1.3  | 2.6                | s    |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 1    | 2                  |      |  |

#### Table 50. Flash memory programming

| Symbol Parameter |                | Conditions                                                                              | Value              | Unit    |  |  |

|------------------|----------------|-----------------------------------------------------------------------------------------|--------------------|---------|--|--|

|                  |                | Conditions                                                                              | Min <sup>(1)</sup> | Unit    |  |  |

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                 | kcycles |  |  |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                 |         |  |  |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                 | Years   |  |  |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                 |         |  |  |

Table 52. Flash memory endurance and data retention

2. Cycling performed over the whole temperature range.

#### 5.3.17 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- **FTB**: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 53*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                                   | Level/Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, TFBGA216,<br>T <sub>A</sub> = +25 °C, f <sub>HCLK</sub> = 168 MHz,<br>conforming to IEC 61000-4-2          | 2B          |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 3.3 \text{ V}$ , TFBGA216,<br>T <sub>A</sub> = +25 °C, f <sub>HCLK</sub> = 168 MHz,<br>conforming to IEC 61000-4-2 | 4A          |

Table 53. EMS characteristics

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### CAN (controller area network) interface

Refer to Section 5.3.20 for more details on the input/output alternate function characteristics (CANx\_TX and CANx\_RX).

#### 5.3.24 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 76* are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 17*.

| Symbol                                                      | Parameter                               | Conditions                                      | Min                                                            | Тур | Max               | Unit               |

|-------------------------------------------------------------|-----------------------------------------|-------------------------------------------------|----------------------------------------------------------------|-----|-------------------|--------------------|

| V <sub>DDA</sub>                                            | Power supply                            |                                                 | 1.7 <sup>(1)</sup>                                             | -   | 3.6               |                    |

| $V_{REF}$ +                                                 | Positive reference voltage              | V <sub>DDA</sub> –V <sub>REF+</sub> < 1.2 V     | 1.7 <sup>(1)</sup>                                             | -   | V <sub>DDA</sub>  | V                  |

| V <sub>REF-</sub>                                           | Negative reference voltage              |                                                 | -                                                              | 0   | -                 |                    |

| f                                                           | ADC alook fraguanov                     | V <sub>DDA</sub> = 1.7 <sup>(1)</sup> to 2.4 V  | 0.6                                                            | 15  | 18                | MHz                |

| f <sub>ADC</sub>                                            | ADC clock frequency                     | V <sub>DDA</sub> = 2.4 to 3.6 V                 | 0.6                                                            | 30  | 36                |                    |

| f <sub>TRIG</sub> <sup>(2)</sup> External trigger frequency |                                         | f <sub>ADC</sub> = 30 MHz,<br>12-bit resolution | -                                                              | -   | 1764              | kHz                |

|                                                             |                                         | -                                               | -                                                              | -   | 17                | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                                            | Conversion voltage range <sup>(3)</sup> | -                                               | 0<br>(V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground) | -   | V <sub>REF+</sub> | v                  |

| R <sub>AIN</sub> <sup>(2)</sup>                             | External input impedance                | Details in Equation 1                           | -                                                              | -   | 50                | kΩ                 |

| $R_{ADC}^{(2)(4)}$                                          | Sampling switch resistance              | -                                               | -                                                              | -   | 6                 | kΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>                             | Internal sample and hold capacitor      | -                                               | -                                                              | 4   | 7                 | pF                 |

| + (2)                                                       | Injection trigger conversion            | f <sub>ADC</sub> = 30 MHz                       | -                                                              | -   | 0.100             | μs                 |

| $t_{lat}^{(2)}$                                             | latency                                 | -                                               | -                                                              | -   | 3 <sup>(5)</sup>  | 1/f <sub>ADC</sub> |

| + (2)                                                       | Regular trigger conversion              | f <sub>ADC</sub> = 30 MHz                       | -                                                              | -   | 0.067             | μs                 |

| t <sub>latr</sub> (2)                                       | latency                                 |                                                 | -                                                              | -   | 2 <sup>(5)</sup>  | 1/f <sub>ADC</sub> |

| t <sub>S</sub> <sup>(2)</sup>                               | Sampling time                           | f <sub>ADC</sub> = 30 MHz                       | 0.100                                                          | -   | 16                | μs                 |

| ι <sub>S</sub> `-'                                          | Sampling time                           | -                                               | 3                                                              | -   | 480               | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(2)</sup>                            | Power-up time                           | -                                               | -                                                              | 2   | 3                 | μs                 |

Table 76. ADC characteristics

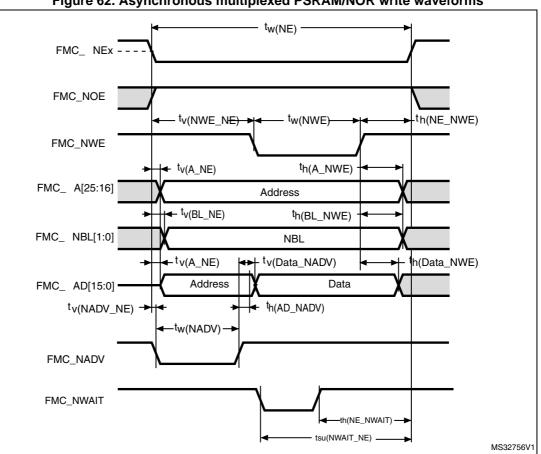

Figure 62. Asynchronous multiplexed PSRAM/NOR write waveforms

| Symbol                    | Parameter                                               | Min                     | Max                     | Unit |

|---------------------------|---------------------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                                         | 4T <sub>HCLK</sub>      | 4T <sub>HCLK</sub> +0.5 |      |

| t <sub>v(NWE_NE)</sub>    | FMC_NEx low to FMC_NWE low                              | T <sub>HCLK</sub> – 1   | T <sub>HCLK</sub> +0.5  |      |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                                        | 2T <sub>HCLK</sub>      | 2T <sub>HCLK</sub> +0.5 |      |

| t <sub>h(NE_NWE)</sub>    | FMC_NWE high to FMC_NE high hold time                   | T <sub>HCLK</sub>       | -                       |      |

| t <sub>v(A_NE)</sub>      | FMC_NEx low to FMC_A valid                              | -                       | 0                       |      |

| t <sub>v(NADV_NE)</sub>   | FMC_NEx low to FMC_NADV low                             | 0.5                     | 1                       |      |

| t <sub>w(NADV)</sub>      | FMC_NADV low time                                       | T <sub>HCLK</sub> – 0.5 | T <sub>HCLK</sub> + 0.5 | ns   |

| t <sub>h(AD_NADV)</sub>   | FMC_AD (address) valid hold time<br>after FMC_NADV high | T <sub>HCLK</sub> – 2   | -                       |      |

| t <sub>h(A_NWE)</sub>     | Address hold time after FMC_NWE high                    | T <sub>HCLK</sub>       | -                       |      |

| t <sub>h(BL_NWE)</sub>    | FMC_BL hold time after FMC_NWE high                     | T <sub>HCLK</sub> – 2   | -                       |      |

| t <sub>v(BL_NE)</sub>     | FMC_NEx low to FMC_BL valid                             | -                       | 2                       |      |

| t <sub>v(Data_NADV)</sub> | FMC_NADV high to Data valid                             | -                       | T <sub>HCLK</sub> +1.5  |      |

| t <sub>h(Data_NWE)</sub>  | Data hold time after FMC_NWE high                       | T <sub>HCLK</sub> +0.5  | -                       |      |

| Symbol                    | Parameter                                 | Min                     | Max                     | Unit |

|---------------------------|-------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 9T <sub>HCLK</sub>      | 9T <sub>HCLK</sub> +0.5 |      |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                          | 7T <sub>HCLK</sub>      | 7T <sub>HCLK</sub> +2   | ns   |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 6T <sub>HCLK</sub> +1.5 | -                       |      |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> –1   | -                       |      |

Table 95. Asynchronous multiplexed PSRAM/NOR write-NWAIT timings<sup>(1)</sup>

#### Synchronous waveforms and timings

Figures 63 through 66 represent synchronous waveforms and *Table 96* through *Table 99* provide the corresponding timings. The results shown in these tables are obtained with the following FMC configuration:

- BurstAccessMode = FMC\_BurstAccessMode\_Enable;

- MemoryType = FMC\_MemoryType\_CRAM;

- WriteBurst = FMC\_WriteBurst\_Enable;

- CLKDivision = 1;

- DataLatency = 1 for NOR Flash; DataLatency = 0 for PSRAM

- C<sub>L</sub> = 30 pF on data and address lines. C<sub>L</sub> = 10 pF on FMC\_CLK unless otherwise specified.

In all timing tables, the  $T_{\text{HCLK}}$  is the HCLK clock period:

- For 2.7 V $\leq$  V<sub>DD</sub> $\leq$  3.6 V, maximum FMC\_CLK = 90 MHz at C<sub>L</sub> = 30 pF (on FMC\_CLK).

- For 1.71 V $\leq$  V<sub>DD</sub><1.9 V, maximum FMC\_CLK = 60 MHz at C<sub>L</sub> = 10 pF (on FMC\_CLK).

Table 100. Switching characteristics for NAND Flash read cycles

| Symbol                  | Parameter                                  | Min                      | Max                      | Unit |

|-------------------------|--------------------------------------------|--------------------------|--------------------------|------|

| t <sub>w(N0E)</sub>     | FMC_NOE low width                          | 4T <sub>HCLK</sub> – 0.5 | 4T <sub>HCLK</sub> +0.5  |      |

| t <sub>su(D-NOE)</sub>  | FMC_D[15-0] valid data before FMC_NOE high | 9                        | -                        |      |

| t <sub>h(NOE-D)</sub>   | FMC_D[15-0] valid data after FMC_NOE high  | 0                        | -                        | ns   |

| t <sub>d(ALE-NOE)</sub> | FMC_ALE valid before FMC_NOE low           | -                        | 3T <sub>HCLK</sub> – 0.5 |      |

| t <sub>h(NOE-ALE)</sub> | FMC_NWE high to FMC_ALE invalid            | 3T <sub>HCLK</sub> – 2   | -                        |      |

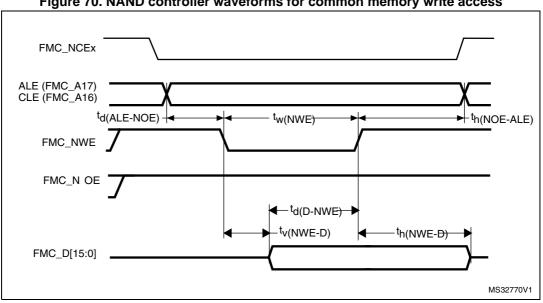

| Table 101. Switching characteristics | for NAND Flash write cycles |

|--------------------------------------|-----------------------------|

|--------------------------------------|-----------------------------|

| Symbol                  | Parameter                             | Min                    | Мах                     | Unit |

|-------------------------|---------------------------------------|------------------------|-------------------------|------|

| t <sub>w(NWE)</sub>     | FMC_NWE low width                     | 4T <sub>HCLK</sub>     | 4T <sub>HCLK</sub> +1   |      |

| t <sub>v(NWE-D)</sub>   | FMC_NWE low to FMC_D[15-0] valid      | 0                      | -                       |      |

| t <sub>h(NWE-D)</sub>   | FMC_NWE high to FMC_D[15-0] invalid   | 3T <sub>HCLK</sub> – 1 | -                       | ns   |

| t <sub>d(D-NWE)</sub>   | FMC_D[15-0] valid before FMC_NWE high | 5T <sub>HCLK</sub> – 3 | -                       | 115  |

| t <sub>d(ALE-NWE)</sub> | FMC_ALE valid before FMC_NWE low      | -                      | 3T <sub>HCLK</sub> -0.5 |      |

| t <sub>h(NWE-ALE)</sub> |                                       |                        | -                       |      |

#### SDRAM waveforms and timings

- $C_L$  = 30 pF on data and address lines.

- $C_L$  = 10 pF on FMC\_SDCLK unless otherwise specified. •

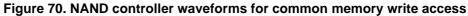

| Symbol                                       | Parameter                        | Min                          | Мах                        | Unit |

|----------------------------------------------|----------------------------------|------------------------------|----------------------------|------|

| f <sub>CLK</sub>                             | LTDC clock output frequency      | -                            | 65                         | MHz  |

| D <sub>CLK</sub>                             | LTDC clock output duty cycle     | 45                           | 55                         | %    |

| t <sub>w(CLKH)</sub><br>t <sub>w(CLKL)</sub> | Clock High time, low time        | t <sub>w(CLK)</sub> /2 – 0.5 | t <sub>w(CLK)</sub> /2+0.5 |      |

| t <sub>v(DATA)</sub>                         | Data output valid time           | -                            | 1.5                        |      |

| t <sub>h(DATA)</sub>                         | Data output hold time            | 0                            | -                          |      |

| t <sub>v(HSYNC)</sub>                        |                                  |                              |                            |      |

| t <sub>v(VSYNC)</sub>                        | HSYNC/VSYNC/DE output valid time | -                            | 0.5                        | ns   |

| t <sub>v(DE)</sub>                           |                                  |                              |                            |      |

| t <sub>h(HSYNC)</sub>                        |                                  |                              |                            |      |

| t <sub>h(VSYNC)</sub>                        | HSYNC/VSYNC/DE output hold time  | 0                            | -                          |      |

| th(DE)                                       |                                  |                              |                            |      |

Table 109. LTDC characteristics<sup>(1)</sup>

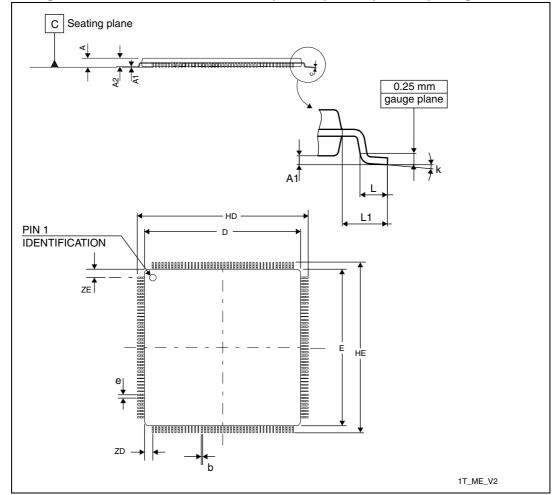

## 6.5 LQFP176 package information

Figure 89. LQFP176, 24 x 24 mm, 176-pin low-profile quad flat package outline

1. Drawing is not to scale.

Table 117. LQFP176, 24 x 24 mm, 176-pin low-profile quad flat package mechanical data

| Symbol |        | millimeters |        |        | inches <sup>(1)</sup> |        |  |

|--------|--------|-------------|--------|--------|-----------------------|--------|--|

| Symbol | Min    | Тур         | Мах    | Min    | Тур                   | Max    |  |

| А      | -      | -           | 1.600  | -      | -                     | 0.0630 |  |

| A1     | 0.050  | -           | 0.150  | 0.0020 | -                     | 0.0059 |  |

| A2     | 1.350  | -           | 1.450  | 0.0531 | -                     | 0.0060 |  |

| b      | 0.170  | -           | 0.270  | 0.0067 | -                     | 0.0106 |  |

| С      | 0.090  | -           | 0.200  | 0.0035 | -                     | 0.0079 |  |

| D      | 23.900 | -           | 24.100 | 0.9409 | -                     | 0.9488 |  |

| Е      | 23.900 | -           | 24.100 | 0.9409 | -                     | 0.9488 |  |

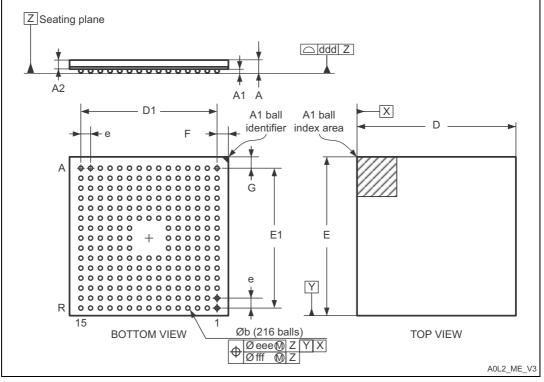

## 6.8 TFBGA216 package information

Figure 97. TFBGA216 - thin fine pitch ball grid array 13 x 13 x 0.8mm, package outline

1. Drawing is not to scale.

| Table 121. TFBGA216 - thin fine pitch ball grid array 13 × 13 × 0.8mm |

|-----------------------------------------------------------------------|

| package mechanical data                                               |

| Symbol |        | millimeters |        |        | inches <sup>(1)</sup> |        |  |  |

|--------|--------|-------------|--------|--------|-----------------------|--------|--|--|

|        | Min    | Тур         | Max    | Min    | Тур                   | Max    |  |  |

| А      | -      | -           | 1.100  | -      | -                     | 0.0433 |  |  |

| A1     | 0.150  | -           | -      | 0.0059 | -                     | -      |  |  |

| A2     | -      | 0.760       | -      | -      | 0.0299                | -      |  |  |

| A4     | -      | 0.210       | -      | -      | 0.0083                | -      |  |  |

| b      | 0.350  | 0.400       | 0.450  | 0.0138 | 0.0157                | 0.0177 |  |  |

| D      | 12.850 | 13.000      | 13.150 | 0.5118 | 0.5118                | 0.5177 |  |  |

| D1     | -      | 11.200      | -      | -      | 0.4409                | -      |  |  |

| E      | 12.850 | 13.000      | 13.150 | 0.5118 | 0.5118                | 0.5177 |  |  |

| E1     | -      | 11.200      | -      | -      | 0.4409                | -      |  |  |

| е      | -      | 0.800       | -      | -      | 0.0315                | -      |  |  |

| F      | -      | 0.900       | -      | -      | 0.0354                | -      |  |  |

| ddd    | -      | -           | 0.080  | -      | -                     | 0.0031 |  |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

## 7 Part numbering

| Table 123. Ordering informa                                                                                                     | tion | sche | me |     |   |    |   |     |

|---------------------------------------------------------------------------------------------------------------------------------|------|------|----|-----|---|----|---|-----|

| Example:                                                                                                                        | STI  | M32  | F  | 469 | V | ΙT | 6 | ххх |

|                                                                                                                                 |      |      |    |     |   |    |   |     |

| Device family                                                                                                                   |      |      |    |     |   |    |   |     |

| STM32 = ARM-based 32-bit microcontroller                                                                                        |      |      |    |     |   |    |   |     |

|                                                                                                                                 |      |      |    |     |   |    |   |     |

| Product type                                                                                                                    |      |      |    |     |   |    |   |     |

| F = general-purpose                                                                                                             |      |      |    |     |   |    |   |     |

| Device subfamily                                                                                                                |      |      |    |     |   |    |   |     |

| 469= STM32F469xx, USB OTG FS/HS, camera interface,<br>Ethernet, LCD-TFT, DSIHost, Quad-SPI,<br>Chrom-ART graphical accelerator. |      |      |    |     |   |    |   |     |

| Pin count                                                                                                                       |      |      |    |     |   |    |   |     |

| V = 100 pins                                                                                                                    |      |      |    |     |   |    |   |     |

| Z = 144 pins                                                                                                                    |      |      |    |     |   |    |   |     |

| A = 168 and 169 pins                                                                                                            |      |      |    |     |   |    |   |     |

| I = 176 pins                                                                                                                    |      |      |    |     |   |    |   |     |

| B = 208 pins                                                                                                                    |      |      |    |     |   |    |   |     |

| N = 216 pins                                                                                                                    |      |      |    |     |   |    |   |     |

| Flash memory size                                                                                                               |      |      |    |     |   |    |   |     |

| E = 512 Kbytes of Flash memory                                                                                                  |      |      |    |     |   |    |   |     |

| G = 1024 Kbytes of Flash memory                                                                                                 |      |      |    |     |   |    |   |     |

| I = 2048 Kbytes of Flash memory                                                                                                 |      |      |    |     |   |    |   |     |

| Package                                                                                                                         |      |      |    |     |   |    |   |     |

| T = LQFP                                                                                                                        |      |      |    |     |   |    |   |     |

| H = BGA                                                                                                                         |      |      |    |     |   |    |   |     |

| Y = WLCSP                                                                                                                       |      |      |    |     |   |    |   |     |

| Temperature range                                                                                                               |      |      |    |     |   |    |   |     |

| 6 = Industrial temperature range, -40 to 85 °C.                                                                                 |      |      |    |     |   |    |   |     |

| 7 = Industrial temperature range, –40 to 105 °C.                                                                                |      |      |    |     |   |    |   |     |

| Options                                                                                                                         |      |      |    |     |   |    |   |     |

xxx = programmed parts

TR = tape and reel

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.

## **Revision history**

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 01-Sep-2015 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 13-Oct-2015 | 2        | Updated Table 4: Regulator ON/OFF and internal reset ON/OFF<br>availability and Table 54: EMI characteristics.<br>Updated Figure 35: PLL output clock waveforms in center spread<br>mode and Figure 36: PLL output clock waveforms in down spread<br>mode.<br>Updated title of Section 6.8: TFBGA216 package information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 08-Mar-2016 | 3        | <ul> <li>Updated cover page with introduction of LQFP100 and LQFP144 packages.</li> <li>Updated Section 1: Description and Section 1.1: Compatibility throughout the family.</li> <li>Updated Figure 1: Incompatible board design for LQFP176 package and its footnote.</li> <li>Updated Table 1: Device summary, Table 2: STM32F469xx features and peripheral counts, Table 4: Regulator ON/OFF and internal reset ON/OFF availability, Table 10: STM32F469xx pin and ball definitions, Table 11: FMC pin definition, Table 12: Alternate function, Table 17: General operating conditions, Table 55: ESD absolute maximum ratings, Table 76: ADC characteristics, Table 122: Package thermal characteristics and Table 123: Ordering information scheme.</li> <li>Removed former Table 73: Ethernet DC electrical characteristics.</li> <li>Added Figure 13: STM32F46x LQFP100 pinout and Figure 14: STM32F46x LQFP144 pinout.</li> <li>Updated Figure 17: STM32F46x UFBGA176 ballout, Figure 18: STM32F46x LQFP176 pinout and Figure 33: ACCHSI vs. temperature.</li> <li>Added Section 6.1: LQFP100 package information and Section 6.2: LQFP144 package information.</li> <li>Replaced former footnote 7 of Table 10: STM32F469xx pin and ball definitions with footnote 2.</li> <li>Added footnote 3 to Table 14: Voltage characteristics.</li> </ul> |  |  |  |

| 02-Mar-2017 | 4        | Updated Table 12: Alternate function.<br>Corrected maximum characterized wakeup timing values for Stop<br>mode in Table 34: Low-power mode wakeup timings.<br>Updated Figure 14: STM32F46x LQFP144 pinout.<br>Updated Device Marking for LQFP100, Device Marking for<br>UFBGA169, Device Marking for LQFP176, Device Marking for<br>LQFP176 and Device Marking for LQFP176.<br>Updated footnotes of figures 82, 85, 88, 91, 96 and 98 in Section 6:<br>Package information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| Table 125 | . Document | revision | history |

|-----------|------------|----------|---------|

|-----------|------------|----------|---------|