#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                              |

|----------------------------|-----------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                                  |

| Speed                      | 180MHz                                                                                              |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SAI, SDIO, SPI, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                   |

| Number of I/O              | 106                                                                                                 |

| Program Memory Size        | 512KB (512K x 8)                                                                                    |

| Program Memory Type        | FLASH                                                                                               |

| EEPROM Size                | -                                                                                                   |

| RAM Size                   | 384К х 8                                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                         |

| Data Converters            | A/D 20x12b; D/A 2x12b                                                                               |

| Oscillator Type            | Internal                                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                   |

| Mounting Type              | Surface Mount                                                                                       |

| Package / Case             | 144-LQFP                                                                                            |

| Supplier Device Package    | 144-LQFP (20x20)                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f469zet6                               |

|                            |                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.10 Quad-SPI memory interface (QUADSPI)

All STM32F469xx devices embeds a Quad-SPI memory interface, which is a specialized communication interface targeting Single, Dual, Quad or Dual-flash SPI memories. It can work in direct mode through registers, external flash status register polling mode and memory mapped mode. Up to 256 Mbytes external Flash memory are mapped, supporting 8, 16 and 32-bit access. Code execution is supported.

The opcode and the frame format are fully programmable. Communication can be either in Single Data Rate or Dual Data Rate.

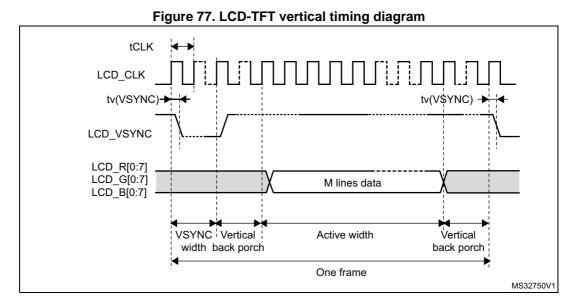

## 2.11 LCD-TFT controller

The LCD-TFT display controller provides a 24-bit parallel digital RGB (Red, Green, Blue) and delivers all signals to interface directly to a broad range of LCD and TFT panels up to XGA (1024x768) resolution with the following features:

- 2 displays layers with dedicated FIFO (64x32-bit)

- Color Look-Up table (CLUT) up to 256 colors (256x24-bit) per layer

- Up to 8 Input color formats selectable per layer

- Flexible blending between two layers using alpha value (per pixel or constant)

- Flexible programmable parameters for each layer

- Color keying (transparency color)

- Up to 4 programmable interrupt events.

## 2.12 DSI Host (DSIHOST)

The DSI Host is a dedicated peripheral for interfacing with MIPI<sup>®</sup> DSI compliant displays. It includes a dedicated video interface internally connected to the LTDC and a generic APB interface that can be used to transmit information to the display.

These interfaces are as follows:

- LTDC interface:

- Used to transmit information in Video Mode, in which the transfers from the host processor to the peripheral take the form of a real-time pixel stream (DPI).

- Through a customized for mode, this interface can be used to transmit information in full bandwidth in the Adapted Command Mode (DBI).

- APB slave interface:

- Allows the transmission of generic information in Command mode, and follows a proprietary register interface.

- Can operate concurrently with either LTDC interface in either Video Mode or Adapted Command Mode.

- Video mode pattern generator:

- Allows the transmission of horizontal/vertical color bar and D-PHY BER testing pattern without any kind of stimuli.

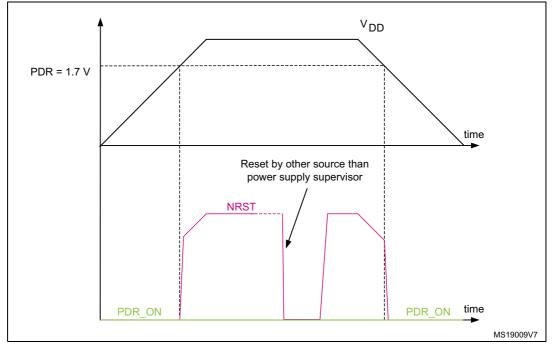

When the internal reset is OFF, the following integrated features are no more supported:

- The integrated power-on reset (POR) / power-down reset (PDR) circuitry is disabled

- The brownout reset (BOR) circuitry must be disabled

- The embedded programmable voltage detector (PVD) is disabled

- V<sub>BAT</sub> functionality is no more available and V<sub>BAT</sub> pin should be connected to V<sub>DD</sub>.

All packages allow to disable the internal reset through the PDR\_ON signal when connected to VSS.

1. PDR\_ON signal to be kept always low.

## 2.20 Voltage regulator

The regulator has four operating modes:

- Regulator ON

- Main regulator mode (MR)

- Low power regulator (LPR)

- Power-down

- Regulator OFF

#### 2.20.1 Regulator ON

On packages embedding the BYPASS\_REG pin, the regulator is enabled by holding BYPASS\_REG low. On all other packages, the regulator is always enabled.

Since the internal voltage scaling is not managed internally, the external voltage value must be aligned with the targeted maximum frequency. Refer to *Operating conditions*. The two 2.2  $\mu$ F ceramic capacitors should be replaced by two 100 nF decoupling capacitors. Refer to *Section 2.18*.

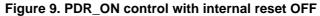

When the regulator is OFF, there is no more internal monitoring on  $V_{12}$ . An external power supply supervisor should be used to monitor the  $V_{12}$  of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on  $V_{12}$  power domain.

In regulator OFF mode, the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset a part of the V<sub>12</sub> logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used under power-on reset. As a consequence, PA0 and NRST pins must be managed separately if the debug connection under reset or pre-reset is required.

- The over-drive and under-drive modes are not available.

- The Standby mode is not available.

#### Figure 10. Regulator OFF

The following conditions must be respected:

- V<sub>DD</sub> should always be higher than V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to avoid current injection between power domains.

- If the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach V<sub>12</sub> minimum value is faster than the time for V<sub>DD</sub> to reach 1.7 V, then PA0 should be kept low to cover both conditions: until V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> reach V<sub>12</sub> minimum value and until V<sub>DD</sub> reaches 1.7 V (see *Figure 11*).

- Otherwise, if the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach V<sub>12</sub> minimum value is slower than the time for V<sub>DD</sub> to reach 1.7 V, then PA0 could be asserted low externally (see *Figure 12*).

- If V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> go below V<sub>12</sub> minimum value and V<sub>DD</sub> is higher than 1.7 V, then a reset must be asserted on PA0 pin.

Note: The minimum value of V<sub>12</sub> depends on the maximum frequency targeted in the application (see Operating conditions).

DocID028196 Rev 4

#### 2.24.4 Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes.

#### 2.24.5 Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### 2.24.6 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard downcounter. It features:

- A 24-bit downcounter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source.

## 2.25 Inter-integrated circuit interface (I<sup>2</sup>C)

Up to three I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support the standard (up to 100 KHz), and fast (up to 400 KHz) modes. They support the 7/10-bit addressing mode and the 7-bit dual addressing mode (as slave). A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SMBus 2.0/PMBus.

The devices also include programmable analog and digital noise filters (see Table 7).

| Filter                           | Analog  | Digital                                                |

|----------------------------------|---------|--------------------------------------------------------|

| Pulse width of suppressed spikes | ≥ 50 ns | Programmable length from 1 to 15 I2C peripheral clocks |

#### Table 7. Comparison of I2C analog and digital filters

# 2.26 Universal synchronous/asynchronous receiver transmitters (USART)

The devices embed four universal synchronous/asynchronous receiver transmitters (USART1, USART2, USART3 and USART6) and four universal asynchronous receiver transmitters (UART4, UART5, UART7, and UART8).

These six interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability. The USART1 and USART6 interfaces are able to

DocID028196 Rev 4

|         |         |          | Pin nu   | umber    |         |         |          |                                                      |           | es             |       |                                                                                |                      |

|---------|---------|----------|----------|----------|---------|---------|----------|------------------------------------------------------|-----------|----------------|-------|--------------------------------------------------------------------------------|----------------------|

| LQFP100 | LQFP144 | UFBGA169 | WLCSP168 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin types | I/O structures | Notes | Alternate functions                                                            | Additional functions |

| -       | 9       | F3       | G10      | E2       | 16      | 16      | D2       | PF0                                                  | I/O       | FT             |       | I2C2_SDA, FMC_A0,<br>EVENTOUT                                                  | -                    |

| -       | 10      | G3       | H10      | H3       | 17      | 17      | E2       | PF1                                                  | I/O       | FT             |       | I2C2_SCL, FMC_A1,<br>EVENTOUT                                                  | -                    |

| -       | 11      | G5       | G12      | H2       | 18      | 18      | G2       | PF2                                                  | I/O       | FT             |       | I2C2_SMBA, FMC_A2,<br>EVENTOUT                                                 | -                    |

| -       | -       | -        | -        | -        | -       | 19      | E3       | PI12                                                 | I/O       | FT             |       | LCD_HSYNC, EVENTOUT                                                            | -                    |

| -       | -       | -        | -        | -        | -       | 20      | G3       | PI13                                                 | I/O       | FT             |       | LCD_VSYNC, EVENTOUT                                                            | -                    |

| -       | -       | -        | -        | -        | -       | 21      | H3       | PI14                                                 | I/O       | FT             |       | LCD_CLK, EVENTOUT                                                              | -                    |

| -       | 12      | H4       | H11      | J2       | 19      | 22      | H2       | PF3                                                  | I/O       | FT             | (5)   | FMC_A3, EVENTOUT                                                               | ADC3_IN9             |

| -       | 13      | L4       | J10      | J3       | 20      | 23      | J2       | PF4                                                  | I/O       | FT             | (5)   | FMC_A4, EVENTOUT                                                               | ADC3_IN14            |

| -       | 14      | H3       | H12      | K3       | 21      | 24      | K3       | PF5                                                  | I/O       | FT             | (5)   | FMC_A5, EVENTOUT                                                               | ADC3_IN15            |

| 7       | 15      | G7       | J11      | G2       | 22      | 25      | H6       | VSS                                                  | S         | -              | -     | -                                                                              | -                    |

| 8       | 16      | G8       | J12      | G3       | 23      | 26      | H5       | VDD                                                  | S         | -              | -     | -                                                                              | -                    |

| -       | -       | -        | -        | K2       | 24      | 27      | К2       | PF6                                                  | I/O       | FT             | (5)   | TIM10_CH1, SPI5_NSS,<br>SAI1_SD_B, UART7_Rx,<br>QUADSPI_BK1_IO3,<br>EVENTOUT   | ADC3_IN4             |

| -       | -       | -        | -        | K1       | 25      | 28      | К1       | PF7                                                  | I/O       | FT             | (5)   | TIM11_CH1, SPI5_SCK,<br>SAI1_MCLK_B, UART7_Tx,<br>QUADSPI_BK1_IO2,<br>EVENTOUT | ADC3_IN5             |

| -       | -       | -        | -        | L3       | 26      | 29      | L3       | PF8                                                  | I/O       | FT             | (5)   | SPI5_MISO, SAI1_SCK_B,<br>TIM13_CH1,<br>QUADSPI_BK1_IO0,<br>EVENTOUT           | ADC3_IN6             |

| -       | -       | -        | -        | L2       | 27      | 30      | L2       | PF9                                                  | I/O       | FT             | (5)   | SPI5_MOSI, SAI1_FS_B,<br>TIM14_CH1,<br>QUADSPI_BK1_IO1,<br>EVENTOUT            | ADC3_IN7             |

| -       | 17      | H1       | K10      | L1       | 28      | 31      | L1       | PF10                                                 | I/O       | FT             | (5)   | QUADSPI_CLK,<br>DCMI_D11, LCD_DE,<br>EVENTOUT                                  | ADC3_IN8             |

| 9       | 18      | G2       | K11      | G1       | 29      | 32      | G1       | PH0-OSC_IN<br>(PH0)                                  | I/O       | FT             | -     | EVENTOUT                                                                       | OSC_IN               |

| 10      | 19      | G1       | K12      | H1       | 30      | 33      | H1       | PH1-OSC_OUT<br>(PH1)                                 | I/O       | FT             | -     | EVENTOUT                                                                       | OSC_OUT              |

| 11      | 20      | H2       | H9       | J1       | 31      | 34      | J1       | NRST                                                 | I/O       | RST            | -     |                                                                                |                      |

| 12      | 21      | M1       | J9       | M2       | 32      | 35      | M2       | PC0                                                  | I/O       | FT             | (5)   | OTG_HS_ULPI_STP,<br>FMC_SDNWE, LCD_R5,<br>EVENTOUT                             | ADC123_<br>IN10      |

Table 10. STM32F469xx pin and ball definitions (continued)

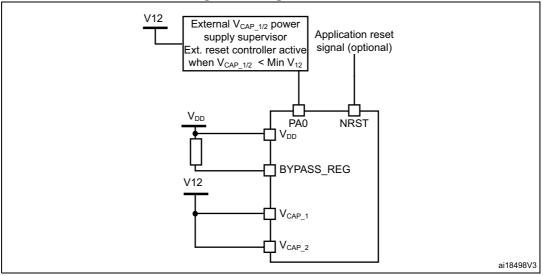

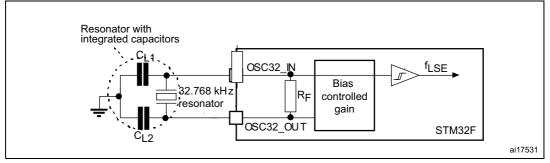

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the informations given in this paragraph are based on characterization results obtained with typical external components specified in *Table 38*.

In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                               | Conditions                     | Min   | Тур  | Max  | Unit |  |  |

|-------------------------------------|-----------------------------------------|--------------------------------|-------|------|------|------|--|--|

| R <sub>F</sub>                      | Feedback resistor                       | -                              | -     | 18.4 | -    | MΩ   |  |  |

|                                     | LSE current consumption                 | Low power mode <sup>(2)</sup>  | -     | -    | 1    |      |  |  |

| I <sub>DD</sub>                     |                                         | High drive mode <sup>(2)</sup> | -     | -    | 3    | μA   |  |  |

| ACC <sub>LSE</sub> <sup>(3)</sup>   | LSE accuracy                            | -                              | - 500 | -    | 500  | ppm  |  |  |

| C crit max                          | Maximum critical crystal g <sub>m</sub> | Low power mode <sup>(2)</sup>  | -     | -    | 0.56 | μA/V |  |  |

| G <sub>m</sub> _crit_max            |                                         | High drive mode <sup>(2)</sup> | -     | -    | 1.5  | μΑνν |  |  |

| t <sub>SU(LSE)</sub> <sup>(4)</sup> | Startup time                            | $V_{\text{DD}}$ is stabilized  | -     | 2    | -    | S    |  |  |

Table 38. LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz)<sup>(1)</sup>

1. Guaranteed by design.

2. LSE mode cannot be changed "on the fly" otherwise, a glitch can be generated on OSCIN pin.

- 3. This parameter depends on the crystal used in the application. Refer to application note AN2867.

- 4. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is based on characterization and not tested in production. It is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

Note:

For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from www.st.com.

|                                        |                                              |                                          | naea)        |     |              |      |

|----------------------------------------|----------------------------------------------|------------------------------------------|--------------|-----|--------------|------|

| Symbol                                 | Parameter                                    | Conditions                               | Min          | Тур | Max          | Unit |

| I <sub>DD(PLLI2S)</sub> <sup>(4)</sup> | PLLI2S power consumption on $\rm V_{\rm DD}$ | VCO freq = 192 MHz<br>VCO freq = 432 MHz | 0.15<br>0.45 | -   | 0.40<br>0.75 | mA   |

|                                        | PLLI2S power consumption on $V_{\mbox{DDA}}$ | VCO freq = 192 MHz<br>VCO freq = 432 MHz | 0.30<br>0.55 | -   | 0.40<br>0.85 | IIIA |

#### Table 42. PLLI2S (audio PLL) characteristics (continued)

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design.

3. Value given with main PLL running.

4. Based on test during characterization.

#### Table 43. PLLSAI (audio and LCD-TFT PLL) characteristics

| Symbol                                  | Parameter                                    | Conditions                                                             |                    | Min                 | Тур  | Max          | Unit |

|-----------------------------------------|----------------------------------------------|------------------------------------------------------------------------|--------------------|---------------------|------|--------------|------|

| f <sub>PLLSAI_IN</sub>                  | PLLSAI input clock <sup>(1)</sup>            | -                                                                      |                    | 0.95 <sup>(2)</sup> | 1    | 2.10         |      |

| f <sub>PLLSAI_OUT</sub>                 | PLLSAI multiplier output clock               | -                                                                      | -                  |                     | -    | 216          | MHz  |

| f <sub>VCO_OUT</sub>                    | PLLSAI VCO output                            | -                                                                      |                    | 192                 | -    | 432          |      |

| +                                       | PLLSAI lock time                             | VCO freq = 192 MHz                                                     | 2                  | 75                  | -    | 200          | 110  |

| t <sub>LOCK</sub>                       |                                              | VCO freq = 432 MHz                                                     | 2                  | 100                 | -    | 300          | μs   |

|                                         |                                              | Cycle to cycle at                                                      | RMS                | -                   | 90   | -            |      |

|                                         | Main CALalack iitten                         | 12.288 MHz on<br>48KHz period,<br>N=432, R=5                           | peak<br>to<br>peak | -                   | ±280 | -            | ps   |

| Jitter <sup>(3)</sup>                   | Main SAI clock jitter                        | Average frequency o<br>12.288 MHz<br>N = 432, R = 5<br>on 1000 samples | f                  | -                   | 90   | -            | ps   |

|                                         | FS clock jitter                              | Cycle to cycle at 48 KHz<br>on 1000 samples                            |                    | -                   | 400  | -            | ps   |

| I <sub>DD(PLLSAI)</sub> <sup>(4)</sup>  | PLLSAI power consumption on $V_{DD}$         | VCO freq = 192 MHz<br>VCO freq = 432 MHz                               |                    | 0.15<br>0.45        | -    | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLLSAI)</sub> <sup>(4)</sup> | PLLSAI power consumption on $V_{\text{DDA}}$ | VCO freq = 192 MHz<br>VCO freq = 432 MHz                               |                    | 0.30<br>0.55        | -    | 0.40<br>0.85 |      |

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design.

3. Value given with main PLL running.

| Table 45. MIPI D-PHY characteristics <sup>(1)</sup> (continued) |                                                                             |                     |         |     |         |      |  |  |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------|---------|-----|---------|------|--|--|

| Symbol                                                          | Parameter                                                                   | Conditions          | Min     | Тур | Мах     | Unit |  |  |

| V <sub>CMTX</sub>                                               | HS transmit common mode voltage                                             | -                   | 150     | 200 | 250     |      |  |  |

| ΔV <sub>CMTX</sub>                                              | V <sub>CMTX</sub> mismatch when output is Differential-0                    | -                   | -       | -   | 5       |      |  |  |

| V <sub>OD</sub>                                                 | HS transmit differential voltage                                            | -                   | 140     | 200 | 270     | mV   |  |  |

| $ \Delta V_{OD} $                                               | V <sub>OD</sub> mismatch when output is<br>Differential-1 or Differential-0 | -                   | -       | -   | 14      |      |  |  |

| V <sub>OHHS</sub>                                               | HS output high voltage                                                      | -                   | -       | -   | 360     |      |  |  |

| Z <sub>OS</sub>                                                 | Single ended output<br>impedance                                            | -                   | 40      | 50  | 62.5    | Ω    |  |  |

| $\Delta Z_{OS}$                                                 | Single ended output<br>impedance mismatch                                   | -                   | -       | -   | 10      | %    |  |  |

| t <sub>HSr</sub> & t <sub>HSf</sub>                             | 20%-80% rise and fall time                                                  | -                   | 100     | -   | 0.35*UI | ps   |  |  |

|                                                                 | LP Receiver                                                                 | r Input Characteris | tics    |     |         |      |  |  |

| V <sub>IL</sub>                                                 | Logic 0 input voltage (not in<br>ULP State)                                 | -                   | -       | -   | 550     |      |  |  |

| V <sub>IL-ULPS</sub>                                            | Logic 0 input voltage in ULP<br>State                                       | -                   | -       | -   | 300     | mV   |  |  |

| V <sub>IH</sub>                                                 | Input high level voltage                                                    | -                   | 880     | -   | -       |      |  |  |

| V <sub>hys</sub>                                                | Voltage hysteresis                                                          | -                   | 25      | -   | -       |      |  |  |

|                                                                 | LP Emitter (                                                                | Output Characteris  | tics    |     |         |      |  |  |

| V <sub>IL</sub>                                                 | Output low level voltage                                                    | -                   | 1.1     | 1.2 | 1.2     | V    |  |  |

| V <sub>IL-ULPS</sub>                                            | Output high level voltage                                                   | -                   | -50     | -   | 50      | mV   |  |  |

| V <sub>IH</sub>                                                 | Output impedance of LP transmitter                                          | -                   | 110     | -   | -       | Ω    |  |  |

| V <sub>hys</sub>                                                | 15%-85% rise and fall time                                                  | -                   | -       | -   | 25      | ns   |  |  |

|                                                                 | LP Contention                                                               | Detector Characte   | ristics |     |         |      |  |  |

| V <sub>ILCD</sub>                                               | Logic 0 contention threshold                                                | _                   | -       | -   | 200     | mV   |  |  |

| V <sub>IHCD</sub>                                               | Logic 0 contention threshold                                                | -                   | 450     | -   | -       |      |  |  |

|                                                                 |                                                                             |                     |         |     |         |      |  |  |

| Table 45. MIPI D-PHY | characteristics <sup>(1)</sup> | (continued) |

|----------------------|--------------------------------|-------------|

|----------------------|--------------------------------|-------------|

1. Guaranteed based on test during characterization.

| Symbol                | Ratings                                                     | Conditions                                                                                                                                             | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge<br>voltage<br>(human body model)    | $T_A = +25 \text{ °C}$<br>conforming to ANSI/ESDA/JEDEC JS-001                                                                                         | 2     | 2000                            |      |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge<br>voltage<br>(charge device model) | T <sub>A</sub> = +25 °C conforming to ANSI/ESD S5.3.1,<br>LQFP100, LQFP144, LQFP176, LQFP208,<br>UFBGA169, UFBGA176, TFBGA216 and<br>WLCSP148 packages | C3    | 250                             | V    |

#### Table 55. ESD absolute maximum ratings

1. Guaranteed based on test during characterization.

#### **Static latchup**

Two complementary static tests are required on six parts to assess the latchup performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latchup standard.

#### Table 56. Electrical sensitivities<sup>(1)</sup>

| Symbol | Parameter             | Conditions                                    | Class      |

|--------|-----------------------|-----------------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105 \text{ °C conforming to JESD78A}$ | II level A |

1. MSV on PA4 and PA5 is 5 V, versus 5.4 V on all IOs.

#### 5.3.19 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (>5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of – 5  $\mu$ A/+0  $\mu$ A range), or other functional failure (for example reset, oscillator frequency deviation).

Negative induced leakage current is caused by negative injection and positive induced leakage current by positive injection.

The test results are given in *Table 57*.

| Symbol           |                                                                                                             | Functional s       |                    |      |

|------------------|-------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|

|                  | Description                                                                                                 | Negative injection | Positive injection | Unit |

|                  | Injected current on BOOT0 and NRST pins                                                                     | - 0                | NA                 |      |

| I <sub>INJ</sub> | Injected current on DSIHOST_D0P,<br>DSIHOST_D0N, DSIHOST_D1P, DSIHOST_D0N,<br>DSIHOST_CKP, DSIHOST_CKN pins | - 0                | 0                  | mA   |

| ·IINJ            | Injected current on PA0 and PC0 pins                                                                        | - 0                | NA                 |      |

|                  | Injected current on any other FT pin                                                                        | - 5                | NA                 |      |

|                  | Injected current on any other pin                                                                           | - 5                | + 5                |      |

| Table 57. I/O | current in | jection a | susce | ptibility | y <sup>(1)</sup> |

|---------------|------------|-----------|-------|-----------|------------------|

|               |            |           |       |           |                  |

1. NA = not applicable.

*Note:* It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

### 5.3.20 I/O port characteristics

#### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 58* are derived from tests performed under the conditions summarized in *Table 17*. All I/Os are CMOS and TTL compliant.

| Symbol          | Parameter                                                                                     | Conditions                                                      | Min                                     | Тур | Max                                    | Unit |

|-----------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------|-----|----------------------------------------|------|

|                 | FT, TTa and NRST I/O input low level voltage 1.7 V≤V <sub>DD</sub> ≤3.6 V                     |                                                                 | -                                       | -   | $0.35V_{DD} - 0.04^{(1)}$              | -    |

|                 |                                                                                               |                                                                 |                                         |     | 0.3V <sub>DD</sub> <sup>(2)</sup>      |      |

| V <sub>IL</sub> | BOOT0 I/O input low level                                                                     | 1.75 V≤V <sub>DD</sub> ≤3.6 V,<br>–40 °C≤T <sub>A</sub> ≤105 °C | -                                       | -   | 0.1V <sub>DD</sub> +0.1 <sup>(1)</sup> |      |

|                 | voltage<br>1.7 V≤V <sub>DD</sub> ≤3.6 V,<br>0 °C≤T <sub>A</sub> ≤105 °C                       |                                                                 | -                                       | -   | 0.1VDD+0.1                             | v    |

|                 | FT, TTa and NRST I/O input<br>high level voltage <sup>(5)</sup><br>BOOT0 I/O input high level | 17/10/ -26/                                                     | 0.45V <sub>DD</sub> +0.3 <sup>(1)</sup> |     |                                        | V    |

|                 |                                                                                               | 1.7 V≤V <sub>DD</sub> ≤3.6 V                                    | 0.7V <sub>DD</sub> <sup>(2)</sup>       | -   | -                                      |      |

| V <sub>IH</sub> |                                                                                               | 1.75 V≤V <sub>DD</sub> ≤3.6 V,<br>–40 °C≤T <sub>A</sub> ≤105 °C | 0.17V <sub>DD</sub> +0.7 <sup>(1)</sup> |     |                                        |      |

|                 | voltage                                                                                       | 1.7 V≤V <sub>DD</sub> ≤3.6 V,<br>0 °C≤T <sub>A</sub> ≤105 °C    | 0.17 VDD+0.7 V                          | _   | -                                      |      |

#### Table 58. I/O static characteristics

| Table 73. Dynamics characteristics. Ethernet MAC signals for SMR |                          |                       |                   |                         |      |

|------------------------------------------------------------------|--------------------------|-----------------------|-------------------|-------------------------|------|

| Symbol                                                           | Parameter                | Min                   | Тур               | Max                     | Unit |

| t <sub>MDC</sub>                                                 | MDC cycle time(2.38 MHz) | 400                   | 400               | 403                     |      |

| T <sub>d(MDIO)</sub>                                             | Write data valid time    | T <sub>HCLK</sub> - 1 | T <sub>HCLK</sub> | T <sub>HCLK</sub> + 1.5 | ns   |

| t <sub>su(MDIO)</sub>                                            | Read data setup time     | 12.5                  | -                 | -                       | 115  |

| t <sub>h(MDIO)</sub>                                             | Read data hold time      | 0                     | -                 | -                       |      |

Table 73. Dynamics characteristics: Ethernet MAC signals for SMI<sup>(1)</sup>

1. Guaranteed based on test during characterization.

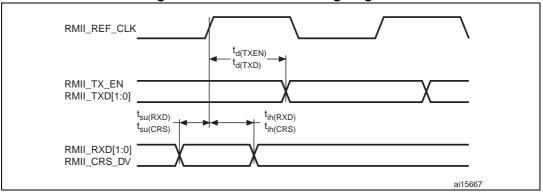

*Table 74* gives the list of Ethernet MAC signals for the RMII and *Figure 52* shows the corresponding timing diagram.

Figure 52. Ethernet RMII timing diagram

| Table 87. DAC characteristics (continued) |                                                                                                                                                                    |     |     |      |      |                                                                                                                         |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|-------------------------------------------------------------------------------------------------------------------------|

| Symbol                                    | Parameter                                                                                                                                                          | Min | Тур | Max  | Unit | Comments                                                                                                                |

|                                           | DAC DC VDDA current                                                                                                                                                | -   | 280 | 380  | μA   | With no load, middle code (0x800) on the inputs                                                                         |

| I <sub>DDA</sub> <sup>(4)</sup>           | consumption in quiescent<br>mode <sup>(3)</sup>                                                                                                                    | -   | 475 | 625  | μA   | With no load, worst code (0xF1C) at<br>V <sub>REF+</sub> = 3.6 V in terms of DC<br>consumption on the inputs            |

| DNL <sup>(4)</sup>                        | Differential non linearity<br>Difference between two                                                                                                               | -   | -   | ±0.5 | LSB  | Given for the DAC in 10-bit configuration.                                                                              |

|                                           | consecutive code-1LSB)                                                                                                                                             | -   | -   | ±2   | LSB  | Given for the DAC in 12-bit configuration.                                                                              |

|                                           | Integral non linearity                                                                                                                                             | -   | -   | ±1   | LSB  | Given for the DAC in 10-bit configuration.                                                                              |

| INL <sup>(4)</sup>                        | (difference between<br>measured value at Code i<br>and the value at Code i on a<br>line drawn between Code 0<br>and last Code 1023)                                | -   | -   | ±4   | LSB  | Given for the DAC in 12-bit configuration.                                                                              |

|                                           | Offset error                                                                                                                                                       | -   | -   | ±10  | mV   | Given for the DAC in 12-bit configuration                                                                               |

| Offset <sup>(4)</sup>                     | (difference between<br>measured value at Code                                                                                                                      | -   | -   | ±3   | LSB  | Given for the DAC in 10-bit at V <sub>REF+</sub> =<br>3.6 V                                                             |

|                                           | (0x800) and the ideal value =<br>V <sub>REF+</sub> /2)                                                                                                             | -   | -   | ±12  | LSB  | Given for the DAC in 12-bit at V <sub>REF+</sub> =<br>3.6 V                                                             |

| Gain<br>error <sup>(4)</sup>              | Gain error                                                                                                                                                         | -   | -   | ±0.5 | %    | Given for the DAC in 12-bit configuration                                                                               |

| tsettling <sup>(4)</sup>                  | Settling time (full scale: for a<br>10-bit input code transition<br>between the lowest and the<br>highest input codes when<br>DAC_OUT reaches final<br>value ±4LSB | -   | 3   | 6    | μs   | C <sub>LOAD</sub> ≤ 50 pF,<br>R <sub>LOAD</sub> ≥ 5 kΩ                                                                  |

| THD <sup>(4)</sup>                        | Total Harmonic Distortion<br>Buffer ON                                                                                                                             | -   | -   | -    | dB   | $C_{LOAD} \le 50 \text{ pF},$<br>$R_{LOAD} \ge 5 \text{ k}\Omega$                                                       |

| Update<br>rate <sup>(2)</sup>             | Max frequency for a correct<br>DAC_OUT change when<br>small variation in the input<br>code (from code i to i+1LSB)                                                 | -   | -   | 1    | MS/s | $C_{LOAD} \le 50 \text{ pF},$<br>$R_{LOAD} \ge 5 \text{ k}\Omega$                                                       |

| t <sub>WAKEUP</sub> <sup>(4)</sup>        | Wakeup time from off state<br>(Setting the ENx bit in the<br>DAC Control register)                                                                                 | -   | 6.5 | 10   | μs   | $C_{LOAD} \le 50 \text{ pF}, R_{LOAD} \ge 5 \text{ k}\Omega$<br>input code between lowest and highest<br>possible ones. |

| PSRR+ <sup>(2)</sup>                      | Power supply rejection ratio<br>(to V <sub>DDA</sub> ) (static DC<br>measurement)                                                                                  | -   | -67 | -40  | dB   | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                                        |

#### Table 87. DAC characteristics (continued)

1. V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 2.19.2).

2. Guaranteed by design.

3. The quiescent mode corresponds to a state where the DAC maintains a stable output level to ensure that no dynamic consumption occurs.

4. Guaranteed based on test during characterization.

|                           | synchronous non-multiplexed SRAW/P    |                          | icaa amings              |      |

|---------------------------|---------------------------------------|--------------------------|--------------------------|------|

| Symbol                    | Parameter                             | Min                      | Мах                      | Unit |

| t <sub>w(NE)</sub>        | FMC_NE low time                       | 2T <sub>HCLK</sub> – 0.5 | 2 T <sub>HCLK</sub> +0.5 |      |

| t <sub>v(NOE_NE)</sub>    | FMC_NEx low to FMC_NOE low            | 0                        | 1                        |      |

| t <sub>w(NOE)</sub>       | FMC_NOE low time                      | 2T <sub>HCLK</sub>       | 2T <sub>HCLK</sub> + 0.5 |      |

| t <sub>h(NE_NOE)</sub>    | FMC_NOE high to FMC_NE high hold time | 0                        | -                        |      |

| t <sub>v(A_NE)</sub>      | FMC_NEx low to FMC_A valid            | -                        | 2                        |      |

| t <sub>h(A_NOE)</sub>     | Address hold time after FMC_NOE high  | 0                        | -                        |      |

| t <sub>v(BL_NE)</sub>     | FMC_NEx low to FMC_BL valid           | -                        | 2                        |      |

| t <sub>h(BL_NOE)</sub>    | FMC_BL hold time after FMC_NOE high   | 0                        | -                        | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FMC_NEx high setup time       | T <sub>HCLK</sub> + 2.5  | -                        |      |

| t <sub>su(Data_NOE)</sub> | Data to FMC_NOEx high setup time      | T <sub>HCLK</sub> +2     | -                        |      |

| t <sub>h(Data_NOE)</sub>  | Data hold time after FMC_NOE high     | 0                        | -                        |      |

| t <sub>h(Data_NE)</sub>   | Data hold time after FMC_NEx high     | 0                        | -                        |      |

| t <sub>v(NADV_NE)</sub>   | FMC_NEx low to FMC_NADV low           | -                        | 0                        | 1    |

| t <sub>w(NADV)</sub>      | FMC_NADV low time                     | -                        | T <sub>HCLK</sub> +1     |      |

Table 88. Asynchronous non-multiplexed SRAM/PSRAM/NOR - read timings<sup>(1)</sup>

1. Based on test during characterization.

| Table 89. Asynchronous non-multiplexed SRAM/PSRAM/NOR read - NWAIT |

|--------------------------------------------------------------------|

| timings <sup>(1)</sup>                                             |

| Symbol                    | Parameter                                 | Min                      | Мах                   | Unit |

|---------------------------|-------------------------------------------|--------------------------|-----------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 7T <sub>HCLK</sub> +0.5  | 7T <sub>HCLK</sub> +1 |      |

| t <sub>w(NOE)</sub>       | FMC_NWE low time                          | 5T <sub>HCLK</sub> – 1.5 | 5T <sub>HCLK</sub> +2 | ns   |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 5T <sub>HCLK</sub> +1.5  | -                     |      |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> +1    | -                     |      |

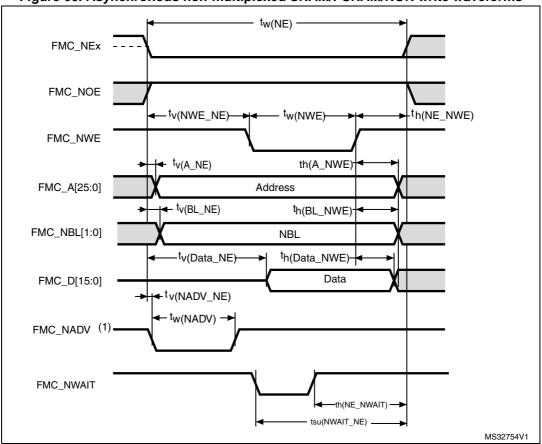

Figure 60. Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms

1. Mode 2/B, C and D only. In Mode 1, FMC\_NADV is not used.

|                        |                       | (1)                                    |

|------------------------|-----------------------|----------------------------------------|

| Table 90. Asynchronous | non-multiplexed SRAM/ | PSRAM/NOR write timings <sup>(1)</sup> |

| Symbol                   | Parameter                             | Min                     | Мах                     | Unit |

|--------------------------|---------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>       | FMC_NE low time                       | 3T <sub>HCLK</sub>      | 3T <sub>HCLK</sub> +1   |      |

| $t_{v(NWE_NE)}$          | FMC_NEx low to FMC_NWE low            | T <sub>HCLK</sub> – 0.5 | T <sub>HCLK</sub> + 0.5 |      |

| t <sub>w(NWE)</sub>      | FMC_NWE low time                      | T <sub>HCLK</sub>       | T <sub>HCLK</sub> + 0.5 |      |

| t <sub>h(NE_NWE)</sub>   | FMC_NWE high to FMC_NE high hold time | T <sub>HCLK</sub> +1.5  | -                       |      |

| t <sub>v(A_NE)</sub>     | FMC_NEx low to FMC_A valid            | -                       | 0                       |      |

| t <sub>h(A_NWE)</sub>    | Address hold time after FMC_NWE high  | T <sub>HCLK</sub> +0.5  | -                       | 20   |

| t <sub>v(BL_NE)</sub>    | FMC_NEx low to FMC_BL valid           | -                       | 1.5                     | ns   |

| t <sub>h(BL_NWE)</sub>   | FMC_BL hold time after FMC_NWE high   | T <sub>HCLK</sub> +0.5  | -                       |      |

| t <sub>v(Data_NE)</sub>  | Data to FMC_NEx low to Data valid     | -                       | T <sub>HCLK</sub> + 2   |      |

| t <sub>h(Data_NWE)</sub> | Data hold time after FMC_NWE high     | T <sub>HCLK</sub> +0.5  | -                       |      |

| t <sub>v(NADV_NE)</sub>  | FMC_NEx low to FMC_NADV low           | -                       | 0.5                     |      |

| t <sub>w(NADV)</sub>     | FMC_NADV low time                     | -                       | T <sub>HCLK</sub> + 0.5 |      |

| Symbol                      | Parameter                                           | Min                    | Max | Unit |

|-----------------------------|-----------------------------------------------------|------------------------|-----|------|

| t <sub>w(CLK)</sub>         | FMC_CLK period, V <sub>DD</sub> range= 2.7 to 3.6 V | 2T <sub>HCLK</sub> – 1 | -   |      |

| t <sub>d(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)                   | -                      | 1.5 | 1    |

| t <sub>d(CLKH-NExH)</sub>   | FMC_CLK high to FMC_NEx high (x= 02)                | T <sub>HCLK</sub>      | -   | 1    |

| t <sub>d(CLKL-NADVL)</sub>  | FMC_CLK low to FMC_NADV low                         | -                      | 0   | 1    |

| t <sub>d(CLKL-NADVH)</sub>  | FMC_CLK low to FMC_NADV high                        | 0                      | -   | 1    |

| t <sub>d(CLKL-AV)</sub>     | FMC_CLK low to FMC_Ax valid (x=1625)                | -                      | 0   | 1    |

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625)             | T <sub>HCLK</sub>      | -   | 1    |

| t <sub>d(CLKL-NWEL)</sub>   | FMC_CLK low to FMC_NWE low                          | -                      | 0   | ns   |

| t <sub>(CLKH-NWEH)</sub>    | FMC_CLK high to FMC_NWE high                        | T <sub>HCLK</sub> -0.5 | -   | 115  |

| t <sub>d(CLKL-ADV)</sub>    | FMC_CLK low to FMC_AD[15:0] valid                   | -                      | 3   | 1    |

| t <sub>d(CLKL-ADIV)</sub>   | FMC_CLK low to FMC_AD[15:0] invalid                 | 0                      | -   | 1    |

| t <sub>d(CLKL-DATA)</sub>   | FMC_A/D[15:0] valid data after FMC_CLK low          | -                      | 3   | 1    |

| t <sub>d(CLKL-NBLL)</sub>   | FMC_CLK low to FMC_NBL low                          | 0                      | -   | 1    |

| t <sub>d(CLKH-NBLH)</sub>   | FMC_CLK high to FMC_NBL high                        | T <sub>HCLK</sub> -0.5 | -   |      |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high                 | 4                      | -   |      |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high                  | 0                      | -   |      |

Table 97. Synchronous multiplexed PSRAM write timings<sup>(1)</sup>

## 5.3.33 SD/SDIO MMC card host interface (SDIO) characteristics

Unless otherwise specified, the parameters given in *Table 110* for the SDIO/MMC interface are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5 V<sub>DD</sub>

Refer to Section 5.3.20 for more details on the input/output characteristics.

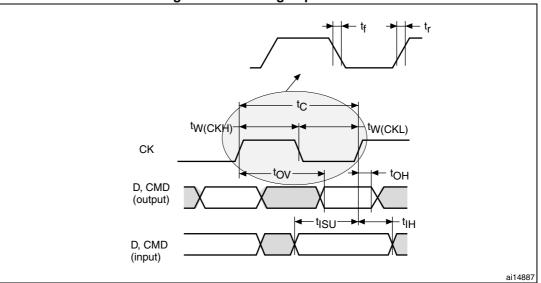

#### Figure 78. SDIO high-speed mode

DocID028196 Rev 4

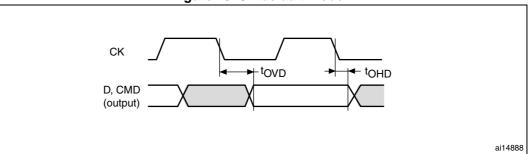

#### Figure 79. SD default mode

|                     | Table 110. Dynamic characteris          | tics: SD / MMC          | character | istics, V <sub>DD</sub> | = 2.7 to 3. | 6 V <sup>(1)</sup> |

|---------------------|-----------------------------------------|-------------------------|-----------|-------------------------|-------------|--------------------|

| Symbol              | Parameter                               | Conditions              | Min       | Тур                     | Max         | Unit               |

| f <sub>PP</sub>     | Clock frequency in data transfer mode   | -                       | 0         | -                       | 50          | MHz                |

| -                   | SDIO_CK/fPCLK2 frequency ratio          | -                       | -         | -                       | 8/3         | -                  |

| t <sub>W(CKL)</sub> | Clock low time                          | 6 50 144                |           | 10.5                    | -           |                    |

| t <sub>W(CKH)</sub> | Clock high time                         | f <sub>pp</sub> =50 MHz | 8.5       | 9.5                     | -           | – ns               |

| CMD, D in           | puts (referenced to CK) in MMC and SE   | OHS mode                |           |                         |             |                    |

| t <sub>ISU</sub>    | Input setup time HS                     | 6 - FO MU-              | 2.0       | -                       | -           |                    |

| t <sub>IH</sub>     | Input hold time HS                      | old time HS             |           | -                       | -           | ns                 |

| CMD, D ou           | tputs (referenced to CK) in MMC and S   | SD HS mode              |           |                         |             |                    |

| t <sub>OV</sub>     | Output valid time HS                    | £ 50 MUL                | -         | 13                      | 13.5        |                    |

| t <sub>OH</sub>     | Output hold time HS                     | f <sub>pp</sub> =50 MHz | 12.5      | -                       | -           | – ns               |

| CMD, D in           | puts (referenced to CK) in SD default m | node                    |           |                         |             |                    |

| t <sub>ISUD</sub>   | Input setup time SD                     |                         | 2.0       | -                       | -           |                    |

| t <sub>IHD</sub>    | Input hold time SD                      | f <sub>pp</sub> =25 MHz | 2.5       | -                       | -           | ns                 |

| CMD, D ou           | tputs (referenced to CK) in SD default  | mode                    |           | -                       |             |                    |

| t <sub>OVD</sub>    | Output valid default time SD            | f -05 ML-               | _         | 1.5                     | 2.0         |                    |

| t <sub>OHD</sub>    | Output hold default time SD             | f <sub>pp</sub> =25 MHz | 1.0       | -                       | -           | – ns               |

1. Guaranteed based on test during characterization.

| Symbol |        | millimeters |        | inches <sup>(1)</sup> |        |        |

|--------|--------|-------------|--------|-----------------------|--------|--------|

| Symbol | Min    | Тур         | Max    | Min                   | Тур    | Max    |

| А      | -      | -           | 1.600  | -                     | -      | 0.0630 |

| A1     | 0.050  | -           | 0.150  | 0.0020                | -      | 0.0059 |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170  | 0.220       | 0.270  | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090  | -           | 0.200  | 0.0035                | -      | 0.0079 |

| D      | 21.800 | 22.000      | 22.200 | 0.8583                | 0.8661 | 0.8740 |

| D1     | 19.800 | 20.000      | 20.200 | 0.7795                | 0.7874 | 0.7953 |

| D3     | -      | 17.500      | -      | -                     | 0.6890 | -      |

| E      | 21.800 | 22.000      | 22.200 | 0.8583                | 0.8661 | 0.8740 |

| E1     | 19.800 | 20.000      | 20.200 | 0.7795                | 0.7874 | 0.7953 |

| E3     | -      | 17.500      | -      | -                     | 0.6890 | -      |

| е      | -      | 0.500       | -      | -                     | 0.0197 | -      |

| L      | 0.450  | 0.600       | 0.750  | 0.0177                | 0.0236 | 0.0295 |

| L1     | -      | 1.000       | -      | -                     | 0.0394 | -      |

| k      | 0°     | 3.5°        | 7°     | 0°                    | 3.5°   | 7°     |

| CCC    | -      | -           | 0.080  | -                     | -      | 0.0031 |

| Table 114. LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package |

|------------------------------------------------------------------------|

| mechanical data                                                        |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

| package mechanical data |             |        |       |                       |        |        |

|-------------------------|-------------|--------|-------|-----------------------|--------|--------|

| Symbol                  | millimeters |        |       | inches <sup>(1)</sup> |        |        |

|                         | Min         | Тур    | Max   | Min                   | Тур    | Max    |

| А                       | 0.525       | 0.555  | 0.585 | 0.0207                | 0.0219 | 0.0230 |

| A1                      | -           | 0.170  | -     | -                     | 0.0067 | -      |

| A2                      | -           | 0.380  | -     | -                     | 0.0150 | -      |

| A3 <sup>(2)</sup>       | -           | 0.025  | -     | -                     | 0.0010 | -      |

| b <sup>(3)</sup>        | 0.220       | 0.250  | 0.280 | 0.0087                | 0.0098 | 0.0110 |

| D                       | 4.856       | 4.891  | 4.926 | 0.1912                | 0.1926 | 0.1939 |

| Е                       | 5.657       | 5.692  | 5.727 | 0.2227                | 0.2241 | 0.2255 |

| е                       | -           | 0.400  | -     | -                     | 0.0157 | -      |

| e1                      | -           | 4.400  | -     | -                     | 0.1732 | -      |

| e2                      | -           | 5.200  | -     | -                     | 0.2047 | -      |

| F                       | -           | 0.2455 | -     | -                     | 0.0097 | -      |

| G                       | -           | 0.246  | -     | -                     | 0.0097 | -      |

| aaa                     | -           | -      | 0.100 | -                     | -      | 0.0039 |

| bbb                     | -           | -      | 0.100 | -                     | -      | 0.0039 |

| CCC                     | -           | -      | 0.100 | -                     | -      | 0.0039 |

| ddd                     | -           | -      | 0.050 | -                     | -      | 0.0020 |

| eee                     | -           | -      | 0.050 | -                     | -      | 0.0020 |

## Table 115. WLCSP168 - 168-pin, 4.891 x 5.692 mm, 0.4 mm pitch wafer level chip scalepackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating.

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

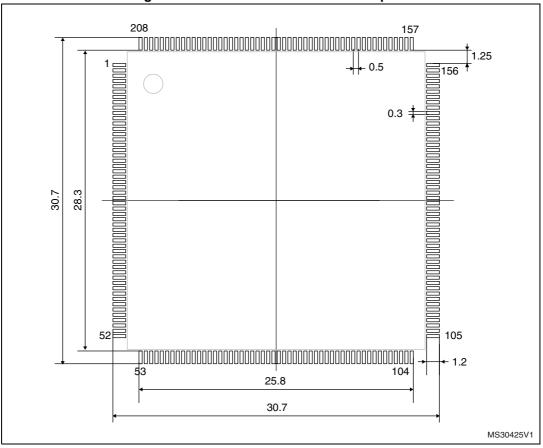

Figure 95. LQFP208 recommended footprint

1. Dimensions are expressed in millimeters.