#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

# Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Not For New Designs                                                                |

|---------------------------------|------------------------------------------------------------------------------------|

| Core Processor                  | ARM® Cortex®-A9                                                                    |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                                     |

| Speed                           | 400MHz                                                                             |

| Co-Processors/DSP               | Multimedia; NEON™ MPE                                                              |

| RAM Controllers                 | SDRAM, SRAM                                                                        |

| Graphics Acceleration           | Yes                                                                                |

| Display & Interface Controllers | DVD, VDC                                                                           |

| Ethernet                        | 10/100Mbps (1), 100Mbps (1)                                                        |

| SATA                            | -                                                                                  |

| USB                             | USB 2.0 (2)                                                                        |

| Voltage - I/O                   | 1.2V, 3.3V                                                                         |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                                  |

| Security Features               | -                                                                                  |

| Package / Case                  | 256-LQFP                                                                           |

| Supplier Device Package         | 256-LQFP (28x28)                                                                   |

| Purchase URL                    | https://www.e-xfl.com/product-detail/renesas-electronics-america/r7s721000vlfp-aa0 |

|                                 |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

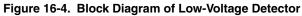

# 3.4.2 Wraparound of CPU address space

#### (1) Program space

Of the 32 bits of the program counter (PC), the higher 6 bits are fixed to 0 and only the lower 26 bits are valid. Even if a carry or borrow occurs from bit 25 to bit 26 as a result of branch address calculation, the higher 6 bits ignore this and remain 0.

Therefore, the upper-limit address of the program space, 03FFFFFH, and the lower-limit address, 00000000H, are contiguous addresses, and the program space is wrapped around at the boundary of these addresses.

Caution No instructions can be fetched from the 4 KB area of 03FFF000H to 03FFFFFFH because this area is an on-chip peripheral I/O area. Therefore, do not execute any branch operation instructions in which the destination address will reside in any part of this area.

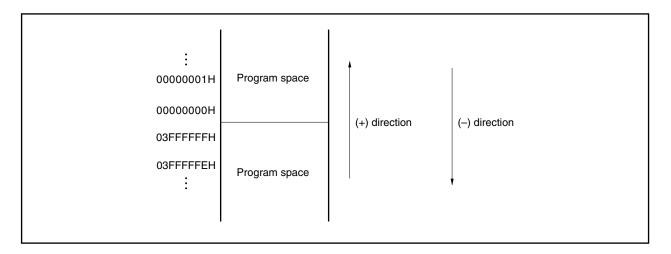

#### (2) Data space

The result of an operand address calculation that exceeds 32 bits is ignored.

Therefore, the upper-limit address of the data space, FFFFFFFH, and the lower-limit address, 00000000H, are contiguous addresses, and the data space is wrapped around at the boundary of these addresses.

# (1) Registers

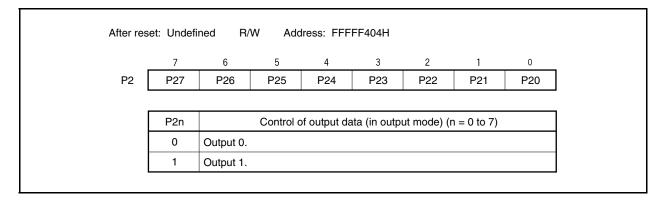

# (a) Port 2 register (P2)

# (b) Port 2 mode register (PM2)

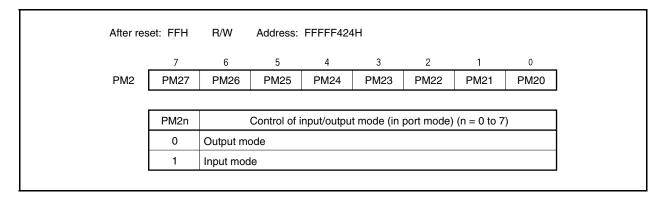

Figure 4-15. Block Diagram of P32 Pin

# CHAPTER 6 16-BIT TIMER/EVENT COUNTER P (TMP)

Timer P (TMP) is a 16-bit timer/event counter. The V850ES/IE2 incorporates TMP0 to TMP3.

# 6.1 Overview

The TMPn of channels are outlined below (n = 0 to 3).

| Item                                           | TMP0   | TMP1              | TMP2   | TMP3              |

|------------------------------------------------|--------|-------------------|--------|-------------------|

| Clock selection                                | 8 ways | 8 ways            | 8 ways | 8 ways            |

| Capture trigger input pin                      | 2      | None              | 2      | None              |

| External event count input pin                 | 1      | None              | 1      | None              |

| External trigger input pin                     | 1      | None              | 1      | None              |

| Timer counter                                  | 1      | 1                 | 1      | 1                 |

| Capture/compare register                       | 2      | 2 <sup>Note</sup> | 2      | 2 <sup>Note</sup> |

| Capture/compare match interrupt request signal | 2      | 2 <sup>Note</sup> | 2      | 2 <sup>Note</sup> |

| Overflow interrupt request signal              | 1      | 1                 | 1      | 1                 |

| Timer output pin                               | 2      | None              | 1      | 1                 |

# Table 6-1. TMPn Overview

#### **Note** Compare function only

# 6.2 Functions

The functions of TMPn that can be realized differ from one channel to another, as shown in the table below (n = 0 to 3).

| Function                      | TMP0         | TMP1            | TMP2         | TMP3          |

|-------------------------------|--------------|-----------------|--------------|---------------|

| Interval timer                | $\checkmark$ | $\checkmark$    | $\checkmark$ | $\checkmark$  |

| External event counter        | $\checkmark$ | ×               | $\checkmark$ | ×             |

| External trigger pulse output | $\checkmark$ | ×               | $\checkmark$ | $\sqrt{Note}$ |

| One-shot pulse output         | $\checkmark$ | ×               | $\checkmark$ | $\sqrt{Note}$ |

| PWM output                    | $\checkmark$ | ×               | $\checkmark$ |               |

| Free-running timer            | $\checkmark$ |                 | $\checkmark$ |               |

| Pulse width measurement       | $\checkmark$ | ×               | $\checkmark$ | ×             |

| Timer tuning operation        | ×            | $\sqrt{(TMQ1)}$ | ×            | ×             |

#### Table 6-2. TMPn Functions

Note Realized by software trigger only. External trigger input cannot be used.

# (6) TMPn option register 0 (TPnOPT0)

The TPnOPT0 register is an 8-bit register that sets the capture/compare operation and detects overflow. This register can be read or written in 8-bit or 1-bit units. Reset sets this register to 00H.

| <b>A</b> (1    |                                                                                                | DAA                                                                                                                             | <b>A</b> al al a a a a                                                                                                             | TROOPTO                                                                                                                                                                                       |                                                                                                                    |                                                                                                                              |                                                                                      |                                                                              |  |  |

|----------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|

| After re       | eset: 00H                                                                                      | R/W                                                                                                                             | Address:                                                                                                                           |                                                                                                                                                                                               |                                                                                                                    | 645H, TP1C                                                                                                                   |                                                                                      |                                                                              |  |  |

|                | 7                                                                                              | 6                                                                                                                               | 5                                                                                                                                  | 1P2OP10<br>4                                                                                                                                                                                  | 3                                                                                                                  | 385H, TP3C                                                                                                                   |                                                                                      | -FF6A5H<br><0>                                                               |  |  |

| TPnOPT0        | 7                                                                                              | 0                                                                                                                               | TPkCCS1 <sup>№t</sup>                                                                                                              |                                                                                                                                                                                               | 0                                                                                                                  | 2                                                                                                                            | 1                                                                                    | TPnOVF                                                                       |  |  |

| (n = 0  to  3, |                                                                                                | Ū                                                                                                                               | 1110001                                                                                                                            | IT NOODD                                                                                                                                                                                      | 0                                                                                                                  | 0                                                                                                                            |                                                                                      |                                                                              |  |  |

| k = 0, 2       | TPkCCS1 <sup>Note</sup>                                                                        |                                                                                                                                 | TPkC                                                                                                                               | CR1 register                                                                                                                                                                                  | capture/                                                                                                           | compare se                                                                                                                   | election                                                                             |                                                                              |  |  |

| - , ,          | 0                                                                                              |                                                                                                                                 | e register s                                                                                                                       |                                                                                                                                                                                               |                                                                                                                    |                                                                                                                              |                                                                                      |                                                                              |  |  |

|                | 1                                                                                              |                                                                                                                                 |                                                                                                                                    |                                                                                                                                                                                               |                                                                                                                    |                                                                                                                              |                                                                                      |                                                                              |  |  |

|                | The TPk                                                                                        | The TPkCCS1 bit setting is valid only in the free-running timer mode.                                                           |                                                                                                                                    |                                                                                                                                                                                               |                                                                                                                    |                                                                                                                              |                                                                                      |                                                                              |  |  |

|                | L                                                                                              |                                                                                                                                 |                                                                                                                                    |                                                                                                                                                                                               |                                                                                                                    |                                                                                                                              |                                                                                      |                                                                              |  |  |

|                | TPkCCS0 <sup>Note</sup>                                                                        |                                                                                                                                 | TPkC                                                                                                                               | CR0 register                                                                                                                                                                                  | capture/                                                                                                           | compare se                                                                                                                   | election                                                                             |                                                                              |  |  |

|                | 0                                                                                              | Compare                                                                                                                         | e register s                                                                                                                       | elected                                                                                                                                                                                       |                                                                                                                    |                                                                                                                              |                                                                                      |                                                                              |  |  |

|                | 1                                                                                              | Capture                                                                                                                         | register sel                                                                                                                       | ected (cleare                                                                                                                                                                                 | ed by TPI                                                                                                          | CTL0.TPk                                                                                                                     | CE bit = 0                                                                           | ))                                                                           |  |  |

|                | The TPk                                                                                        | CCS0 bit s                                                                                                                      | setting is va                                                                                                                      | alid only in th                                                                                                                                                                               | e free-rur                                                                                                         | nning timer i                                                                                                                | mode.                                                                                |                                                                              |  |  |

|                |                                                                                                |                                                                                                                                 |                                                                                                                                    |                                                                                                                                                                                               |                                                                                                                    |                                                                                                                              |                                                                                      |                                                                              |  |  |

|                | TPr                                                                                            | TPnOVF TMPn overflow detection flag                                                                                             |                                                                                                                                    |                                                                                                                                                                                               |                                                                                                                    |                                                                                                                              |                                                                                      |                                                                              |  |  |

|                | Set (1)                                                                                        |                                                                                                                                 | Overflow                                                                                                                           | occurred                                                                                                                                                                                      |                                                                                                                    |                                                                                                                              |                                                                                      |                                                                              |  |  |

|                | Reset (0)                                                                                      | )                                                                                                                               | 0 written                                                                                                                          | to TPnOVF                                                                                                                                                                                     | bit or TP                                                                                                          | nCTL0.TPn                                                                                                                    | CE bit = 0                                                                           | )                                                                            |  |  |

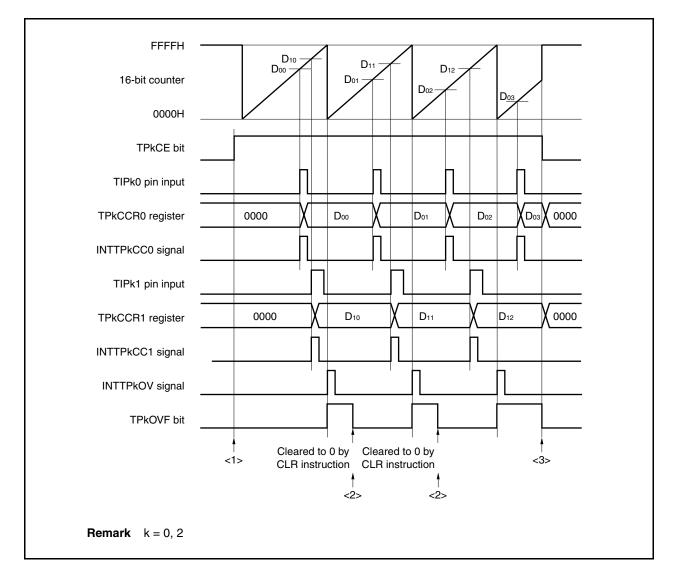

|                | to 0000<br>An over<br>that the<br>other th<br>The TF<br>registe<br>Before<br>sure to<br>The TF | DH in the fir<br>erflow inter-<br>e TPnOVF<br>han the fre<br>PnOVF bit<br>r is read w<br>clearing th<br>confirm (b<br>PnOVF bit | ree-running<br>rupt reques<br>bit is set to<br>ee-running<br>is not clear<br>then the TF<br>ne TPnOVF<br>by reading)<br>can be bot | when the 16-<br>g timer mode<br>at signal (INT<br>o 1. The INT<br>timer mode a<br>red to 0 even<br>PnOVF bit =<br><sup>5</sup> bit to 0 afte<br>that the TPr<br>h read and w<br>has no effect | or the pu<br>TPnOV)<br>TPnOV s<br>and the pu<br>when the<br>when the<br>1.<br>r generat<br>pOVF bit<br>written, bu | Ilse width m<br>is generated<br>signal is not<br>ulse width m<br>e TPnOVF t<br>ion of the IN<br>is set to 1.<br>it the TPnOV | easurem<br>d at the s<br>generate<br>neasurem<br>bit or the<br>NTTPnOV<br>VF bit car | ent mode.<br>ame time<br>d in modes<br>nent mode.<br>TPnOPT0<br>/ signal, be |  |  |

|                | the TPkC                                                                                       | CS1 and<br>FPkCE bi                                                                                                             | TPkCCS<br>it = 1.) If                                                                                                              | 0 bits whe                                                                                                                                                                                    | n the Tl                                                                                                           | PkCE bit =                                                                                                                   | = 0. (Th                                                                             |                                                                              |  |  |

| 2. Be sure     | to clear b                                                                                     | its 1 to 3                                                                                                                      | , 6, and 7                                                                                                                         | to "0".                                                                                                                                                                                       |                                                                                                                    |                                                                                                                              |                                                                                      |                                                                              |  |  |

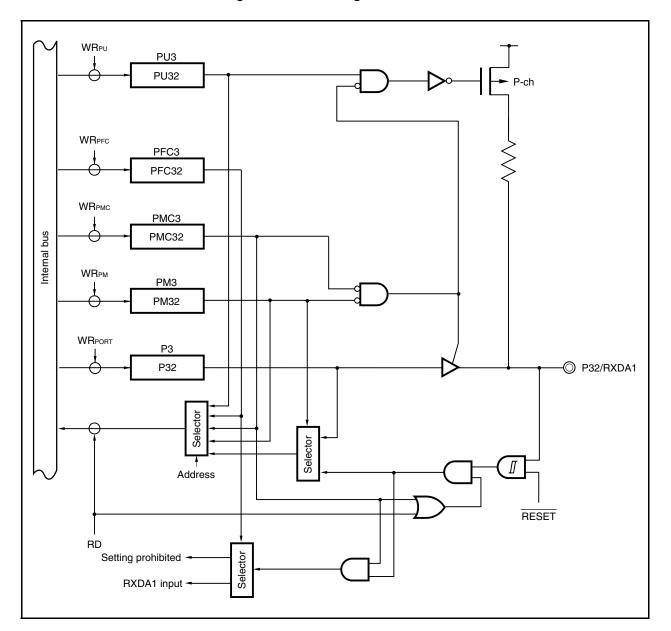

# (b) Operation if TPnCCR0 register is set to FFFFH

If the TPnCCR0 register is set to FFFFH, the 16-bit counter counts up to FFFFH. The counter is cleared to 0000H in synchronization with the next count-up timing. The INTTPnCC0 signal is generated and the output of the TOP00 pin is inverted. At this time, an overflow interrupt request signal (INTTPnOV) is not generated, nor is the overflow flag (TPnOPT0.TPnOVF bit) set to 1.

(d) Operation of TPnCCR1 register

# 6.6.5 PWM output mode (TPmMD2 to TPmMD0 bits = 100)

This mode is valid only in TMP0, TMP2, and TMP3.

In the PWM output mode, a PWM waveform is output from the TOPm1 pin when the TPmCTL0.TPmCE bit is set to 1.

In addition, a PWM waveform with a duty factor of 50% with the set value of the TPmCCR0 register + 1 as half its cycle is output from the TOP00 pin.

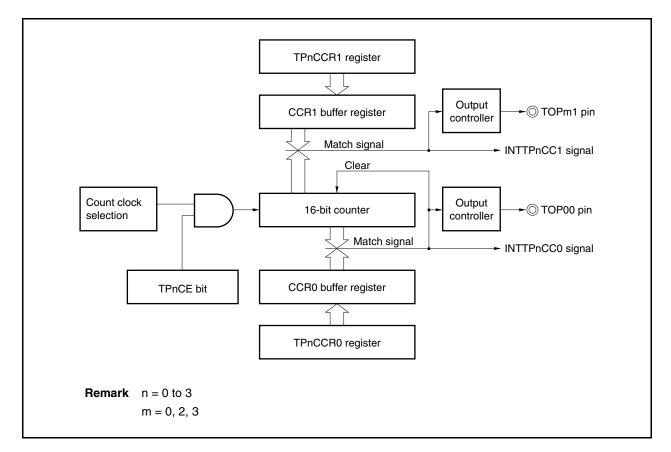

Figure 6-31. Configuration in PWM Output Mode

# (b) When using capture/compare register as capture register

# Figure 6-40. Software Processing Flow in Free-Running Timer Mode (Capture Function) (1/2)

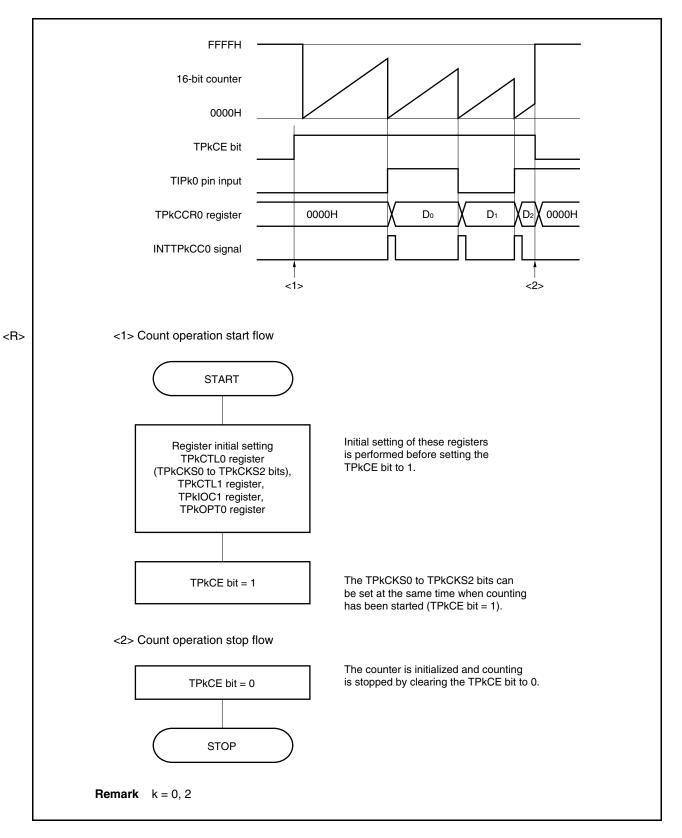

# (1) Operation flow in pulse width measurement mode

Figure 6-44. Software Processing Flow in Pulse Width Measurement Mode

- Cautions 2. Rewrite the TQnOLm and TQnOEm bits when the TQnCTL0.TQnCE bit = 0. (The same value can be written when the TQnCE bit = 1.) If rewriting was mistakenly performed, clear (0) the TQnCE bit and then set the bits again.

- 3. If the TQnOLm bit is manipulated when the TQnCE and TQnOE bits are 0, the output level of the TOQnm, TOQH0b, and TOQ1Tb pins changes.

- 4. To generate the TOQ1Tb pin output and the A/D conversion start trigger signal of A/D converters 0 and 1 in the 6-phase PWM output mode, be sure to set the TOQ1Tb pin output mode using the TQ1IOC0 register. At this time, be sure to clear the TQ1OL0 bit to 0 and set the TQ1OE0 bit to 1 (b = 1 to 3).

# 7.6 Operation

The functions that can be realized differ between TMQ0 and TMQ1. The functions of each channel are shown below.

| Operation                          | TQ0CTL1.TQ0EST Bit<br>(Software Trigger Bit) | Capture/Compare Register<br>Setting | Compare Register Write<br>Method |

|------------------------------------|----------------------------------------------|-------------------------------------|----------------------------------|

| Interval timer mode                | Invalid                                      | Compare only                        | Anytime write                    |

| External event count mode          | Invalid                                      | Compare only                        | Anytime write                    |

| External trigger pulse output mode | Valid                                        | Compare only                        | Batch write                      |

| One-shot pulse output mode         | Valid                                        | Compare only                        | Anytime write                    |

| PWM output mode                    | Invalid                                      | Compare only                        | Batch write                      |

| Free-running timer mode            | Invalid                                      | Switchable                          | Anytime write                    |

| Pulse width measurement mode       | Invalid                                      | Capture only                        | Not applicable                   |

# Table 7-10. TMQ0 Specifications in Each Mode

# Table 7-11. TMQ1 Specifications in Each Mode

| Operation                          | Software Trigger Bit | Capture/Compare Register<br>Setting | Compare Register Write<br>Method |

|------------------------------------|----------------------|-------------------------------------|----------------------------------|

| Interval timer mode                | Invalid              | Compare only                        | Anytime write                    |

| External event count mode          | None                 |                                     |                                  |

| External trigger pulse output mode | None                 |                                     |                                  |

| One-shot pulse output mode         | None                 |                                     |                                  |

| PWM output mode                    | None                 |                                     |                                  |

| Free-running timer mode            | Invalid              | Compare only                        | Anytime write                    |

| Pulse width measurement mode       | None                 |                                     |                                  |

Remark TMQ1 has a function to execute tuning with TMP1. For details, see CHAPTER 9 MOTOR CONTROL FUNCTION.

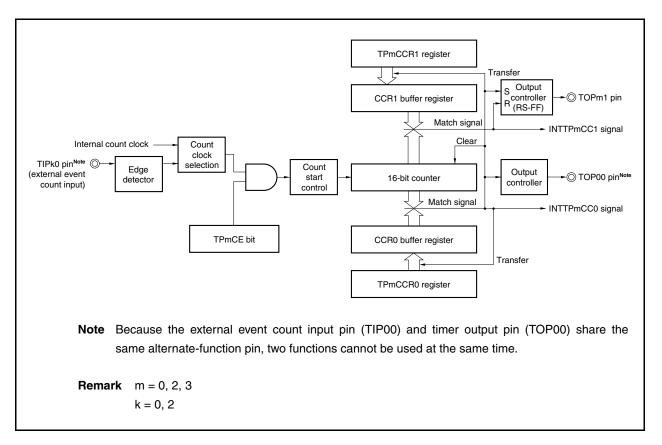

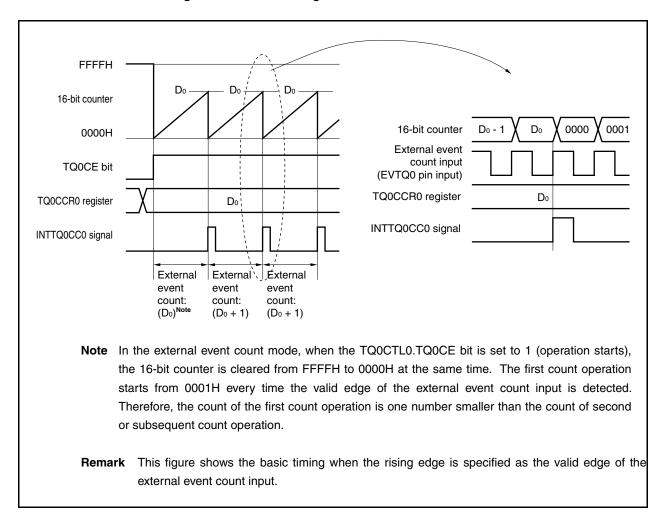

Figure 7-16. Basic Timing in External Event Count Mode

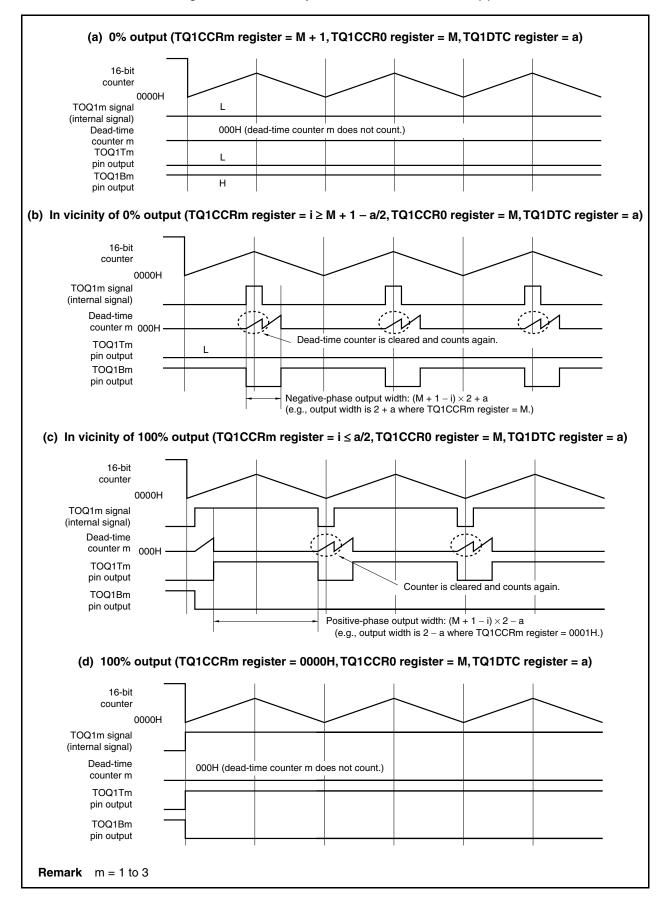

# (b) 0%/100% output of PWM waveform

<R>

To output a 0% waveform, set the TQ0CCRb register to 0000H. The 16-bit counter is cleared to 0000H and the INTTQ0CC0 and INTTQ0CCb signals are generated at the next timing after a match between the count value of the 16-bit counter and the value of the CCR0 buffer register.

| Count clock<br>16-bit counter                                                                           |       | $ \begin{array}{c c} & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & $ | $ \begin{array}{c}                                     $ | <u> </u> |  |  |  |  |

|---------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------|--|--|--|--|

| TQ0CE bit                                                                                               |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>\}</u>                                                |          |  |  |  |  |

| TQ0CCR0 register                                                                                        |       | Do                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Do                                                       |          |  |  |  |  |

| TQ0CCRb register                                                                                        | 0000H | 0000H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0000H                                                    |          |  |  |  |  |

| INTTQ0CC0 signal                                                                                        | (     | Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ( <u></u>                                                | Note     |  |  |  |  |

| INTTQ0CCb signal                                                                                        |       | Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          | Note     |  |  |  |  |

| TOQ0b (TOQH0b) pin output                                                                               |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                          |          |  |  |  |  |

| <b>Note</b> Actually, the timing is delayed by one operating clock (fxx).<br><b>Remark</b> $b = 1$ to 3 |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                          |          |  |  |  |  |

To output a 100% waveform, set a value of (set value of TQ0CCR0 register + 1) to the TQ0CCRb register. If the set value of the TQ0CCR0 register is FFFFH, 100% output cannot be produced.

| Count clock<br>16-bit counter |                         | $\sum_{i=1}^{n} \sum_{i=1}^{n} \sum_{i$ |                    | $\frac{1}{\sqrt{D_0 - 1}}$ | γ 0000 γ |

|-------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------|----------|

| TQ0CE bit                     |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    | ,                          | //_      |

| TQ0CCR0 register              | D                       | ;;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Do                 | Do                         |          |

| TQ0CCRb register              | D_0 + 1                 | \ <u></u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D <sub>0</sub> + 1 | ∑                          |          |

| INTTQ0CC0 signal              |                         | ···                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Note               | ··<br>·                    | Note     |

| INTTQ0CCb signal              | <u> </u>                | ; <del>;</del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    | \ <del></del>              |          |

| TOQ0b (TOQH0b) pin output     |                         | ; <del>;</del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    | 5                          |          |