Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                 |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | V850ES                                                                              |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 20MHz                                                                               |

| Connectivity               | CSI, UART/USART                                                                     |

| Peripherals                | LVD, PWM, WDT                                                                       |

| Number of I/O              | 39                                                                                  |

| Program Memory Size        | 128KB (128K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 6К х 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                         |

| Data Converters            | A/D 8x10b                                                                           |

| Oscillator Type            | External                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 64-LQFP                                                                             |

| Supplier Device Package    | -                                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3714gc-8bs-a |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.2.2 System register set

System registers control the status of the CPU and hold interrupt information.

Read from and write to system registers are performed by setting the system register numbers shown below with the system register load/store instructions (LDSR, STSR instructions).

| System       | System Register Name                                                                          | Operand Specif        | fication Enabled      |

|--------------|-----------------------------------------------------------------------------------------------|-----------------------|-----------------------|

| Register No. |                                                                                               | LDSR<br>Instruction   | STSR<br>Instruction   |

| 0            | Interrupt status saving register (EIPC) <sup>Note 1</sup>                                     | Yes                   | Yes                   |

| 1            | Interrupt status saving register (EIPSW) <sup>Note 1</sup>                                    | Yes                   | Yes                   |

| 2            | NMI status saving register (FEPC)                                                             | Yes                   | Yes                   |

| 3            | NMI status saving register (FEPSW)                                                            | Yes                   | Yes                   |

| 4            | Interrupt source register (ECR)                                                               | No                    | Yes                   |

| 5            | Program status word (PSW)                                                                     | Yes                   | Yes                   |

| 6 to 15      | Reserved numbers for future function expansion (The operation is not guaranteed if accessed.) | No                    | No                    |

| 16           | CALLT execution status saving register (CTPC)                                                 | Yes                   | Yes                   |

| 17           | CALLT execution status saving register (CTPSW)                                                | Yes                   | Yes                   |

| 18           | Exception/debug trap status saving register (DBPC)                                            | Yes <sup>Note 2</sup> | Yes <sup>Note 2</sup> |

| 19           | Exception/debug trap status saving register (DBPSW)                                           | Yes <sup>Note 2</sup> | Yes <sup>Note 2</sup> |

| 20           | CALLT base pointer (CTBP)                                                                     | Yes                   | Yes                   |

| 21 to 31     | Reserved numbers for future function expansion (The operation is not guaranteed if accessed.) | No                    | No                    |

## Table 3-2. System Register Numbers

**Notes 1.** Since only one set of these registers is available, the contents of this register must be saved by the program when multiple interrupt servicing is enabled.

2. Can be accessed only after the DBTRAP instruction or illegal opcode is executed and before the DBRET instruction is executed.

Caution Even if bit 0 of EIPC, FEPC, or CTPC is set (1) by the LDSR instruction, bit 0 is ignored during return with the RETI instruction following interrupt servicing (because bit 0 of PC is fixed to 0). When setting a value to EIPC, FEPC, and CTPC, set an even number (bit 0 = 0).

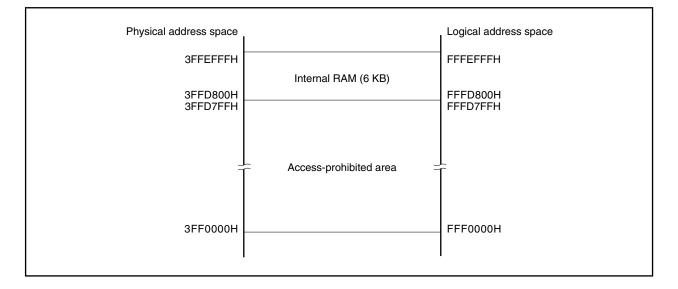

# (2) Internal RAM area

An area of 60 KB maximum from 3FF0000H to 3FFEFFFH is reserved for the internal RAM area. A 6 KB area from 3FFD800H to 3FFEFFFH is provided as physical internal RAM for the V850ES/IE2. Addresses 3FF0000H to 3FFD7FFH are an access-prohibited area.

## Figure 3-6. Internal RAM Area (6 KB)

| Port Name                     | Function                          | PMCmn | PFCEmn | PFCmn | PMmn | Output Data                        | Pmn Read Value | Remark                         |

|-------------------------------|-----------------------------------|-------|--------|-------|------|------------------------------------|----------------|--------------------------------|

| P14                           | Output port                       | 0     | None   | ×     | 0    | Port latch                         | Port latch     |                                |

|                               | Input port                        |       |        |       | 1    | -                                  | Pin level      |                                |

|                               | TOQH03                            | 1     | None   | 0     | 0    | Alternate output                   | Port latch     |                                |

|                               |                                   |       |        |       | 1    | (timer output)                     | Pin level      |                                |

|                               | EVTQ0                             | 1     | None   | 1     | 0    | -                                  | Port latch     | Alternate input (timer input)  |

|                               |                                   |       |        |       | 1    |                                    | Pin level      |                                |

| P16 (CLMER) <sup>Note</sup> , | Output port <sup>Note</sup>       | 0     | None   | ×     | 0    | Port latch                         | Port latch     |                                |

| P17                           | Input port                        |       |        |       | 1    | -                                  | Pin level      |                                |

|                               | TOQ00 (CLMER) <sup>Note</sup> ,   | 1     | None   | 0     | 0    | Alternate output<br>(timer output) | Port latch     |                                |

|                               | TOP21                             |       |        |       | 1    |                                    | Pin level      |                                |

|                               | TIP20, TIP21                      | 1     | None   | 1     | 0    |                                    | Port latch     | Alternate input (timer input)  |

|                               |                                   |       |        |       | 1    |                                    | Pin level      |                                |

| P20 to P27                    | Output port                       | 0     | None   | None  | 0    | Port latch                         | Port latch     |                                |

|                               | Input port                        |       |        |       | 1    | -                                  | Pin level      |                                |

|                               | TOQ1T1 to TOQ1T3,                 | 1     | None   | None  | 0    | Alternate output<br>(timer output) | Port latch     |                                |

|                               | TOQ1B1 to TOQ1B3,<br>TOQ10, TOP31 |       |        |       | 1    |                                    | Pin level      |                                |

| P30                           | Output port                       | 0     | None   | None  | 0    | Port latch                         | Port latch     |                                |

|                               | Input port                        |       |        |       | 1    | -                                  | Pin level      |                                |

|                               | RXDA0                             | 1     | None   | None  | 0    | -                                  | Port latch     | Alternate input (serial input) |

|                               |                                   |       |        |       | 1    |                                    | Pin level      |                                |

| P31                           | Output port                       | 0     | None   | None  | 0    | Port latch                         | Port latch     |                                |

|                               | Input port                        |       |        |       | 1    | -                                  | Pin level      |                                |

|                               | TXDA0                             | 1     | None   | None  | 0    | Alternate output                   | Port latch     |                                |

|                               |                                   |       |        |       | 1    | (serial output)                    | Pin level      |                                |

Table 4-10. Output Data and Port Read Value for Each Setting (2/4)

Note When P16 is set as the output port or TOQ00 output function, if an error (oscillator stop) is detected by the clock monitor, the CLMER signal (low level) is output from P16. Low-level output is released by reset signal. For details, see Table 4-5 Alternate-Function Pins of Port 1.

**Remark** ×: Don't care

User's Manual U17716EJ2V0UD

| Pin Name             | Altern                | ate Pin | Pnx Bit of Pn Register         | PMnx Bit of PMn Register        | PMCnx Bit of     | PFCEnx Bit of  | PFCnx Bit of  | Other Bit  |

|----------------------|-----------------------|---------|--------------------------------|---------------------------------|------------------|----------------|---------------|------------|

|                      | Name                  | I/O     |                                |                                 | PMCn<br>Register | PFCEn Register | PFCn Register | (Register) |

| P43                  | TOP00                 | Output  | P43 = Setting not required     | PM43 = Setting not required     | PMC43 = 1        | -              | PFC43 = 0     |            |

|                      | TIP00                 | Input   | P43 = Setting not required     | PM43 = Setting not required     | PMC43 = 1        | -              | PFC43 = 1     |            |

| P44                  | TOP01                 | Output  | P44 = Setting not required     | PM44 = Setting not required     | PMC44 = 1        | -              | PFC44 = 0     |            |

|                      | TIP01                 | Input   | P44 = Setting not required     | PM44 = Setting not required     | PMC44 = 1        | -              | PFC44 = 1     |            |

| PDL0                 | _                     | _       | PDL0 = Setting not<br>required | PMDL0 = Setting not<br>required | _                | -              | -             |            |

| PDL1                 | -                     | -       | PDL1 = Setting not<br>required | PMDL1 = Setting not<br>required | -                | -              | -             |            |

| PDL2                 | -                     | -       | PDL2 = Setting not<br>required | PMDL2 = Setting not<br>required | -                | -              | -             |            |

| PDL3                 | _                     | -       | PDL3 = Setting not<br>required | PMDL3 = Setting not<br>required | -                | -              | -             |            |

| PDL4                 | _                     | -       | PDL4 = Setting not<br>required | PMDL4 = Setting not<br>required | _                | -              | -             |            |

| PDL5 <sup>Note</sup> | FLMD1 <sup>Note</sup> | Input   | PDL5 = Setting not<br>required | PMDL5 = Setting not<br>required | _                | -              | -             |            |

| PDL6                 | _                     | -       | PDL6 = Setting not<br>required | PMDL6 = Setting not<br>required | _                | -              | -             |            |

| PDL7                 | _                     | _       | PDL7 = Setting not required    | PMDL7 = Setting not<br>required | _                | -              | -             |            |

Note The PDL5 pin also functions as a pin to be set in the flash programming mode (FLMD1). This pin does not need to be manipulated using the port control register. For details, see CHAPTER 18 FLASH MEMORY.

User's Manual U17716EJ2V0UD

# (6) TMPn option register 0 (TPnOPT0)

The TPnOPT0 register is an 8-bit register that sets the capture/compare operation and detects overflow. This register can be read or written in 8-bit or 1-bit units. Reset sets this register to 00H.

| <b>A</b> (1    |                                                                                                | DAA                                                                                                                             | <b>A</b> al al a a a a                                                                                                             | TROOPTO                                                                                                                                                                                       |                                                                                                                    |                                                                                                                              |                                                                                      |                                                                              |  |  |

|----------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|

| After re       | eset: 00H                                                                                      | R/W                                                                                                                             | Address:                                                                                                                           |                                                                                                                                                                                               |                                                                                                                    | 645H, TP1C                                                                                                                   |                                                                                      |                                                                              |  |  |

|                | 7                                                                                              | 6                                                                                                                               | 5                                                                                                                                  | 1P2OP10<br>4                                                                                                                                                                                  | 3                                                                                                                  | 385H, TP3C                                                                                                                   |                                                                                      | -FF6A5H<br><0>                                                               |  |  |

| TPnOPT0        | 7                                                                                              | 0                                                                                                                               | TPkCCS1 <sup>№t</sup>                                                                                                              |                                                                                                                                                                                               | 0                                                                                                                  | 2                                                                                                                            | 1                                                                                    | TPnOVF                                                                       |  |  |

| (n = 0  to  3, |                                                                                                | Ū                                                                                                                               | 1110001                                                                                                                            | IT NO COU                                                                                                                                                                                     | 0                                                                                                                  | 0                                                                                                                            |                                                                                      |                                                                              |  |  |

| k = 0, 2       | TPkCCS1 <sup>Note</sup>                                                                        |                                                                                                                                 | TPkC                                                                                                                               | CR1 register                                                                                                                                                                                  | capture/                                                                                                           | compare se                                                                                                                   | election                                                                             |                                                                              |  |  |

| - , ,          | 0                                                                                              |                                                                                                                                 | ompare register selected<br>apture register selected (cleared by TPkCTL0.TPkCE bit = 0)                                            |                                                                                                                                                                                               |                                                                                                                    |                                                                                                                              |                                                                                      |                                                                              |  |  |

|                | 1                                                                                              |                                                                                                                                 |                                                                                                                                    |                                                                                                                                                                                               |                                                                                                                    |                                                                                                                              |                                                                                      |                                                                              |  |  |

|                | The TPk                                                                                        | CCS1 bit s                                                                                                                      | setting is va                                                                                                                      | lid only in th                                                                                                                                                                                | e free-rur                                                                                                         | nning timer i                                                                                                                | mode.                                                                                | <u>,</u>                                                                     |  |  |

|                | L                                                                                              |                                                                                                                                 |                                                                                                                                    |                                                                                                                                                                                               |                                                                                                                    |                                                                                                                              |                                                                                      |                                                                              |  |  |

|                | TPkCCS0 <sup>Note</sup>                                                                        |                                                                                                                                 | TPkC                                                                                                                               | CR0 register                                                                                                                                                                                  | capture/                                                                                                           | compare se                                                                                                                   | election                                                                             |                                                                              |  |  |

|                | 0                                                                                              | Compare                                                                                                                         | e register s                                                                                                                       | elected                                                                                                                                                                                       |                                                                                                                    |                                                                                                                              |                                                                                      |                                                                              |  |  |

|                | 1                                                                                              |                                                                                                                                 |                                                                                                                                    |                                                                                                                                                                                               |                                                                                                                    |                                                                                                                              |                                                                                      |                                                                              |  |  |

|                | The TPk                                                                                        | The TPkCCS0 bit setting is valid only in the free-running timer mode.                                                           |                                                                                                                                    |                                                                                                                                                                                               |                                                                                                                    |                                                                                                                              |                                                                                      |                                                                              |  |  |

|                |                                                                                                |                                                                                                                                 |                                                                                                                                    |                                                                                                                                                                                               |                                                                                                                    |                                                                                                                              |                                                                                      |                                                                              |  |  |

|                | TPr                                                                                            | TPnOVF TMPn overflow detection flag                                                                                             |                                                                                                                                    |                                                                                                                                                                                               |                                                                                                                    |                                                                                                                              |                                                                                      |                                                                              |  |  |

|                | Set (1)                                                                                        | Overflow occurred                                                                                                               |                                                                                                                                    |                                                                                                                                                                                               |                                                                                                                    |                                                                                                                              |                                                                                      |                                                                              |  |  |

|                | Reset (0)                                                                                      | )                                                                                                                               | 0 written                                                                                                                          | to TPnOVF                                                                                                                                                                                     | bit or TP                                                                                                          | nCTL0.TPn                                                                                                                    | CE bit = 0                                                                           | )                                                                            |  |  |

|                | to 0000<br>An over<br>that the<br>other th<br>The TF<br>registe<br>Before<br>sure to<br>The TF | DH in the fir<br>erflow inter-<br>e TPnOVF<br>han the fre<br>PnOVF bit<br>r is read w<br>clearing th<br>confirm (b<br>PnOVF bit | ree-running<br>rupt reques<br>bit is set to<br>ee-running<br>is not clear<br>then the TF<br>ne TPnOVF<br>by reading)<br>can be bot | when the 16-<br>g timer mode<br>at signal (INT<br>o 1. The INT<br>timer mode a<br>red to 0 even<br>PnOVF bit =<br><sup>5</sup> bit to 0 afte<br>that the TPr<br>h read and w<br>has no effect | or the pu<br>TPnOV)<br>TPnOV s<br>and the pu<br>when the<br>when the<br>1.<br>r generat<br>pOVF bit<br>written, bu | Ilse width m<br>is generater<br>signal is not<br>ulse width m<br>e TPnOVF t<br>ion of the IN<br>is set to 1.<br>it the TPnOV | easurem<br>d at the s<br>generate<br>neasurem<br>bit or the<br>NTTPnOV<br>VF bit car | ent mode.<br>ame time<br>d in modes<br>nent mode.<br>TPnOPT0<br>/ signal, be |  |  |

|                | the TPkC                                                                                       | CS1 and<br>FPkCE bi                                                                                                             | TPkCCS<br>it = 1.) If                                                                                                              | 0 bits whe                                                                                                                                                                                    | n the Tl                                                                                                           | PkCE bit =                                                                                                                   | = 0. (Th                                                                             |                                                                              |  |  |

| 2. Be sure     | to clear b                                                                                     | its 1 to 3                                                                                                                      | , 6, and 7                                                                                                                         | to "0".                                                                                                                                                                                       |                                                                                                                    |                                                                                                                              |                                                                                      |                                                                              |  |  |

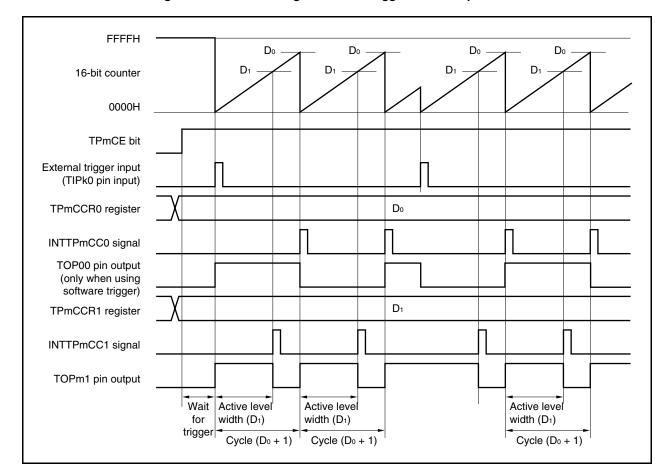

Figure 6-24. Basic Timing in External Trigger Pulse Output Mode

16-bit timer/event counter P waits for a trigger when the TPmCE bit is set to 1. When the trigger is generated, the 16-bit counter is cleared from FFFFH to 0000H, starts counting at the same time, and outputs a PWM waveform from the TOPm1 pin. If the trigger is generated again while the counter is operating, the counter is cleared to 0000H and restarted. (The output of the TOP00 pin is inverted. The TOPm1 pin outputs high level regardless of the status (high/low) when a trigger occurs.)

<R>

<R>

The active level width, cycle, and duty factor of the PWM waveform can be calculated as follows.

Active level width = (Set value of TPmCCR1 register) × Count clock cycle Cycle = (Set value of TPmCCR0 register + 1) × Count clock cycle Duty factor = (Set value of TPmCCR1 register)/(Set value of TPmCCR0 register + 1)

The compare match interrupt request signal INTTPmCC0 is generated when the 16-bit counter counts next time after its count value matches the value of the CCR0 buffer register, and the 16-bit counter is cleared to 0000H. The compare match interrupt request signal INTTPmCC1 is generated when the count value of the 16-bit counter matches the value of the CCR1 buffer register.

The value set to the TPmCCRa register is transferred to the CCRa buffer register when the count value of the 16bit counter matches the value of the CCRa buffer register and the 16-bit counter is cleared to 0000H.

The valid edge of an external trigger input (TIPk0) or setting the software trigger (TPmCTL1.TPmEST bit) to 1 is used as the trigger.

**Remark** m = 0, 2, 3 k = 0, 2 a = 0, 1

### (2) External trigger pulse output mode operation timing

## (a) Note on changing pulse width during operation

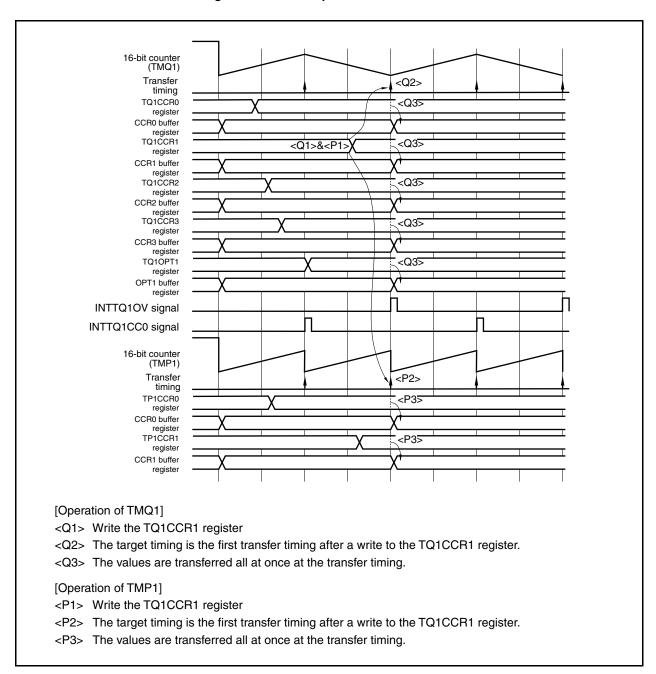

To change the PWM waveform while the counter is operating, write the TPmCCR1 register last. Rewrite the TPmCCRa register after writing the TPmCCR1 register after the INTTPmCC0 signal is detected.

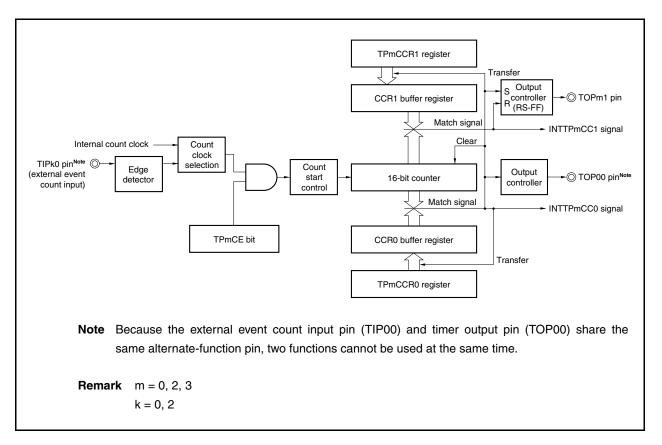

### 6.6.5 PWM output mode (TPmMD2 to TPmMD0 bits = 100)

This mode is valid only in TMP0, TMP2, and TMP3.

In the PWM output mode, a PWM waveform is output from the TOPm1 pin when the TPmCTL0.TPmCE bit is set to 1.

In addition, a PWM waveform with a duty factor of 50% with the set value of the TPmCCR0 register + 1 as half its cycle is output from the TOP00 pin.

Figure 6-31. Configuration in PWM Output Mode

## (c) Generation timing of compare match interrupt request signal (INTTPmCC1)

The timing of generation of the INTTPmCC1 signal in the PWM output mode differs from the timing of INTTPmCC1 signals in other modes; the INTTPmCC1 signal is generated when the count value of the 16bit counter matches the value of the TPmCCR1 register.

| Count clock            |                                |                      |

|------------------------|--------------------------------|----------------------|

| 16-bit counter         | D1 - 2 D1 - 1                  | D1 D1 + 1 D1 + 2     |

| TPmCCR1 register       |                                | D1                   |

| TOPm1 pin output       |                                | Note                 |

| INTTPmCC1 signal       |                                | Note                 |

| Note Actually, the     | e timing is delayed by one ope | erating clock (fxx). |

| <b>Remark</b> m = 0, 2 | 2, 3                           |                      |

Usually, the INTTPmCC1 signal is generated in synchronization with the next counting up after the count value of the 16-bit counter matches the value of the TPmCCR1 register.

In the PWM output mode, however, it is generated one clock earlier. This is because the timing is changed to match the change timing of the output signal of the TOPm1 pin.

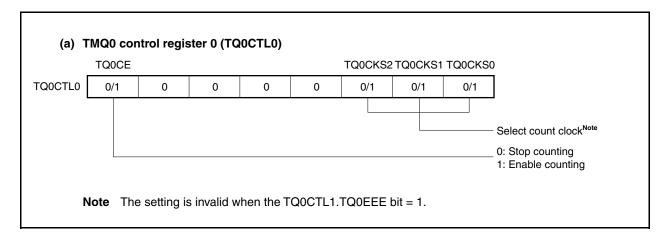

(2) Operation timing in external event count mode

<R>

- Cautions 1. In the external event count mode, the TQ0CCR0 to TQ0CCR3 registers must not be cleared to 0000H.

- In the external event count mode, use of the timer output (TOQ00 to TOQ03) is disabled. If using timer output (TOQ00 to TOQ03) with external event count input (EVTQ0), set the interval timer mode, and enable the count clock operation with the external event count input (TQ0CTL1.TQ0EEE bit = 1) (see 7.6.1 (3) Operation by external event count input (EVTQ0)).

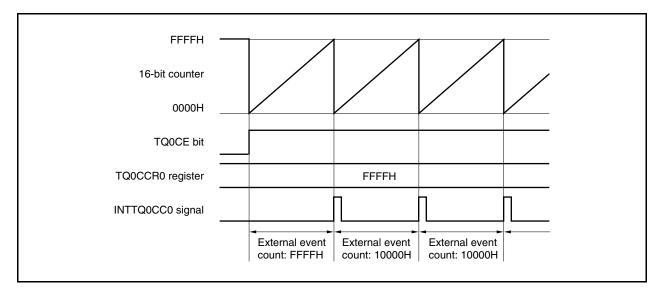

### (a) Operation if TQ0CCR0 register is set to FFFFH

If the TQ0CCR0 register is set to FFFFH, the 16-bit counter counts to FFFFH each time the valid edge of the external event count signal has been detected. The 16-bit counter is cleared to 0000H in synchronization with the next count-up timing, and the INTTQ0CC0 signal is generated. At this time, the TQ0OPT0.TQ0OVF bit is not set.

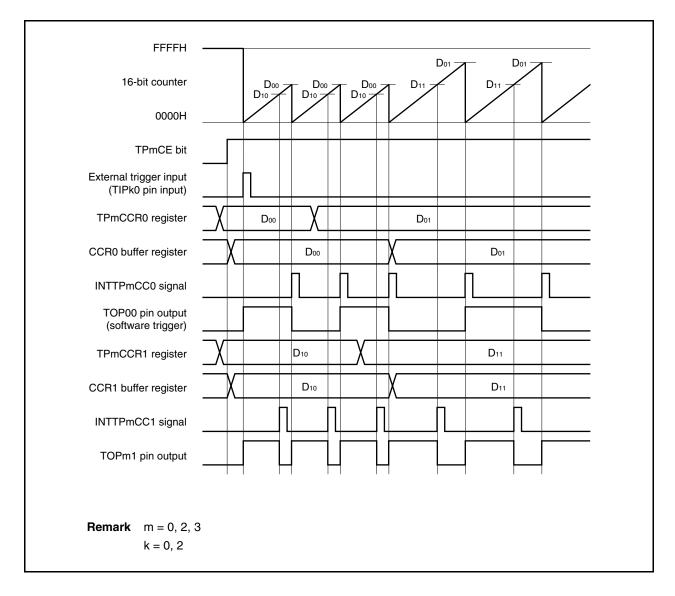

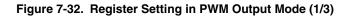

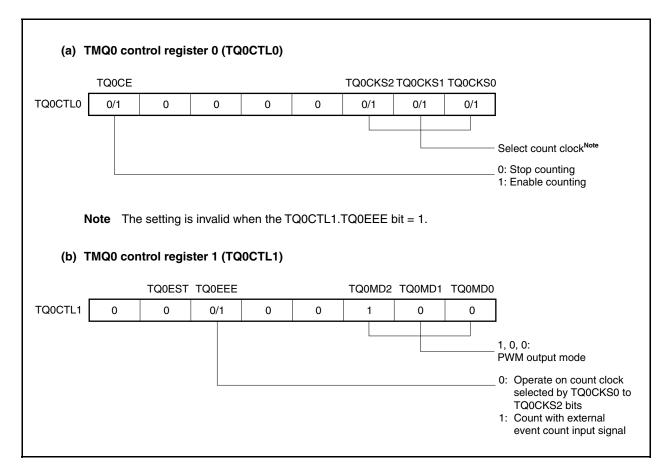

16-bit timer/event counter Q waits for a trigger when the TQ0CE bit is set to 1. When the trigger is generated, the 16-bit counter is cleared from FFFFH to 0000H, starts counting at the same time, and outputs a PWM waveform from the TOQ0b pin. If the trigger is generated again while the counter is operating, the counter is cleared to 0000H and restarted. (The output of the TOQ00 pin is inverted. The TOQ0b pin outputs high level regardless of the status (high/low) when a trigger occurs.)

The active level width, cycle, and duty factor of the PWM waveform can be calculated as follows.

Active level width = (Set value of TQ0CCRb register) × Count clock cycle Cycle = (Set value of TQ0CCR0 register + 1) × Count clock cycle Duty factor = (Set value of TQ0CCRb register)/(Set value of TQ0CCR0 register + 1)

The compare match interrupt request signal INTTQ0CC0 is generated when the 16-bit counter counts next time after its count value matches the value of the CCR0 buffer register, and the 16-bit counter is cleared to 0000H. The compare match interrupt request signal INTTQ0CCb is generated when the count value of the 16-bit counter matches the value of the CCRb buffer register.

The value set to the TQ0CCRa register is transferred to the CCRa buffer register when the count value of the 16-bit counter matches the value of the CCRa buffer register and the 16-bit counter is cleared to 0000H.

Only setting the software trigger (TQ0CTL1.TQ0EST bit) to 1 is used as the trigger.

**Remark** a = 0 to 3 b = 1 to 3

#### Figure 7-24. Setting of Registers in External Trigger Pulse Output Mode (1/3)

When the TQ0CE bit is set to 1, the 16-bit counter is cleared from FFFFH to 0000H, starts counting, and outputs PWM waveform from the TOQ0b pin (TOQH0b).

The active level width, cycle, and duty factor of the PWM waveform can be calculated as follows.

Active level width = (Set value of TQ0CCRb register)  $\times$  Count clock cycle Cycle = (Set value of TQ0CCR0 register + 1)  $\times$  Count clock cycle Duty factor = (Set value of TQ0CCRb register)/(Set value of TQ0CCR0 register + 1)

The PWM waveform can be changed by rewriting the TQ0CCRa register while the counter is operating. The newly written value is reflected when the count value of the 16-bit counter matches the value of the CCR0 buffer register and the 16-bit counter is cleared to 0000H.

The compare match interrupt request signal INTTQ0CC0 is generated when the 16-bit counter counts next time after its count value matches the value of the CCR0 buffer register, and the 16-bit counter is cleared to 0000H. The compare match interrupt request signal INTTQ0CCb is generated when the count value of the 16-bit counter matches the value of the CCRb buffer register.

**Remark** a = 0 to 3 b = 1 to 3

When performing an interval operation in the free-running timer mode, two intervals can be set with one channel.

To perform the interval operation, the value of the corresponding TQnCCRa register must be re-set in the interrupt servicing that is executed when the INTTQnCCa signal is detected.

The set value for re-setting the TQnCCRa register can be calculated by the following expression, where " $D_a$ " is the interval period.

Compare register default value:  $D_a - 1$

Value set to compare register second and subsequent time: Previous set value +  $D_a$

(If the calculation result is greater than FFFFH, subtract 10000H from the result and set this value to the register.)

**Remark** n = 0, 1a = 0 to 3

Figure 9-26. Basic Operation in Batch Mode

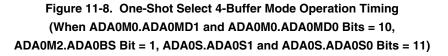

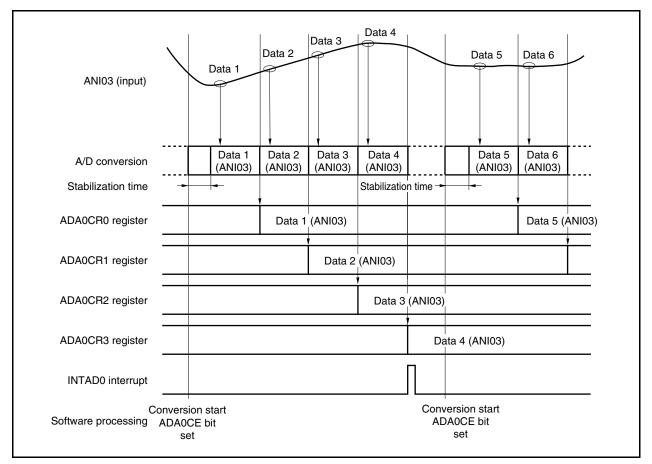

### • 4-buffer mode

In this mode the voltage of one analog input pin (ANInm) is A/D converted four times and the results are stored in the ADAnCRm register. The A/Dn conversion end interrupt request signal (INTADn) is generated when the four A/D conversions end. After end of A/D conversion, the conversion operation is stopped.

**Remark** n = 0, 1, m = 0 to 3

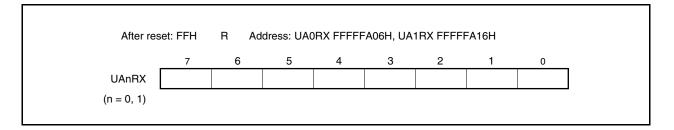

## (6) UARTAn receive data register (UAnRX)

The UAnRX register is an 8-bit buffer register that stores parallel data converted by the UARTAn receive shift register.

The data stored in the UARTAn receive shift register is transferred to the UAnRX register upon end of reception of 1 byte of data. A reception end interrupt request signal (INTUAnR) is generated at this timing.

During LSB-first reception when the data length has been specified as 7 bits, the receive data is transferred to bits 6 to 0 of the UAnRX register and the MSB always becomes 0. During MSB-first reception, the receive data is transferred to bits 7 to 1 of the UAnRX register and the LSB always becomes 0.

When an overrun error occurs (UAnSTR.UAnOVE bit = 1), the receive data at this time is not transferred to the UAnRX register and is discarded.

This register is read-only, in 8-bit units.

In addition to reset, the UAnRX register can be set to FFH by clearing the UAnCTL0.UAnPWR bit to 0.

### (7) UARTAn transmit data register (UAnTX)

The UAnTX register is an 8-bit register used to set transmit data.

Transmission starts when transmit data is written to the UAnTX register in the transmission enabled status (UAnCTL0.UAnTXE bit = 1). When the data of the UAnTX register has been transferred to the UARTAn transmit shift register, the transmission enable interrupt request signal (INTUAnT) is generated.

This register can be read or written in 8-bit units.

Reset sets this register to FFH.

| After rese | et: FFH | R/W | Address: l | JA0TX FFF | FFA07H, l | JA1TX FFF | FFA17H |   |

|------------|---------|-----|------------|-----------|-----------|-----------|--------|---|

| -          | 7       | 6   | 5          | 4         | 3         | 2         | 1      | 0 |

| UAnTX      |         |     |            |           |           |           |        |   |

| (n = 0, 1) |         |     |            |           |           |           |        |   |

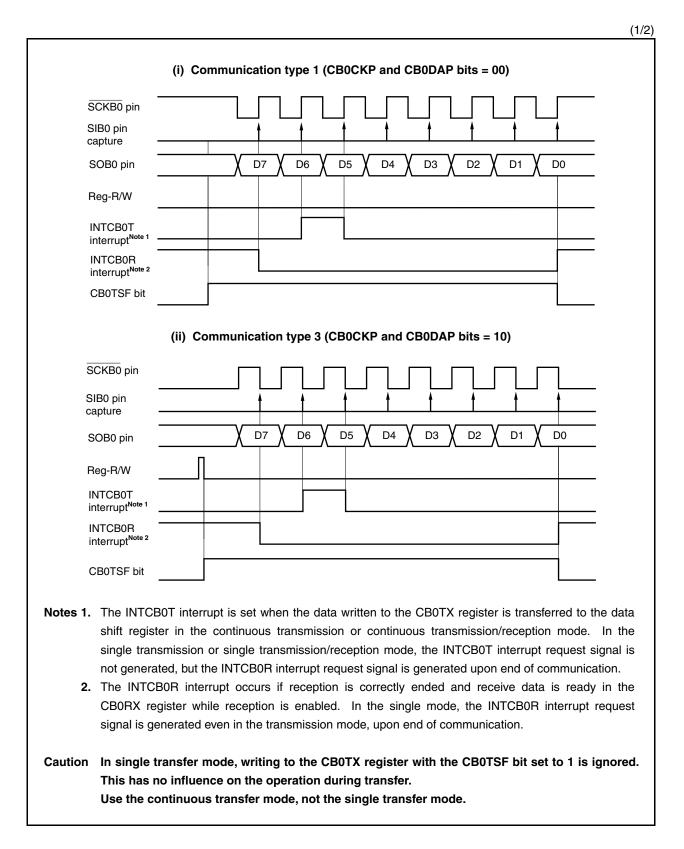

## 13.4.14 Clock timing

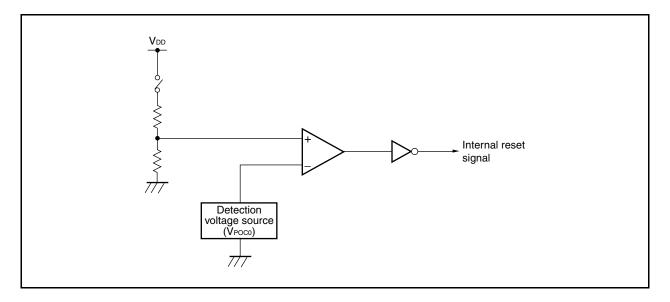

## 16.3.4 Power-on-clear circuit (POC)

# (1) Overview

An overview of the power-on-clear (POC) circuit is shown below.

- Generates a reset signal upon power application.

- Compares the supply voltage (V<sub>DD</sub>) and detection voltage (V<sub>POC0</sub>), and generates a reset signal when V<sub>DD</sub> < V<sub>POC0</sub>.

# (2) Configuration

The block diagram is shown below.

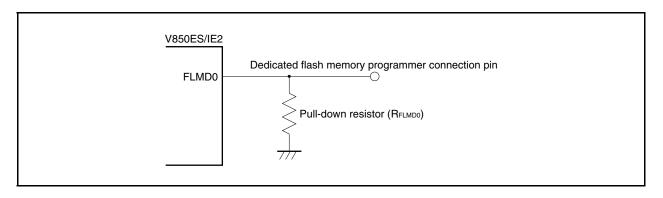

### 18.4.6 Pin connection

When performing on-board writing, mount a connector on the target system to connect to the dedicated flash memory programmer. Also, incorporate a function on-board to switch from the normal operation mode to the flash memory programming mode.

In the flash memory programming mode, all the pins not used for flash memory programming become the same status as that immediately after reset. Therefore, pin handling is required when the external device does not acknowledge the status immediately after a reset.

## (1) FLMD0 pin

In the normal operation mode, input a voltage of Vss level to the FLMD0 pin. In the flash memory programming mode, supply a write voltage of  $V_{DD}$  level to the FLMD0 pin.

Because the FLMD0 pin serves as a write protection pin in the self programming mode ( $\mu$ PD70F3714 only), a voltage of V<sub>DD</sub> level must be supplied to the FLMD0 pin via port control, etc., before writing to the flash memory. For details, see **18.5.5 (1)** FLMD0 pin.

### Figure 18-10. FLMD0 Pin Connection Example

- Cautions 1. Do not directly connect the output (or I/O) pins of IC products to each other, or to V<sub>DD</sub>, EV<sub>DD</sub>, and GND. Open-drain pins or open-collector pins, however, can be directly connected to each other. Direct connection of the output pins between an IC product and an external circuit is possible, if the output pins can be set to the high-impedance state and the output timing of the external circuit is designed to avoid output conflict.

- 2. Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

The ratings and conditions indicated for DC characteristics and AC characteristics represent the quality assurance range during normal operation.

| Parameter          | Symbol | Conditions                       | MIN. | TYP. | MAX. | Unit |

|--------------------|--------|----------------------------------|------|------|------|------|

| Input capacitance  | Cı     | fc = 1 MHz                       |      |      | 15   | pF   |

| I/O capacitance    | Сю     | Unmeasured pins returned to 0 V. |      |      | 15   | pF   |

| Output capacitance | Co     |                                  |      |      | 15   | pF   |

### Capacitance (TA = 25°C, VDD = VSS = EVDD = EVSS = AVDD0 = AVSS0 = AVDD1 = AVSS1 = 0 V)

### Operating Conditions (T<sub>A</sub> = -40 to +85°C, Vss = EVss = AVss0 = AVss1 = 0 V)

| Parameter              | Symbol       | Conditions                                                   | MIN.   | TYP. | MAX. | Unit |

|------------------------|--------------|--------------------------------------------------------------|--------|------|------|------|

| System clock frequency | fxx          | PLL mode                                                     | 20     |      | 20   | MHz  |

|                        |              | Clock through mode                                           | 2.5    |      | 2.5  | MHz  |

| CPU clock frequency    | fcpu         | PLL mode                                                     | 2.5    |      | 20   | MHz  |

|                        |              | Clock through mode                                           | 0.3125 |      | 2.5  | MHz  |

| VDD, EVDD voltage      | Vdd,<br>EVdd |                                                              | 3.5    |      | 5.5  | V    |

| AVDD0, AVDD1 voltage   | AVdd         | Operation is not guaranteed when $EV_{DD}$ is 4.5 V or less. | 4.5    |      | EVDD | V    |