Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 1057                                                    |

| Number of Logic Elements/Cells | 10570                                                   |

| Total RAM Bits                 | 920448                                                  |

| Number of I/O                  | 335                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                         |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 484-BBGA, FCBGA                                         |

| Supplier Device Package        | 484-FBGA (23x23)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s10f484c5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **About This Handbook**

This handbook provides comprehensive information about the Altera® Stratix family of devices.

# How to Find Information

You can find more information in the following ways:

- The Adobe Acrobat Find feature, which searches the text of a PDF document. Click the binoculars toolbar icon to open the Find dialog box.

- Acrobat bookmarks, which serve as an additional table of contents in PDF documents.

- Thumbnail icons, which provide miniature previews of each page, provide a link to the pages.

- Numerous links, shown in green text, which allow you to jump to related information.

# How to Contact Altera

For the most up-to-date information about Altera products, go to the Altera world-wide web site at www.altera.com. For technical support on this product, go to www.altera.com/mysupport. For additional information about Altera products, consult the sources shown below.

| Information Type               | USA & Canada                                                   | All Other Locations                                                    |

|--------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------|

| Technical support              | www.altera.com/mysupport/                                      | www.altera.com/mysupport/                                              |

|                                | (800) 800-EPLD (3753)<br>(7:00 a.m. to 5:00 p.m. Pacific Time) | +1 408-544-8767<br>7:00 a.m. to 5:00 p.m. (GMT -8:00)<br>Pacific Time  |

| Product literature             | www.altera.com                                                 | www.altera.com                                                         |

| Altera literature services     | literature@altera.com                                          | literature@altera.com                                                  |

| Non-technical customer service | (800) 767-3753                                                 | + 1 408-544-7000<br>7:00 a.m. to 5:00 p.m. (GMT -8:00)<br>Pacific Time |

| FTP site                       | ftp.altera.com                                                 | ftp.altera.com                                                         |

Altera Corporation ix

### **Shift Register Support**

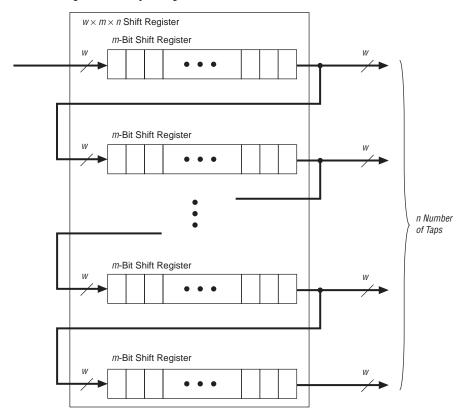

You can configure embedded memory blocks to implement shift registers for DSP applications such as pseudo-random number generators, multichannel filtering, auto-correlation, and cross-correlation functions. These and other DSP applications require local data storage, traditionally implemented with standard flip-flops, which can quickly consume many logic cells and routing resources for large shift registers. A more efficient alternative is to use embedded memory as a shift register block, which saves logic cell and routing resources and provides a more efficient implementation with the dedicated circuitry.

The size of a  $w \times m \times n$  shift register is determined by the input data width (w), the length of the taps (m), and the number of taps (n). The size of a  $w \times m \times n$  shift register must be less than or equal to the maximum number of memory bits in the respective block: 576 bits for the M512 RAM block and 4,608 bits for the M4K RAM block. The total number of shift register outputs (number of taps  $n \times$  width w) must be less than the maximum data width of the RAM block (18 for M512 blocks, 36 for M4K blocks). To create larger shift registers, the memory blocks are cascaded together.

Data is written into each address location at the falling edge of the clock and read from the address at the rising edge of the clock. The shift register mode logic automatically controls the positive and negative edge clocking to shift the data in one clock cycle. Figure 2–14 shows the TriMatrix memory block in the shift register mode.

Figure 2-14. Shift Register Memory Configuration

## **Memory Block Size**

TriMatrix memory provides three different memory sizes for efficient application support. The large number of M512 blocks are ideal for designs with many shallow first-in first-out (FIFO) buffers. M4K blocks provide additional resources for channelized functions that do not require large amounts of storage. The M-RAM blocks provide a large single block of RAM ideal for data packet storage. The different-sized blocks allow Stratix devices to efficiently support variable-sized memory in designs.

The Quartus II software automatically partitions the user-defined memory into the embedded memory blocks using the most efficient size combinations. You can also manually assign the memory to a specific block size or a mixture of block sizes.

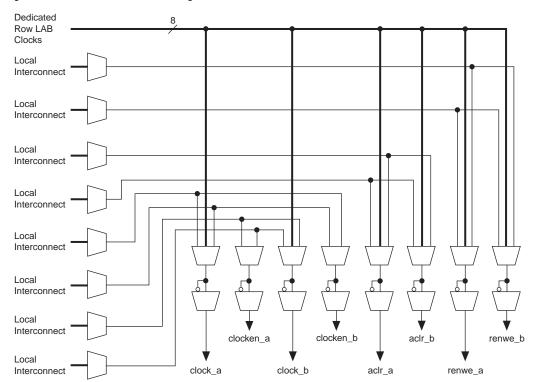

Figure 2-19. M-RAM Block Control Signals

One of the M-RAM block's horizontal sides drive the address and control signal (clock, renwe, byteena, etc.) inputs. Typically, the horizontal side closest to the device perimeter contains the interfaces. The one exception is when two M-RAM blocks are paired next to each other. In this case, the side of the M-RAM block opposite the common side of the two blocks contains the input interface. The top and bottom sides of any M-RAM block contain data input and output interfaces to the logic array. The top side has 72 data inputs and 72 data outputs for port B, and the bottom side has another 72 data inputs and 72 data outputs for port A. Figure 2–20 shows an example floorplan for the EP1S60 device and the location of the M-RAM interfaces.

Table 2–13 shows the number of DSP blocks in each Stratix device.

| Table 2–13. DSP Blocks in Stratix Devices Notes (1), (2) |            |                            |                              |                              |  |  |  |

|----------------------------------------------------------|------------|----------------------------|------------------------------|------------------------------|--|--|--|

| Device                                                   | DSP Blocks | Total 9 × 9<br>Multipliers | Total 18 × 18<br>Multipliers | Total 36 × 36<br>Multipliers |  |  |  |

| EP1S10                                                   | 6          | 48                         | 24                           | 6                            |  |  |  |

| EP1S20                                                   | 10         | 80                         | 40                           | 10                           |  |  |  |

| EP1S25                                                   | 10         | 80                         | 40                           | 10                           |  |  |  |

| EP1S30                                                   | 12         | 96                         | 48                           | 12                           |  |  |  |

| EP1S40                                                   | 14         | 112                        | 56                           | 14                           |  |  |  |

| EP1S60                                                   | 18         | 144                        | 72                           | 18                           |  |  |  |

| EP1S80                                                   | 22         | 176                        | 88                           | 22                           |  |  |  |

#### *Notes to Table 2–13:*

- (1) Each device has either the number of  $9 \times 9$ -,  $18 \times 18$ -, or  $36 \times 36$ -bit multipliers shown. The total number of multipliers for each device is not the sum of all the multipliers.

- (2) The number of supported multiply functions shown is based on signed/signed or unsigned/unsigned implementations.

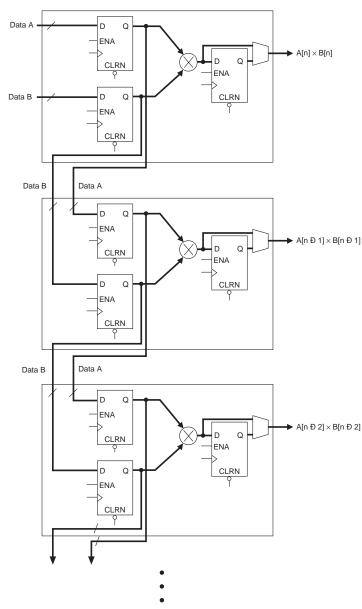

DSP block multipliers can optionally feed an adder/subtractor or accumulator within the block depending on the configuration. This makes routing to LEs easier, saves LE routing resources, and increases performance, because all connections and blocks are within the DSP block. Additionally, the DSP block input registers can efficiently implement shift registers for FIR filter applications.

Figure 2–30 shows the top-level diagram of the DSP block configured for  $18 \times 18$ -bit multiplier mode. Figure 2–31 shows the  $9 \times 9$ -bit multiplier configuration of the DSP block.

Figure 2–33. Multiplier Sub-Blocks Using Input Shift Register Connections Note (1)

Note to Figure 2–33:

(1) Either Data A or Data B input can be set to a parallel input for constant coefficient multiplication.

Table 2–14 shows the summary of input register modes for the DSP block.

| Table 2–14. Input Register Modes                               |          |          |   |  |  |  |  |  |

|----------------------------------------------------------------|----------|----------|---|--|--|--|--|--|

| Register Input Mode $9 \times 9$ $18 \times 18$ $36 \times 36$ |          |          |   |  |  |  |  |  |

| Parallel input                                                 | <b>✓</b> | <b>✓</b> | ✓ |  |  |  |  |  |

| Shift register input                                           | ✓        | ✓        |   |  |  |  |  |  |

#### Multiplier

The multiplier supports  $9 \times 9$ -,  $18 \times 18$ -, or  $36 \times 36$ -bit multiplication. Each DSP block supports eight possible  $9 \times 9$ -bit or smaller multipliers. There are four multiplier blocks available for multipliers larger than  $9 \times 9$  bits but smaller than  $18 \times 18$  bits. There is one multiplier block available for multipliers larger than  $18 \times 18$  bits but smaller than or equal to  $36 \times 36$  bits. The ability to have several small multipliers is useful in applications such as video processing. Large multipliers greater than  $18 \times 18$  bits are useful for applications such as the mantissa multiplication of a single-precision floating-point number.

The multiplier operands can be signed or unsigned numbers, where the result is signed if either input is signed as shown in Table 2–15. The sign\_a and sign\_b signals provide dynamic control of each operand's representation: a logic 1 indicates the operand is a signed number, a logic 0 indicates the operand is an unsigned number. These sign signals affect all multipliers and adders within a single DSP block and you can register them to match the data path pipeline. The multipliers are full precision (that is, 18 bits for the 18-bit multiply, 36-bits for the 36-bit multiply, and so on) regardless of whether sign\_a or sign\_b set the operands as signed or unsigned numbers.

| Table 2–15. Multiplier Signed Representation |          |          |  |  |  |  |

|----------------------------------------------|----------|----------|--|--|--|--|

| Data A                                       | Result   |          |  |  |  |  |

| Unsigned                                     | Unsigned | Unsigned |  |  |  |  |

| Unsigned                                     | Signed   | Signed   |  |  |  |  |

| Signed                                       | Unsigned | Signed   |  |  |  |  |

| Signed                                       | Signed   | Signed   |  |  |  |  |

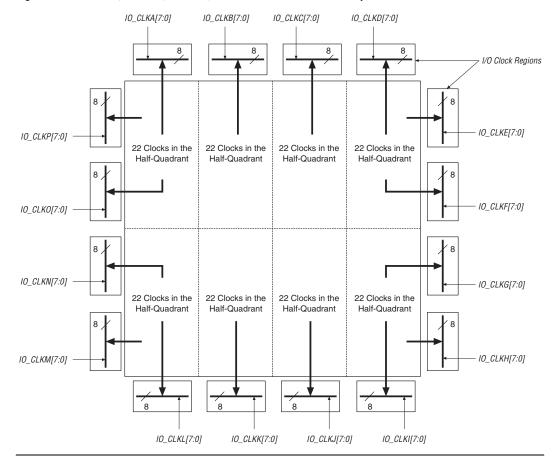

Figure 2-48. EP1S30, EP1S40, EP1S60, EP1S80 Device I/O Clock Groups

You can use the Quartus II software to control whether a clock input pin is either global, regional, or fast regional. The Quartus II software automatically selects the clocking resources if not specified.

#### **Enhanced & Fast PLLs**

Stratix devices provide robust clock management and synthesis using up to four enhanced PLLs and eight fast PLLs. These PLLs increase performance and provide advanced clock interfacing and clock-frequency synthesis. With features such as clock switchover, spread spectrum clocking, programmable bandwidth, phase and delay control, and PLL reconfiguration, the Stratix device's enhanced PLLs provide you with complete control of your clocks and system timing. The fast PLLs

| Table 2–20. I/O Standards Supported for Enhanced PLL Pins (Part 2 of 2) |          |          |           |          |  |  |

|-------------------------------------------------------------------------|----------|----------|-----------|----------|--|--|

| I/O Standard                                                            |          | Output   |           |          |  |  |

| I/O Standard                                                            | INCLK    | FBIN     | PLLENABLE | EXTCLK   |  |  |

| 1.5-V HSTL Class II                                                     | <b>✓</b> | <b>✓</b> |           | ✓        |  |  |

| 1.8-V HSTL Class I                                                      | <b>✓</b> | <b>✓</b> |           | ✓        |  |  |

| 1.8-V HSTL Class II                                                     | <b>✓</b> | <b>✓</b> |           | ✓        |  |  |

| SSTL-18 Class I                                                         | <b>✓</b> | <b>✓</b> |           | ✓        |  |  |

| SSTL-18 Class II                                                        | <b>✓</b> | <b>✓</b> |           | ✓        |  |  |

| SSTL-2 Class I                                                          | <b>✓</b> | <b>✓</b> |           | ✓        |  |  |

| SSTL-2 Class II                                                         | <b>✓</b> | <b>✓</b> |           | ✓        |  |  |

| SSTL-3 Class I                                                          | <b>✓</b> | <b>✓</b> |           | ✓        |  |  |

| SSTL-3 Class II                                                         | <b>✓</b> | ✓        |           | ✓        |  |  |

| AGP (1× and 2×)                                                         | <b>✓</b> | ✓        |           | <b>✓</b> |  |  |

| СТТ                                                                     | <b>✓</b> | ✓        |           | ✓        |  |  |

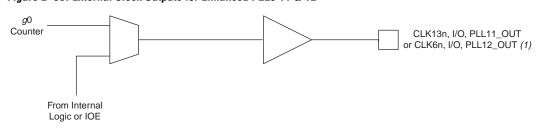

Enhanced PLLs 11 and 12 support one single-ended output each (see Figure 2–56). These outputs do not have their own VCC and GND signals. Therefore, to minimize jitter, do not place switching I/O pins next to this output pin.

Figure 2-56. External Clock Outputs for Enhanced PLLs 11 & 12

Note to Figure 2-56:

(1) For PLL 11, this pin is CLK13n; for PLL 12 this pin is CLK7n.

Stratix devices can drive any enhanced PLL driven through the global clock or regional clock network to any general I/O pin as an external output clock. The jitter on the output clock is not guaranteed for these cases.

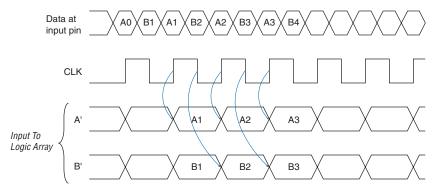

Figure 2-66. Input Timing Diagram in DDR Mode

When using the IOE for DDR outputs, the two output registers are configured to clock two data paths from LEs on rising clock edges. These output registers are multiplexed by the clock to drive the output pin at a  $\times 2$  rate. One output register clocks the first bit out on the clock high time, while the other output register clocks the second bit out on the clock low time. Figure 2–67 shows the IOE configured for DDR output. Figure 2–68 shows the DDR output timing diagram.

## **Programmable Pull-Up Resistor**

Each Stratix device I/O pin provides an optional programmable pull-up resistor during user mode. If this feature is enabled for an I/O pin, the pull-up resistor (typically 25 k $\Omega$ ) weakly holds the output to the V<sub>CCIO</sub> level of the output pin's bank. Table 2–30 shows which pin types support the weak pull-up resistor feature.

| Table 2–30. Programmable Weak Pull-Up Resistor Support |              |  |  |  |  |

|--------------------------------------------------------|--------------|--|--|--|--|

| Pin Type Programmable Weak Pull-Up F                   |              |  |  |  |  |

| I/O pins                                               | ✓            |  |  |  |  |

| CLK[150]                                               |              |  |  |  |  |

| FCLK                                                   | ~            |  |  |  |  |

| FPLL[710]CLK                                           |              |  |  |  |  |

| Configuration pins                                     |              |  |  |  |  |

| JTAG pins                                              | <b>√</b> (1) |  |  |  |  |

*Note to Table 2–30:*

(1) TDO pins do not support programmable weak pull-up resistors.

## Advanced I/O Standard Support

Stratix device IOEs support the following I/O standards:

- LVTTL

- LVCMOS

- 1.5 V

- 1.8 V

- 2.5 V

- 3.3-V PCI

- 3.3-V PCI-X 1.0

- 3.3-V AGP (1× and 2×)

- LVDS

- LVPECL

- 3.3-V PCML

- HyperTransport

- Differential HSTL (on input/output clocks only)

- Differential SSTL (on output column clock pins only)

- GTL/GTL+

- 1.5-V HSTL Class I and II

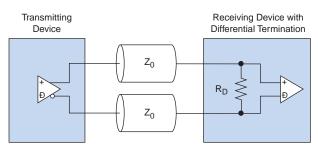

Figure 2-71. LVDS Input Differential On-Chip Termination

I/O banks on the left and right side of the device support LVDS receiver (far-end) differential termination.

Table 2–33 shows the Stratix device differential termination support.

| Table 2–33. Differential Termination Supported by I/O Banks                                                             |      |  |          |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------|------|--|----------|--|--|--|

| Differential Termination Support I/O Standard Support Top & Bottom Banks (3, 4, 7 & 8) Left & Right Banks (1, 2, 5 & 6) |      |  |          |  |  |  |

| Differential termination (1), (2)                                                                                       | LVDS |  | <b>✓</b> |  |  |  |

Notes to Table 2-33:

- (1) Clock pin CLK0, CLK2, CLK9, CLK11, and pins FPLL [7..10] CLK do not support differential termination.

- (2) Differential termination is only supported for LVDS because of a 3.3-V V<sub>CCIO</sub>.

Table 2–34 shows the termination support for different pin types.

| Table 2–34. Differential Termination Support Across Pin Types |                |  |  |  |  |

|---------------------------------------------------------------|----------------|--|--|--|--|

| Pin Type                                                      | R <sub>D</sub> |  |  |  |  |

| Top and bottom I/O banks (3, 4, 7, and 8)                     |                |  |  |  |  |

| DIFFIO_RX[]                                                   | <b>✓</b>       |  |  |  |  |

| CLK[0,2,9,11],CLK[4-7],CLK[12-15]                             |                |  |  |  |  |

| CLK[1,3,8,10]                                                 | <b>✓</b>       |  |  |  |  |

| FCLK                                                          |                |  |  |  |  |

| FPLL[710]CLK                                                  |                |  |  |  |  |

The differential on-chip resistance at the receiver input buffer is 118  $\Omega \pm 20$  %.

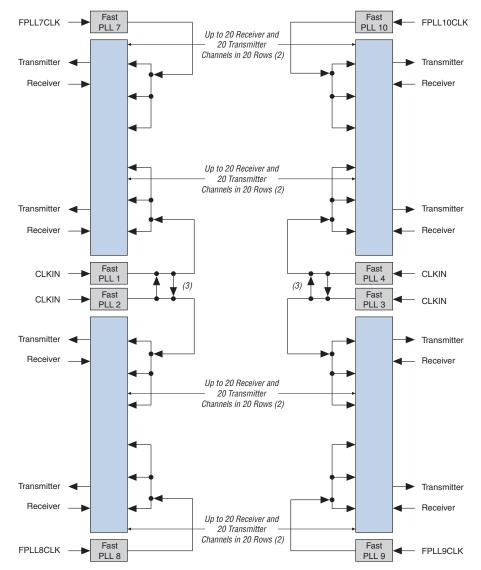

Figure 2-75. Fast PLL & Channel Layout in the EP1S30 to EP1S80 Devices Note (1)

#### Notes to Figure 2-75:

- (1) Wire-bond packages support up to 624 Mbps.

- (2) See Table 2–38 through 2–41 for the number of channels each device supports.

- (3) There is a multiplexer here to select the PLL clock source. If a PLL uses this multiplexer to clock channels outside of its bank quadrant, those clocked channels support up to 840 Mbps for "high" speed channels and 462 Mbps for "low" speed channels as labeled in the device pin-outs at www.altera.com.

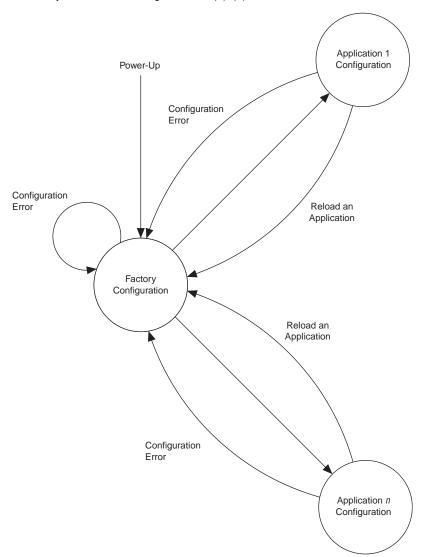

While in the factory configuration, the factory-configuration logic performs the following operations:

- Loads a remote update-control register to determine the page address of the new application configuration

- Determines whether to enable a user watchdog timer for the application configuration

- Determines what the watchdog timer setting should be if it is enabled

The user watchdog timer is a counter that must be continually reset within a specific amount of time in the user mode of an application configuration to ensure that valid configuration occurred during a remote update. Only valid application configurations designed for remote update can reset the user watchdog timer in user mode. If a valid application configuration does not reset the user watchdog timer in a specific amount of time, the timer updates a status register and loads the factory configuration. The user watchdog timer is automatically disabled for factory configurations.

If an error occurs in loading the application configuration, the configuration logic writes a status register to specify the cause of the error. Once this occurs, the Stratix device automatically loads the factory configuration, which reads the status register and determines the reason for reconfiguration. Based on the reason, the factory configuration will take appropriate steps and will write the remote update control register to specify the next application configuration page to be loaded.

When the Stratix device successfully loads the application configuration, it enters into user mode. The Stratix device then executes the main application of the user. Intellectual property (IP), such as a Nios® (16-bit ISA) and Nios® II (32-bit ISA) embedded processors, can help the Stratix device determine when remote update is coming. The Nios embedded processor or user logic receives incoming data, writes it to the configuration device, and loads the factory configuration. The factory configuration will read the remote update status register and determine the valid application configuration to load. Figure 3–2 shows the Stratix remote update. Figure 3–3 shows the transition diagram for remote update mode.

Figure 3–3. Remote Update Transition Diagram Notes (1), (2)

#### *Notes to Figure 3–3:*

- (1) Remote update of Application Configuration is controlled by a Nios embedded processor or user logic programmed in the Factory or Application configurations.

- (2) Up to seven pages can be specified allowing up to seven different configuration applications.

| Table 4–39. DSP              | Block Internal Timing Microparameter Descriptions                                                                                                                                                                                                                                                                                                         |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                       | Parameter                                                                                                                                                                                                                                                                                                                                                 |

| t <sub>SU</sub>              | Input, pipeline, and output register setup time before clock                                                                                                                                                                                                                                                                                              |

| t <sub>H</sub>               | Input, pipeline, and output register hold time after clock                                                                                                                                                                                                                                                                                                |

| t <sub>co</sub>              | Input, pipeline, and output register clock-to-output delay                                                                                                                                                                                                                                                                                                |

| t <sub>INREG2PIPE9</sub>     | Input Register to DSP Block pipeline register in $9\times9$ -bit mode                                                                                                                                                                                                                                                                                     |

| t <sub>INREG2PIPE18</sub>    | Input Register to DSP Block pipeline register in 18 $\times$ 18-bit mode                                                                                                                                                                                                                                                                                  |

| t <sub>PIPE2OUTREG2ADD</sub> | DSP Block Pipeline Register to output register delay in Two-Multipliers Adder mode                                                                                                                                                                                                                                                                        |

| t <sub>PIPE2OUTREG4ADD</sub> | DSP Block Pipeline Register to output register delay in Four-Multipliers Adder mode                                                                                                                                                                                                                                                                       |

| t <sub>PD9</sub>             | Combinatorial input to output delay for $9 \times 9$                                                                                                                                                                                                                                                                                                      |

| t <sub>PD18</sub>            | Combinatorial input to output delay for 18 × 18                                                                                                                                                                                                                                                                                                           |

| t <sub>PD36</sub>            | Combinatorial input to output delay for $36 \times 36$                                                                                                                                                                                                                                                                                                    |

| t <sub>CLR</sub>             | Minimum clear pulse width                                                                                                                                                                                                                                                                                                                                 |

| t <sub>CLKHL</sub>           | Register minimum clock high or low time. This is a limit on the min time for the clock on the registers in these blocks. The actual performance is dependent upon the internal point-to-point delays in the blocks and may give slower performance as shown in Table 4–36 on page 4–20 and as reported by the timing analyzer in the Quartus II software. |

| Table 4–49. M4K Block Internal Timing Microparameters |       |       |       |       |       |       |       |       |      |

|-------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Symbol                                                | -     | -5    |       | -6    |       | -7    |       | -8    |      |

| Зуший                                                 | Min   | Max   | Min   | Max   | Min   | Max   | Min   | Max   | Unit |

| t <sub>M4KRC</sub>                                    |       | 3,807 |       | 4,320 |       | 4,967 |       | 5,844 | ps   |

| t <sub>M4KWC</sub>                                    |       | 2,556 |       | 2,840 |       | 3,265 |       | 3,842 | ps   |

| t <sub>M4KWERESU</sub>                                | 131   |       | 149   |       | 171   |       | 202   |       | ps   |

| t <sub>M4KWEREH</sub>                                 | 34    |       | 38    |       | 43    |       | 51    |       | ps   |

| t <sub>M4KCLKENSU</sub>                               | 193   |       | 215   |       | 247   |       | 290   |       | ps   |

| t <sub>M4KCLKENH</sub>                                | -63   |       | -70   |       | -81   |       | -95   |       | ps   |

| t <sub>M4KBESU</sub>                                  | 131   |       | 149   |       | 171   |       | 202   |       | ps   |

| t <sub>M4KBEH</sub>                                   | 34    |       | 38    |       | 43    |       | 51    |       | ps   |

| t <sub>M4KDATAASU</sub>                               | 131   |       | 149   |       | 171   |       | 202   |       | ps   |

| t <sub>M4KDATAAH</sub>                                | 34    |       | 38    |       | 43    |       | 51    |       | ps   |

| t <sub>M4KADDRASU</sub>                               | 131   |       | 149   |       | 171   |       | 202   |       | ps   |

| t <sub>M4KADDRAH</sub>                                | 34    |       | 38    |       | 43    |       | 51    |       | ps   |

| t <sub>M4KDATABSU</sub>                               | 131   |       | 149   |       | 171   |       | 202   |       | ps   |

| t <sub>M4KDATABH</sub>                                | 34    |       | 38    |       | 43    |       | 51    |       | ps   |

| t <sub>M4KADDRBSU</sub>                               | 131   |       | 149   |       | 171   |       | 202   |       | ps   |

| t <sub>M4KADDRBH</sub>                                | 34    |       | 38    |       | 43    |       | 51    |       | ps   |

| t <sub>M4KDATACO1</sub>                               |       | 571   |       | 635   |       | 729   |       | 858   | ps   |

| t <sub>M4KDATACO2</sub>                               |       | 3,984 |       | 4,507 |       | 5,182 |       | 6,097 | ps   |

| t <sub>M4KCLKHL</sub>                                 | 1,000 |       | 1,111 |       | 1,190 |       | 1,400 |       | ps   |

| t <sub>M4KCLR</sub>                                   | 170   |       | 189   |       | 217   |       | 255   |       | ps   |

| Table 4–50. M-RAM Block Internal Timing Microparameters (Part 1 of 2) |     |       |     |       |     |       |     |       |      |

|-----------------------------------------------------------------------|-----|-------|-----|-------|-----|-------|-----|-------|------|

| Symbol                                                                | -5  |       | -   | -6    |     | -7    |     | -8    |      |

|                                                                       | Min | Max   | Min | Max   | Min | Max   | Min | Max   | Unit |

| t <sub>MRAMRC</sub>                                                   |     | 4,364 |     | 4,838 |     | 5,562 |     | 6,544 | ps   |

| t <sub>MRAMWC</sub>                                                   |     | 3,654 |     | 4,127 |     | 4,746 |     | 5,583 | ps   |

| t <sub>MRAMWERESU</sub>                                               | 25  |       | 25  |       | 28  |       | 33  |       | ps   |

| t <sub>MRAMWEREH</sub>                                                | 18  |       | 20  |       | 23  |       | 27  |       | ps   |

| t <sub>MRAMCLKENSU</sub>                                              | 99  |       | 111 |       | 127 |       | 150 |       | ps   |

| t <sub>MRAMCLKENH</sub>                                               | -48 |       | -53 |       | -61 |       | -72 |       | ps   |

Table 4–119. Stratix Maximum Input Clock Rate for CLK[1, 3, 8, 10] Pins in Wire-Bond Packages (Part 2 of 2)

| I/O Standard                  | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------|-------------------|-------------------|-------------------|------|

| SSTL-18 Class I               | 350               | 300               | 300               | MHz  |

| SSTL-18 Class II              | 350               | 300               | 300               | MHz  |

| 1.5-V HSTL Class I            | 350               | 300               | 300               | MHz  |

| 1.8-V HSTL Class I            | 350               | 300               | 300               | MHz  |

| CTT                           | 250               | 200               | 200               | MHz  |

| Differential 1.5-V HSTL<br>C1 | 350               | 300               | 300               | MHz  |

| LVPECL (1)                    | 645               | 622               | 622               | MHz  |

| PCML (1)                      | 275               | 275               | 275               | MHz  |

| LVDS (1)                      | 645               | 622               | 622               | MHz  |

| HyperTransport technology (1) | 500               | 450               | 450               | MHz  |

Note to Tables 4–114 through 4–119:

Tables 4–120 through 4–123 show the maximum output clock rate for column and row pins in Stratix devices.

Table 4–120. Stratix Maximum Output Clock Rate for PLL[5, 6, 11, 12] Pins in Flip-Chip Packages (Part 1 of 2)

| I/O Standard       | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|--------------------|-------------------|-------------------|-------------------|-------------------|------|

| LVTTL              | 350               | 300               | 250               | 250               | MHz  |

| 2.5 V              | 350               | 300               | 300               | 300               | MHz  |

| 1.8 V              | 250               | 250               | 250               | 250               | MHz  |

| 1.5 V              | 225               | 200               | 200               | 200               | MHz  |

| LVCMOS             | 350               | 300               | 250               | 250               | MHz  |

| GTL                | 200               | 167               | 125               | 125               | MHz  |

| GTL+               | 200               | 167               | 125               | 125               | MHz  |

| SSTL-3 Class I     | 200               | 167               | 167               | 133               | MHz  |

| SSTL-3 Class II    | 200               | 167               | 167               | 133               | MHz  |

| SSTL-2 Class I (3) | 200               | 200               | 167               | 167               | MHz  |

| SSTL-2 Class I (4) | 200               | 200               | 167               | 167               | MHz  |

| SSTL-2 Class I (5) | 150               | 134               | 134               | 134               | MHz  |

<sup>(1)</sup> These parameters are only available on row I/O pins.

| Table 4–132. Fast PLL Specifications for -7 Speed Grades (Part 2 of 2) |                                                            |     |     |         |

|------------------------------------------------------------------------|------------------------------------------------------------|-----|-----|---------|

| Symbol                                                                 | Parameter                                                  | Min | Max | Unit    |

| t <sub>JITTER</sub>                                                    | Period jitter for DIFFIO clock out (6)                     |     | (5) | ps      |

| t <sub>LOCK</sub>                                                      | Time required for PLL to acquire lock                      | 10  | 100 | μs      |

| m                                                                      | Multiplication factors for <i>m</i> counter (7)            | 1   | 32  | Integer |

| 10, 11, g0                                                             | Multiplication factors for IO, I1, and gO counter (7), (8) | 1   | 32  | Integer |

| t <sub>ARESET</sub>                                                    | Minimum pulse width on areset signal                       | 10  |     | ns      |

| Table 4–133. Fast PLL Specifications for -8 Speed Grades (Part 1 of 2) |                                                                                   |       |      |         |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------|------|---------|

| Symbol                                                                 | Parameter                                                                         | Min   | Max  | Unit    |

| f <sub>IN</sub>                                                        | CLKIN frequency (1), (3)                                                          | 10    | 460  | MHz     |

| f <sub>INPFD</sub>                                                     | Input frequency to PFD                                                            | 10    | 500  | MHz     |

| f <sub>OUT</sub>                                                       | Output frequency for internal global or regional clock (4)                        | 9.375 | 420  | MHz     |

| f <sub>OUT_DIFFIO</sub>                                                | Output frequency for external clock driven out on a differential I/O data channel | (5)   | (5)  | MHz     |

| f <sub>VCO</sub>                                                       | VCO operating frequency                                                           | 300   | 700  | MHz     |

| t <sub>INDUTY</sub>                                                    | CLKIN duty cycle                                                                  | 40    | 60   | %       |

| t <sub>INJITTER</sub>                                                  | Period jitter for CLKIN pin                                                       |       | ±200 | ps      |

| t <sub>DUTY</sub>                                                      | Duty cycle for DFFIO 1× CLKOUT pin (6)                                            | 45    | 55   | %       |

| t <sub>JITTER</sub>                                                    | Period jitter for DIFFIO clock out (6)                                            |       | (5)  | ps      |

| t <sub>LOCK</sub>                                                      | Time required for PLL to acquire lock                                             | 10    | 100  | μs      |

| m                                                                      | Multiplication factors for <i>m</i> counter (7)                                   | 1     | 32   | Integer |

| 10, 11, g0                                                             | Multiplication factors for I0, I1, and g0 counter (7), (8)                        | 1     | 32   | Integer |

| Mode 2–36                                             | Port I/O Standards 2–102                            |

|-------------------------------------------------------|-----------------------------------------------------|

| Row & Column Interface Unit                           | I/O Standards Supported for Enhanced PLL            |

| Signals 2–43                                          | Pins 2–94                                           |

| Parity Bit Support 2–24                               | Lock Detect & Programmable Gated                    |

| Shift Register                                        | Locked 2–98                                         |

| Memory Configuration 2–26                             | PLL Locations 2–84                                  |

| Support 2–25                                          | Programmable Bandwidth 2–91                         |

| Simple Dual-Port & Single-Port Memory                 | Programmable Delay Chain 2-111                      |

| Configurations 2–23                                   | Programmable Duty Cycle 2–98                        |

| Stratix IOE in DDR Input I/O                          | Reconfiguration 2–90                                |

| Configuration 2–112                                   |                                                     |

| Stratix IOE in DDR Output I/O                         | Т                                                   |

| Configuration 2–114                                   | 1                                                   |

| TriMatrix Memory 2–21                                 | Testing                                             |

| True Dual-Port Memory                                 | Temperature Sensing Diode 3–13                      |

| Configuration 2–22                                    | Electrical Characteristics 3–14                     |

|                                                       | External 3–14                                       |

| 0                                                     | Temperature vs. Temperature-Sensing Diode           |

|                                                       | Voltage 3–15                                        |

| Ordering Information 5–1                              | Timing                                              |

| Device Pin-Outs 5–1                                   | DSP                                                 |

| Packaging Ordering Information 5–2                    | Block Internal Timing                               |

| Reference & Ordering Information 5–1                  | Microparameter                                      |

| Output Registers 2–64                                 | Descriptions 4–23                                   |

| Output Selection Multiplexer 2–64                     | Microparameters 4–29                                |

|                                                       | Dual-Port RAM Timing Microparameter                 |

| P                                                     | Waveform 4–27                                       |

| P. 1                                                  | External Timing in Stratix Devices 4–33             |

| Packaging                                             | High-Speed I/O Timing 4–87                          |

| BGA Package Sizes 1–4                                 | High-Speed Timing Specifications & Terminology 4–87 |

| Device Speed Grades 1–5                               | Internal Parameters 4–22                            |

| FineLine BGA Package Sizes 1–5                        | IOE Internal Timing Microparameter                  |

| PCI-X 1.0 Specifications 4–10<br>Phase Shifting 2–103 | Descriptions 4–22                                   |

| PLL                                                   | LE Internal Timing Microparameters 4–28             |

| Advanced Clear & Enable Control 2–98                  | Logic Elements Internal Timing Microparam-          |

| Dynamically Programmable Counters & De-               | eter Descriptions 4–22                              |

| lays in Stratix Device Enhanced                       | Model 4–19                                          |

| PLLs 2–91                                             | PLL Timing 4–94                                     |

| Enhanced                                              | Preliminary & Final 4–19                            |

| Fast PLLs 2–81                                        | Stratix Device Timing Model Status 4–19             |

| Fast PLL 2–100                                        | Stratix JTAG                                        |

| Channel Layout EP1S10, EP1S20 or                      | Timing Parameters & Values 3–4                      |

| EP1S25 Devices 2–138                                  | TriMatrix Memory                                    |

| Channel Layout EP1S30 to EP1S80                       | TriMatrix Memory Features 2–21                      |

| Devices 2–139                                         | •                                                   |

Index-6 Altera Corporation