Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 1057                                                     |

| Number of Logic Elements/Cells | 10570                                                    |

| Total RAM Bits                 | 920448                                                   |

| Number of I/O                  | 335                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 484-BBGA, FCBGA                                          |

| Supplier Device Package        | 484-FBGA (23x23)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s10f484c5n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Contents Contents

| Maximum Input & Output Clock Rates                    | 4–76 |

|-------------------------------------------------------|------|

| High-Speed I/O Specification                          | 4–87 |

| PLL Specifications                                    | 4–94 |

| DLL Specifications                                    |      |

|                                                       |      |

| Chapter 5. Reference & Ordering Information           |      |

| Software                                              |      |

| Chapter 5. Reference & Ordering Information  Software | 5–1  |

# Index

Altera Corporation v

Figure 2-2. Stratix LAB Structure

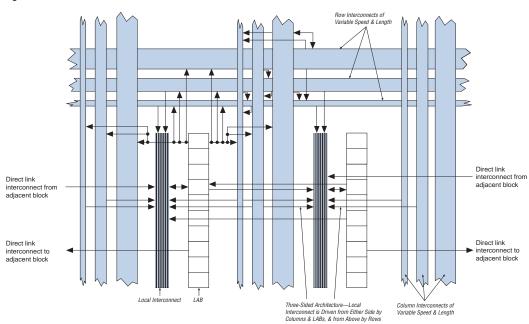

### LAB Interconnects

The LAB local interconnect can drive LEs within the same LAB. The LAB local interconnect is driven by column and row interconnects and LE outputs within the same LAB. Neighboring LABs, M512 RAM blocks, M4K RAM blocks, or DSP blocks from the left and right can also drive an LAB's local interconnect through the direct link connection. The direct link connection feature minimizes the use of row and column interconnects, providing higher performance and flexibility. Each LE can drive 30 other LEs through fast local and direct link interconnects. Figure 2–3 shows the direct link connection.

asynchronous load, and clear signals. An asynchronous clear signal takes precedence if both signals are asserted simultaneously. Each LAB supports up to two clears and one preset signal.

In addition to the clear and preset ports, Stratix devices provide a chip-wide reset pin (DEV\_CLRn) that resets all registers in the device. An option set before compilation in the Quartus II software controls this pin. This chip-wide reset overrides all other control signals.

# MultiTrack Interconnect

In the Stratix architecture, connections between LEs, TriMatrix memory, DSP blocks, and device I/O pins are provided by the MultiTrack interconnect structure with DirectDrive technology. The MultiTrack interconnect consists of continuous, performance-optimized routing lines of different lengths and speeds used for inter- and intra-design block connectivity. The Quartus II Compiler automatically places critical design paths on faster interconnects to improve design performance.

DirectDrive technology is a deterministic routing technology that ensures identical routing resource usage for any function regardless of placement within the device. The MultiTrack interconnect and DirectDrive technology simplify the integration stage of block-based designing by eliminating the re-optimization cycles that typically follow design changes and additions.

The MultiTrack interconnect consists of row and column interconnects that span fixed distances. A routing structure with fixed length resources for all devices allows predictable and repeatable performance when migrating through different device densities. Dedicated row interconnects route signals to and from LABs, DSP blocks, and TriMatrix memory within the same row. These row resources include:

- Direct link interconnects between LABs and adjacent blocks.

- R4 interconnects traversing four blocks to the right or left.

- R8 interconnects traversing eight blocks to the right or left.

- R24 row interconnects for high-speed access across the length of the device.

The direct link interconnect allows an LAB, DSP block, or TriMatrix memory block to drive into the local interconnect of its left and right neighbors and then back into itself. Only one side of a M-RAM block interfaces with direct link and row interconnects. This provides fast communication between adjacent LABs and/or blocks without using row interconnect resources.

The R4 interconnects span four LABs, three LABs and one M512 RAM block, two LABs and one M4K RAM block, or two LABs and one DSP block to the right or left of a source LAB. These resources are used for fast

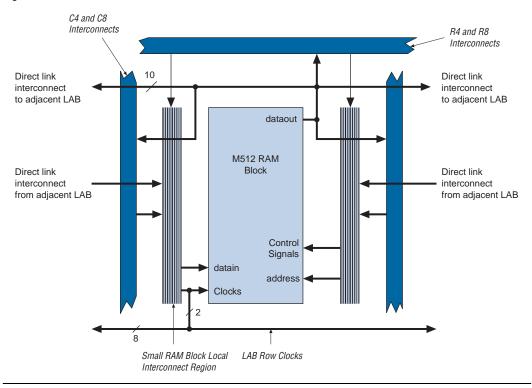

Figure 2-16. M512 RAM Block LAB Row Interface

### M4K RAM Blocks

The M4K RAM block includes support for true dual-port RAM. The M4K RAM block is used to implement buffers for a wide variety of applications such as storing processor code, implementing lookup schemes, and implementing larger memory applications. Each block contains 4,608 RAM bits (including parity bits). M4K RAM blocks can be configured in the following modes:

- True dual-port RAM

- Simple dual-port RAM

- Single-port RAM

- FIFO

- ROM

- Shift register

When configured as RAM or ROM, you can use an initialization file to pre-load the memory contents.

#### M-RAM Block

The largest TriMatrix memory block, the M-RAM block, is useful for applications where a large volume of data must be stored on-chip. Each block contains 589,824 RAM bits (including parity bits). The M-RAM block can be configured in the following modes:

- True dual-port RAM

- Simple dual-port RAM

- Single-port RAM

- FIFO RAM

You cannot use an initialization file to initialize the contents of a M-RAM block. All M-RAM block contents power up to an undefined value. Only synchronous operation is supported in the M-RAM block, so all inputs are registered. Output registers can be bypassed. The memory address and output width can be configured as  $64 \text{K} \times 8$  (or  $64 \text{K} \times 9$  bits),  $32 \text{K} \times 16$  (or  $32 \text{K} \times 18$  bits),  $16 \text{K} \times 32$  (or  $16 \text{K} \times 36$  bits),  $8 \text{K} \times 64$  (or  $8 \text{K} \times 72$  bits), and  $4 \text{K} \times 128$  (or  $4 \text{K} \times 144$  bits). The  $4 \text{K} \times 128$  configuration is unavailable in true dual-port mode because there are a total of 144 data output drivers in the block. Mixed-width configurations are also possible, allowing different read and write widths. Tables 2–8 and 2–9 summarize the possible M-RAM block configurations:

| Table 2–8. M-RAM Block Configurations (Simple Dual-Port) |            |          |          |          |          |  |  |  |  |  |

|----------------------------------------------------------|------------|----------|----------|----------|----------|--|--|--|--|--|

| Read Port                                                | Write Port |          |          |          |          |  |  |  |  |  |

|                                                          | 64K × 9    | 32K × 18 | 16K × 36 | 8K × 72  | 4K × 144 |  |  |  |  |  |

| 64K × 9                                                  | <b>✓</b>   | <b>✓</b> | ✓        | <b>✓</b> |          |  |  |  |  |  |

| 32K × 18                                                 | ✓          | ✓        | ✓        | ✓        |          |  |  |  |  |  |

| 16K × 36                                                 | ✓          | ✓        | ✓        | ✓        |          |  |  |  |  |  |

| 8K × 72                                                  | <b>✓</b>   | <b>✓</b> | ✓        | <b>✓</b> |          |  |  |  |  |  |

| 4K × 144                                                 |            |          |          |          | ✓        |  |  |  |  |  |

## Read/Write Clock Mode

The memory blocks implement read/write clock mode for simple dual-port memory. You can use up to two clocks in this mode. The write clock controls the block's data inputs, wraddress, and wren. The read clock controls the data output, rdaddress, and rden. The memory blocks support independent clock enables for each clock and asynchronous clear signals for the read- and write-side registers. Figure 2–27 shows a memory block in read/write clock mode.

Table 2–14 shows the summary of input register modes for the DSP block.

| Table 2–14. Input Register Modes |          |         |         |  |  |  |  |  |  |

|----------------------------------|----------|---------|---------|--|--|--|--|--|--|

| Register Input Mode              | 9 × 9    | 18 × 18 | 36 × 36 |  |  |  |  |  |  |

| Parallel input                   | <b>✓</b> | ✓       | ✓       |  |  |  |  |  |  |

| Shift register input             | ✓        | ✓       |         |  |  |  |  |  |  |

#### Multiplier

The multiplier supports  $9 \times 9$ -,  $18 \times 18$ -, or  $36 \times 36$ -bit multiplication. Each DSP block supports eight possible  $9 \times 9$ -bit or smaller multipliers. There are four multiplier blocks available for multipliers larger than  $9 \times 9$  bits but smaller than  $18 \times 18$  bits. There is one multiplier block available for multipliers larger than  $18 \times 18$  bits but smaller than or equal to  $36 \times 36$  bits. The ability to have several small multipliers is useful in applications such as video processing. Large multipliers greater than  $18 \times 18$  bits are useful for applications such as the mantissa multiplication of a single-precision floating-point number.

The multiplier operands can be signed or unsigned numbers, where the result is signed if either input is signed as shown in Table 2–15. The sign\_a and sign\_b signals provide dynamic control of each operand's representation: a logic 1 indicates the operand is a signed number, a logic 0 indicates the operand is an unsigned number. These sign signals affect all multipliers and adders within a single DSP block and you can register them to match the data path pipeline. The multipliers are full precision (that is, 18 bits for the 18-bit multiply, 36-bits for the 36-bit multiply, and so on) regardless of whether sign\_a or sign\_b set the operands as signed or unsigned numbers.

| Table 2–15. Multiplier Signed Representation |          |          |  |  |  |  |  |  |

|----------------------------------------------|----------|----------|--|--|--|--|--|--|

| Data A                                       | Data B   | Result   |  |  |  |  |  |  |

| Unsigned                                     | Unsigned | Unsigned |  |  |  |  |  |  |

| Unsigned                                     | Signed   | Signed   |  |  |  |  |  |  |

| Signed                                       | Unsigned | Signed   |  |  |  |  |  |  |

| Signed                                       | Signed   | Signed   |  |  |  |  |  |  |

#### Clock Multiplication & Division

Each Stratix device enhanced PLL provides clock synthesis for PLL output ports using  $m/(n \times post\text{-scale counter})$  scaling factors. The input clock is divided by a pre-scale divider, *n*, and is then multiplied by the *m* feedback factor. The control loop drives the VCO to match  $f_{IN} \times (m/n)$ . Each output port has a unique post-scale counter that divides down the high-frequency VCO. For multiple PLL outputs with different frequencies, the VCO is set to the least common multiple of the output frequencies that meets its frequency specifications. Then, the post-scale dividers scale down the output frequency for each output port. For example, if output frequencies required from one PLL are 33 and 66 MHz, set the VCO to 330 MHz (the least common multiple in the VCO's range). There is one pre-scale counter, *n*, and one multiply counter, *m*, per PLL, with a range of 1 to 512 on each. There are two post-scale counters (*l*) for regional clock output ports, four counters (g) for global clock output ports, and up to four counters (e) for external clock outputs, all ranging from 1 to 1024 with a 50% duty cycle setting. The post-scale counters range from 1 to 512 with any non-50% duty cycle setting. The Quartus II software automatically chooses the appropriate scaling factors according to the input frequency, multiplication, and division values entered.

#### Clock Switchover

To effectively develop high-reliability network systems, clocking schemes must support multiple clocks to provide redundancy. For this reason, Stratix device enhanced PLLs support a flexible clock switchover capability. Figure 2–53 shows a block diagram of the switchover circuit. The switchover circuit is configurable, so you can define how to implement it. Clock-sense circuitry automatically switches from the primary to secondary clock for PLL reference when the primary clock signal is not present.

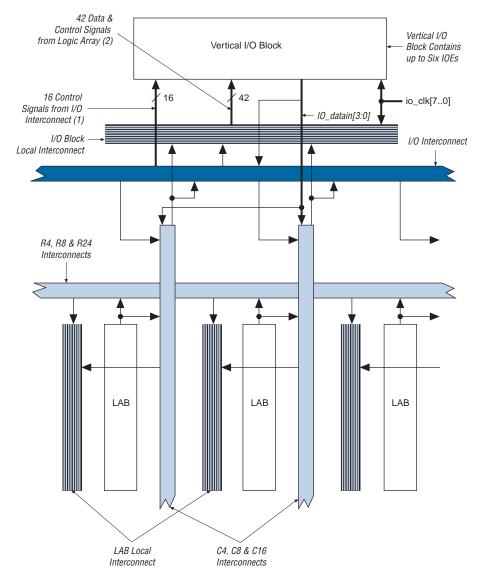

Figure 2-61. Column I/O Block Connection to the Interconnect

#### *Notes to Figure 2–61:*

- (1) The 16 control signals are composed of four output enables io\_boe[3..0], four clock enables io\_boe[3..0], four clocks io\_bclk[3..0], and four clear signals io\_bclr[3..0].

- (2) The 42 data and control signals consist of 12 data out lines; six lines each for DDR applications io\_dataouta[5..0] and io\_dataoutb[5..0], six output enables io\_coe[5..0], six input clock enables io\_cce\_in[5..0], six output clock enables io\_cce\_out[5..0], six clocks io\_cclk[5..0], and six clear signals io cclr[5..0].

#### Local Update Mode

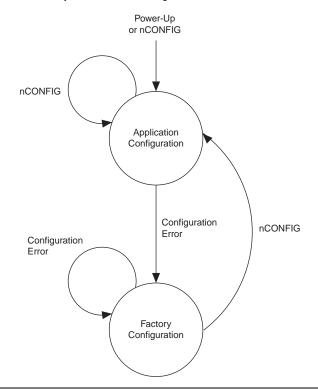

Local update mode is a simplified version of the remote update. This feature is intended for simple systems that need to load a single application configuration immediately upon power up without loading the factory configuration first. Local update designs have only one application configuration to load, so it does not require a factory configuration to determine which application configuration to use. Figure 3–4 shows the transition diagram for local update mode.

Figure 3-4. Local Update Transition Diagram

Stratix Automated Single Event Upset (SEU) Detection

Stratix devices offer on-chip circuitry for automated checking of single event upset (SEU) detection. FPGA devices that operate at high elevations or in close proximity to earth's North or South Pole require periodic checks to ensure continued data integrity. The error detection cyclic redundancy check (CRC) feature controlled by the **Device & Pin Options** dialog box in the Quartus II software uses a 32-bit CRC circuit to ensure data reliability and is one of the best options for mitigating SEU.

For Stratix, the CRC is computed by the Quartus II software and downloaded into the device as a part of the configuration bit stream. The CRC\_ERROR pin reports a soft error when configuration SRAM data is corrupted, triggering device reconfiguration.

## **Custom-Built Circuitry**

Dedicated circuitry is built in the Stratix devices to perform error detection automatically. You can use the built-in dedicated circuitry for error detection using CRC feature in Stratix devices, eliminating the need for external logic. This circuitry will perform error detection automatically when enabled. This error detection circuitry in Stratix devices constantly checks for errors in the configuration SRAM cells while the device is in user mode. You can monitor one external pin for the error and use it to trigger a re-configuration cycle. Select the desired time between checks by adjusting a built-in clock divider.

#### **Software Interface**

In the Quartus II software version 4.1 and later, you can turn on the automated error detection CRC feature in the **Device & Pin Options** dialog box. This dialog box allows you to enable the feature and set the internal frequency of the CRC between 400 kHz to 100 MHz. This controls the rate that the CRC circuitry verifies the internal configuration SRAM bits in the FPGA device.

For more information on CRC, see AN 357: Error Detection Using CRC in Altera FPGA Devices.

# Temperature Sensing Diode

Stratix devices include a diode-connected transistor for use as a temperature sensor in power management. This diode is used with an external digital thermometer device such as a MAX1617A or MAX1619 from MAXIM Integrated Products. These devices steer bias current through the Stratix diode, measuring forward voltage and converting this reading to temperature in the form of an 8-bit signed number (7 bits plus sign). The external device's output represents the junction temperature of the Stratix device and can be used for intelligent power management.

The diode requires two pins (tempdiodep and tempdioden) on the Stratix device to connect to the external temperature-sensing device, as shown in Figure 3–5. The temperature sensing diode is a passive element and therefore can be used before the Stratix device is powered.

| Table 4–41. M4<br>2 of 2) | IK Block Internal Timing Microparameter Descriptions (Part                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Symbol                    | Parameter                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| t <sub>M4KDATAAH</sub>    | A port data hold time after clock                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| t <sub>M4KADDRASU</sub>   | A port address setup time before clock                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| t <sub>M4KADDRAH</sub>    | A port address hold time after clock                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| t <sub>M4KDATABSU</sub>   | B port data setup time before clock                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| t <sub>M4KDATABH</sub>    | B port data hold time after clock                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| t <sub>M4KADDRBSU</sub>   | B port address setup time before clock                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| t <sub>M4KADDRBH</sub>    | B port address hold time after clock                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| t <sub>M4KDATACO1</sub>   | Clock-to-output delay when using output registers                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| t <sub>M4KDATACO2</sub>   | Clock-to-output delay without output registers                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| t <sub>M4KCLKHL</sub>     | Register minimum clock high or low time. This is a limit on the min time for the clock on the registers in these blocks. The actual performance is dependent upon the internal point-to-point delays in the blocks and may give slower performance as shown inTable 4–36 on page 4–20 and as reported by the timing analyzer in the Quartus II software. |  |  |  |  |  |  |  |

Minimum clear pulse width

$t_{\mathsf{M4KCLR}}$

| Table 4–42. M-RAM Block Internal Timing Microparameter  Descriptions (Part 1 of 2) |                                              |  |  |  |  |  |  |

|------------------------------------------------------------------------------------|----------------------------------------------|--|--|--|--|--|--|

| Symbol                                                                             | Parameter                                    |  |  |  |  |  |  |

| t <sub>MRAMRC</sub>                                                                | Synchronous read cycle time                  |  |  |  |  |  |  |

| t <sub>MRAMWC</sub>                                                                | Synchronous write cycle time                 |  |  |  |  |  |  |

| t <sub>MRAMWERESU</sub>                                                            | Write or read enable setup time before clock |  |  |  |  |  |  |

| t <sub>MRAMWEREH</sub>                                                             | Write or read enable hold time after clock   |  |  |  |  |  |  |

| t <sub>MRAMCLKENSU</sub>                                                           | Clock enable setup time before clock         |  |  |  |  |  |  |

| t <sub>MRAMCLKENH</sub>                                                            | Clock enable hold time after clock           |  |  |  |  |  |  |

| t <sub>MRAMBESU</sub>                                                              | Byte enable setup time before clock          |  |  |  |  |  |  |

| t <sub>MRAMBEH</sub>                                                               | Byte enable hold time after clock            |  |  |  |  |  |  |

| t <sub>MRAMDATAASU</sub>                                                           | A port data setup time before clock          |  |  |  |  |  |  |

| t <sub>MRAMDATAAH</sub>                                                            | A port data hold time after clock            |  |  |  |  |  |  |

| t <sub>MRAMADDRASU</sub>                                                           | A port address setup time before clock       |  |  |  |  |  |  |

| t <sub>MRAMADDRAH</sub>                                                            | A port address hold time after clock         |  |  |  |  |  |  |

| t <sub>MRAMDATABSU</sub>                                                           | B port setup time before clock               |  |  |  |  |  |  |

Tables 4–67 through 4–72 show the external timing parameters on column and row pins for EP1S25 devices.

| Table 4–67. EP1S25 External I/O Timing on Column Pins Using Fast Regional Clock Networks |                |       |                |       |                |       |                |       |      |  |  |  |

|------------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-------|------|--|--|--|

| Parameter                                                                                | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | 11!4 |  |  |  |

|                                                                                          | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max   | Unit |  |  |  |

| t <sub>INSU</sub>                                                                        | 2.412          |       | 2.613          |       | 2.968          |       | 3.468          |       | ns   |  |  |  |

| t <sub>INH</sub>                                                                         | 0.000          |       | 0.000          |       | 0.000          |       | 0.000          |       | ns   |  |  |  |

| t <sub>OUTCO</sub>                                                                       | 2.196          | 4.475 | 2.196          | 4.748 | 2.196          | 5.118 | 2.196          | 5.603 | ns   |  |  |  |

| t <sub>XZ</sub>                                                                          | 2.136          | 4.349 | 2.136          | 4.616 | 2.136          | 4.994 | 2.136          | 5.488 | ns   |  |  |  |

| t <sub>ZX</sub>                                                                          | 2.136          | 4.349 | 2.136          | 4.616 | 2.136          | 4.994 | 2.136          | 5.488 | ns   |  |  |  |

| Table 4–68. EP1S25 External I/O Timing on Column Pins Using Regional Clock Networks |                |       |                |       |                |       |                |       |      |  |  |  |

|-------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-------|------|--|--|--|

| Parameter                                                                           | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | IIi4 |  |  |  |

| rarameter                                                                           | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max   | Unit |  |  |  |

| t <sub>INSU</sub>                                                                   | 1.535          |       | 1.661          |       | 1.877          |       | 2.125          |       | ns   |  |  |  |

| t <sub>INH</sub>                                                                    | 0.000          |       | 0.000          |       | 0.000          |       | 0.000          |       | ns   |  |  |  |

| t <sub>оитсо</sub>                                                                  | 2.739          | 5.396 | 2.739          | 5.746 | 2.739          | 6.262 | 2.739          | 6.946 | ns   |  |  |  |

| t <sub>XZ</sub>                                                                     | 2.679          | 5.270 | 2.679          | 5.614 | 2.679          | 6.138 | 2.679          | 6.831 | ns   |  |  |  |

| t <sub>ZX</sub>                                                                     | 2.679          | 5.270 | 2.679          | 5.614 | 2.679          | 6.138 | 2.679          | 6.831 | ns   |  |  |  |

| t <sub>INSUPLL</sub>                                                                | 0.934          |       | 0.980          |       | 1.092          |       | 1.231          |       | ns   |  |  |  |

| t <sub>INHPLL</sub>                                                                 | 0.000          |       | 0.000          |       | 0.000          |       | 0.000          |       | ns   |  |  |  |

| toutcopll                                                                           | 1.316          | 2.733 | 1.316          | 2.839 | 1.316          | 2.921 | 1.316          | 3.110 | ns   |  |  |  |

| t <sup>XZPLL</sup>                                                                  | 1.256          | 2.607 | 1.256          | 2.707 | 1.256          | 2.797 | 1.256          | 2.995 | ns   |  |  |  |

| t <sub>ZXPLL</sub>                                                                  | 1.256          | 2.607 | 1.256          | 2.707 | 1.256          | 2.797 | 1.256          | 2.995 | ns   |  |  |  |

Tables 4–85 through 4–90 show the external timing parameters on column and row pins for EP1S60 devices.

| Table 4–85. EP1S60 External I/O Timing on Column Pins Using Fast Regional Clock Networks Note (1) |         |                |       |                |       |                |     |                |      |  |  |  |

|---------------------------------------------------------------------------------------------------|---------|----------------|-------|----------------|-------|----------------|-----|----------------|------|--|--|--|

| Davamatav                                                                                         | -5 Spee | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |     | -8 Speed Grade |      |  |  |  |

| Parameter                                                                                         | Min     | Max            | Min   | Max            | Min   | Max            | Min | Max            | Unit |  |  |  |

| t <sub>INSU</sub>                                                                                 | 3.029   |                | 3.277 |                | 3.733 |                | NA  |                | ns   |  |  |  |

| t <sub>INH</sub>                                                                                  | 0.000   |                | 0.000 |                | 0.000 |                | NA  |                | ns   |  |  |  |

| t <sub>OUTCO</sub>                                                                                | 2.446   | 4.871          | 2.446 | 5.215          | 2.446 | 5.685          | NA  | NA             | ns   |  |  |  |

| t <sub>XZ</sub>                                                                                   | 2.386   | 4.745          | 2.386 | 5.083          | 2.386 | 5.561          | NA  | NA             | ns   |  |  |  |

| t <sub>ZX</sub>                                                                                   | 2.386   | 4.745          | 2.386 | 5.083          | 2.386 | 5.561          | NA  | NA             | ns   |  |  |  |

| Table 4-86. I         | Table 4–86. EP1S60 External I/O Timing on Column Pins Using Regional Clock Networks Note (1) |       |         |                |       |                |     |                |      |  |  |  |

|-----------------------|----------------------------------------------------------------------------------------------|-------|---------|----------------|-------|----------------|-----|----------------|------|--|--|--|

| Davamatav             | -5 Speed Grade                                                                               |       | -6 Spee | -6 Speed Grade |       | -7 Speed Grade |     | -8 Speed Grade |      |  |  |  |

| Parameter             | Min                                                                                          | Max   | Min     | Max            | Min   | Max            | Min | Max            | Unit |  |  |  |

| t <sub>INSU</sub>     | 2.491                                                                                        |       | 2.691   |                | 3.060 |                | NA  |                | ns   |  |  |  |

| t <sub>INH</sub>      | 0.000                                                                                        |       | 0.000   |                | 0.000 |                | NA  |                | ns   |  |  |  |

| t <sub>OUTCO</sub>    | 2.767                                                                                        | 5.409 | 2.767   | 5.801          | 2.767 | 6.358          | NA  | NA             | ns   |  |  |  |

| t <sub>XZ</sub>       | 2.707                                                                                        | 5.283 | 2.707   | 5.669          | 2.707 | 6.234          | NA  | NA             | ns   |  |  |  |

| t <sub>ZX</sub>       | 2.707                                                                                        | 5.283 | 2.707   | 5.669          | 2.707 | 6.234          | NA  | NA             | ns   |  |  |  |

| t <sub>INSUPLL</sub>  | 1.233                                                                                        |       | 1.270   |                | 1.438 |                | NA  |                | ns   |  |  |  |

| t <sub>INHPLL</sub>   | 0.000                                                                                        |       | 0.000   |                | 0.000 |                | NA  |                | ns   |  |  |  |

| t <sub>OUTCOPLL</sub> | 1.078                                                                                        | 2.278 | 1.078   | 2.395          | 1.078 | 2.428          | NA  | NA             | ns   |  |  |  |

| t <sub>XZPLL</sub>    | 1.018                                                                                        | 2.152 | 1.018   | 2.263          | 1.018 | 2.304          | NA  | NA             | ns   |  |  |  |

| t <sub>ZXPLL</sub>    | 1.018                                                                                        | 2.152 | 1.018   | 2.263          | 1.018 | 2.304          | NA  | NA             | ns   |  |  |  |

the FPGA device. The Quartus II software calculates the I/O timing for each I/O standard with a default baseline loading as specified by the I/O standard.

Altera measures clock-to-output delays ( $t_{CO}$ ) at worst-case process, minimum voltage, and maximum temperature (PVT) for the 3.3-V LVTTL I/O standard with 24 mA (default case) current drive strength setting and fast slew rate setting. I/O adder delays are measured to calculate the  $t_{CO}$  change at worst-case PVT across all I/O standards and current drive strength settings with the default loading shown in Table 4–101 on page 4–62. Timing derating data for additional loading is taken for  $t_{CO}$  across worst-case PVT for all I/O standards and drive strength settings. These three pieces of data are used to predict the timing at the output pin.

$t_{CO}$  at pin =  $t_{OUTCO}$  max for 3.3-V 24 mA LVTTL + I/O Adder + Output Delay Adder for Loading

Simulation using IBIS models is required to determine the delays on the PCB traces in addition to the output pin delay timing reported by the Quartus II software and the timing model in the device handbook.

- 1. Simulate the output driver of choice into the generalized test setup using values from Table 4–101 on page 4–62.

- Record the time to VMEAS.

- 3. Simulate the output driver of choice into the actual PCB trace and load, using the appropriate IBIS input buffer model or an equivalent capacitance value to represent the load.

- Record the time to VMEAS.

- 5. Compare the results of steps 2 and 4. The increase or decrease in delay should be added to or subtracted from the I/O Standard Output Adder delays to yield the actual worst-case propagation delay (clock-to-input) of the PCB trace.

The Quartus II software reports maximum timing with the conditions shown in Table 4–101 on page 4–62 using the proceeding equation. Figure 4–7 on page 4–62 shows the model of the circuit that is represented by the Quartus II output timing.

Tables 4–105 through 4–108 show the output adder delays associated with column and row I/O pins for both fast and slow slew rates. If an I/O standard is selected other than 3.3-V LVTTL 4mA or LVCMOS 2 mA with a fast slew rate, add the selected delay to the external  $t_{\rm OUTCO}$ ,  $t_{\rm OUTCOPLL}$ ,  $t_{\rm XZ}$ ,  $t_{\rm XZPLL}$ , and  $t_{\rm ZXPLL}$  I/O parameters shown in Table 4–55 on page 4–36 through Table 4–96 on page 4–56.

| Table 4–105. Stratix I/O Standard Output Delay Adders for Fast Slew Rate on Column Pins (Part 1 of 2) |       |                |       |         |                |     |                |     |          |      |

|-------------------------------------------------------------------------------------------------------|-------|----------------|-------|---------|----------------|-----|----------------|-----|----------|------|

| Donomo                                                                                                |       | -5 Speed Grade |       | -6 Spee | -6 Speed Grade |     | -7 Speed Grade |     | ed Grade | 11   |

| Parame                                                                                                | ter   | Min            | Max   | Min     | Max            | Min | Max            | Min | Max      | Unit |

| LVCMOS                                                                                                | 2 mA  |                | 1,895 |         | 1,990          |     | 1,990          |     | 1,990    | ps   |

|                                                                                                       | 4 mA  |                | 956   |         | 1,004          |     | 1,004          |     | 1,004    | ps   |

|                                                                                                       | 8 mA  |                | 189   |         | 198            |     | 198            |     | 198      | ps   |

|                                                                                                       | 12 mA |                | 0     |         | 0              |     | 0              |     | 0        | ps   |

|                                                                                                       | 24 mA |                | -157  |         | -165           |     | -165           |     | -165     | ps   |

| 3.3-V LVTTL                                                                                           | 4 mA  |                | 1,895 |         | 1,990          |     | 1,990          |     | 1,990    | ps   |

|                                                                                                       | 8 mA  |                | 1,347 |         | 1,414          |     | 1,414          |     | 1,414    | ps   |

|                                                                                                       | 12 mA |                | 636   |         | 668            |     | 668            |     | 668      | ps   |

|                                                                                                       | 16 mA |                | 561   |         | 589            |     | 589            |     | 589      | ps   |

|                                                                                                       | 24 mA |                | 0     |         | 0              |     | 0              |     | 0        | ps   |

| 2.5-V LVTTL                                                                                           | 2 mA  |                | 2,517 |         | 2,643          |     | 2,643          |     | 2,643    | ps   |

|                                                                                                       | 8 mA  |                | 834   |         | 875            |     | 875            |     | 875      | ps   |

|                                                                                                       | 12 mA |                | 504   |         | 529            |     | 529            |     | 529      | ps   |

|                                                                                                       | 16 mA |                | 194   |         | 203            |     | 203            |     | 203      | ps   |

| 1.8-V LVTTL                                                                                           | 2 mA  |                | 1,304 |         | 1,369          |     | 1,369          |     | 1,369    | ps   |

|                                                                                                       | 8 mA  |                | 960   |         | 1,008          |     | 1,008          |     | 1,008    | ps   |

|                                                                                                       | 12 mA |                | 960   |         | 1,008          |     | 1,008          |     | 1,008    | ps   |

| 1.5-V LVTTL                                                                                           | 2 mA  |                | 6,680 |         | 7,014          |     | 7,014          |     | 7,014    | ps   |

|                                                                                                       | 4 mA  |                | 3,275 |         | 3,439          |     | 3,439          |     | 3,439    | ps   |

|                                                                                                       | 8 mA  |                | 1,589 |         | 1,668          |     | 1,668          |     | 1,668    | ps   |

| GTL                                                                                                   | •     |                | 16    |         | 17             |     | 17             |     | 17       | ps   |

| GTL+                                                                                                  |       |                | 9     |         | 9              |     | 9              |     | 9        | ps   |

| 3.3-V PCI                                                                                             |       |                | 50    |         | 52             |     | 52             |     | 52       | ps   |

| 3.3-V PCI-X 1.0                                                                                       | )     |                | 50    |         | 52             |     | 52             |     | 52       | ps   |

| Compact PCI                                                                                           |       |                | 50    |         | 52             |     | 52             |     | 52       | ps   |

| AGP 1×                                                                                                |       |                | 50    |         | 52             |     | 52             |     | 52       | ps   |

| AGP 2×                                                                                                |       |                | 1,895 |         | 1,990          |     | 1,990          |     | 1,990    | ps   |

**Table 4–110. Stratix IOE Programmable Delays on Row Pins** Note (1) -5 Speed Grade -6 Speed Grade -7 Speed Grade -8 Speed Grade **Parameter** Settina Unit Min Max Min Max Min Max Min Max Decrease input delay Off 3,970 4,367 5,022 5,908 ps to internal cells Small 3,390 3.729 4,288 5,045 ps 2.810 3.091 3.554 Medium 4.181 ps Large 173 181 208 245 ps On 173 181 208 245 ps Decrease input delay Off 3.900 4.290 4.933 5,804 ps to input register On 0 0 0 0 ps Decrease input delay Off 1.240 1.364 1.568 1.845 ps to output register On 0 0 0 0 ps Increase delay to Off 0 0 0 0 ps output pin On 397 417 417 417 ps Increase delay to Off 0 0 0 0 ps output enable pin 383 441 On 348 518 ps 0 Increase output clock Off 0 0 0 ps enable delay 180 227 Small 198 267 ps Large 260 286 328 386 ps On 260 286 328 386 ps Increase input clock Off 0 0 0 0 ps enable delay Small 180 198 227 267 ps Large 260 286 328 386 ps On 260 286 328 386 ps Off Increase output 0 0 0 0 ps enable clock enable Small 540 594 683 804 ps delav 1.285 Large 1.016 1.118 1,512 ps On 1,016 1,118 1,285 1,512 ps Increase tzx delay to Off 0 0 0 0 ps output pin On 1.993 2.092 2.092 2.092 ps

Note to Table 4-109 and Table 4-110:

<sup>(1)</sup> The delay chain delays vary for different device densities. These timing values only apply to EP1S30 and EP1S40 devices. Reference the timing information reported by the Quartus II software for other devices.

Table 4–121. Stratix Maximum Output Clock Rate (Using I/O Pins) for PLL[1, 2, 3, 4] Pins in Flip-Chip Packages

| I/O Standard                  | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------|-------------------|-------------------|-------------------|-------------------|------|

| LVTTL                         | 400               | 350               | 300               | 300               | MHz  |

| 2.5 V                         | 400               | 350               | 300               | 300               | MHz  |

| 1.8 V                         | 400               | 350               | 300               | 300               | MHz  |

| 1.5 V                         | 350               | 300               | 300               | 300               | MHz  |

| LVCMOS                        | 400               | 350               | 300               | 300               | MHz  |

| GTL                           | 200               | 167               | 125               | 125               | MHz  |

| GTL+                          | 200               | 167               | 125               | 125               | MHz  |

| SSTL-3 Class I                | 167               | 150               | 133               | 133               | MHz  |

| SSTL-3 Class II               | 167               | 150               | 133               | 133               | MHz  |

| SSTL-2 Class I                | 150               | 133               | 133               | 133               | MHz  |

| SSTL-2 Class II               | 150               | 133               | 133               | 133               | MHz  |

| SSTL-18 Class I               | 150               | 133               | 133               | 133               | MHz  |

| SSTL-18 Class II              | 150               | 133               | 133               | 133               | MHz  |

| 1.5-V HSTL Class I            | 250               | 225               | 200               | 200               | MHz  |

| 1.5-V HSTL Class II           | 225               | 225               | 200               | 200               | MHz  |

| 1.8-V HSTL Class I            | 250               | 225               | 200               | 200               | MHz  |

| 1.8-V HSTL Class II           | 225               | 225               | 200               | 200               | MHz  |

| 3.3-V PCI                     | 250               | 225               | 200               | 200               | MHz  |

| 3.3-V PCI-X 1.0               | 225               | 225               | 200               | 200               | MHz  |

| Compact PCI                   | 400               | 350               | 300               | 300               | MHz  |

| AGP 1×                        | 400               | 350               | 300               | 300               | MHz  |

| AGP 2×                        | 400               | 350               | 300               | 300               | MHz  |

| CTT                           | 300               | 250               | 200               | 200               | MHz  |

| LVPECL (2)                    | 717               | 717               | 500               | 500               | MHz  |

| PCML (2)                      | 420               | 420               | 420               | 420               | MHz  |

| LVDS (2)                      | 717               | 717               | 500               | 500               | MHz  |

| HyperTransport technology (2) | 420               | 420               | 420               | 420               | MHz  |

# Table 4–123. Stratix Maximum Output Clock Rate (Using I/O Pins) for PLL[1, 2, 3, 4] Pins in Wire-Bond Packages (Part 2 of 2)

| I/O Standard                  | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |  |  |

|-------------------------------|-------------------|-------------------|-------------------|------|--|--|

| LVDS (2)                      | 400               | 311               | 311               | MHz  |  |  |

| HyperTransport technology (2) | 420               | 400               | 400               | MHz  |  |  |

#### Notes to Tables 4-120 through 4-123:

- (1) Differential SSTL-2 outputs are only available on column clock pins.

- (2) These parameters are only available on row I/O pins.

- (3) SSTL-2 in maximum drive strength condition. See Table 4–101 on page 4–62 for more information on exact loading conditions for each I/O standard.

- (4) SSTL-2 in minimum drive strength with  $\leq$ 10pF output load condition.

- (5) SSTL-2 in minimum drive strength with > 10pF output load condition.

- (6) Differential SSTL-2 outputs are only supported on column clock pins.