Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 1057                                                    |

| Number of Logic Elements/Cells | 10570                                                   |

| Total RAM Bits                 | 920448                                                  |

| Number of I/O                  | 345                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                         |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 672-BBGA                                                |

| Supplier Device Package        | 672-FBGA (27x27)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s10f672c6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

vi Altera Corporation

# **Chapter Revision Dates**

The chapters in this book, *Stratix Device Handbook*, *Volume 1*, were revised on the following dates. Where chapters or groups of chapters are available separately, part numbers are listed.

Chapter 1. Introduction

Revised: July 2005 Part number: S51001-3.2

Chapter 2. Stratix Architecture

Revised: July 2005 Part number: S51002-3.2

Chapter 3. Configuration & Testing

Revised: July 2005 Part number: S51003-1.3

Chapter 4. DC & Switching Characteristics

Revised: January 2006 Part number: S51004-3.4

Chapter 5. Reference & Ordering Information

Revised: September 2004 Part number: S51005-2.1

Altera Corporation vii

Figure 2-2. Stratix LAB Structure

#### LAB Interconnects

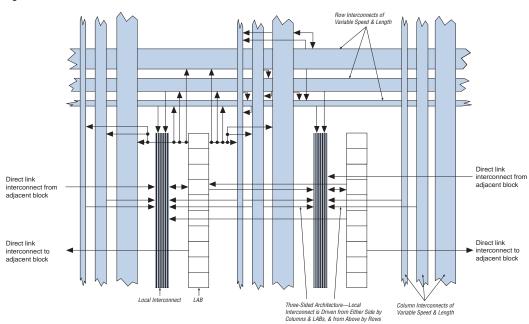

The LAB local interconnect can drive LEs within the same LAB. The LAB local interconnect is driven by column and row interconnects and LE outputs within the same LAB. Neighboring LABs, M512 RAM blocks, M4K RAM blocks, or DSP blocks from the left and right can also drive an LAB's local interconnect through the direct link connection. The direct link connection feature minimizes the use of row and column interconnects, providing higher performance and flexibility. Each LE can drive 30 other LEs through fast local and direct link interconnects. Figure 2–3 shows the direct link connection.

Direct link interconnect from

left LAB, TriMatrix memory

block, DSP block, or IOE output

Direct link interconnect from

right LAB, TriMatrix memory

block, DSP block, or IOE output

Direct link interconnect from

right LAB, TriMatrix memory

block, DSP block, or IOE output

Direct link interconnect from

right LAB, TriMatrix memory

block, DSP block, or IOE output

Figure 2-3. Direct Link Connection

### **LAB Control Signals**

Each LAB contains dedicated logic for driving control signals to its LEs. The control signals include two clocks, two clock enables, two asynchronous clears, synchronous clear, asynchronous preset/load, synchronous load, and add/subtract control signals. This gives a maximum of 10 control signals at a time. Although synchronous load and clear signals are generally used when implementing counters, they can also be used with other functions.

Each LAB can use two clocks and two clock enable signals. Each LAB's clock and clock enable signals are linked. For example, any LE in a particular LAB using the labclk1 signal will also use labclkena1. If the LAB uses both the rising and falling edges of a clock, it also uses both LAB-wide clock signals. De-asserting the clock enable signal will turn off the LAB-wide clock.

Each LAB can use two asynchronous clear signals and an asynchronous load/preset signal. The asynchronous load acts as a preset when the asynchronous load data input is tied high.

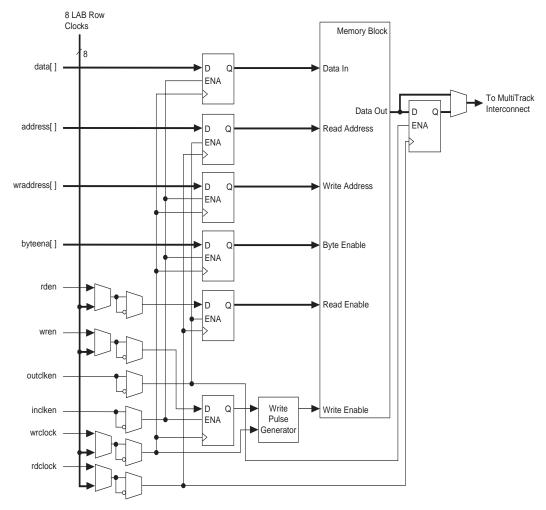

Figure 2-27. Read/Write Clock Mode in Simple Dual-Port Mode Notes (1), (2)

#### Notes to Figure 2-27:

- (1) All registers shown except the rden register have asynchronous clear ports.

- (2) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

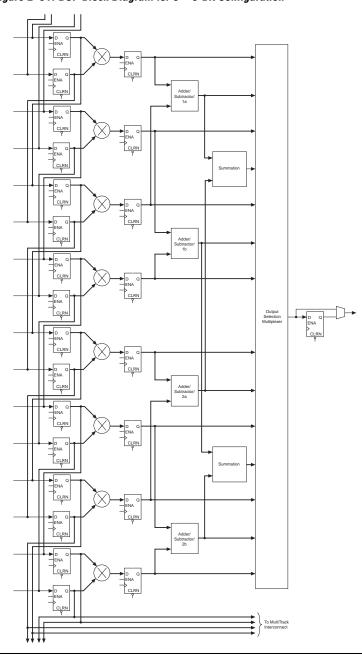

Figure 2–31. DSP Block Diagram for  $9 \times 9$ -Bit Configuration

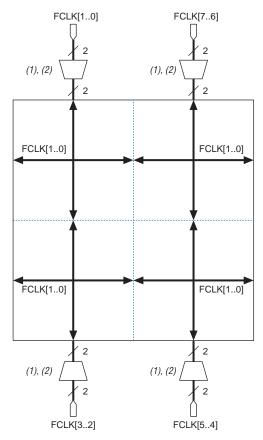

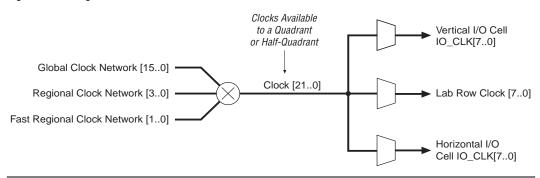

There are 16 dedicated clock pins (CLK [15..0]) to drive either the global or regional clock networks. Four clock pins drive each side of the device, as shown in Figure 2–42. Enhanced and fast PLL outputs can also drive the global and regional clock networks.

#### Global Clock Network

These clocks drive throughout the entire device, feeding all device quadrants. The global clock networks can be used as clock sources for all resources within the device—IOEs, LEs, DSP blocks, and all memory blocks. These resources can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin. The global clock networks can also be driven by internal logic for internally generated global clocks and asynchronous clears, clock enables, or other control signals with large fanout. Figure 2–42 shows the 16 dedicated CLK pins driving global clock networks.

Figure 2–44. EP1S25, EP1S20 & EP1S10 Device Fast Clock Pin Connections to Fast Regional Clocks

#### Notes to Figure 2-44:

- (1) This is a set of two multiplexers.

- (2) In addition to the FCLK pin inputs, there is also an input from the I/O interconnect.

Figure 2-46. Regional Clock Bus

IOE clocks have horizontal and vertical block regions that are clocked by eight I/O clock signals chosen from the 22 quadrant or half-quadrant clock resources. Figures 2–47 and 2–48 show the quadrant and half-quadrant relationship to the I/O clock regions, respectively. The vertical regions (column pins) have less clock delay than the horizontal regions (row pins).

During switchover, the PLL VCO continues to run and will either slow down or speed up, generating frequency drift on the PLL outputs. The clock switchover transitions without any glitches. After the switch, there is a finite resynchronization period to lock onto new clock as the VCO ramps up. The exact amount of time it takes for the PLL to relock relates to the PLL configuration and may be adjusted by using the programmable bandwidth feature of the PLL. The specification for the maximum time to relock is  $100~\mu s$ .

For more information on clock switchover, see *AN 313, Implementing Clock Switchover in Stratix & Stratix GX Devices*.

#### PLL Reconfiguration

The PLL reconfiguration feature enables system logic to change Stratix device enhanced PLL counters and delay elements without reloading a Programmer Object File (.pof). This provides considerable flexibility for frequency synthesis, allowing real-time PLL frequency and output clock delay variation. You can sweep the PLL output frequencies and clock delay in prototype environments. The PLL reconfiguration feature can also dynamically or intelligently control system clock speeds or  $t_{\rm CO}$  delays in end systems.

Clock delay elements at each PLL output port implement variable delay. Figure 2–54 shows a diagram of the overall dynamic PLL control feature for the counters and the clock delay elements. The configuration time is less than 20 µs for the enhanced PLL using a input shift clock rate of 22 MHz. The charge pump, loop filter components, and phase shifting using VCO phase taps cannot be dynamically adjusted.

Any of the four external output counters can drive the single-ended or differential clock outputs for PLLs 5 and 6. This means one counter or frequency can drive all output pins available from PLL 5 or PLL 6. Each pair of output pins (four pins total) has dedicated VCC and GND pins to reduce the output clock's overall jitter by providing improved isolation from switching I/O pins.

For PLLs 5 and 6, each pin of a single-ended output pair can either be in phase or 180° out of phase. The clock output pin pairs support the same I/O standards as standard output pins (in the top and bottom banks) as well as LVDS, LVPECL, 3.3-V PCML, HyperTransport technology, differential HSTL, and differential SSTL. Table 2–20 shows which I/O standards the enhanced PLL clock pins support. When in single-ended or differential mode, the two outputs operate off the same power supply. Both outputs use the same standards in single-ended mode to maintain performance. You can also use the external clock output pins as user output pins if external enhanced PLL clocking is not needed.

| Table 2–20. I/O Standards Supported for Enhanced PLL Pins (Part 1 of 2) |          |          |           |        |  |  |  |  |  |  |

|-------------------------------------------------------------------------|----------|----------|-----------|--------|--|--|--|--|--|--|

| L/O Ctondovd                                                            |          | Input    |           |        |  |  |  |  |  |  |

| I/O Standard                                                            | INCLK    | FBIN     | PLLENABLE | EXTCLK |  |  |  |  |  |  |

| LVTTL                                                                   | <b>✓</b> | <b>✓</b> | <b>✓</b>  | ✓      |  |  |  |  |  |  |

| LVCMOS                                                                  | <b>✓</b> | <b>✓</b> | ✓         | ✓      |  |  |  |  |  |  |

| 2.5 V                                                                   | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |  |  |

| 1.8 V                                                                   | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |  |  |

| 1.5 V                                                                   | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |  |  |

| 3.3-V PCI                                                               | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |  |  |

| 3.3-V PCI-X 1.0                                                         | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |  |  |

| LVPECL                                                                  | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |  |  |

| 3.3-V PCML                                                              | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |  |  |

| LVDS                                                                    | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |  |  |

| HyperTransport technology                                               | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |  |  |

| Differential HSTL                                                       | <b>✓</b> |          |           | ✓      |  |  |  |  |  |  |

| Differential SSTL                                                       |          |          |           | ✓      |  |  |  |  |  |  |

| 3.3-V GTL                                                               | <b>✓</b> | ✓        |           | ✓      |  |  |  |  |  |  |

| 3.3-V GTL+                                                              | <b>✓</b> | ✓        |           | ✓      |  |  |  |  |  |  |

| 1.5-V HSTL Class I                                                      | <b>✓</b> | ✓        |           | ✓      |  |  |  |  |  |  |

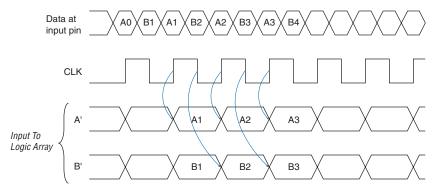

Figure 2-66. Input Timing Diagram in DDR Mode

When using the IOE for DDR outputs, the two output registers are configured to clock two data paths from LEs on rising clock edges. These output registers are multiplexed by the clock to drive the output pin at a  $\times 2$  rate. One output register clocks the first bit out on the clock high time, while the other output register clocks the second bit out on the clock low time. Figure 2–67 shows the IOE configured for DDR output. Figure 2–68 shows the DDR output timing diagram.

Table 2–28 shows the possible settings for the I/O standards with drive strength control.

| Table 2–28. Programmable Drive                                                                                                  | Strength                                                        |

|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| I/O Standard                                                                                                                    | I <sub>OH</sub> / I <sub>OL</sub> Current Strength Setting (mA) |

| 3.3-V LVTTL                                                                                                                     | 24 (1), 16, 12, 8, 4                                            |

| 3.3-V LVCMOS                                                                                                                    | 24 (2), 12 (1), 8, 4, 2                                         |

| 2.5-V LVTTL/LVCMOS                                                                                                              | 16 (1), 12, 8, 2                                                |

| 1.8-V LVTTL/LVCMOS                                                                                                              | 12 (1), 8, 2                                                    |

| 1.5-V LVCMOS                                                                                                                    | 8 (1), 4, 2                                                     |

| GTL/GTL+ 1.5-V HSTL Class I and II 1.8-V HSTL Class I and II SSTL-3 Class I and II SSTL-2 Class I and II SSTL-18 Class I and II | Support max and min strength                                    |

Notes to Table 2-28:

- (1) This is the Quartus II software default current setting.

- (2) I/O banks 1, 2, 5, and 6 do not support this setting.

Quartus II software version 4.2 and later will report current strength as "PCI Compliant" for 3.3-V PCI, 3.3-V PCI-X 1.0, and Compact PCI I/O standards.

Stratix devices support series on-chip termination (OCT) using programmable drive strength. For more information, contact your Altera Support Representative.

## Open-Drain Output

Stratix devices provide an optional open-drain (equivalent to an open-collector) output for each I/O pin. This open-drain output enables the device to provide system-level control signals (e.g., interrupt and write-enable signals) that can be asserted by any of several devices.

#### Slew-Rate Control

The output buffer for each Stratix device I/O pin has a programmable output slew-rate control that can be configured for low-noise or high-speed performance. A faster slew rate provides high-speed transitions for high-performance systems. However, these fast transitions may introduce noise transients into the system. A slow slew rate reduces system noise, but adds a nominal delay to rising and falling edges. Each

| Symbol            | Parameter                                          | Parameter Conditions |              | Maximum           | Unit |  |

|-------------------|----------------------------------------------------|----------------------|--------------|-------------------|------|--|

| V <sub>CCIO</sub> | Supply voltage for output buffers, 3.3-V operation | (4), (5)             | 3.00 (3.135) | 3.60 (3.465)      | V    |  |

|                   | Supply voltage for output buffers, 2.5-V operation | (4)                  | 2.375        | 2.625             | ٧    |  |

|                   | Supply voltage for output buffers, 1.8-V operation | (4)                  | 1.71         | 1.89              | ٧    |  |

|                   | Supply voltage for output buffers, 1.5-V operation | (4)                  | 1.4          | 1.6               | ٧    |  |

| VI                | Input voltage                                      | (3), (6)             | -0.5         | 4.0               | V    |  |

| V <sub>O</sub>    | Output voltage                                     |                      | 0            | V <sub>CCIO</sub> | V    |  |

| TJ                | Operating junction                                 | For commercial use   | 0            | 85                | °C   |  |

|                   | temperature                                        | For industrial use   | -40          | 100               | °C   |  |

| Table 4–3        | . Stratix Device DC 0                         | perating Conditions Note (7                                  | (Part 1 of 2) |         |         |      |

|------------------|-----------------------------------------------|--------------------------------------------------------------|---------------|---------|---------|------|

| Symbol           | Parameter                                     | Conditions                                                   | Minimum       | Typical | Maximum | Unit |

| I <sub>I</sub>   | Input pin leakage current                     | $V_I = V_{CCIOmax}$ to 0 V (8)                               | -10           |         | 10      | μА   |

| I <sub>OZ</sub>  | Tri-stated I/O pin leakage current            | V <sub>O</sub> = V <sub>CCIOmax</sub> to 0 V (8)             | -10           |         | 10      | μА   |

| I <sub>CC0</sub> | V <sub>CC</sub> supply current (standby) (All | V <sub>I</sub> = ground, no load, no toggling inputs         |               |         |         | mA   |

|                  | memory blocks in power-down mode)             | EP1S10. V <sub>I</sub> = ground, no load, no toggling inputs |               | 37      |         | mA   |

|                  |                                               | EP1S20. V <sub>I</sub> = ground, no load, no toggling inputs |               | 65      |         | mA   |

|                  |                                               | EP1S25. V <sub>I</sub> = ground, no load, no toggling inputs |               | 90      |         | mA   |

|                  |                                               | EP1S30. V <sub>I</sub> = ground, no load, no toggling inputs |               | 114     |         | mA   |

|                  |                                               | EP1S40. V <sub>I</sub> = ground, no load, no toggling inputs |               | 145     |         | mA   |

|                  |                                               | EP1S60. V <sub>I</sub> = ground, no load, no toggling inputs |               | 200     |         | mA   |

|                  |                                               | EP1S80. V <sub>I</sub> = ground, no load, no toggling inputs |               | 277     |         | mA   |

| Table 4–3.        | Table 4–3. Stratix Device DC Operating Conditions Note (7) (Part 2 of 2) |                                 |    |  |     |    |  |  |  |  |  |

|-------------------|--------------------------------------------------------------------------|---------------------------------|----|--|-----|----|--|--|--|--|--|

| Symbol            | Symbol Parameter Conditions Minimum Typical Maximum Uni                  |                                 |    |  |     |    |  |  |  |  |  |

| R <sub>CONF</sub> | Value of I/O pin pull-                                                   | $V_{CCIO} = 3.0 V (9)$          | 20 |  | 50  | kΩ |  |  |  |  |  |

|                   | up resistor before and during                                            | V <sub>CCIO</sub> = 2.375 V (9) | 30 |  | 80  | kΩ |  |  |  |  |  |

|                   | configuration                                                            | V <sub>CCIO</sub> = 1.71 V (9)  | 60 |  | 150 | kΩ |  |  |  |  |  |

| Table 4-4.        | Table 4–4. LVTTL Specifications |                                                |         |         |      |  |  |  |  |  |  |  |

|-------------------|---------------------------------|------------------------------------------------|---------|---------|------|--|--|--|--|--|--|--|

| Symbol            | Parameter                       | Conditions                                     | Minimum | Maximum | Unit |  |  |  |  |  |  |  |

| V <sub>CCIO</sub> | Output supply voltage           |                                                | 3.0     | 3.6     | V    |  |  |  |  |  |  |  |

| V <sub>IH</sub>   | High-level input voltage        |                                                | 1.7     | 4.1     | V    |  |  |  |  |  |  |  |

| V <sub>IL</sub>   | Low-level input voltage         |                                                | -0.5    | 0.7     | V    |  |  |  |  |  |  |  |

| V <sub>OH</sub>   | High-level output voltage       | $I_{OH} = -4 \text{ to } -24 \text{ mA } (10)$ | 2.4     |         | V    |  |  |  |  |  |  |  |

| V <sub>OL</sub>   | Low-level output voltage        | I <sub>OL</sub> = 4 to 24 mA (10)              |         | 0.45    | V    |  |  |  |  |  |  |  |

| Table 4–5.        | LVCMOS Specifications     |                                              |                         |         |      |

|-------------------|---------------------------|----------------------------------------------|-------------------------|---------|------|

| Symbol            | Parameter                 | Conditions                                   | Minimum                 | Maximum | Unit |

| V <sub>CCIO</sub> | Output supply voltage     |                                              | 3.0                     | 3.6     | V    |

| V <sub>IH</sub>   | High-level input voltage  |                                              | 1.7                     | 4.1     | V    |

| V <sub>IL</sub>   | Low-level input voltage   |                                              | -0.5                    | 0.7     | V    |

| V <sub>OH</sub>   | High-level output voltage | $V_{CCIO} = 3.0,$ $I_{OH} = -0.1 \text{ mA}$ | V <sub>CCIO</sub> - 0.2 |         | V    |

| V <sub>OL</sub>   | Low-level output voltage  | $V_{CCIO} = 3.0,$ $I_{OL} = 0.1 \text{ mA}$  |                         | 0.2     | V    |

| Table 4–6.        | 2.5-V I/O Specifications  |                              |         |         |      |

|-------------------|---------------------------|------------------------------|---------|---------|------|

| Symbol            | Parameter                 | Conditions                   | Minimum | Maximum | Unit |

| V <sub>CCIO</sub> | Output supply voltage     |                              | 2.375   | 2.625   | V    |

| V <sub>IH</sub>   | High-level input voltage  |                              | 1.7     | 4.1     | V    |

| V <sub>IL</sub>   | Low-level input voltage   |                              | -0.5    | 0.7     | V    |

| V <sub>OH</sub>   | High-level output voltage | I <sub>OH</sub> = -1 mA (10) | 2.0     |         | V    |

| V <sub>OL</sub>   | Low-level output voltage  | I <sub>OL</sub> = 1 mA (10)  |         | 0.4     | V    |

| Table 4–31       | . CTT I/O Specifications                       |                                           |                        |         |                        |      |

|------------------|------------------------------------------------|-------------------------------------------|------------------------|---------|------------------------|------|

| Symbol           | Parameter                                      | Conditions                                | Minimum                | Typical | Maximum                | Unit |

| $V_{CCIO}$       | Output supply voltage                          |                                           | 2.05                   | 3.3     | 3.6                    | V    |

| $V_{TT}/V_{REF}$ | Termination and input reference voltage        |                                           | 1.35                   | 1.5     | 1.65                   | V    |

| V <sub>IH</sub>  | High-level input voltage                       |                                           | V <sub>REF</sub> + 0.2 |         |                        | V    |

| V <sub>IL</sub>  | Low-level input voltage                        |                                           |                        |         | V <sub>REF</sub> - 0.2 | V    |

| V <sub>OH</sub>  | High-level output voltage                      | $I_{OH} = -8 \text{ mA}$                  | V <sub>REF</sub> + 0.4 |         |                        | V    |

| V <sub>OL</sub>  | Low-level output voltage                       | I <sub>OL</sub> = 8 mA                    |                        |         | V <sub>REF</sub> - 0.4 | V    |

| Io               | Output leakage current (when output is high Z) | GND ≤V <sub>OUT</sub> ≤ V <sub>CCIO</sub> | -10                    |         | 10                     | μΑ   |

| Table 4–32. Bus Hold Parameters |                                                |       |      |       |                   |                 |      |       |      |      |

|---------------------------------|------------------------------------------------|-------|------|-------|-------------------|-----------------|------|-------|------|------|

|                                 |                                                |       |      |       | V <sub>CCIO</sub> | Level           |      |       |      |      |

| Parameter                       | Conditions                                     | 1.5 V |      | 1.8 V |                   | 2.5 V           |      | 3.3 V |      | Unit |

|                                 |                                                | Min   | Max  | Min   | Max               | Min             | Max  | Min   | Max  |      |

| Low sustaining current          | $V_{IN} > V_{IL}$ (maximum)                    | 25    |      | 30    |                   | 50              |      | 70    |      | μА   |

| High sustaining current         | V <sub>IN</sub> < V <sub>IH</sub><br>(minimum) | -25   |      | -30   |                   | <del>-</del> 50 |      | -70   |      | μА   |

| Low overdrive current           | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      |       | 160  |       | 200               |                 | 300  |       | 500  | μА   |

| High overdrive current          | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      |       | -160 |       | -200              |                 | -300 |       | -500 | μА   |

| Bus-hold trip point             |                                                | 0.5   | 1.0  | 0.68  | 1.07              | 0.7             | 1.7  | 0.8   | 2.0  | V    |

|                       | -5 Spee | d Grade | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |     |      |

|-----------------------|---------|---------|----------------|-------|----------------|-------|----------------|-----|------|

| Parameter             | Min     | Max     | Min            | Max   | Min            | Max   | Min            | Max | Unit |

| t <sub>INSU</sub>     | 1.351   |         | 1.479          |       | 1.699          |       | NA             |     | ns   |

| t <sub>INH</sub>      | 0.000   |         | 0.000          |       | 0.000          |       | NA             |     | ns   |

| t <sub>outco</sub>    | 2.732   | 5.380   | 2.732          | 5.728 | 2.732          | 6.240 | NA             | NA  | ns   |

| t <sub>XZ</sub>       | 2.672   | 5.254   | 2.672          | 5.596 | 2.672          | 6.116 | NA             | NA  | ns   |

| t <sub>ZX</sub>       | 2.672   | 5.254   | 2.672          | 5.596 | 2.672          | 6.116 | NA             | NA  | ns   |

| t <sub>INSUPLL</sub>  | 0.923   |         | 0.971          |       | 1.098          |       | NA             |     | ns   |

| t <sub>INHPLL</sub>   | 0.000   |         | 0.000          |       | 0.000          |       | NA             |     | ns   |

| t <sub>OUTCOPLL</sub> | 1.210   | 2.544   | 1.210          | 2.648 | 1.210          | 2.715 | NA             | NA  | ns   |

| t <sub>XZPLL</sub>    | 1.150   | 2.418   | 1.150          | 2.516 | 1.150          | 2.591 | NA             | NA  | ns   |

| t <sub>ZXPLL</sub>    | 1.150   | 2.418   | 1.150          | 2.516 | 1.150          | 2.591 | NA             | NA  | ns   |

| Table 4–64. EP1S20 External I/O Timing on Row Pins Using Fast Regional Clock Networks Note (1) |                |       |                |       |                |       |                |     |       |

|------------------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-----|-------|

| Parameter                                                                                      | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |     | 11-24 |

|                                                                                                | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max | Unit  |

| t <sub>INSU</sub>                                                                              | 2.032          |       | 2.207          |       | 2.535          |       | NA             |     | ns    |

| t <sub>INH</sub>                                                                               | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns    |

| t <sub>OUTCO</sub>                                                                             | 2.492          | 5.018 | 2.492          | 5.355 | 2.492          | 5.793 | NA             | NA  | ns    |

| t <sub>XZ</sub>                                                                                | 2.519          | 5.072 | 2.519          | 5.411 | 2.519          | 5.861 | NA             | NA  | ns    |

| t <sub>ZX</sub>                                                                                | 2.519          | 5.072 | 2.519          | 5.411 | 2.519          | 5.861 | NA             | NA  | ns    |

#### Skew on Input Pins

Table 4–99 shows the package skews that were considered to get the worst case I/O skew value. You can use these values, for example, when calculating the timing budget on the input (read) side of a memory interface.

| Table 4–99. Package Skew on Input Pins         |                      |  |  |  |  |

|------------------------------------------------|----------------------|--|--|--|--|

| Package Parameter                              | Worst-Case Skew (ps) |  |  |  |  |

| Pins in the same I/O bank                      | 50                   |  |  |  |  |

| Pins in top/bottom (vertical I/O) banks        | 50                   |  |  |  |  |

| Pins in left/right side (horizontal I/O) banks | 50                   |  |  |  |  |

| Pins across the entire device                  | 100                  |  |  |  |  |

#### PLL Counter & Clock Network Skews

Table 4–100 shows the clock skews between different clock outputs from the Stratix device PLL.

| Table 4–100. PLL Counter & Clock Network Skews                                                        |                      |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|--|

| Parameter                                                                                             | Worst-Case Skew (ps) |  |  |  |  |  |

| Clock skew between two external clock outputs driven by the same counter                              | 100                  |  |  |  |  |  |

| Clock skew between two external clock outputs driven by the different counters with the same settings | 150                  |  |  |  |  |  |

| Dual-purpose PLL dedicated clock output used as I/O pin vs. regular I/O pin                           | 270 (1)              |  |  |  |  |  |

| Clock skew between any two outputs of the PLL that drive global clock networks                        | 150                  |  |  |  |  |  |

Note to Table 4-100:

(1) The Quartus II software models 270 ps of delay on the PLL dedicated clock output (PLL6\_OUT[3..0]p/n and PLL5\_OUT[3..0]p/n) pins both when used as clocks and when used as I/O pins.

## I/O Timing Measurement Methodology

Different I/O standards require different baseline loading techniques for reporting timing delays. Altera characterizes timing delays with the required termination and loading for each I/O standard. The timing information is specified from the input clock pin up to the output pin of

Output

Buffer

OUTPUT

VMEAS

R<sub>UP</sub>

R<sub>S</sub>

R<sub>DN</sub>

C<sub>L</sub>

GND

Figure 4-7. Output Delay Timing Reporting Setup Modeled by Quartus II

#### *Notes to Figure 4–7:*

- Output pin timing is reported at the output pin of the FPGA device. Additional delays for loading and board trace delay need to be accounted for with IBIS model simulations.

- (2)  $V_{CCINT}$  is 1.42-V unless otherwise specified.

**Table 4–101.** Reporting Methodology For Maximum Timing For Single-Ended Output Pins (Part 1 of 2) Notes (1), (2), (3)

| 1/2.01                | Loading and Termination |          |                |                     |                          |            |                        | Measurement<br>Point |

|-----------------------|-------------------------|----------|----------------|---------------------|--------------------------|------------|------------------------|----------------------|

| I/O Standard          | R <sub>UP</sub>         | $R_{DN}$ | R <sub>S</sub> | R <sub>T</sub><br>Ω | V <sub>CCIO</sub><br>(V) | VTT<br>(V) | C <sub>L</sub><br>(pF) | V <sub>MEAS</sub>    |

| 3.3-V LVTTL           | -                       | -        | 0              | -                   | 2.950                    | 2.95       | 10                     | 1.500                |

| 2.5-V LVTTL           | -                       | -        | 0              | -                   | 2.370                    | 2.37       | 10                     | 1.200                |

| 1.8-V LVTTL           | -                       | -        | 0              | -                   | 1.650                    | 1.65       | 10                     | 0.880                |

| 1.5-V LVTTL           | -                       | -        | 0              | -                   | 1.400                    | 1.40       | 10                     | 0.750                |

| 3.3-V LVCMOS          | _                       | _        | 0              | _                   | 2.950                    | 2.95       | 10                     | 1.500                |

| 2.5-V LVCMOS          | _                       | _        | 0              | _                   | 2.370                    | 2.37       | 10                     | 1.200                |

| 1.8-V LVCMOS          | -                       | -        | 0              | -                   | 1.650                    | 1.65       | 10                     | 0.880                |

| 1.5-V LVCMOS          | _                       | _        | 0              | _                   | 1.400                    | 1.40       | 10                     | 0.750                |

| 3.3-V GTL             | _                       | -        | 0              | 25                  | 2.950                    | 1.14       | 30                     | 0.740                |

| 2.5-V GTL             | _                       | _        | 0              | 25                  | 2.370                    | 1.14       | 30                     | 0.740                |

| 3.3-V GTL+            | _                       | _        | 0              | 25                  | 2.950                    | 1.35       | 30                     | 0.880                |

| 2.5-V GTL+            | _                       | _        | 0              | 25                  | 2.370                    | 1.35       | 30                     | 0.880                |

| 3.3-V SSTL-3 Class II | _                       | _        | 25             | 25                  | 2.950                    | 1.25       | 30                     | 1.250                |

**Table 4–110. Stratix IOE Programmable Delays on Row Pins** Note (1) -5 Speed Grade -6 Speed Grade -7 Speed Grade -8 Speed Grade **Parameter** Settina Unit Min Max Min Max Min Max Min Max Decrease input delay Off 3,970 4,367 5,022 5,908 ps to internal cells Small 3,390 3.729 4,288 5,045 ps 2.810 3.091 3.554 Medium 4.181 ps Large 173 181 208 245 ps On 173 181 208 245 ps Decrease input delay Off 3.900 4.290 4.933 5,804 ps to input register On 0 0 0 0 ps Decrease input delay Off 1.240 1.364 1.568 1.845 ps to output register On 0 0 0 0 ps Increase delay to Off 0 0 0 0 ps output pin On 397 417 417 417 ps Increase delay to Off 0 0 0 0 ps output enable pin 383 441 On 348 518 ps 0 Increase output clock Off 0 0 0 ps enable delay 180 227 Small 198 267 ps Large 260 286 328 386 ps On 260 286 328 386 ps Increase input clock Off 0 0 0 0 ps enable delay Small 180 198 227 267 ps Large 260 286 328 386 ps On 260 286 328 386 ps Off Increase output 0 0 0 0 ps enable clock enable Small 540 594 683 804 ps delav 1.285 Large 1.016 1.118 1,512 ps On 1,016 1,118 1,285 1,512 ps Increase tzx delay to Off 0 0 0 0 ps output pin On 1.993 2.092 2.092 2.092 ps

Note to Table 4-109 and Table 4-110:

<sup>(1)</sup> The delay chain delays vary for different device densities. These timing values only apply to EP1S30 and EP1S40 devices. Reference the timing information reported by the Quartus II software for other devices.