Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 1057                                                     |

| Number of Logic Elements/Cells | 10570                                                    |

| Total RAM Bits                 | 920448                                                   |

| Number of I/O                  | 345                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 672-BBGA                                                 |

| Supplier Device Package        | 672-FBGA (27x27)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s10f672c7n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

functions. Another special packing mode allows the register output to feed back into the LUT of the same LE so that the register is packed with its own fan-out LUT. This provides another mechanism for improved fitting. The LE can also drive out registered and unregistered versions of the LUT output.

#### **LUT Chain & Register Chain**

In addition to the three general routing outputs, the LEs within an LAB have LUT chain and register chain outputs. LUT chain connections allow LUTs within the same LAB to cascade together for wide input functions. Register chain outputs allow registers within the same LAB to cascade together. The register chain output allows an LAB to use LUTs for a single combinatorial function and the registers to be used for an unrelated shift register implementation. These resources speed up connections between LABs while saving local interconnect resources. See "MultiTrack Interconnect" on page 2–14 for more information on LUT chain and register chain connections.

#### addnsub Signal

The LE's dynamic adder/subtractor feature saves logic resources by using one set of LEs to implement both an adder and a subtractor. This feature is controlled by the LAB-wide control signal addnsub. The addnsub signal sets the LAB to perform either A+B or A-B. The LUT computes addition, and subtraction is computed by adding the two's complement of the intended subtractor. The LAB-wide signal converts to two's complement by inverting the B bits within the LAB and setting carry-in = 1 to add one to the least significant bit (LSB). The LSB of an adder/subtractor must be placed in the first LE of the LAB, where the LAB-wide addnsub signal automatically sets the carry-in to 1. The Quartus II Compiler automatically places and uses the adder/subtractor feature when using adder/subtractor parameterized functions.

## **LE Operating Modes**

The Stratix LE can operate in one of the following modes:

- Normal mode

- Dynamic arithmetic mode

Each mode uses LE resources differently. In each mode, eight available inputs to the LE—the four data inputs from the LAB local interconnect; carry-in0 and carry-in1 from the previous LE; the LAB carry-in from the previous carry-chain LAB; and the register chain connection—are directed to different destinations to implement the desired logic function. LAB-wide signals provide clock, asynchronous clear,

can drive other R8 interconnects to extend their range as well as C8 interconnects for row-to-row connections. One R8 interconnect is faster than two R4 interconnects connected together.

R24 row interconnects span 24 LABs and provide the fastest resource for long row connections between LABs, TriMatrix memory, DSP blocks, and IOEs. The R24 row interconnects can cross M-RAM blocks. R24 row interconnects drive to other row or column interconnects at every fourth LAB and do not drive directly to LAB local interconnects. R24 row interconnects drive LAB local interconnects via R4 and C4 interconnects. R24 interconnects can drive R24, R4, C16, and C4 interconnects.

The column interconnect operates similarly to the row interconnect and vertically routes signals to and from LABs, TriMatrix memory, DSP blocks, and IOEs. Each column of LABs is served by a dedicated column interconnect, which vertically routes signals to and from LABs, TriMatrix memory and DSP blocks, and horizontal IOEs. These column resources include:

- LUT chain interconnects within an LAB

- Register chain interconnects within an LAB

- C4 interconnects traversing a distance of four blocks in up and down direction

- C8 interconnects traversing a distance of eight blocks in up and down direction

- C16 column interconnects for high-speed vertical routing through the device

Stratix devices include an enhanced interconnect structure within LABs for routing LE output to LE input connections faster using LUT chain connections and register chain connections. The LUT chain connection allows the combinatorial output of an LE to directly drive the fast input of the LE right below it, bypassing the local interconnect. These resources can be used as a high-speed connection for wide fan-in functions from LE 1 to LE 10 in the same LAB. The register chain connection allows the register output of one LE to connect directly to the register input of the next LE in the LAB for fast shift registers. The Quartus II Compiler automatically takes advantage of these resources to improve utilization and performance. Figure 2–10 shows the LUT chain and register chain interconnects.

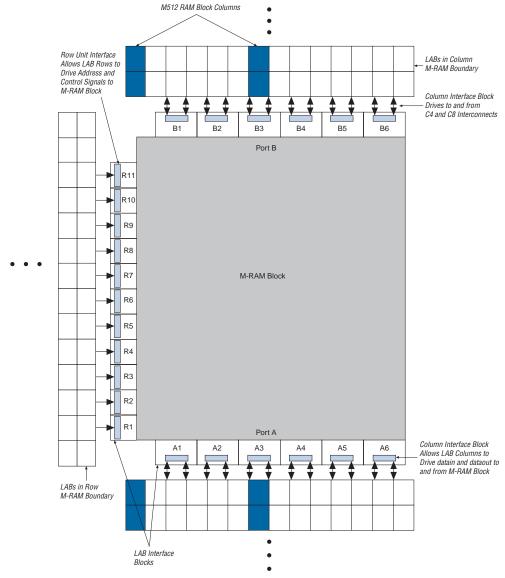

Figure 2–21. Left-Facing M-RAM to Interconnect Interface Notes (1), (2)

*Notes to Figure 2–21:*

- (1) Only R24 and C16 interconnects cross the M-RAM block boundaries.

- (2) The right-facing M-RAM block has interface blocks on the right side, but none on the left. B1 to B6 and A1 to A6 orientation is clipped across the vertical axis for right-facing M-RAM blocks.

## **Independent Clock Mode**

The memory blocks implement independent clock mode for true dual-port memory. In this mode, a separate clock is available for each port (ports A and B). Clock A controls all registers on the port A side, while clock B controls all registers on the port B side. Each port, A and B, also supports independent clock enables and asynchronous clear signals for port A and B registers. Figure 2–24 shows a TriMatrix memory block in independent clock mode.

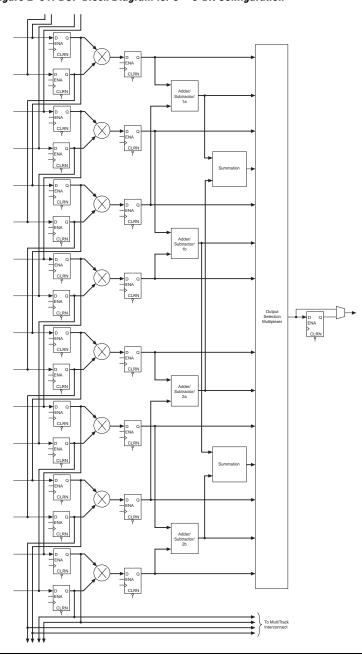

Figure 2–31. DSP Block Diagram for  $9 \times 9$ -Bit Configuration

#### Pipeline/Post Multiply Register

The output of  $9 \times 9$ - or  $18 \times 18$ -bit multipliers can optionally feed a register to pipeline multiply-accumulate and multiply-add/subtract functions. For  $36 \times 36$ -bit multipliers, this register will pipeline the multiplier function.

#### **Adder/Output Blocks**

The result of the multiplier sub-blocks are sent to the adder/output block which consist of an adder/subtractor/accumulator unit, summation unit, output select multiplexer, and output registers. The results are used to configure the adder/output block as a pure output, accumulator, a simple two-multiplier adder, four-multiplier adder, or final stage of the 36-bit multiplier. You can configure the adder/output block to use output registers in any mode, and must use output registers for the accumulator. The system cannot use adder/output blocks independently of the multiplier. Figure 2–34 shows the adder and output stages.

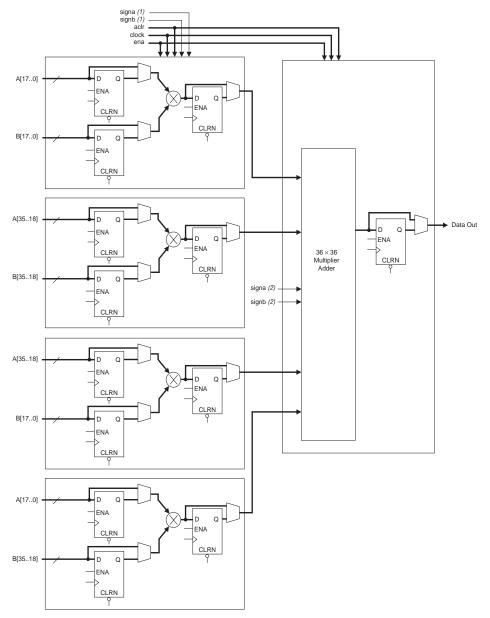

Figure 2–36. 36  $\times$  36 Multiply Mode

#### *Notes to Figure 2–36:*

- (1) These signals are not registered or registered once to match the pipeline.

- (2) These signals are not registered, registered once, or registered twice for latency to match the pipeline.

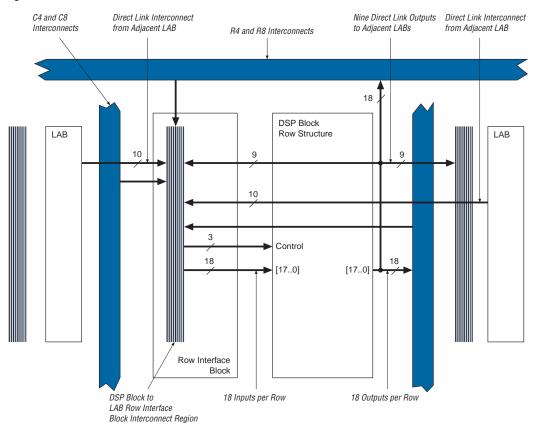

Figure 2-41. DSP Block Interface to Interconnect

A bus of 18 control signals feeds the entire DSP block. These signals include clock[0..3] clocks, aclr[0..3] asynchronous clears, ena[1..4] clock enables, signa, signb signed/unsigned control signals, addnsub1 and addnsub3 addition and subtraction control signals, and accum sload[0..1] accumulator synchronous loads. The

| Table 2–22. Fast PLL Port I/O Standards (Part 2 of 2) |          |           |  |  |  |  |  |  |  |  |

|-------------------------------------------------------|----------|-----------|--|--|--|--|--|--|--|--|

| I/O Standard                                          | I        | nput      |  |  |  |  |  |  |  |  |

| I/U Standard                                          | INCLK    | PLLENABLE |  |  |  |  |  |  |  |  |

| SSTL-2 Class II                                       | <b>✓</b> |           |  |  |  |  |  |  |  |  |

| SSTL-3 Class I                                        | ✓        |           |  |  |  |  |  |  |  |  |

| SSTL-3 Class II                                       | ✓        |           |  |  |  |  |  |  |  |  |

| AGP (1× and 2×)                                       |          |           |  |  |  |  |  |  |  |  |

| СТТ                                                   | <b>✓</b> |           |  |  |  |  |  |  |  |  |

Table 2–23 shows the performance on each of the fast PLL clock inputs when using LVDS, LVPECL, 3.3-V PCML, or HyperTransport technology.

| Table 2–23. LVDS Performance on Fast PLL Input                         |                               |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------|-------------------------------|--|--|--|--|--|--|--|--|

| Fast PLL Clock Input                                                   | Maximum Input Frequency (MHz) |  |  |  |  |  |  |  |  |

| CLK0, CLK2, CLK9, CLK11,<br>FPLL7CLK, FPLL8CLK, FPLL9CLK,<br>FPLL10CLK | 717 <i>(</i> 1)               |  |  |  |  |  |  |  |  |

| CLK1, CLK3, CLK8, CLK10                                                | 645                           |  |  |  |  |  |  |  |  |

*Note to Table 2–23:*

#### External Clock Outputs

Each fast PLL supports differential or single-ended outputs for source-synchronous transmitters or for general-purpose external clocks. There are no dedicated external clock output pins. Any I/O pin can be driven by the fast PLL global or regional outputs as an external output pin. The I/O standards supported by any particular bank determines what standards are possible for an external clock output driven by the fast PLL in that bank.

#### Phase Shifting

Stratix device fast PLLs have advanced clock shift capability that enables programmable phase shifts. You can enter a phase shift (in degrees or time units) for each PLL clock output port or for all outputs together in one shift. You can perform phase shifting in time units with a resolution range of 125 to 416.66 ps. This resolution is a function of the VCO period, with the finest step being equal to an eighth (×0.125) of the VCO period.

<sup>(1)</sup> See the chapter DC & Switching Characteristics of the Stratix Device Handbook, Volume 1 for more information.

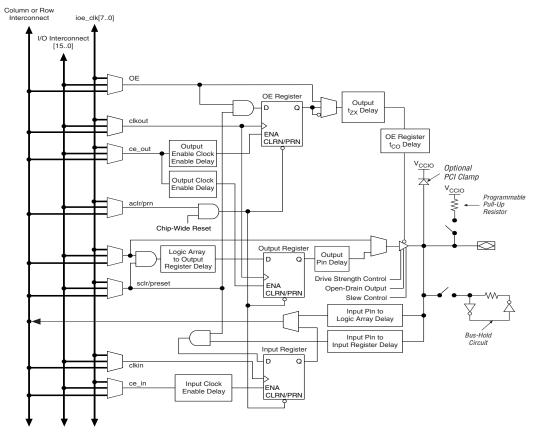

Stratix devices have an I/O interconnect similar to the R4 and C4 interconnect to drive high-fanout signals to and from the I/O blocks. There are 16 signals that drive into the I/O blocks composed of four output enables <code>io\_boe[3..0]</code>, four clock enables <code>io\_bce[3..0]</code>, four clocks <code>io\_bclk[3..0]</code>, and four clear signals <code>io\_bclr[3..0]</code>. The pin's <code>datain</code> signals can drive the IO interconnect, which in turn drives the logic array or other I/O blocks. In addition, the control and data signals can be driven from the logic array, providing a slower but more flexible routing resource. The row or column IOE clocks, <code>io\_clk[7..0]</code>, provide a dedicated routing resource for low-skew, high-speed clocks. I/O clocks are generated from regional, global, or fast regional clocks (see "PLLs & Clock Networks" on page 2–73). Figure 2–62 illustrates the signal paths through the I/O block.

Row or Column io\_clk[7..0] io\_boe[3..0] To Other io\_bce[3..0] 10Es From I/O Interconnect io\_bclk[3..0] io\_bclr[3..0] io\_datain0 To Logic Array io datain1 ◀ oe ce\_in ce\_out io coe Control IOE aclr/apreset io cce in Signal Selection sclr/spreset io cce out clk in From Logic io\_cclr Array clk out io\_cclk io\_dataout0 io\_dataout1

Figure 2-62. Signal Path through the I/O Block

Figure 2–64. Stratix IOE in Bidirectional I/O Configuration Note (1)

Note to Figure 2-64:

(1) All input signals to the IOE can be inverted at the IOE.

The Stratix device IOE includes programmable delays that can be activated to ensure zero hold times, input IOE register-to-logic array register transfers, or logic array-to-output IOE register transfers.

A path in which a pin directly drives a register may require the delay to ensure zero hold time, whereas a path in which a pin drives a register through combinatorial logic may not require the delay. Programmable delays exist for decreasing input-pin-to-logic-array and IOE input register delays. The Quartus II Compiler can program these delays to automatically minimize setup time while providing a zero hold time. Programmable delays can increase the register-to-pin delays for output

shift by the same degree amount. For example, all 10 DQS pins on the top of the device can be shifted by 90° and all 10 DQS pins on the bottom of the device can be shifted by 72°. The reference circuits require a maximum of 256 system reference clock cycles to set the correct phase on the DQS delay elements. Figure 2–69 illustrates the phase-shift reference circuit control of each DQS delay shift on the top of the device. This same circuit is duplicated on the bottom of the device.

Input

Reference

Clock

Phase

Comparator

Up/Down

Counter

Delay Chains

Control Signals to DQS Pins

Figure 2-69. Simplified Diagram of the DQS Phase-Shift Circuitry

See the *External Memory Interfaces* chapter in the *Stratix Device Handbook, Volume 2* for more information on external memory interfaces.

## **Programmable Drive Strength**

The output buffer for each Stratix device I/O pin has a programmable drive strength control for certain I/O standards. The LVTTL and LVCMOS standard has several levels of drive strength that the user can control. SSTL-3 Class I and II, SSTL-2 Class I and II, HSTL Class I and II, and 3.3-V GTL+ support a minimum setting, the lowest drive strength that guarantees the  $\rm I_{OH}/\rm I_{OL}$  of the standard. Using minimum settings provides signal slew rate control to reduce system noise and signal overshoot.

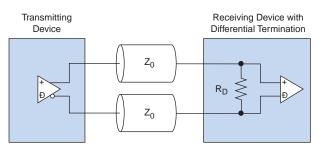

Figure 2-71. LVDS Input Differential On-Chip Termination

I/O banks on the left and right side of the device support LVDS receiver (far-end) differential termination.

Table 2–33 shows the Stratix device differential termination support.

| Table 2–33. Differential Termination Supported by I/O Banks |                                     |                                     |          |  |  |  |  |  |  |  |

|-------------------------------------------------------------|-------------------------------------|-------------------------------------|----------|--|--|--|--|--|--|--|

| Differential Termination Support                            | Top & Bottom<br>Banks (3, 4, 7 & 8) | Left & Right Banks<br>(1, 2, 5 & 6) |          |  |  |  |  |  |  |  |

| Differential termination (1), (2)                           | LVDS                                |                                     | <b>✓</b> |  |  |  |  |  |  |  |

Notes to Table 2-33:

- (1) Clock pin CLK0, CLK2, CLK9, CLK11, and pins FPLL [7..10] CLK do not support differential termination.

- (2) Differential termination is only supported for LVDS because of a 3.3-V V<sub>CCIO</sub>.

Table 2–34 shows the termination support for different pin types.

| Table 2–34. Differential Termination Support Across Pin Types |                |  |  |  |  |  |  |

|---------------------------------------------------------------|----------------|--|--|--|--|--|--|

| Pin Type                                                      | R <sub>D</sub> |  |  |  |  |  |  |

| Top and bottom I/O banks (3, 4, 7, and 8)                     |                |  |  |  |  |  |  |

| DIFFIO_RX[]                                                   | <b>✓</b>       |  |  |  |  |  |  |

| CLK[0,2,9,11],CLK[4-7],CLK[12-15]                             |                |  |  |  |  |  |  |

| CLK[1,3,8,10]                                                 | <b>✓</b>       |  |  |  |  |  |  |

| FCLK                                                          |                |  |  |  |  |  |  |

| FPLL[710]CLK                                                  |                |  |  |  |  |  |  |

The differential on-chip resistance at the receiver input buffer is 118  $\Omega \pm 20$  %.

Stratix, Stratix II, Cyclone<sup>®</sup>, and Cyclone II devices must be within the first 17 devices in a JTAG chain. All of these devices have the same JTAG controller. If any of the Stratix, Stratix II, Cyclone, and Cyclone II devices are in the 18th or after they will fail configuration. This does not affect SignalTap II.

For more information on JTAG, see the following documents:

- AN 39: IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices

- Jam Programming & Test Language Specification

## SignalTap II Embedded Logic Analyzer

Stratix devices feature the SignalTap II embedded logic analyzer, which monitors design operation over a period of time through the IEEE Std. 1149.1 (JTAG) circuitry. You can analyze internal logic at speed without bringing internal signals to the I/O pins. This feature is particularly important for advanced packages, such as FineLine BGA® packages, because it can be difficult to add a connection to a pin during the debugging process after a board is designed and manufactured.

## Configuration

The logic, circuitry, and interconnects in the Stratix architecture are configured with CMOS SRAM elements. Altera® devices are reconfigurable. Because every device is tested with a high-coverage production test program, you do not have to perform fault testing and can focus on simulation and design verification.

Stratix devices are configured at system power-up with data stored in an Altera serial configuration device or provided by a system controller. Altera offers in-system programmability (ISP)-capable configuration devices that configure Stratix devices via a serial data stream. Stratix devices can be configured in under 100 ms using 8-bit parallel data at 100 MHz. The Stratix device's optimized interface allows microprocessors to configure it serially or in parallel, and synchronously or asynchronously. The interface also enables microprocessors to treat Stratix devices as memory and configure them by writing to a virtual memory location, making reconfiguration easy. After a Stratix device has been configured, it can be reconfigured in-circuit by resetting the device and loading new data. Real-time changes can be made during system operation, enabling innovative reconfigurable computing applications.

## **Operating Modes**

The Stratix architecture uses SRAM configuration elements that require configuration data to be loaded each time the circuit powers up. The process of physically loading the SRAM data into the device is called configuration. During initialization, which occurs immediately after

| Table 4-59. I         | EP1S10 Ext | ternal I/O T | iming on F | Row Pins U     | sing Regio | nal Clock I    | letworks / | Vote (1)       |      |

|-----------------------|------------|--------------|------------|----------------|------------|----------------|------------|----------------|------|

| Davamatav             | -5 Spee    | d Grade      | -6 Spee    | -6 Speed Grade |            | -7 Speed Grade |            | -8 Speed Grade |      |

| Parameter             | Min        | Max          | Min        | Max            | Min        | Max            | Min        | Max            | Unit |

| t <sub>INSU</sub>     | 2.161      |              | 2.336      |                | 2.685      |                | NA         |                | ns   |

| t <sub>INH</sub>      | 0.000      |              | 0.000      |                | 0.000      |                | NA         |                | ns   |

| t <sub>OUTCO</sub>    | 2.434      | 4.889        | 2.434      | 5.226          | 2.434      | 5.643          | NA         | NA             | ns   |

| t <sub>XZ</sub>       | 2.461      | 4.493        | 2.461      | 5.282          | 2.461      | 5.711          | NA         | NA             | ns   |

| t <sub>ZX</sub>       | 2.461      | 4.493        | 2.461      | 5.282          | 2.461      | 5.711          | NA         | NA             | ns   |

| t <sub>INSUPLL</sub>  | 1.057      |              | 1.172      |                | 1.315      |                | NA         |                | ns   |

| t <sub>INHPLL</sub>   | 0.000      |              | 0.000      |                | 0.000      |                | NA         |                | ns   |

| t <sub>OUTCOPLL</sub> | 1.327      | 2.773        | 1.327      | 2.848          | 1.327      | 2.940          | NA         | NA             | ns   |

| t <sub>XZPLL</sub>    | 1.354      | 2.827        | 1.354      | 2.904          | 1.354      | 3.008          | NA         | NA             | ns   |

| t <sub>ZXPLL</sub>    | 1.354      | 2.827        | 1.354      | 2.904          | 1.354      | 3.008          | NA         | NA             | ns   |

| Table 4–60. l         | Table 4–60. EP1S10 External I/O Timing on Row Pins Using Global Clock Networks         Note (1) |         |         |                |       |         |         |      |      |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------|---------|---------|----------------|-------|---------|---------|------|------|--|--|--|--|

| Doromotor             | -5 Spee                                                                                         | d Grade | -6 Spee | -6 Speed Grade |       | d Grade | -8 Spee | 11!4 |      |  |  |  |  |

| Parameter             | Min                                                                                             | Max     | Min     | Max            | Min   | Max     | Min     | Max  | Unit |  |  |  |  |

| t <sub>INSU</sub>     | 1.787                                                                                           |         | 1.944   |                | 2.232 |         | NA      |      | ns   |  |  |  |  |

| t <sub>INH</sub>      | 0.000                                                                                           |         | 0.000   |                | 0.000 |         | NA      |      | ns   |  |  |  |  |

| t <sub>OUTCO</sub>    | 2.647                                                                                           | 5.263   | 2.647   | 5.618          | 2.647 | 6.069   | NA      | NA   | ns   |  |  |  |  |

| t <sub>XZ</sub>       | 2.674                                                                                           | 5.317   | 2.674   | 5.674          | 2.674 | 6.164   | NA      | NA   | ns   |  |  |  |  |

| t <sub>ZX</sub>       | 2.674                                                                                           | 5.317   | 2.674   | 5.674          | 2.674 | 6.164   | NA      | NA   | ns   |  |  |  |  |

| t <sub>INSUPLL</sub>  | 1.371                                                                                           |         | 1.1472  |                | 1.654 |         | NA      |      | ns   |  |  |  |  |

| t <sub>INHPLL</sub>   | 0.000                                                                                           |         | 0.000   |                | 0.000 |         | NA      |      | ns   |  |  |  |  |

| t <sub>OUTCOPLL</sub> | 1.144                                                                                           | 2.459   | 1.144   | 2.548          | 1.144 | 2.601   | NA      | NA   | ns   |  |  |  |  |

| t <sub>XZPLL</sub>    | 1.171                                                                                           | 2.513   | 1.171   | 2.604          | 1.171 | 2.669   | NA      | NA   | ns   |  |  |  |  |

| t <sup>ZXPLL</sup>    | 1.171                                                                                           | 2.513   | 1.171   | 2.604          | 1.171 | 2.669   | NA      | NA   | ns   |  |  |  |  |

*Note to Tables 4–55 to 4–60:*

<sup>(1)</sup> Only EP1S25, EP1S30, and EP1S40 have speed grade of -8.

Tables 4–67 through 4–72 show the external timing parameters on column and row pins for EP1S25 devices.

| Table 4–67. I      | Table 4–67. EP1S25 External I/O Timing on Column Pins Using Fast Regional Clock Networks |         |                |       |                |       |                |       |      |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------|---------|----------------|-------|----------------|-------|----------------|-------|------|--|--|--|--|

|                    | -5 Spee                                                                                  | d Grade | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | Heit |  |  |  |  |

| Parameter          | Min                                                                                      | Max     | Min            | Max   | Min            | Max   | Min            | Max   | Unit |  |  |  |  |

| t <sub>INSU</sub>  | 2.412                                                                                    |         | 2.613          |       | 2.968          |       | 3.468          |       | ns   |  |  |  |  |

| t <sub>INH</sub>   | 0.000                                                                                    |         | 0.000          |       | 0.000          |       | 0.000          |       | ns   |  |  |  |  |

| t <sub>OUTCO</sub> | 2.196                                                                                    | 4.475   | 2.196          | 4.748 | 2.196          | 5.118 | 2.196          | 5.603 | ns   |  |  |  |  |

| t <sub>XZ</sub>    | 2.136                                                                                    | 4.349   | 2.136          | 4.616 | 2.136          | 4.994 | 2.136          | 5.488 | ns   |  |  |  |  |

| t <sub>ZX</sub>    | 2.136                                                                                    | 4.349   | 2.136          | 4.616 | 2.136          | 4.994 | 2.136          | 5.488 | ns   |  |  |  |  |

| Table 4–68. I        | Table 4–68. EP1S25 External I/O Timing on Column Pins Using Regional Clock Networks |         |         |                |       |         |         |       |      |  |  |  |  |

|----------------------|-------------------------------------------------------------------------------------|---------|---------|----------------|-------|---------|---------|-------|------|--|--|--|--|

| Parameter            | -5 Spee                                                                             | d Grade | -6 Spee | -6 Speed Grade |       | d Grade | -8 Spee | 11-14 |      |  |  |  |  |

| rarameter            | Min                                                                                 | Max     | Min     | Max            | Min   | Max     | Min     | Max   | Unit |  |  |  |  |

| t <sub>INSU</sub>    | 1.535                                                                               |         | 1.661   |                | 1.877 |         | 2.125   |       | ns   |  |  |  |  |

| t <sub>INH</sub>     | 0.000                                                                               |         | 0.000   |                | 0.000 |         | 0.000   |       | ns   |  |  |  |  |

| t <sub>оитсо</sub>   | 2.739                                                                               | 5.396   | 2.739   | 5.746          | 2.739 | 6.262   | 2.739   | 6.946 | ns   |  |  |  |  |

| t <sub>XZ</sub>      | 2.679                                                                               | 5.270   | 2.679   | 5.614          | 2.679 | 6.138   | 2.679   | 6.831 | ns   |  |  |  |  |

| t <sub>ZX</sub>      | 2.679                                                                               | 5.270   | 2.679   | 5.614          | 2.679 | 6.138   | 2.679   | 6.831 | ns   |  |  |  |  |

| t <sub>INSUPLL</sub> | 0.934                                                                               |         | 0.980   |                | 1.092 |         | 1.231   |       | ns   |  |  |  |  |

| t <sub>INHPLL</sub>  | 0.000                                                                               |         | 0.000   |                | 0.000 |         | 0.000   |       | ns   |  |  |  |  |

| toutcopll            | 1.316                                                                               | 2.733   | 1.316   | 2.839          | 1.316 | 2.921   | 1.316   | 3.110 | ns   |  |  |  |  |

| t <sup>XZPLL</sup>   | 1.256                                                                               | 2.607   | 1.256   | 2.707          | 1.256 | 2.797   | 1.256   | 2.995 | ns   |  |  |  |  |

| t <sub>ZXPLL</sub>   | 1.256                                                                               | 2.607   | 1.256   | 2.707          | 1.256 | 2.797   | 1.256   | 2.995 | ns   |  |  |  |  |

#### Skew on Input Pins

Table 4–99 shows the package skews that were considered to get the worst case I/O skew value. You can use these values, for example, when calculating the timing budget on the input (read) side of a memory interface.

| Table 4–99. Package Skew on Input Pins         |                      |  |  |  |  |  |  |  |  |

|------------------------------------------------|----------------------|--|--|--|--|--|--|--|--|

| Package Parameter                              | Worst-Case Skew (ps) |  |  |  |  |  |  |  |  |

| Pins in the same I/O bank                      | 50                   |  |  |  |  |  |  |  |  |

| Pins in top/bottom (vertical I/O) banks        | 50                   |  |  |  |  |  |  |  |  |

| Pins in left/right side (horizontal I/O) banks | 50                   |  |  |  |  |  |  |  |  |

| Pins across the entire device                  | 100                  |  |  |  |  |  |  |  |  |

#### PLL Counter & Clock Network Skews

Table 4–100 shows the clock skews between different clock outputs from the Stratix device PLL.

| Table 4–100. PLL Counter & Clock Network Skews                                                        |                      |  |  |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|--|--|--|--|--|--|

| Parameter                                                                                             | Worst-Case Skew (ps) |  |  |  |  |  |  |  |  |  |  |

| Clock skew between two external clock outputs driven by the same counter                              | 100                  |  |  |  |  |  |  |  |  |  |  |

| Clock skew between two external clock outputs driven by the different counters with the same settings | 150                  |  |  |  |  |  |  |  |  |  |  |

| Dual-purpose PLL dedicated clock output used as I/O pin vs. regular I/O pin                           | 270 (1)              |  |  |  |  |  |  |  |  |  |  |

| Clock skew between any two outputs of the PLL that drive global clock networks                        | 150                  |  |  |  |  |  |  |  |  |  |  |

Note to Table 4-100:

(1) The Quartus II software models 270 ps of delay on the PLL dedicated clock output (PLL6\_OUT[3..0]p/n and PLL5\_OUT[3..0]p/n) pins both when used as clocks and when used as I/O pins.

## I/O Timing Measurement Methodology

Different I/O standards require different baseline loading techniques for reporting timing delays. Altera characterizes timing delays with the required termination and loading for each I/O standard. The timing information is specified from the input clock pin up to the output pin of

| Symbol            | Conditions                                                         | -5 Speed Grade |     | -6 Speed Grade |      | -7 Speed Grade |      |      | -8 Speed Grade |      |      | IImia |      |      |

|-------------------|--------------------------------------------------------------------|----------------|-----|----------------|------|----------------|------|------|----------------|------|------|-------|------|------|

|                   | Conditions                                                         | Min            | Тур | Max            | Min  | Тур            | Max  | Min  | Тур            | Max  | Min  | Тур   | Max  | Unit |

| t <sub>DUTY</sub> | LVDS ( $J = 2$ through 10)                                         | 47.5           | 50  | 52.5           | 47.5 | 50             | 52.5 | 47.5 | 50             | 52.5 | 47.5 | 50    | 52.5 | %    |

|                   | LVDS (J=1)<br>and LVPECL,<br>PCML,<br>HyperTransport<br>technology | 45             | 50  | 55             | 45   | 50             | 55   | 45   | 50             | 55   | 45   | 50    | 55   | %    |

| t <sub>LOCK</sub> | All                                                                |                |     | 100            |      |                | 100  |      |                | 100  |      |       | 100  | μs   |

#### Notes to Table 4–125:

- (1) When J = 4, 7, 8, and 10, the SERDES block is used.

- (2) When J = 2 or J = 1, the SERDES is bypassed.

| Table 4–127. Enhanced PLL Specifications for -5 Speed Grades (Part 2 of 2) |                                                                                                                     |     |     |     |      |  |  |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|--|--|

| Symbol                                                                     | Parameter                                                                                                           | Min | Тур | Max | Unit |  |  |

| t <sub>SKEW</sub>                                                          | Clock skew between two external clock outputs driven by the different counters with the same settings               |     | ±75 |     | ps   |  |  |

| f <sub>SS</sub>                                                            | Spread spectrum modulation frequency                                                                                | 30  |     | 150 | kHz  |  |  |

| % spread                                                                   | Percentage spread for spread spectrum frequency (10)                                                                | 0.4 | 0.5 | 0.6 | %    |  |  |

| t <sub>ARESET</sub>                                                        | Minimum pulse width on areset signal                                                                                | 10  |     |     | ns   |  |  |

| tareset_recon<br>fig                                                       | Minimum pulse width on the areset signal when using PLL reconfiguration. Reset the PLL after scandataout goes high. | 500 |     |     | ns   |  |  |

| Table 4–128. Enhanced PLL Specifications for -6 Speed Grades (Part 1 of 2) |                                                                 |               |     |                                                            |              |  |

|----------------------------------------------------------------------------|-----------------------------------------------------------------|---------------|-----|------------------------------------------------------------|--------------|--|

| Symbol                                                                     | Parameter                                                       | Min           | Тур | Max                                                        | Unit         |  |

| $f_{\text{IN}}$                                                            | Input clock frequency                                           | 3<br>(1), (2) |     | 650                                                        | MHz          |  |

| f <sub>INPFD</sub>                                                         | Input frequency to PFD                                          | 3             |     | 420                                                        | MHz          |  |

| f <sub>INDUTY</sub>                                                        | Input clock duty cycle                                          | 40            |     | 60                                                         | %            |  |

| f <sub>EINDUTY</sub>                                                       | External feedback clock input duty cycle                        | 40            |     | 60                                                         | %            |  |

| t <sub>INJITTER</sub>                                                      | Input clock period jitter                                       |               |     | ±200 (3)                                                   | ps           |  |

| t <sub>EINJITTER</sub>                                                     | External feedback clock period jitter                           |               |     | ±200 (3)                                                   | ps           |  |

| t <sub>FCOMP</sub>                                                         | External feedback clock compensation time (4)                   |               |     | 6                                                          | ns           |  |

| f <sub>OUT</sub>                                                           | Output frequency for internal global or regional clock          | 0.3           |     | 450                                                        | MHz          |  |

| f <sub>OUT_EXT</sub>                                                       | Output frequency for external clock (3)                         | 0.3           |     | 500                                                        | MHz          |  |

| toutduty                                                                   | Duty cycle for external clock output (when set to 50%)          | 45            |     | 55                                                         | %            |  |

| t <sub>JITTER</sub>                                                        | Period jitter for external clock output (6)                     |               |     | ±100 ps for >200-MHz outclk<br>±20 mUI for <200-MHz outclk | ps or<br>mUI |  |

| t <sub>CONFIG5,6</sub>                                                     | Time required to reconfigure the scan chains for PLLs 5 and 6   |               |     | 289/f <sub>SCANCLK</sub>                                   |              |  |

| t <sub>CONFIG11,12</sub>                                                   | Time required to reconfigure the scan chains for PLLs 11 and 12 |               |     | 193/f <sub>SCANCLK</sub>                                   |              |  |

| Fast Regional Clock External I/O Timing            | I                                                           |

|----------------------------------------------------|-------------------------------------------------------------|

| Parameters 4–49                                    | I/O                                                         |

| Global Clock External I/O Timing                   | Standards                                                   |

| Parameters 4–50 Regional Clock External I/O Timing | 1.5-V 4-14, 4-15                                            |

| Parameters 4–50                                    | I/O Specifications 4–4                                      |

| EP1S60 Devices                                     | 1.8-V                                                       |

| Column Pin                                         | I/O Specifications 4–4                                      |

| Fast Regional Clock External I/O Timing            | 2.5-V                                                       |

| Parameters 4–51                                    | I/O Specifications 4–3                                      |

| Global Clock External I/O Timing                   | 3.3-V 4–13                                                  |

| Parameters 4–52                                    | LVDS I/O Specifications 4–6                                 |

| Regional Clock External I/O Timing                 | PCI Specifications 4–9                                      |

| Parameters 4–51                                    | PCML Specifications 4–8                                     |

| M-RAM                                              | Advanced I/O Standard Support 2–122                         |

| Interface Locations 2–38                           | Column I/O Block Connection to the                          |

| Row Pin                                            | Interconnect 2–107                                          |

| Fast Regional Clock External I/O Timing            | Column Pin                                                  |

| Parameters 4–52                                    | Input Delay Adders 4–66                                     |

| Global Clock External I/O Timing                   | Control Signal Selection per IOE 2–109                      |

| Parameters 4–53                                    | CTT I/O Specifications 4–16                                 |

| Regional Clock External I/O Timing                 | Differential LVDS Input On-Chip                             |

| Parameters 4–53                                    | Termination 2–128                                           |

| EP1S80 Devices                                     | External I/O Delay Parameters 4–66                          |

| Column Pin                                         | GTL+ I/O Specifications 4–10<br>High-Speed Differential I/O |

| Fast Regional Clock External I/O Timing            | Support 2–130                                               |

| Parameters 4–54                                    | HyperTransport Technology                                   |

| Global Clock External I/O Timing                   | Specifications 4–9                                          |

| Parameters 4–55                                    | I/O Banks 2–125                                             |

| Regional Clock External I/O Timing                 | I/O Structure 2–104                                         |

| Parameters 4–54                                    | I/O Support by Bank 2–126                                   |

| Global Clock External I/O Timing                   | IOE Structure 2–105                                         |

| Parameters 4–56                                    | LVCMOS Specifications 4–3                                   |

| Row Pin                                            | LVDS Performance on Fast PLL                                |

| Fast Regional Clock External I/O Timing            | Input 2–103                                                 |

| Parameters 4–55                                    | LVPECL Specifications 4–8                                   |

| Regional Clock External I/O Timing                 | LVTTL Specifications 4–3                                    |

| Parameters 4–56                                    | MultiVolt I/O Interface 2–129                               |

|                                                    | MultiVolt I/O Support 2–130                                 |

| H                                                  | Output Delay Adders for Fast Slew Rate                      |

| HSTL                                               | on Column Pins 4–68                                         |

| Class I Specifications 4–14, 4–15                  | Output Delay Adders for Fast Slew Rate                      |

| Class II Specifications 4–14, 4–15                 | on Row Pins 4–69                                            |

| Ciass II Specifications 4-14, 4-15                 | Output Delay Adders for Slow Slew Rate                      |

|                                                    | on Column Pins 4–70                                         |

|                                                    | Package Options & I/O Pin Counts 1–4                        |

|                                                    | Receiver Input Waveforms for Differential                   |

Index-4 Altera Corporation