Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 1057                                                     |

| Number of Logic Elements/Cells | 10570                                                    |

| Total RAM Bits                 | 920448                                                   |

| Number of I/O                  | 426                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 780-BBGA                                                 |

| Supplier Device Package        | 780-FBGA (29x29)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s10f780c5n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Chapter | Date/Version         | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4       | January 2005, 3.2    | Updated rise and fall input values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | September 2004, v3.1 | <ul> <li>Updated Note 3 in Table 4–8 on page 4–4.</li> <li>Updated Table 4–10 on page 4–6.</li> <li>Updated Table 4–20 on page 4–12 through Table 4–23 on page 4–13. Added rows V<sub>IL(AC)</sub> and V<sub>IH(AC)</sub> to each table.</li> <li>Updated Table 4–26 on page 4–14 through Table 4–29 on page 4–15.</li> <li>Updated Table 4–31 on page 4–16.</li> <li>Updated Table 4–36 on page 4–20.</li> <li>Added signals t<sub>OUTCO</sub>, T<sub>XZ</sub>, and T<sub>ZX</sub> to Figure 4–4 on page 4–33.</li> <li>Added rows t<sub>M512CLKENSU</sub> and t<sub>M512CLKENH</sub> to Table 4–40 on page 4–24.</li> <li>Added rows t<sub>M4CLKENSU</sub> and t<sub>M4CLKENH</sub> to Table 4–41 on page 4–24.</li> <li>Updated Note 2 in Table 4–54 on page 4–35.</li> <li>Added rows t<sub>MRAMCLKENSU</sub> and t<sub>MRAMCLKENH</sub> to Table 4–42 on page 4–25.</li> <li>Updated Table 4–46 on page 4–29.</li> <li>Updated Table 4–47 on page 4–29.</li> </ul> |

Section I–4 Altera Corporation

Figure 2–8 shows the carry-select circuitry in an LAB for a 10-bit full adder. One portion of the LUT generates the sum of two bits using the input signals and the appropriate carry-in bit; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used for accumulator functions. Another portion of the LUT generates carry-out bits. An LAB-wide carry in bit selects which chain is used for the addition of given inputs. The carry-in signal for each chain, carry-in0 or carry-in1, selects the carry-out to carry forward to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it is fed to local, row, or column interconnects.

The Quartus II Compiler automatically creates carry chain logic during design processing, or you can create it manually during design entry. Parameterized functions such as LPM functions automatically take advantage of carry chains for the appropriate functions.

The Quartus II Compiler creates carry chains longer than 10 LEs by linking LABs together automatically. For enhanced fitting, a long carry chain runs vertically allowing fast horizontal connections to  $TriMatrix^{TM}$  memory and DSP blocks. A carry chain can continue as far as a full column.

can drive other R8 interconnects to extend their range as well as C8 interconnects for row-to-row connections. One R8 interconnect is faster than two R4 interconnects connected together.

R24 row interconnects span 24 LABs and provide the fastest resource for long row connections between LABs, TriMatrix memory, DSP blocks, and IOEs. The R24 row interconnects can cross M-RAM blocks. R24 row interconnects drive to other row or column interconnects at every fourth LAB and do not drive directly to LAB local interconnects. R24 row interconnects drive LAB local interconnects via R4 and C4 interconnects. R24 interconnects can drive R24, R4, C16, and C4 interconnects.

The column interconnect operates similarly to the row interconnect and vertically routes signals to and from LABs, TriMatrix memory, DSP blocks, and IOEs. Each column of LABs is served by a dedicated column interconnect, which vertically routes signals to and from LABs, TriMatrix memory and DSP blocks, and horizontal IOEs. These column resources include:

- LUT chain interconnects within an LAB

- Register chain interconnects within an LAB

- C4 interconnects traversing a distance of four blocks in up and down direction

- C8 interconnects traversing a distance of eight blocks in up and down direction

- C16 column interconnects for high-speed vertical routing through the device

Stratix devices include an enhanced interconnect structure within LABs for routing LE output to LE input connections faster using LUT chain connections and register chain connections. The LUT chain connection allows the combinatorial output of an LE to directly drive the fast input of the LE right below it, bypassing the local interconnect. These resources can be used as a high-speed connection for wide fan-in functions from LE 1 to LE 10 in the same LAB. The register chain connection allows the register output of one LE to connect directly to the register input of the next LE in the LAB for fast shift registers. The Quartus II Compiler automatically takes advantage of these resources to improve utilization and performance. Figure 2–10 shows the LUT chain and register chain interconnects.

TriMatrix memory architecture can implement pipelined RAM by registering both the input and output signals to the RAM block. All TriMatrix memory block inputs are registered providing synchronous write cycles. In synchronous operation, the memory block generates its own self-timed strobe write enable (WREN) signal derived from the global or regional clock. In contrast, a circuit using asynchronous RAM must generate the RAM WREN signal while ensuring its data and address signals meet setup and hold time specifications relative to the WREN signal. The output registers can be bypassed. Flow-through reading is possible in the simple dual-port mode of M512 and M4K RAM blocks by clocking the read enable and read address registers on the negative clock edge and bypassing the output registers.

Two single-port memory blocks can be implemented in a single M4K block as long as each of the two independent block sizes is equal to or less than half of the M4K block size.

The Quartus II software automatically implements larger memory by combining multiple TriMatrix memory blocks. For example, two  $256 \times 16$ -bit RAM blocks can be combined to form a  $256 \times 32$ -bit RAM block. Memory performance does not degrade for memory blocks using the maximum number of words available in one memory block. Logical memory blocks using less than the maximum number of words use physical blocks in parallel, eliminating any external control logic that would increase delays. To create a larger high-speed memory block, the Quartus II software automatically combines memory blocks with LE control logic.

# Clear Signals

When applied to input registers, the asynchronous clear signal for the TriMatrix embedded memory immediately clears the input registers. However, the output of the memory block does not show the effects until the next clock edge. When applied to output registers, the asynchronous clear signal clears the output registers and the effects are seen immediately.

# **Parity Bit Support**

The memory blocks support a parity bit for each byte. The parity bit, along with internal LE logic, can implement parity checking for error detection to ensure data integrity. You can also use parity-size data words to store user-specified control bits. In the M4K and M-RAM blocks, byte enables are also available for data input masking during write operations.

## **Shift Register Support**

You can configure embedded memory blocks to implement shift registers for DSP applications such as pseudo-random number generators, multichannel filtering, auto-correlation, and cross-correlation functions. These and other DSP applications require local data storage, traditionally implemented with standard flip-flops, which can quickly consume many logic cells and routing resources for large shift registers. A more efficient alternative is to use embedded memory as a shift register block, which saves logic cell and routing resources and provides a more efficient implementation with the dedicated circuitry.

The size of a  $w \times m \times n$  shift register is determined by the input data width (w), the length of the taps (m), and the number of taps (n). The size of a  $w \times m \times n$  shift register must be less than or equal to the maximum number of memory bits in the respective block: 576 bits for the M512 RAM block and 4,608 bits for the M4K RAM block. The total number of shift register outputs (number of taps  $n \times$  width w) must be less than the maximum data width of the RAM block (18 for M512 blocks, 36 for M4K blocks). To create larger shift registers, the memory blocks are cascaded together.

Data is written into each address location at the falling edge of the clock and read from the address at the rising edge of the clock. The shift register mode logic automatically controls the positive and negative edge clocking to shift the data in one clock cycle. Figure 2–14 shows the TriMatrix memory block in the shift register mode.

#### Output Selection Multiplexer

The outputs from the various elements of the adder/output block are routed through an output selection multiplexer. Based on the DSP block operational mode and user settings, the multiplexer selects whether the output from the multiplier, the adder/subtractor/accumulator, or summation block feeds to the output.

#### Output Registers

Optional output registers for the DSP block outputs are controlled by four sets of control signals: clock [3..0], aclr [3..0], and ena [3..0]. Output registers can be used in any mode.

## **Modes of Operation**

The adder, subtractor, and accumulate functions of a DSP block have four modes of operation:

- Simple multiplier

- Multiply-accumulator

- Two-multipliers adder

- Four-multipliers adder

Each DSP block can only support one mode. Mixed modes in the same DSP block is not supported.

### Simple Multiplier Mode

In simple multiplier mode, the DSP block drives the multiplier sub-block result directly to the output with or without an output register. Up to four  $18 \times 18$ -bit multipliers or eight  $9 \times 9$ -bit multipliers can drive their results directly out of one DSP block. See Figure 2–35.

#### Clock Multiplication & Division

Each Stratix device enhanced PLL provides clock synthesis for PLL output ports using  $m/(n \times post\text{-scale counter})$  scaling factors. The input clock is divided by a pre-scale divider, *n*, and is then multiplied by the *m* feedback factor. The control loop drives the VCO to match  $f_{IN} \times (m/n)$ . Each output port has a unique post-scale counter that divides down the high-frequency VCO. For multiple PLL outputs with different frequencies, the VCO is set to the least common multiple of the output frequencies that meets its frequency specifications. Then, the post-scale dividers scale down the output frequency for each output port. For example, if output frequencies required from one PLL are 33 and 66 MHz, set the VCO to 330 MHz (the least common multiple in the VCO's range). There is one pre-scale counter, *n*, and one multiply counter, *m*, per PLL, with a range of 1 to 512 on each. There are two post-scale counters (*l*) for regional clock output ports, four counters (g) for global clock output ports, and up to four counters (e) for external clock outputs, all ranging from 1 to 1024 with a 50% duty cycle setting. The post-scale counters range from 1 to 512 with any non-50% duty cycle setting. The Quartus II software automatically chooses the appropriate scaling factors according to the input frequency, multiplication, and division values entered.

#### Clock Switchover

To effectively develop high-reliability network systems, clocking schemes must support multiple clocks to provide redundancy. For this reason, Stratix device enhanced PLLs support a flexible clock switchover capability. Figure 2–53 shows a block diagram of the switchover circuit. The switchover circuit is configurable, so you can define how to implement it. Clock-sense circuitry automatically switches from the primary to secondary clock for PLL reference when the primary clock signal is not present.

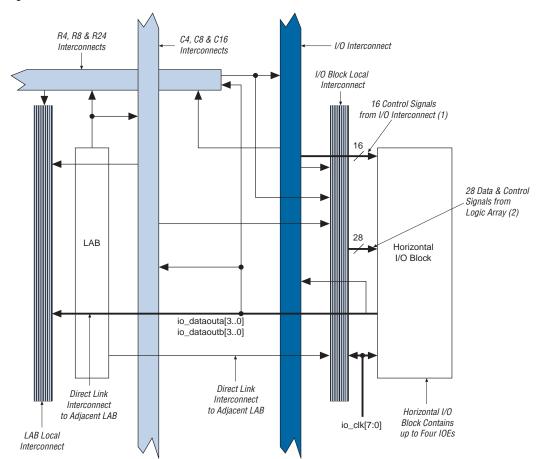

Figure 2-60. Row I/O Block Connection to the Interconnect

#### *Notes to Figure 2–60:*

- (1) The 16 control signals are composed of four output enables io\_boe[3..0], four clock enables io\_boe[3..0], four clocks io\_clk[3..0], and four clear signals io\_bclr[3..0].

- (2) The 28 data and control signals consist of eight data out lines: four lines each for DDR applications io\_dataouta[3..0] and io\_dataoutb[3..0], four output enables io\_coe[3..0], four input clock enables io\_cce\_in[3..0], four output clock enables io\_cce\_out[3..0], four clocks io\_cclk[3..0], and four clear signals io\_cclr[3..0].

| Table 2-39            | . EP1S40 Diffe  | erential Cha          | nnels (Part 2   | 2 of 2) / | Vote (1,         | )         |           |           |                           |           |        |  |

|-----------------------|-----------------|-----------------------|-----------------|-----------|------------------|-----------|-----------|-----------|---------------------------|-----------|--------|--|

|                       | Transmitter/    | Total                 | Maximum         | C         | Center Fast PLLs |           |           |           | Corner Fast PLLs (2), (3) |           |        |  |

| Package               | Receiver        | Channels              | Speed<br>(Mbps) | PLL1      | PLL2             | PLL3      | PLL4      | PLL7      | PLL8                      | PLL9      | PLL10  |  |

| 956-pin               | Transmitter     | 80                    | 840             | 18        | 17               | 17        | 18        | 20        | 20                        | 20        | 20     |  |

| BGA (4) Receiver      |                 | 840 (5)               | 35              | 35        | 35               | 35        | 20        | 20        | 20                        | 20        |        |  |

|                       | Receiver        | 80                    | 840             | 20        | 20               | 20        | 20        | 18        | 17                        | 17        | 18     |  |

|                       |                 |                       | 840 (5)         | 40        | 40               | 40        | 40        | 18        | 17                        | 17        | 18     |  |

| .,                    | Transmitter (4) | 80 (10)<br><i>(7)</i> | 840             | 18<br>(2) | 17<br>(3)        | 17<br>(3) | 18<br>(2) | 20        | 20                        | 20        | 20     |  |

| BGA                   |                 |                       | 840 (5), (8)    | 35<br>(5) | 35<br>(5)        | 35<br>(5) | 35<br>(5) | 20        | 20                        | 20        | 20     |  |

|                       | Receiver        | 80 (10)<br><i>(7)</i> | 840             | 20        | 20               | 20        | 20        | 18<br>(2) | 17<br>(3)                 | 17<br>(3) | 18 (2) |  |

|                       |                 |                       | 840 (5), (8)    | 40        | 40               | 40        | 40        | 18<br>(2) | 17<br>(3)                 | 17<br>(3) | 18 (2) |  |

| 1,508-pin<br>FineLine | Transmitter (4) | 80 (10)<br><i>(7)</i> | 840             | 18<br>(2) | 17<br>(3)        | 17<br>(3) | 18<br>(2) | 20        | 20                        | 20        | 20     |  |

| BGA                   |                 |                       | 840 (5), (8)    | 35<br>(5) | 35<br>(5)        | 35<br>(5) | 35<br>(5) | 20        | 20                        | 20        | 20     |  |

|                       | Receiver        | 80 (10)<br><i>(7)</i> | 840             | 20        | 20               | 20        | 20        | 18<br>(2) | 17<br>(3)                 | 17<br>(3) | 18 (2) |  |

|                       |                 |                       | 840 (5), (8)    | 40        | 40               | 40        | 40        | 18<br>(2) | 17<br>(3)                 | 17<br>(3) | 18 (2) |  |

| Table 2–40. EP1S60 Differential Channels (Part 1 of 2) Note (1) |              |          |                     |      |      |      |      |      |      |      |       |

|-----------------------------------------------------------------|--------------|----------|---------------------|------|------|------|------|------|------|------|-------|

|                                                                 | Transmitter/ | Total    | Maximum             | (-), |      |      |      |      |      |      |       |

| Package                                                         | Receiver     | Channels | Speed<br>(Mbps)     | PLL1 | PLL2 | PLL3 | PLL4 | PLL7 | PLL8 | PLL9 | PLL10 |

| 956-pin                                                         | Transmitter  | 80       | 840                 | 12   | 10   | 10   | 12   | 20   | 20   | 20   | 20    |

| BGA                                                             | (4)          |          | 840 (5), (8)        | 22   | 22   | 22   | 22   | 20   | 20   | 20   | 20    |

|                                                                 | Receiver 80  | 80       | 840                 | 20   | 20   | 20   | 20   | 12   | 10   | 10   | 12    |

|                                                                 |              |          | 840 <i>(5), (8)</i> | 40   | 40   | 40   | 40   | 12   | 10   | 10   | 12    |

| Table 4–7.        | Table 4–7. 1.8-V I/O Specifications |                                               |                          |                        |      |  |  |  |  |  |  |  |

|-------------------|-------------------------------------|-----------------------------------------------|--------------------------|------------------------|------|--|--|--|--|--|--|--|

| Symbol            | Parameter                           | Conditions                                    | Minimum                  | Maximum                | Unit |  |  |  |  |  |  |  |

| V <sub>CCIO</sub> | Output supply voltage               |                                               | 1.65                     | 1.95                   | V    |  |  |  |  |  |  |  |

| V <sub>IH</sub>   | High-level input voltage            |                                               | $0.65 \times V_{CCIO}$   | 2.25                   | V    |  |  |  |  |  |  |  |

| V <sub>IL</sub>   | Low-level input voltage             |                                               | -0.3                     | $0.35 \times V_{CCIO}$ | ٧    |  |  |  |  |  |  |  |

| V <sub>OH</sub>   | High-level output voltage           | $I_{OH} = -2 \text{ to } -8 \text{ mA } (10)$ | V <sub>CCIO</sub> - 0.45 |                        | ٧    |  |  |  |  |  |  |  |

| V <sub>OL</sub>   | Low-level output voltage            | I <sub>OL</sub> = 2 to 8 mA (10)              |                          | 0.45                   | V    |  |  |  |  |  |  |  |

| Table 4–8.        | Table 4–8. 1.5-V I/O Specifications |                              |                        |                         |      |  |  |  |  |  |  |  |

|-------------------|-------------------------------------|------------------------------|------------------------|-------------------------|------|--|--|--|--|--|--|--|

| Symbol            | Parameter                           | Conditions                   | Minimum                | Maximum                 | Unit |  |  |  |  |  |  |  |

| V <sub>CCIO</sub> | Output supply voltage               |                              | 1.4                    | 1.6                     | V    |  |  |  |  |  |  |  |

| V <sub>IH</sub>   | High-level input voltage            |                              | $0.65 \times V_{CCIO}$ | V <sub>CCIO</sub> + 0.3 | V    |  |  |  |  |  |  |  |

| V <sub>IL</sub>   | Low-level input voltage             |                              | -0.3                   | $0.35 \times V_{CCIO}$  | V    |  |  |  |  |  |  |  |

| V <sub>OH</sub>   | High-level output voltage           | I <sub>OH</sub> = -2 mA (10) | $0.75 \times V_{CCIO}$ |                         | V    |  |  |  |  |  |  |  |

| V <sub>OL</sub>   | Low-level output voltage            | I <sub>OL</sub> = 2 mA (10)  |                        | $0.25 \times V_{CCIO}$  | V    |  |  |  |  |  |  |  |

#### Notes to Tables 4–1 through 4–8:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Conditions beyond those listed in Table 4–1 may cause permanent damage to a device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse affects on the device.

- (3) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns, or overshoot to the voltage shown in Table 4-9, based on input duty cycle for input currents less than 100 mA. The overshoot is dependent upon duty cycle of the signal. The DC case is equivalent to 100% duty cycle.

- (4) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically.

- (5) V<sub>CCIO</sub> maximum and minimum conditions for LVPECL, LVDS, and 3.3-V PCML are shown in parentheses.

- (6) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (7) Typical values are for  $T_A$  = 25°C,  $V_{CCINT}$  = 1.5 V, and  $V_{CCIO}$  = 1.5 V, 1.8 V, 2.5 V, and 3.3 V.

- (8) This value is specified for normal device operation. The value may vary during power-up. This applies for all V<sub>CCIO</sub> settings (3.3, 2.5, 1.8, and 1.5 V).

- (9) Pin pull-up resistance values will lower if an external source drives the pin higher than V<sub>CCIO</sub>.

- (10) Drive strength is programmable according to the values shown in the *Stratix Architecture* chapter of the *Stratix Device Handbook, Volume 1*.

| Table 4–9. Overshoot Input Voltage with Respect to Duty Cycle (Part 1 of 2) |     |  |  |  |  |  |  |

|-----------------------------------------------------------------------------|-----|--|--|--|--|--|--|

| Vin (V) Maximum Duty Cycle (%)                                              |     |  |  |  |  |  |  |

| 4.0                                                                         | 100 |  |  |  |  |  |  |

| 4.1                                                                         | 90  |  |  |  |  |  |  |

| 4.2                                                                         | 50  |  |  |  |  |  |  |

| Table 4-36          | S. Stratix Performance (             | Part 2 | of 2) Notes                   | 5 (1), (2)    |                      |                      |                      |                      |       |  |

|---------------------|--------------------------------------|--------|-------------------------------|---------------|----------------------|----------------------|----------------------|----------------------|-------|--|

|                     |                                      | F      | Resources L                   | Jsed          | Performance          |                      |                      |                      |       |  |

|                     | Applications                         | LEs    | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -5<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade | Units |  |

| TriMatrix<br>memory | True dual-port<br>RAM 16K × 36 bit   | 0      | 1                             | 0             | 269.83               | 237.69               | 206.82               | 175.74               | MHz   |  |

| M-RAM<br>block      | Single port<br>RAM 32K × 18 bit      | 0      | 1                             | 0             | 275.86               | 244.55               | 212.76               | 180.83               | MHz   |  |

|                     | Simple dual-port<br>RAM 32K × 18 bit | 0      | 1                             | 0             | 275.86               | 244.55               | 212.76               | 180.83               | MHz   |  |

|                     | True dual-port<br>RAM 32K × 18 bit   | 0      | 1                             | 0             | 275.86               | 244.55               | 212.76               | 180.83               | MHz   |  |

|                     | Single port<br>RAM 64K × 9 bit       | 0      | 1                             | 0             | 287.85               | 253.29               | 220.36               | 187.26               | MHz   |  |

|                     | Simple dual-port<br>RAM 64K × 9 bit  | 0      | 1                             | 0             | 287.85               | 253.29               | 220.36               | 187.26               | MHz   |  |

|                     | True dual-port<br>RAM 64K × 9 bit    | 0      | 1                             | 0             | 287.85               | 253.29               | 220.36               | 187.26               | MHz   |  |

| DSP block           | 9 × 9-bit multiplier (3)             | 0      | 0                             | 1             | 335.0                | 293.94               | 255.68               | 217.24               | MHz   |  |

|                     | 18 × 18-bit multiplier (4)           | 0      | 0                             | 1             | 278.78               | 237.41               | 206.52               | 175.50               | MHz   |  |

|                     | $36 \times 36$ -bit multiplier (4)   | 0      | 0                             | 1             | 148.25               | 134.71               | 117.16               | 99.59                | MHz   |  |

|                     | 36 × 36-bit multiplier (5)           | 0      | 0                             | 1             | 278.78               | 237.41               | 206.52               | 175.5                | MHz   |  |

|                     | 18-bit, 4-tap FIR filter             | 0      | 0                             | 1             | 278.78               | 237.41               | 206.52               | 175.50               | MHz   |  |

| Larger<br>Designs   | 8-bit, 16-tap parallel<br>FIR filter | 58     | 0                             | 4             | 141.26               | 133.49               | 114.88               | 100.28               | MHz   |  |

|                     | 8-bit, 1,024-point FFT function      | 870    | 5                             | 1             | 261.09               | 235.51               | 205.21               | 175.22               | MHz   |  |

### Notes to Table 4–36:

- (1) These design performance numbers were obtained using the Quartus II software.

- (2) Numbers not listed will be included in a future version of the data sheet.

- (3) This application uses registered inputs and outputs.

- (4) This application uses registered multiplier input and output stages within the DSP block.

- (5) This application uses registered multiplier input, pipeline, and output stages within the DSP block.

| Table 4–39. DSP              | Block Internal Timing Microparameter Descriptions                                                                                                                                                                                                                                                                                                         |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                       | Parameter                                                                                                                                                                                                                                                                                                                                                 |

| t <sub>SU</sub>              | Input, pipeline, and output register setup time before clock                                                                                                                                                                                                                                                                                              |

| t <sub>H</sub>               | Input, pipeline, and output register hold time after clock                                                                                                                                                                                                                                                                                                |

| t <sub>co</sub>              | Input, pipeline, and output register clock-to-output delay                                                                                                                                                                                                                                                                                                |

| t <sub>INREG2PIPE9</sub>     | Input Register to DSP Block pipeline register in $9\times9$ -bit mode                                                                                                                                                                                                                                                                                     |

| t <sub>INREG2PIPE18</sub>    | Input Register to DSP Block pipeline register in 18 $\times$ 18-bit mode                                                                                                                                                                                                                                                                                  |

| t <sub>PIPE2OUTREG2ADD</sub> | DSP Block Pipeline Register to output register delay in Two-Multipliers Adder mode                                                                                                                                                                                                                                                                        |

| t <sub>PIPE2OUTREG4ADD</sub> | DSP Block Pipeline Register to output register delay in Four-Multipliers Adder mode                                                                                                                                                                                                                                                                       |

| t <sub>PD9</sub>             | Combinatorial input to output delay for $9 \times 9$                                                                                                                                                                                                                                                                                                      |

| t <sub>PD18</sub>            | Combinatorial input to output delay for 18 × 18                                                                                                                                                                                                                                                                                                           |

| t <sub>PD36</sub>            | Combinatorial input to output delay for $36 \times 36$                                                                                                                                                                                                                                                                                                    |

| t <sub>CLR</sub>             | Minimum clear pulse width                                                                                                                                                                                                                                                                                                                                 |

| t <sub>CLKHL</sub>           | Register minimum clock high or low time. This is a limit on the min time for the clock on the registers in these blocks. The actual performance is dependent upon the internal point-to-point delays in the blocks and may give slower performance as shown in Table 4–36 on page 4–20 and as reported by the timing analyzer in the Quartus II software. |

|                    | Table 4–43. Routing Delay Internal Timing Microparameter Descriptions (Part 2 of 2)                                                            |  |  |  |  |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Symbol             | Parameter                                                                                                                                      |  |  |  |  |  |  |  |  |

| t <sub>C4</sub>    | Delay for a C4 line with average loading; covers a distance of four LAB rows.                                                                  |  |  |  |  |  |  |  |  |

| t <sub>C8</sub>    | Delay for a C8 line with average loading; covers a distance of eight LAB rows.                                                                 |  |  |  |  |  |  |  |  |

| t <sub>C16</sub>   | Delay for a C16 line with average loading; covers a distance of 16 LAB rows.                                                                   |  |  |  |  |  |  |  |  |

| t <sub>LOCAL</sub> | Local interconnect delay, for connections within a LAB, and for the final routing hop of connections to LABs, DSP blocks, RAM blocks and I/Os. |  |  |  |  |  |  |  |  |

| Table 4–44. LE Internal Timing Microparameters |      |     |      |     |      |     |      |     |      |  |  |

|------------------------------------------------|------|-----|------|-----|------|-----|------|-----|------|--|--|

| Parameter                                      | -5   |     | -6   |     | _    | 7   | -8   |     | 11:4 |  |  |

|                                                | Min  | Max | Min  | Max | Min  | Max | Min  | Max | Unit |  |  |

| t <sub>SU</sub>                                | 10   |     | 10   |     | 11   |     | 13   |     | ps   |  |  |

| t <sub>H</sub>                                 | 100  |     | 100  |     | 114  |     | 135  |     | ps   |  |  |

| t <sub>CO</sub>                                |      | 156 |      | 176 |      | 202 |      | 238 | ps   |  |  |

| t <sub>LUT</sub>                               |      | 366 |      | 459 |      | 527 |      | 621 | ps   |  |  |

| t <sub>CLR</sub>                               | 100  |     | 100  |     | 114  |     | 135  |     | ps   |  |  |

| t <sub>PRE</sub>                               | 100  |     | 100  |     | 114  |     | 135  |     | ps   |  |  |

| t <sub>CLKHL</sub>                             | 1000 |     | 1111 |     | 1190 |     | 1400 |     | ps   |  |  |

| Table 4–45. IOE Internal TSU Microparameter by Device Density (Part 1 of 2) |                   |     |     |     |     |     |     |     |     |    |

|-----------------------------------------------------------------------------|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|----|

| Device                                                                      |                   | -   | -5  |     | -6  |     | -7  |     | -8  |    |

|                                                                             | Symbol            | Min | Max | Min | Max | Min | Max | Min | Max |    |

| EP1S10                                                                      | t <sub>SU_R</sub> | 76  |     | 80  |     | 80  |     | 80  |     | ps |

|                                                                             | t <sub>SU_C</sub> | 176 |     | 80  |     | 80  |     | 80  |     | ps |

| EP1S20                                                                      | t <sub>SU_R</sub> | 76  |     | 80  |     | 80  |     | 80  |     | ps |

|                                                                             | t <sub>SU_C</sub> | 76  |     | 80  |     | 80  |     | 80  |     | ps |

| EP1S25                                                                      | t <sub>SU_R</sub> | 276 |     | 280 |     | 280 |     | 280 |     | ps |

|                                                                             | t <sub>SU_C</sub> | 276 |     | 280 |     | 280 |     | 280 |     | ps |

| EP1S30                                                                      | t <sub>SU_R</sub> | 76  |     | 80  |     | 80  |     | 80  |     | ps |

|                                                                             | t <sub>SU_C</sub> | 176 |     | 180 |     | 180 |     | 180 |     | ps |

| Davis  | Symbol            | -   | -5  |     | -6  |     | -7  |     | -8  |    |

|--------|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|----|

| Device | Symbol            | Min | Max | Min | Max | Min | Max | Min | Max |    |

| EP1S40 | t <sub>SU_R</sub> | 76  |     | 80  |     | 80  |     | 80  |     | ps |

|        | t <sub>SU_C</sub> | 376 |     | 380 |     | 380 |     | 380 |     | ps |

| EP1S60 | t <sub>SU_R</sub> | 276 |     | 280 |     | 280 |     | 280 |     | ps |

|        | t <sub>SU_C</sub> | 276 |     | 280 |     | 280 |     | 280 |     | ps |

| EP1S80 | t <sub>SU_R</sub> | 426 |     | 430 |     | 430 |     | 430 |     | ps |

|        | t <sub>SU_C</sub> | 76  |     | 80  |     | 80  |     | 80  |     | ps |

| Table 4–46. IOE Internal Timing Microparameters |       |       |       |       |       |       |       |       |      |  |

|-------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|------|--|

| Symbol                                          | -     | -5    |       | -6    |       | -7    |       | -8    |      |  |

|                                                 | Min   | Max   | Min   | Max   | Min   | Max   | Min   | Max   | Unit |  |

| t <sub>H</sub>                                  | 68    |       | 71    |       | 82    |       | 96    |       | ps   |  |

| t <sub>CO_R</sub>                               |       | 171   |       | 179   |       | 206   |       | 242   | ps   |  |

| t <sub>CO_C</sub>                               |       | 171   |       | 179   |       | 206   |       | 242   | ps   |  |

| t <sub>PIN2COMBOUT_R</sub>                      |       | 1,234 |       | 1,295 |       | 1,490 |       | 1,753 | ps   |  |

| t <sub>PIN2COMBOUT_C</sub>                      |       | 1,087 |       | 1,141 |       | 1,312 |       | 1,544 | ps   |  |

| t <sub>COMBIN2PIN_R</sub>                       |       | 3,894 |       | 4,089 |       | 4,089 |       | 4,089 | ps   |  |

| t <sub>COMBIN2PIN_C</sub>                       |       | 4,299 |       | 4,494 |       | 4,494 |       | 4,494 | ps   |  |

| t <sub>CLR</sub>                                | 276   |       | 289   |       | 333   |       | 392   |       | ps   |  |

| t <sub>PRE</sub>                                | 260   |       | 273   |       | 313   |       | 369   |       | ps   |  |

| t <sub>CLKHL</sub>                              | 1,000 |       | 1,111 |       | 1,190 |       | 1,400 |       | ps   |  |

| Table 4–47. DSP Block Internal Timing Microparameters (Part 1 of 2) |     |       |     |       |     |       |     |       |          |  |  |

|---------------------------------------------------------------------|-----|-------|-----|-------|-----|-------|-----|-------|----------|--|--|

|                                                                     | -5  |       | -6  |       | -7  |       | -8  |       | II m i t |  |  |

| Symbol                                                              | Min | Max   | Min | Max   | Min | Max   | Min | Max   | Unit     |  |  |

| t <sub>SU</sub>                                                     | 0   |       | 0   |       | 0   |       | 0   |       | ps       |  |  |

| t <sub>H</sub>                                                      | 67  |       | 75  |       | 86  |       | 101 |       | ps       |  |  |

| t <sub>CO</sub>                                                     |     | 142   |     | 158   |     | 181   |     | 214   | ps       |  |  |

| t <sub>INREG2PIPE9</sub>                                            |     | 2,613 |     | 2,982 |     | 3,429 |     | 4,035 | ps       |  |  |

| t <sub>INREG2PIPE18</sub>                                           |     | 3,390 |     | 3,993 |     | 4,591 |     | 5,402 | ps       |  |  |

| Table 4-81. I         | Table 4–81. EP1S40 External I/O Timing on Column Pins Using Global Clock Networks |       |         |                |       |         |                |       |         |  |  |  |

|-----------------------|-----------------------------------------------------------------------------------|-------|---------|----------------|-------|---------|----------------|-------|---------|--|--|--|

| Davamatav             | -5 Speed Grade                                                                    |       | -6 Spee | -6 Speed Grade |       | d Grade | -8 Speed Grade |       | II.a.iA |  |  |  |

| Parameter             | Min                                                                               | Max   | Min     | Max            | Min   | Max     | Min            | Max   | Unit    |  |  |  |

| t <sub>INSU</sub>     | 2.126                                                                             |       | 2.268   |                | 2.558 |         | 2.930          |       | ns      |  |  |  |

| t <sub>INH</sub>      | 0.000                                                                             |       | 0.000   |                | 0.000 |         | 0.000          |       | ns      |  |  |  |

| t <sub>OUTCO</sub>    | 2.856                                                                             | 5.585 | 2.856   | 5.987          | 2.856 | 6.541   | 2.847          | 7.253 | ns      |  |  |  |

| t <sub>XZ</sub>       | 2.796                                                                             | 5.459 | 2.796   | 5.855          | 2.796 | 6.417   | 2.787          | 7.138 | ns      |  |  |  |

| t <sub>ZX</sub>       | 2.796                                                                             | 5.459 | 2.796   | 5.855          | 2.796 | 6.417   | 2.787          | 7.138 | ns      |  |  |  |

| t <sub>INSUPLL</sub>  | 1.466                                                                             |       | 1.455   |                | 1.711 |         | 1.906          |       | ns      |  |  |  |

| t <sub>INHPLL</sub>   | 0.000                                                                             |       | 0.000   |                | 0.000 |         | 0.000          |       | ns      |  |  |  |

| t <sub>OUTCOPLL</sub> | 1.092                                                                             | 2.345 | 1.092   | 2.510          | 1.092 | 2.455   | 1.089          | 2.473 | ns      |  |  |  |

| t <sub>XZPLL</sub>    | 1.032                                                                             | 2.219 | 1.032   | 2.378          | 1.032 | 2.331   | 1.029          | 2.358 | ns      |  |  |  |

| t <sub>ZXPLL</sub>    | 1.032                                                                             | 2.219 | 1.032   | 2.378          | 1.032 | 2.331   | 1.029          | 2.358 | ns      |  |  |  |

| Table 4–82. I      | Table 4–82. EP1S40 External I/O Timing on Row Pins Using Fast Regional Clock Networks |         |         |                |       |                |       |                |      |  |  |  |

|--------------------|---------------------------------------------------------------------------------------|---------|---------|----------------|-------|----------------|-------|----------------|------|--|--|--|

| Doromotor          | -5 Spee                                                                               | d Grade | -6 Spee | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |      |  |  |  |

| Parameter          | Min                                                                                   | Max     | Min     | Max            | Min   | Max            | Min   | Max            | Unit |  |  |  |

| t <sub>INSU</sub>  | 2.472                                                                                 |         | 2.685   |                | 3.083 |                | 3.056 |                | ns   |  |  |  |

| t <sub>INH</sub>   | 0.000                                                                                 |         | 0.000   |                | 0.000 |                | 0.000 |                | ns   |  |  |  |

| t <sub>OUTCO</sub> | 2.631                                                                                 | 5.258   | 2.631   | 5.625          | 2.631 | 6.105          | 2.745 | 7.324          | ns   |  |  |  |

| t <sub>XZ</sub>    | 2.658                                                                                 | 5.312   | 2.658   | 5.681          | 2.658 | 6.173          | 2.772 | 7.406          | ns   |  |  |  |

| t <sub>ZX</sub>    | 2.658                                                                                 | 5.312   | 2.658   | 5.681          | 2.658 | 6.173          | 2.772 | 7.406          | ns   |  |  |  |

Tables 4–91 through 4–96 show the external timing parameters on column and row pins for EP1S80 devices.

| Table 4–91. EP1S80 External I/O Timing on Column Pins Using Fast Regional Clock Networks Note (1) |         |         |         |         |         |         |                |     |      |  |  |

|---------------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|----------------|-----|------|--|--|

| Davamatav                                                                                         | -5 Spee | d Grade | -6 Spee | d Grade | -7 Spee | d Grade | -8 Speed Grade |     | 11   |  |  |

| Parameter                                                                                         | Min     | Max     | Min     | Max     | Min     | Max     | Min            | Max | Unit |  |  |

| t <sub>INSU</sub>                                                                                 | 2.328   |         | 2.528   |         | 2.900   |         | NA             |     | ns   |  |  |

| t <sub>INH</sub>                                                                                  | 0.000   |         | 0.000   |         | 0.000   |         | NA             |     | ns   |  |  |

| t <sub>OUTCO</sub>                                                                                | 2.422   | 4.830   | 2.422   | 5.169   | 2.422   | 5.633   | NA             | NA  | ns   |  |  |

| t <sub>XZ</sub>                                                                                   | 2.362   | 4.704   | 2.362   | 5.037   | 2.362   | 5.509   | NA             | NA  | ns   |  |  |

| t <sub>ZX</sub>                                                                                   | 2.362   | 4.704   | 2.362   | 5.037   | 2.362   | 5.509   | NA             | NA  | ns   |  |  |

| Table 4–92. I         | Table 4–92. EP1S80 External I/O Timing on Column Pins Using Regional Clock Networks Note (1) |       |         |                |       |         |         |         |       |  |  |  |

|-----------------------|----------------------------------------------------------------------------------------------|-------|---------|----------------|-------|---------|---------|---------|-------|--|--|--|

| Parameter             | -5 Speed Grade                                                                               |       | -6 Spee | -6 Speed Grade |       | d Grade | -8 Spee | d Grade | Unit  |  |  |  |

| Parameter             | Min                                                                                          | Max   | Min     | Max            | Min   | Max     | Min     | Max     | UIIIL |  |  |  |

| t <sub>INSU</sub>     | 1.760                                                                                        |       | 1.912   |                | 2.194 |         | NA      |         | ns    |  |  |  |

| t <sub>INH</sub>      | 0.000                                                                                        |       | 0.000   |                | 0.000 |         | NA      |         | ns    |  |  |  |

| t <sub>OUTCO</sub>    | 2.761                                                                                        | 5.398 | 2.761   | 5.785          | 2.761 | 6.339   | NA      | NA      | ns    |  |  |  |

| t <sub>XZ</sub>       | 2.701                                                                                        | 5.272 | 2.701   | 5.653          | 2.701 | 6.215   | NA      | NA      | ns    |  |  |  |

| t <sub>ZX</sub>       | 2.701                                                                                        | 5.272 | 2.701   | 5.653          | 2.701 | 6.215   | NA      | NA      | ns    |  |  |  |

| t <sub>INSUPLL</sub>  | 0.462                                                                                        |       | 0.606   |                | 0.785 |         | NA      |         | ns    |  |  |  |

| t <sub>INHPLL</sub>   | 0.000                                                                                        |       | 0.000   |                | 0.000 |         | NA      |         | ns    |  |  |  |

| t <sub>OUTCOPLL</sub> | 1.661                                                                                        | 2.849 | 1.661   | 2.859          | 1.661 | 2.881   | NA      | NA      | ns    |  |  |  |

| t <sub>XZPLL</sub>    | 1.601                                                                                        | 2.723 | 1.601   | 2.727          | 1.601 | 2.757   | NA      | NA      | ns    |  |  |  |

| t <sub>ZXPLL</sub>    | 1.601                                                                                        | 2.723 | 1.601   | 2.727          | 1.601 | 2.757   | NA      | NA      | ns    |  |  |  |

| Table 4–104. Stratix I/ | Table 4–104. Stratix I/O Standard Row Pin Input Delay Adders |         |         |         |         |         |         |         |      |  |  |

|-------------------------|--------------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|------|--|--|

| Davis marks in          | -5 Spee                                                      | d Grade | -6 Spee | d Grade | -7 Spee | d Grade | -8 Spee | d Grade | 11   |  |  |

| Parameter               | Min                                                          | Max     | Min     | Max     | Min     | Max     | Min     | Max     | Unit |  |  |

| LVCMOS                  |                                                              | 0       |         | 0       |         | 0       |         | 0       | ps   |  |  |

| 3.3-V LVTTL             |                                                              | 0       |         | 0       |         | 0       |         | 0       | ps   |  |  |

| 2.5-V LVTTL             |                                                              | 21      |         | 22      |         | 25      |         | 29      | ps   |  |  |

| 1.8-V LVTTL             |                                                              | 181     |         | 190     |         | 218     |         | 257     | ps   |  |  |

| 1.5-V LVTTL             |                                                              | 300     |         | 315     |         | 362     |         | 426     | ps   |  |  |

| GTL+                    |                                                              | -152    |         | -160    |         | -184    |         | -216    | ps   |  |  |

| CTT                     |                                                              | -168    |         | -177    |         | -203    |         | -239    | ps   |  |  |

| SSTL-3 Class I          |                                                              | -193    |         | -203    |         | -234    |         | -275    | ps   |  |  |

| SSTL-3 Class II         |                                                              | -193    |         | -203    |         | -234    |         | -275    | ps   |  |  |

| SSTL-2 Class I          |                                                              | -262    |         | -276    |         | -317    |         | -373    | ps   |  |  |

| SSTL-2 Class II         |                                                              | -262    |         | -276    |         | -317    |         | -373    | ps   |  |  |

| SSTL-18 Class I         |                                                              | -105    |         | -111    |         | -127    |         | -150    | ps   |  |  |

| SSTL-18 Class II        |                                                              | 0       |         | 0       |         | 0       |         | 0       | ps   |  |  |

| 1.5-V HSTL Class I      |                                                              | -151    |         | -159    |         | -183    |         | -215    | ps   |  |  |

| 1.8-V HSTL Class I      |                                                              | -126    |         | -133    |         | -153    |         | -179    | ps   |  |  |

| LVDS                    |                                                              | -149    |         | -157    |         | -180    |         | -212    | ps   |  |  |

| LVPECL                  |                                                              | -149    |         | -157    |         | -180    |         | -212    | ps   |  |  |

| 3.3-V PCML              |                                                              | -65     |         | -69     |         | -79     |         | -93     | ps   |  |  |

| HyperTransport          |                                                              | 77      |         | -81     |         | -93     |         | -110    | ps   |  |  |

Table 4–117. Stratix Maximum Input Clock Rate for CLK[7..4] & CLK[15..12] Pins in Wire-Bond Packages (Part 2 of 2)

| I/O Standard                  | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------|-------------------|-------------------|-------------------|------|

| GTL+                          | 250               | 200               | 200               | MHz  |

| SSTL-3 Class I                | 300               | 250               | 250               | MHz  |

| SSTL-3 Class II               | 300               | 250               | 250               | MHz  |

| SSTL-2 Class I                | 300               | 250               | 250               | MHz  |

| SSTL-2 Class II               | 300               | 250               | 250               | MHz  |

| SSTL-18 Class I               | 300               | 250               | 250               | MHz  |

| SSTL-18 Class II              | 300               | 250               | 250               | MHz  |

| 1.5-V HSTL Class I            | 300               | 180               | 180               | MHz  |

| 1.5-V HSTL Class II           | 300               | 180               | 180               | MHz  |

| 1.8-V HSTL Class I            | 300               | 180               | 180               | MHz  |

| 1.8-V HSTL Class II           | 300               | 180               | 180               | MHz  |

| 3.3-V PCI                     | 422               | 390               | 390               | MHz  |

| 3.3-V PCI-X 1.0               | 422               | 390               | 390               | MHz  |

| Compact PCI                   | 422               | 390               | 390               | MHz  |

| AGP 1×                        | 422               | 390               | 390               | MHz  |

| AGP 2×                        | 422               | 390               | 390               | MHz  |

| CTT                           | 250               | 180               | 180               | MHz  |

| Differential 1.5-V HSTL<br>C1 | 300               | 180               | 180               | MHz  |

| LVPECL (1)                    | 422               | 400               | 400               | MHz  |

| PCML (1)                      | 215               | 200               | 200               | MHz  |

| LVDS (1)                      | 422               | 400               | 400               | MHz  |

| HyperTransport technology (1) | 422               | 400               | 400               | MHz  |

Table 4–118. Stratix Maximum Input Clock Rate for CLK[0, 2, 9, 11] Pins & FPLL[10..7]CLK Pins in Wire-Bond Packages (Part 1 of 2)

| I/O Standard | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|--------------|-------------------|-------------------|-------------------|------|

| LVTTL        | 422               | 390               | 390               | MHz  |

| 2.5 V        | 422               | 390               | 390               | MHz  |

| 1.8 V        | 422               | 390               | 390               | MHz  |

| 1.5 V        | 422               | 390               | 390               | MHz  |

# Table 4–123. Stratix Maximum Output Clock Rate (Using I/O Pins) for PLL[1, 2, 3, 4] Pins in Wire-Bond Packages (Part 2 of 2)

| I/O Standard                  | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |  |

|-------------------------------|-------------------|-------------------|-------------------|------|--|

| LVDS (2)                      | 400               | 311               | 311               | MHz  |  |

| HyperTransport technology (2) | 420               | 400               | 400               | MHz  |  |

#### Notes to Tables 4-120 through 4-123:

- (1) Differential SSTL-2 outputs are only available on column clock pins.

- (2) These parameters are only available on row I/O pins.

- (3) SSTL-2 in maximum drive strength condition. See Table 4–101 on page 4–62 for more information on exact loading conditions for each I/O standard.

- (4) SSTL-2 in minimum drive strength with  $\leq$ 10pF output load condition.

- (5) SSTL-2 in minimum drive strength with > 10pF output load condition.

- (6) Differential SSTL-2 outputs are only supported on column clock pins.