Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 1057                                                    |

| Number of Logic Elements/Cells | 10570                                                   |

| Total RAM Bits                 | 920448                                                  |

| Number of I/O                  | 426                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                         |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 780-BBGA                                                |

| Supplier Device Package        | 780-FBGA (29x29)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s10f780c6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Section I. Stratix Device Family Data Sheet

This section provides the data sheet specifications for Stratix® devices. They contain feature definitions of the internal architecture, configuration and JTAG boundary-scan testing information, DC operating conditions, AC timing parameters, a reference to power consumption, and ordering information for Stratix devices.

This section contains the following chapters:

- Chapter 1, Introduction

- Chapter 2, Stratix Architecture

- Chapter 3, Configuration & Testing

- Chapter 4, DC & Switching Characteristics

- Chapter 5, Reference & Ordering Information

## **Revision History**

The table below shows the revision history for Chapters 1 through 5.

| Chapter | Date/Version         | Changes Made                                                                                                                                                                                                                                                                                                                     |

|---------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | July 2005, v3.2      | Minor content changes.                                                                                                                                                                                                                                                                                                           |

|         | September 2004, v3.1 | Updated Table 1–6 on page 1–5.                                                                                                                                                                                                                                                                                                   |

|         | April 2004, v3.0     | <ul> <li>Main section page numbers changed on first page.</li> <li>Changed PCI-X to PCI-X 1.0 in "Features" on page 1–2.</li> <li>Global change from SignalTap to SignalTap II.</li> <li>The DSP blocks in "Features" on page 1–2 provide dedicated implementation of multipliers that are now "faster than 300 MHz."</li> </ul> |

|         | January 2004, v2.2   | Updated -5 speed grade device information in Table 1-6.                                                                                                                                                                                                                                                                          |

|         | October 2003, v2.1   | Add -8 speed grade device information.                                                                                                                                                                                                                                                                                           |

|         | July 2003, v2.0      | Format changes throughout chapter.                                                                                                                                                                                                                                                                                               |

Altera Corporation Section I–1

Table 2–2 shows the Stratix device's routing scheme.

| Table 2–2. Strat            | ix De     | vice F         | Routin             | ng Scl                   | heme            |                 |                  |                 |                 |                  |          |                |               |             |            |            |          |

|-----------------------------|-----------|----------------|--------------------|--------------------------|-----------------|-----------------|------------------|-----------------|-----------------|------------------|----------|----------------|---------------|-------------|------------|------------|----------|

|                             |           |                |                    |                          |                 |                 |                  | Des             | stinat          | ion              |          |                |               |             |            |            |          |

| Source                      | LUT Chain | Register Chain | Local Interconnect | Direct Link Interconnect | R4 Interconnect | R8 Interconnect | R24 Interconnect | C4 Interconnect | C8 Interconnect | C16 Interconnect | TE       | M512 RAM Block | M4K RAM Block | M-RAM Block | DSP Blocks | Column 10E | Row IOE  |

| LUT Chain                   |           |                |                    |                          |                 |                 |                  |                 |                 |                  | >        |                |               |             |            |            |          |

| Register Chain              |           |                |                    |                          |                 |                 |                  |                 |                 |                  | <b>\</b> |                |               |             |            |            |          |

| Local<br>Interconnect       |           |                |                    |                          |                 |                 |                  |                 |                 |                  | <b>✓</b> | <b>✓</b>       | <b>✓</b>      | <b>✓</b>    | <b>✓</b>   | <b>✓</b>   | <b>\</b> |

| Direct Link<br>Interconnect |           |                | <b>✓</b>           |                          |                 |                 |                  |                 |                 |                  |          |                |               |             |            |            |          |

| R4 Interconnect             |           |                | <b>✓</b>           |                          | <b>✓</b>        |                 | <b>✓</b>         | <b>✓</b>        |                 | <b>✓</b>         |          |                |               |             |            |            |          |

| R8 Interconnect             |           |                | <b>✓</b>           |                          |                 | <b>✓</b>        |                  |                 | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| R24<br>Interconnect         |           |                |                    |                          | <b>✓</b>        |                 | <b>~</b>         | <b>✓</b>        |                 | <b>✓</b>         |          |                |               |             |            |            |          |

| C4 Interconnect             |           |                | <b>✓</b>           |                          | <b>✓</b>        |                 |                  | <b>✓</b>        |                 |                  |          |                |               |             |            |            |          |

| C8 Interconnect             |           |                | <b>✓</b>           |                          |                 | <b>✓</b>        |                  |                 | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| C16<br>Interconnect         |           |                |                    |                          | <b>✓</b>        |                 | <b>\</b>         | <b>\</b>        |                 | <b>✓</b>         |          |                |               |             |            |            |          |

| LE                          | <b>✓</b>  | <b>✓</b>       | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        | <b>✓</b>        |                  | <b>✓</b>        | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| M512 RAM<br>Block           |           |                | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        | <b>✓</b>        |                  | <b>\</b>        | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| M4K RAM Block               |           |                | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        | <b>✓</b>        |                  | <b>✓</b>        | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| M-RAM Block                 |           |                |                    |                          |                 |                 |                  | <b>✓</b>        | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| DSP Blocks                  |           |                | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        | <b>✓</b>        |                  | <b>✓</b>        | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| Column IOE                  |           |                |                    | <b>✓</b>                 |                 |                 |                  | <b>✓</b>        | <b>✓</b>        | <b>✓</b>         |          |                |               |             |            |            |          |

| Row IOE                     |           |                |                    | <b>✓</b>                 |                 | <b>✓</b>        | <b>✓</b>         | <b>✓</b>        | <b>✓</b>        | <b>✓</b>         |          |                |               |             |            |            |          |

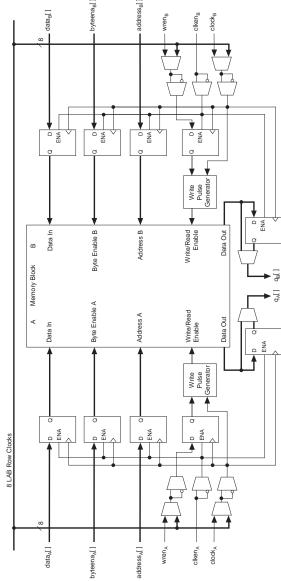

Figure 2–24. Independent Clock Mode Notes (1), (2)

Notes to Figure 2-24

- (1) All registers shown have asynchronous clear ports.

- (2) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

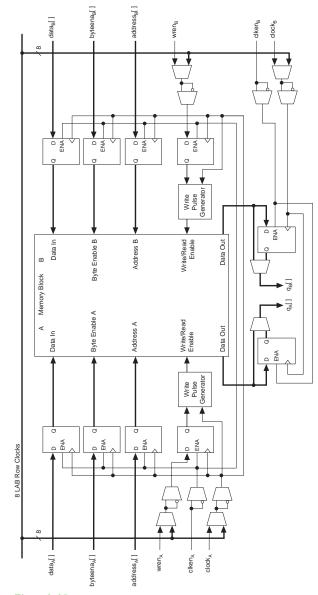

Figure 2–25. Input/Output Clock Mode in True Dual-Port Mode Notes (1), (2)

Notes to Figure 2-25:

- (1) All registers shown have asynchronous clear ports.

- (2) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

#### Read/Write Clock Mode

The memory blocks implement read/write clock mode for simple dual-port memory. You can use up to two clocks in this mode. The write clock controls the block's data inputs, wraddress, and wren. The read clock controls the data output, rdaddress, and rden. The memory blocks support independent clock enables for each clock and asynchronous clear signals for the read- and write-side registers. Figure 2–27 shows a memory block in read/write clock mode.

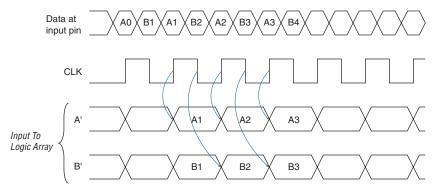

clock signals are routed from LAB row clocks and are generated from specific LAB rows at the DSP block interface. The LAB row source for control signals, data inputs, and outputs is shown in Table 2–17.

| Table 2-17. D           | SP Block Signal Source       | s & Destinations |              |

|-------------------------|------------------------------|------------------|--------------|

| LAB Row at<br>Interface | Control Signals<br>Generated | Data Inputs      | Data Outputs |

| 1                       | signa                        | A1[170]          | OA[170]      |

| 2                       | aclr0<br>accum_sload0        | B1[170]          | OB[170]      |

| 3                       | addnsub1<br>clock0<br>ena0   | A2[170]          | OC[170]      |

| 4                       | aclr1<br>clock1<br>ena1      | B2[170]          | OD[170]      |

| 5                       | aclr2<br>clock2<br>ena2      | A3[170]          | OE[170]      |

| 6                       | sign_b<br>clock3<br>ena3     | B3[170]          | OF[170]      |

| 7                       | clear3<br>accum_sload1       | A4[170]          | OG[170]      |

| 8                       | addnsub3                     | B4[170]          | OH[170]      |

# PLLs & Clock Networks

Stratix devices provide a hierarchical clock structure and multiple PLLs with advanced features. The large number of clocking resources in combination with the clock synthesis precision provided by enhanced and fast PLLs provides a complete clock management solution.

## **Global & Hierarchical Clocking**

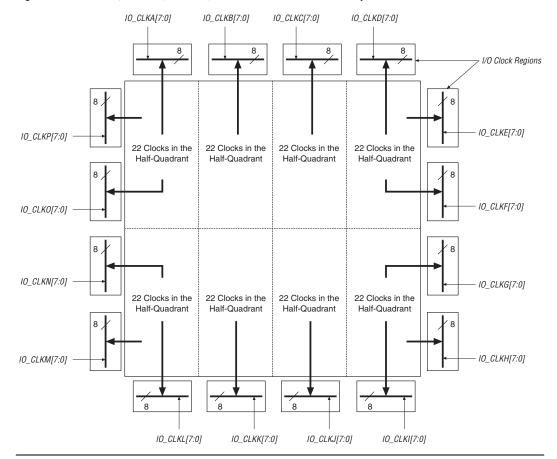

Stratix devices provide 16 dedicated global clock networks, 16 regional clock networks (four per device quadrant), and 8 dedicated fast regional clock networks (for EP1S10, EP1S20, and EP1S25 devices), and 16 dedicated fast regional clock networks (for EP1S30 EP1S40, and EP1S60, and EP1S80 devices). These clocks are organized into a hierarchical clock structure that allows for up to 22 clocks per device region with low skew and delay. This hierarchical clocking scheme provides up to 48 unique clock domains within Stratix devices.

There are 16 dedicated clock pins (CLK [15..0]) to drive either the global or regional clock networks. Four clock pins drive each side of the device, as shown in Figure 2–42. Enhanced and fast PLL outputs can also drive the global and regional clock networks.

#### Global Clock Network

These clocks drive throughout the entire device, feeding all device quadrants. The global clock networks can be used as clock sources for all resources within the device—IOEs, LEs, DSP blocks, and all memory blocks. These resources can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin. The global clock networks can also be driven by internal logic for internally generated global clocks and asynchronous clears, clock enables, or other control signals with large fanout. Figure 2–42 shows the 16 dedicated CLK pins driving global clock networks.

Figure 2-48. EP1S30, EP1S40, EP1S60, EP1S80 Device I/O Clock Groups

You can use the Quartus II software to control whether a clock input pin is either global, regional, or fast regional. The Quartus II software automatically selects the clocking resources if not specified.

#### **Enhanced & Fast PLLs**

Stratix devices provide robust clock management and synthesis using up to four enhanced PLLs and eight fast PLLs. These PLLs increase performance and provide advanced clock interfacing and clock-frequency synthesis. With features such as clock switchover, spread spectrum clocking, programmable bandwidth, phase and delay control, and PLL reconfiguration, the Stratix device's enhanced PLLs provide you with complete control of your clocks and system timing. The fast PLLs

#### Clock Feedback

The following four feedback modes in Stratix device enhanced PLLs allow multiplication and/or phase and delay shifting:

- Zero delay buffer: The external clock output pin is phase-aligned with the clock input pin for zero delay. Altera recommends using the same I/O standard on the input clock and the output clocks for optimum performance.

- External feedback: The external feedback input pin, FBIN, is phase-aligned with the clock input, CLK, pin. Aligning these clocks allows you to remove clock delay and skew between devices. This mode is only possible for PLLs 5 and 6. PLLs 5 and 6 each support feedback for one of the dedicated external outputs, either one single-ended or one differential pair. In this mode, one *e* counter feeds back to the PLL FBIN input, becoming part of the feedback loop. Altera recommends using the same I/O standard on the input clock, the FBIN pin, and the output clocks for optimum performance.

- Normal mode: If an internal clock is used in this mode, it is phasealigned to the input clock pin. The external clock output pin will have a phase delay relative to the clock input pin if connected in this mode. You define which internal clock output from the PLL should be phase-aligned to the internal clock pin.

- No compensation: In this mode, the PLL will not compensate for any clock networks or external clock outputs.

#### Phase & Delay Shifting

Stratix device enhanced PLLs provide advanced programmable phase and clock delay shifting. These parameters are set in the Quartus II software.

#### Phase Delay

The Quartus II software automatically sets the phase taps and counter settings according to the phase shift entry. You enter a desired phase shift and the Quartus II software automatically sets the closest setting achievable. This type of phase shift is not reconfigurable during system operation. For phase shifting, enter a phase shift (in degrees or time units) for each PLL clock output port or for all outputs together in one shift. You can select phase-shifting values in time units with a resolution of 156.25 to 416.66 ps. This resolution is a function of frequency input and the multiplication and division factors (that is, it is a function of the VCO period), with the finest step being equal to an eighth (×0.125) of the VCO period. Each clock output counter can choose a different phase of the

The pllenable pin is a dedicated pin that enables/disables PLLs. When the pllenable pin is low, the clock output ports are driven by GND and all the PLLs go out of lock. When the pllenable pin goes high again, the PLLs relock and resynchronize to the input clocks. You can choose which PLLs are controlled by the pllenable signal by connecting the pllenable input port of the altpll megafunction to the common pllenable input pin.

The areset signals are reset/resynchronization inputs for each PLL. The areset signal should be asserted every time the PLL loses lock to guarantee correct phase relationship between the PLL output clocks. Users should include the areset signal in designs if any of the following conditions are true:

- PLL Reconfiguration or Clock switchover enables in the design.

- Phase relationships between output clocks need to be maintained after a loss of lock condition

The device input pins or logic elements (LEs) can drive these input signals. When driven high, the PLL counters will reset, clearing the PLL output and placing the PLL out of lock. The VCO will set back to its nominal setting (~700 MHz). When driven low again, the PLL will resynchronize to its input as it relocks. If the target VCO frequency is below this nominal frequency, then the output frequency will start at a higher value than desired as the PLL locks. If the system cannot tolerate this, the clkena signal can disable the output clocks until the PLL locks.

The pfdena signals control the phase frequency detector (PFD) output with a programmable gate. If you disable the PFD, the VCO operates at its last set value of control voltage and frequency with some long-term drift to a lower frequency. The system continues running when the PLL goes out of lock or the input clock is disabled. By maintaining the last locked frequency, the system has time to store its current settings before shutting down. You can either use your own control signal or a clkloss status signal to trigger pfdena.

The clkena signals control the enhanced PLL regional and global outputs. Each regional and global output port has its own clkena signal. The clkena signals synchronously disable or enable the clock at the PLL output port by gating the outputs of the g and l counters. The clkena signals are registered on the falling edge of the counter output clock to enable or disable the clock without glitches. Figure 2–57 shows the waveform example for a PLL clock port enable. The PLL can remain locked independent of the clkena signals since the loop-related counters are not affected. This feature is useful for applications that require a low power or sleep mode. Upon re-enabling, the PLL does not need a

#### Control Signals

The fast PLL has the same lock output, pllenable input, and are set input control signals as the enhanced PLL.

If the input clock stops and causes the PLL to lose lock, then the PLL must be reset for correct phase shift operation.

For more information on high-speed differential I/O support, see "High-Speed Differential I/O Support" on page 2–130.

# I/O Structure

IOEs provide many features, including:

- Dedicated differential and single-ended I/O buffers

- 3.3-V, 64-bit, 66-MHz PCI compliance

- 3.3-V, 64-bit, 133-MHz PCI-X 1.0 compliance

- Joint Test Action Group (JTAG) boundary-scan test (BST) support

- Differential on-chip termination for LVDS I/O standard

- Programmable pull-up during configuration

- Output drive strength control

- Slew-rate control

- Tri-state buffers

- Bus-hold circuitry

- Programmable pull-up resistors

- Programmable input and output delays

- Open-drain outputs

- DQ and DQS I/O pins

- Double-data rate (DDR) Registers

The IOE in Stratix devices contains a bidirectional I/O buffer, six registers, and a latch for a complete embedded bidirectional single data rate or DDR transfer. Figure 2–59 shows the Stratix IOE structure. The IOE contains two input registers (plus a latch), two output registers, and two output enable registers. The design can use both input registers and the latch to capture DDR input and both output registers to drive DDR outputs. Additionally, the design can use the output enable (OE) register for fast clock-to-output enable timing. The negative edge-clocked OE register is used for DDR SDRAM interfacing. The Quartus II software automatically duplicates a single OE register that controls multiple output or bidirectional pins.

Figure 2-66. Input Timing Diagram in DDR Mode

When using the IOE for DDR outputs, the two output registers are configured to clock two data paths from LEs on rising clock edges. These output registers are multiplexed by the clock to drive the output pin at a  $\times 2$  rate. One output register clocks the first bit out on the clock high time, while the other output register clocks the second bit out on the clock low time. Figure 2–67 shows the IOE configured for DDR output. Figure 2–68 shows the DDR output timing diagram.

Tables 2–25 and 2–26 show the performance specification for DDR SDRAM, RLDRAM II, QDR SRAM, QDRII SRAM, and ZBT SRAM interfaces in EP1S10 through EP1S40 devices and in EP1S60 and EP1S80 devices. The DDR SDRAM and QDR SRAM numbers in Table 2–25 have been verified with hardware characterization with third-party DDR SDRAM and QDR SRAM devices over temperature and voltage extremes.

| Table 2–25. External                 | Table 2–25. External RAM Support in EP1S10 through EP1S40 Devices |                          |           |               |               |               |                |               |  |  |  |  |  |

|--------------------------------------|-------------------------------------------------------------------|--------------------------|-----------|---------------|---------------|---------------|----------------|---------------|--|--|--|--|--|

|                                      |                                                                   | Maximum Clock Rate (MHz) |           |               |               |               |                |               |  |  |  |  |  |

| DDR Memory Type                      | I/O<br>Standard                                                   | -5 Speed<br>Grade        | -6 Spee   | d Grade       | -7 Spec       | ed Grade      | -8 Speed Grade |               |  |  |  |  |  |

|                                      |                                                                   | Flip-Chip                | Flip-Chip | Wire-<br>Bond | Flip-<br>Chip | Wire-<br>Bond | Flip-<br>Chip  | Wire-<br>Bond |  |  |  |  |  |

| DDR SDRAM (1), (2)                   | SSTL-2                                                            | 200                      | 167       | 133           | 133           | 100           | 100            | 100           |  |  |  |  |  |

| DDR SDRAM - side banks (2), (3), (4) | SSTL-2                                                            | 150                      | 133       | 110           | 133           | 100           | 100            | 100           |  |  |  |  |  |

| RLDRAM II (4)                        | 1.8-V HSTL                                                        | 200                      | (5)       | (5)           | (5)           | (5)           | (5)            | (5)           |  |  |  |  |  |

| QDR SRAM (6)                         | 1.5-V HSTL                                                        | 167                      | 167       | 133           | 133           | 100           | 100            | 100           |  |  |  |  |  |

| QDRII SRAM (6)                       | 1.5-V HSTL                                                        | 200                      | 167       | 133           | 133           | 100           | 100            | 100           |  |  |  |  |  |

| ZBT SRAM (7)                         | LVTTL                                                             | 200                      | 200       | 200           | 167           | 167           | 133            | 133           |  |  |  |  |  |

#### Notes to Table 2-25:

- (1) These maximum clock rates apply if the Stratix device uses DQS phase-shift circuitry to interface with DDR SDRAM. DQS phase-shift circuitry is only available in the top and bottom I/O banks (I/O banks 3, 4, 7, and 8).

- (2) For more information on DDR SDRAM, see AN 342: Interfacing DDR SDRAM with Stratix & Stratix GX Devices.

- (3) DDR SDRAM is supported on the Stratix device side I/O banks (I/O banks 1, 2, 5, and 6) without dedicated DQS phase-shift circuitry. The read DQS signal is ignored in this mode.

- (4) These performance specifications are preliminary.

- (5) This device does not support RLDRAM II.

- (6) For more information on QDR or QDRII SRAM, see AN 349: QDR SRAM Controller Reference Design for Stratix & Stratix GX Devices.

- (7) For more information on ZBT SRAM, see AN 329: ZBT SRAM Controller Reference Design for Stratix & Stratix GX Devices.

| Symbol                  | Parameter                                                                     | Conditions                                                                                 | Minimum | Typical | Maximum | Unit |

|-------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------|---------|---------|------|

| V <sub>ICM</sub>        | Output differential voltage (single-ended)  Change in V <sub>OD</sub> between | LVDS<br>$0.3 \text{ V} \leq \text{V}_{\text{ID}} \leq 1.0 \text{ V}$<br>W = 1  through  10 | 100     |         | 1,100   | mV   |

|                         |                                                                               | LVDS<br>$0.3 \text{ V} \leq V_{\text{ID}} \leq 1.0 \text{ V}$<br>W = 1  through  10        | 1,600   |         | 1,800   | mV   |

|                         |                                                                               | LVDS<br>0.2 V ≤V <sub>ID</sub> ≤1.0 V<br>W = 1                                             | 1,100   |         | 1,600   | mV   |

|                         |                                                                               | LVDS<br>$0.1 \text{ V} \leq V_{\text{ID}} \leq 1.0 \text{ V}$<br>W = 2  through  10        | 1,100   |         | 1,600   | mV   |

| V <sub>OD</sub> (1)     | Output differential voltage (single-ended)                                    | R <sub>L</sub> = 100 Ω                                                                     | 250     | 375     | 550     | mV   |

| Δ V <sub>OD</sub>       | Change in V <sub>OD</sub> between high and low                                | R <sub>L</sub> = 100 Ω                                                                     |         |         | 50      | mV   |

| V <sub>OCM</sub>        | Output common mode voltage                                                    | $R_L = 100 \Omega$                                                                         | 1,125   | 1,200   | 1,375   | mV   |

| $\Delta V_{\text{OCM}}$ | Change in V <sub>OCM</sub> between high and low                               | $R_L = 100 \Omega$                                                                         |         |         | 50      | mV   |

| R <sub>L</sub>          | Receiver differential input discrete resistor (external to Stratix devices)   |                                                                                            | 90      | 100     | 110     | Ω    |

Table 4–52 shows the external I/O timing parameters when using fast regional clock networks.

|                    | Table 4–52. Stratix Fast Regional Clock External I/O Timing Parameters Notes (1), (2)                                |  |  |  |  |  |  |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| Symbol             | Parameter                                                                                                            |  |  |  |  |  |  |  |  |  |  |

| t <sub>INSU</sub>  | Setup time for input or bidirectional pin using IOE input register with fast regional clock fed by FCLK pin          |  |  |  |  |  |  |  |  |  |  |

| t <sub>INH</sub>   | Hold time for input or bidirectional pin using IOE input register with fast regional clock fed by FCLK pin           |  |  |  |  |  |  |  |  |  |  |

| t <sub>outco</sub> | Clock-to-output delay output or bidirectional pin using IOE output register with fast regional clock fed by FCLK pin |  |  |  |  |  |  |  |  |  |  |

| t <sub>XZ</sub>    | Synchronous IOE output enable register to output pin disable delay using fast regional clock fed by FCLK pin         |  |  |  |  |  |  |  |  |  |  |

| t <sub>ZX</sub>    | Synchronous IOE output enable register to output pin enable delay using fast regional clock fed by FCLK pin          |  |  |  |  |  |  |  |  |  |  |

Notes to Table 4-52:

- (1) These timing parameters are sample-tested only.

- (2) These timing parameters are for column and row IOE pins. You should use the Quartus II software to verify the external timing for any pin.

Table 4–53 shows the external I/O timing parameters when using regional clock networks.

| Symbol                | Parameter                                                                                                                               |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>INSU</sub>     | Setup time for input or bidirectional pin using IOE input register with regional clock fed by CLK pin                                   |

| t <sub>INH</sub>      | Hold time for input or bidirectional pin using IOE input register with regional clock fed by CLK pin                                    |

| t <sub>OUTCO</sub>    | Clock-to-output delay output or bidirectional pin using IOE output register with regional clock fed by CLK pin                          |

| t <sub>INSUPLL</sub>  | Setup time for input or bidirectional pin using IOE input register with regional clock fed by Enhanced PLL with default phase setting   |

| t <sub>INHPLL</sub>   | Hold time for input or bidirectional pin using IOE input register with regional clock fed by Enhanced PLL with default phase setting    |

| t <sub>OUTCOPLL</sub> | Clock-to-output delay output or bidirectional pin using IOE output register with regional clock Enhanced PLL with default phase setting |

| Table 4-71. I         | Table 4–71. EP1S25 External I/O Timing on Row Pins Using Regional Clock Networks |       |         |         |         |         |         |       |      |  |  |  |  |  |

|-----------------------|----------------------------------------------------------------------------------|-------|---------|---------|---------|---------|---------|-------|------|--|--|--|--|--|

| Davamatav             | -5 Speed Grade                                                                   |       | -6 Spee | d Grade | -7 Spee | d Grade | -8 Spee | Unit  |      |  |  |  |  |  |

| Parameter             | Min                                                                              | Max   | Min     | Max     | Min     | Max     | Min     | Max   | Unit |  |  |  |  |  |

| t <sub>INSU</sub>     | 1.793                                                                            |       | 1.927   |         | 2.182   |         | 2.542   |       | ns   |  |  |  |  |  |

| t <sub>INH</sub>      | 0.000                                                                            |       | 0.000   |         | 0.000   |         | 0.000   |       | ns   |  |  |  |  |  |

| t <sub>OUTCO</sub>    | 2.759                                                                            | 5.457 | 2.759   | 5.835   | 2.759   | 6.346   | 2.759   | 7.024 | ns   |  |  |  |  |  |

| t <sub>XZ</sub>       | 2.786                                                                            | 5.511 | 2.786   | 5.891   | 2.786   | 6.414   | 2.786   | 7.106 | ns   |  |  |  |  |  |

| t <sub>ZX</sub>       | 2.786                                                                            | 5.511 | 2.786   | 5.891   | 2.786   | 6.414   | 2.786   | 7.106 | ns   |  |  |  |  |  |

| t <sub>INSUPLL</sub>  | 1.169                                                                            |       | 1.221   |         | 1.373   |         | 1.600   |       | ns   |  |  |  |  |  |

| t <sub>INHPLL</sub>   | 0.000                                                                            |       | 0.000   |         | 0.000   |         | 0.000   |       | ns   |  |  |  |  |  |

| t <sub>OUTCOPLL</sub> | 1.375                                                                            | 2.861 | 1.375   | 2.999   | 1.375   | 3.082   | 1.375   | 3.174 | ns   |  |  |  |  |  |

| t <sub>XZPLL</sub>    | 1.402                                                                            | 2.915 | 1.402   | 3.055   | 1.402   | 3.150   | 1.402   | 3.256 | ns   |  |  |  |  |  |

| t <sub>ZXPLL</sub>    | 1.402                                                                            | 2.915 | 1.402   | 3.055   | 1.402   | 3.150   | 1.402   | 3.256 | ns   |  |  |  |  |  |

| Table 4-72. I         | Table 4–72. EP1S25 External I/O Timing on Row Pins Using Global Clock Networks |         |         |         |         |         |         |       |       |  |  |  |  |

|-----------------------|--------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|-------|-------|--|--|--|--|

| Davamatav             | -5 Spee                                                                        | d Grade | -6 Spee | d Grade | -7 Spee | d Grade | -8 Spee | Unit  |       |  |  |  |  |

| Parameter             | Min                                                                            | Max     | Min     | Max     | Min     | Max     | Min     | Max   | Ullit |  |  |  |  |

| t <sub>INSU</sub>     | 1.665                                                                          |         | 1.779   |         | 2.012   |         | 2.372   |       | ns    |  |  |  |  |

| t <sub>INH</sub>      | 0.000                                                                          |         | 0.000   |         | 0.000   |         | 0.000   |       | ns    |  |  |  |  |

| t <sub>OUTCO</sub>    | 2.834                                                                          | 5.585   | 2.834   | 5.983   | 2.834   | 6.516   | 2.834   | 7.194 | ns    |  |  |  |  |

| t <sub>XZ</sub>       | 2.861                                                                          | 5.639   | 2.861   | 6.039   | 2.861   | 6.584   | 2.861   | 7.276 | ns    |  |  |  |  |

| t <sub>ZX</sub>       | 2.861                                                                          | 5.639   | 2.861   | 6.039   | 2.861   | 6.584   | 2.861   | 7.276 | ns    |  |  |  |  |

| t <sub>INSUPLL</sub>  | 1.538                                                                          |         | 1.606   |         | 1.816   |         | 2.121   |       | ns    |  |  |  |  |

| t <sub>INHPLL</sub>   | 0.000                                                                          |         | 0.000   |         | 0.000   |         | 0.000   |       | ns    |  |  |  |  |

| t <sub>OUTCOPLL</sub> | 1.164                                                                          | 2.492   | 1.164   | 2.614   | 1.164   | 2.639   | 1.164   | 2.653 | ns    |  |  |  |  |

| t <sub>XZPLL</sub>    | 1.191                                                                          | 2.546   | 1.191   | 2.670   | 1.191   | 2.707   | 1.191   | 2.735 | ns    |  |  |  |  |

| t <sub>ZXPLL</sub>    | 1.191                                                                          | 2.546   | 1.191   | 2.670   | 1.191   | 2.707   | 1.191   | 2.735 | ns    |  |  |  |  |

Table 4–120. Stratix Maximum Output Clock Rate for PLL[5, 6, 11, 12] Pins in Flip-Chip Packages (Part 2 of 2)

| I/O Standard                        | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------------|-------------------|-------------------|-------------------|-------------------|------|

| SSTL-2 Class II (3)                 | 200               | 200               | 167               | 167               | MHz  |

| SSTL-2 Class II (4)                 | 200               | 200               | 167               | 167               | MHz  |

| SSTL-2 Class II (5)                 | 150               | 134               | 134               | 134               | MHz  |

| SSTL-18 Class I                     | 150               | 133               | 133               | 133               | MHz  |

| SSTL-18 Class II                    | 150               | 133               | 133               | 133               | MHz  |

| 1.5-V HSTL Class I                  | 250               | 225               | 200               | 200               | MHz  |

| 1.5-V HSTL Class II                 | 225               | 200               | 200               | 200               | MHz  |

| 1.8-V HSTL Class I                  | 250               | 225               | 200               | 200               | MHz  |

| 1.8-V HSTL Class II                 | 225               | 200               | 200               | 200               | MHz  |

| 3.3-V PCI                           | 350               | 300               | 250               | 250               | MHz  |

| 3.3-V PCI-X 1.0                     | 350               | 300               | 250               | 250               | MHz  |

| Compact PCI                         | 350               | 300               | 250               | 250               | MHz  |

| AGP 1×                              | 350               | 300               | 250               | 250               | MHz  |

| AGP 2×                              | 350               | 300               | 250               | 250               | MHz  |

| CTT                                 | 200               | 200               | 200               | 200               | MHz  |

| Differential 1.5-V HSTL<br>C1       | 225               | 200               | 200               | 200               | MHz  |

| Differential 1.8-V HSTL<br>Class I  | 250               | 225               | 200               | 200               | MHz  |

| Differential 1.8-V HSTL<br>Class II | 225               | 200               | 200               | 200               | MHz  |

| Differential SSTL-2 (6)             | 200               | 200               | 167               | 167               | MHz  |

| LVPECL (2)                          | 500               | 500               | 500               | 500               | MHz  |

| PCML (2)                            | 350               | 350               | 350               | 350               | MHz  |

| LVDS (2)                            | 500               | 500               | 500               | 500               | MHz  |

| HyperTransport technology (2)       | 350               | 350               | 350               | 350               | MHz  |

Tables 4–125 and 4–126 show the high-speed I/O timing for Stratix devices.

| Symbol                                                                                                                                         | Conditions                         | -5 Speed Grade |     |     | -6 Speed Grade |     |     | -7 Speed Grade |     |     | -8 Speed Grade |     |       | Unit  |

|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|-----|-----|----------------|-----|-----|----------------|-----|-----|----------------|-----|-------|-------|

| Symbol                                                                                                                                         | Conuntions                         | Min            | Тур | Max   | Julii |

| f <sub>HSCLK</sub> (Clock<br>frequency)<br>(LVDS,<br>LVPECL,<br>HyperTransport<br>technology)<br>f <sub>HSCLK</sub> = f <sub>HSDR</sub> /<br>W | W = 4 to 30<br>(Serdes used)       | 10             |     | 210 | 10             |     | 210 | 10             |     | 156 | 10             |     | 115.5 | MHz   |

|                                                                                                                                                | W = 2 (Serdes bypass)              | 50             |     | 231 | 50             |     | 231 | 50             |     | 231 | 50             |     | 231   | MHz   |

|                                                                                                                                                | W = 2 (Serdes used)                | 150            |     | 420 | 150            |     | 420 | 150            |     | 312 | 150            |     | 231   | MHz   |

|                                                                                                                                                | W = 1 (Serdes bypass)              | 100            |     | 462 | 100            |     | 462 | 100            |     | 462 | 100            |     | 462   | MHz   |

|                                                                                                                                                | W = 1 (Serdes used)                | 300            |     | 717 | 300            |     | 717 | 300            |     | 624 | 300            |     | 462   | MHz   |

| f <sub>HSDR</sub> Device                                                                                                                       | J = 10                             | 300            |     | 840 | 300            |     | 840 | 300            |     | 640 | 300            |     | 462   | Mbps  |

| operation<br>(LVDS,                                                                                                                            | J = 8                              | 300            |     | 840 | 300            |     | 840 | 300            |     | 640 | 300            |     | 462   | Mbps  |

| LVPECL,                                                                                                                                        | J = 7                              | 300            |     | 840 | 300            |     | 840 | 300            |     | 640 | 300            |     | 462   | Mbps  |

| HyperTransport                                                                                                                                 | J = 4                              | 300            |     | 840 | 300            |     | 840 | 300            |     | 640 | 300            |     | 462   | Mbps  |

|                                                                                                                                                | J = 2                              | 100            |     | 462 | 100            |     | 462 | 100            |     | 640 | 100            |     | 462   | Mbps  |

|                                                                                                                                                | J = 1 (LVDS<br>and LVPECL<br>only) | 100            |     | 462 | 100            |     | 462 | 100            |     | 640 | 100            |     | 462   | Mbps  |

| Differential HSTL Specifications 4–15<br>DSP        | Parameters 4–39<br>Row Pin                         |

|-----------------------------------------------------|----------------------------------------------------|

| Block Diagram                                       | Fast Regional Clock External I/O Timing            |

| Configuration                                       | Parameters 4–40                                    |

| for 18 x 18-Bit 2–55                                | Global Clock External I/O Timing                   |

| for 9 x 9-Bit 2–56                                  | Parameters 4–41                                    |

| Block Interconnect Interface 2–71                   | Regional Clock External I/O Timing                 |

| Block Interface 2–70                                | Parameters 4–41                                    |

| Block Signal Sources & Destinations 2–73            | EP1S25 Devices                                     |

| Blocks                                              | Column Pin                                         |

| Arranged in Columns 2–53                            | Fast Regional Clock External I/O Timing            |

| in Stratix Devices 2–54                             | Parameters 4–42                                    |

| Input Register Modes 2-60                           | Global Clock External I/O Timing                   |

| Input Registers 2–58                                | Parameters 4–43                                    |

| Multiplier                                          | Regional Clock External I/O Timing                 |

| 2–60                                                | Parameters 4–42                                    |

| Block 2–57                                          | Row Pin                                            |

| Signed Representation 2-60                          | Fast Regional Clock External I/O Timing            |

| Sub-Block 2–57                                      | Parameters 4–43                                    |

| Sub-Blocks Using Input Shift Register               | Global Clock External I/O Timing                   |

| Connections 2–59                                    | Parameters 4–44                                    |

| Pipeline/Post Multiply Register 2–61                | Regional Clock External I/O Timing                 |

|                                                     | Parameters 4–44                                    |

| E                                                   | EP1S30 Devices                                     |

| <b>L</b>                                            | Column Pin                                         |

| EP1S10 Devices                                      | Fast Regional Clock External I/O Timing            |

| Column Pin                                          | Parameters 4–45                                    |

| Fast Regional Clock External I/O Timing             | Global Clock External I/O Timing                   |

| Parameters 4–36                                     | Parameters 4–45                                    |

| Global Clock External I/O Timing<br>Parameters 4–37 | Regional Clock External I/O Timing Parameters 4–45 |

| Regional Clock External I/O Timing                  | Row Pin                                            |

| Parameters 4–36                                     | Fast Regional Clock External I/O Timing            |

| Row Pin                                             | Parameters 4–46                                    |

| Fast Regional Clock External I/O Timing             | Global Clock External I/O Timing                   |

| Parameters 4–37                                     | Parameters 4–47                                    |

| Global Clock External I/O Timing                    | Regional Clock External I/O Timing                 |

| Parameters 4–38                                     | Parameters 4–47                                    |

| Regional Clock External I/O Timing                  | EP1S40 Devices                                     |

| Parameters 4–38                                     | Column Pin                                         |

| EP1S20 Devices                                      | Fast Regional Clock External I/O Timing            |

| Column Pin                                          | Parameters 4–48                                    |

| Fast Regional Clock External I/O Timing             | Global Clock External I/O Timing                   |

| Parameters 4–39                                     | Parameters 4–49                                    |

| Global Clock External I/O Timing                    | Regional Clock External I/O Timing                 |

| Parameters 4–40                                     | Parameters 4–48                                    |

| Regional Clock External I/O Timing                  | Row Pin                                            |

Altera Corporation Index-3