Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 1057                                                     |

| Number of Logic Elements/Cells | 10570                                                    |

| Total RAM Bits                 | 920448                                                   |

| Number of I/O                  | 426                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 780-BBGA                                                 |

| Supplier Device Package        | 780-FBGA (29x29)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s10f780c6n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Contents Contents

| Maximum Input & Output Clock Rates                    | 4–76 |

|-------------------------------------------------------|------|

| High-Speed I/O Specification                          | 4–87 |

| PLL Specifications                                    | 4–94 |

| DLL Specifications                                    |      |

|                                                       |      |

| Chapter 5. Reference & Ordering Information           |      |

| Software                                              |      |

| Chapter 5. Reference & Ordering Information  Software | 5–1  |

## Index

Altera Corporation v

# **Chapter Revision Dates**

The chapters in this book, *Stratix Device Handbook*, *Volume 1*, were revised on the following dates. Where chapters or groups of chapters are available separately, part numbers are listed.

Chapter 1. Introduction

Revised: July 2005 Part number: S51001-3.2

Chapter 2. Stratix Architecture

Revised: July 2005 Part number: S51002-3.2

Chapter 3. Configuration & Testing

Revised: July 2005 Part number: S51003-1.3

Chapter 4. DC & Switching Characteristics

Revised: January 2006 Part number: S51004-3.4

Chapter 5. Reference & Ordering Information

Revised: September 2004 Part number: S51005-2.1

Altera Corporation vii

| Chapter | Date/Version         | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2       | July 2005 v3.2       | <ul> <li>Added "Clear Signals" section.</li> <li>Updated "Power Sequencing &amp; Hot Socketing" section.</li> <li>Format changes.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | September 2004, v3.1 | <ul> <li>Updated fast regional clock networks description on page 2–73.</li> <li>Deleted the word preliminary from the "specification for the maximum time to relock is 100 µs" on page 2–90.</li> <li>Added information about differential SSTL and HSTL outputs in "External Clock Outputs" on page 2–92.</li> <li>Updated notes in Figure 2–55 on page 2–93.</li> <li>Added information about <i>m</i> counter to "Clock Multiplication &amp; Division" on page 2–101.</li> <li>Updated Note 1 in Table 2–58 on page 2–101.</li> <li>Updated description of "Clock Multiplication &amp; Division" on page 2–88.</li> <li>Updated Table 2–22 on page 2–102.</li> <li>Added references to AN 349 and AN 329 to "External RAM Interfacing" on page 2–115.</li> <li>Table 2–25 on page 2–116: updated the table, updated Notes 3 and 4. Notes 4, 5, and 6, are now Notes 5, 6, and 7, respectively.</li> <li>Updated Table 2–26 on page 2–117.</li> <li>Added information about PCI Compliance to page 2–120.</li> <li>Table 2–32 on page 2–126: updated the table and deleted Note 1.</li> <li>Updated reference to device pin-outs now being available on the web on page 2–130.</li> <li>Added Notes 4 and 5 to Table 2–36 on page 2–130.</li> <li>Updated Note 3 in Table 2–37 on page 2–131.</li> <li>Updated Note 5 in Table 2–41 on page 2–135.</li> </ul> |

|         | April 2004, v3.0     | <ul> <li>Added note 3 to rows 11 and 12 in Table 2–18.</li> <li>Deleted "Stratix and Stratix GX Device PLL Availability" table.</li> <li>Added I/O standards row in Table 2–28 that support max and min strength.</li> <li>Row clk [1,3,8,10] was removed from Table 2–30.</li> <li>Added checkmarks in Enhanced column for LVPECL, 3.3-V PCML, LVDS, and HyperTransport technology rows in Table 2–32.</li> <li>Removed the Left and Right I/O Banks row in Table 2–34.</li> <li>Changed RCLK values in Figures 2–50 and 2–51.</li> <li>External RAM Interfacing section replaced.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | November 2003, v2.2  | <ul> <li>Added 672-pin BGA package information in Table 2–37.</li> <li>Removed support for series and parallel on-chip termination.</li> <li>Termination Technology renamed differential on-chip termination.</li> <li>Updated the number of channels per PLL in Tables 2-38 through 2-42.</li> <li>Updated Figures 2–65 and 2–67.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | October 2003, v2.1   | <ul> <li>Updated DDR I information.</li> <li>Updated Table 2–22.</li> <li>Added Tables 2–25, 2–29, 2–30, and 2–72.</li> <li>Updated Figures 2–59, 2–65, and 2–67.</li> <li>Updated the Lock Detect section.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Section I–2 Altera Corporation

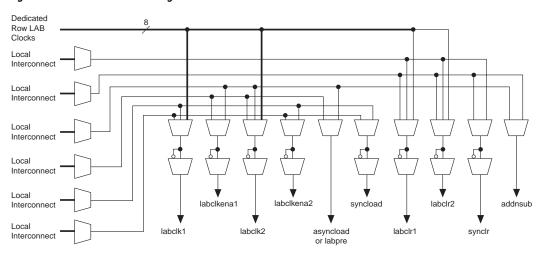

With the LAB-wide addnsub control signal, a single LE can implement a one-bit adder and subtractor. This saves LE resources and improves performance for logic functions such as DSP correlators and signed multipliers that alternate between addition and subtraction depending on data.

The LAB row clocks [7..0] and LAB local interconnect generate the LAB-wide control signals. The MultiTrack $^{\text{IM}}$  interconnect's inherent low skew allows clock and control signal distribution in addition to data. Figure 2–4 shows the LAB control signal generation circuit.

Figure 2-4. LAB-Wide Control Signals

## **Logic Elements**

The smallest unit of logic in the Stratix architecture, the LE, is compact and provides advanced features with efficient logic utilization. Each LE contains a four-input LUT, which is a function generator that can implement any function of four variables. In addition, each LE contains a programmable register and carry chain with carry select capability. A single LE also supports dynamic single bit addition or subtraction mode selectable by an LAB-wide control signal. Each LE drives all types of interconnects: local, row, column, LUT chain, register chain, and direct link interconnects. See Figure 2–5.

Figure 2–8 shows the carry-select circuitry in an LAB for a 10-bit full adder. One portion of the LUT generates the sum of two bits using the input signals and the appropriate carry-in bit; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used for accumulator functions. Another portion of the LUT generates carry-out bits. An LAB-wide carry in bit selects which chain is used for the addition of given inputs. The carry-in signal for each chain, carry-in0 or carry-in1, selects the carry-out to carry forward to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it is fed to local, row, or column interconnects.

The Quartus II Compiler automatically creates carry chain logic during design processing, or you can create it manually during design entry. Parameterized functions such as LPM functions automatically take advantage of carry chains for the appropriate functions.

The Quartus II Compiler creates carry chains longer than 10 LEs by linking LABs together automatically. For enhanced fitting, a long carry chain runs vertically allowing fast horizontal connections to  $TriMatrix^{TM}$  memory and DSP blocks. A carry chain can continue as far as a full column.

LAB Carry-In LAB Carry-In Sum1 A1 B1 LE1 Carry-In0 Carry-In1 Sum2 LE2 LUT B2 data1 Sum data2 Sum3 LUT LE3 A4 B4 Sum4 LUT LE4 LUT A5 B5 Sum5 LE5 Carry-Out0 Carry-Out1 Sum6 A6 B6 LE6 A7 B7 Sum7 LE7 \_<u>A8</u> \_B8 Sum8 LE8 <u>A9</u> B9 Sum9 LE9 Sum10 A10 B10 LE10 LAB Carry-Out

Figure 2-8. Carry Select Chain

## **Clear & Preset Logic Control**

LAB-wide signals control the logic for the register's clear and preset signals. The LE directly supports an asynchronous clear and preset function. The register preset is achieved through the asynchronous load of a logic high. The direct asynchronous preset does not require a NOT-gate push-back technique. Stratix devices support simultaneous preset/

C8 interconnects span eight LABs, M512, or M4K blocks up or down from a source LAB. Every LAB has its own set of C8 interconnects to drive either up or down. C8 interconnect connections between the LABs in a column are similar to the C4 connections shown in Figure 2–11 with the exception that they connect to eight LABs above and below. The C8 interconnects can drive and be driven by all types of architecture blocks similar to C4 interconnects. C8 interconnects can drive each other to extend their range as well as R8 interconnects for column-to-column connections. C8 interconnects are faster than two C4 interconnects.

C16 column interconnects span a length of 16 LABs and provide the fastest resource for long column connections between LABs, TriMatrix memory blocks, DSP blocks, and IOEs. C16 interconnects can cross M-RAM blocks and also drive to row and column interconnects at every fourth LAB. C16 interconnects drive LAB local interconnects via C4 and R4 interconnects and do not drive LAB local interconnects directly.

All embedded blocks communicate with the logic array similar to LAB-to-LAB interfaces. Each block (i.e., TriMatrix memory and DSP blocks) connects to row and column interconnects and has local interconnect regions driven by row and column interconnects. These blocks also have direct link interconnects for fast connections to and from a neighboring LAB. All blocks are fed by the row LAB clocks, labclk [7..0].

| Table 2–11. M-RAM Combined Byte Selection for × 144 Mode Notes (1), (2) |             |  |  |  |  |

|-------------------------------------------------------------------------|-------------|--|--|--|--|

| byteena[150]                                                            | datain ×144 |  |  |  |  |

| [0] = 1                                                                 | [80]        |  |  |  |  |

| [1] = 1                                                                 | [179]       |  |  |  |  |

| [2] = 1                                                                 | [2618]      |  |  |  |  |

| [3] = 1                                                                 | [3527]      |  |  |  |  |

| [4] = 1                                                                 | [4436]      |  |  |  |  |

| [5] = 1                                                                 | [5345]      |  |  |  |  |

| [6] = 1                                                                 | [6254]      |  |  |  |  |

| [7] = 1                                                                 | [7163]      |  |  |  |  |

| [8] = 1                                                                 | [8072]      |  |  |  |  |

| [9] = 1                                                                 | [8981]      |  |  |  |  |

| [10] = 1                                                                | [9890]      |  |  |  |  |

| [11] = 1                                                                | [10799]     |  |  |  |  |

| [12] = 1                                                                | [116108]    |  |  |  |  |

| [13] = 1                                                                | [125117]    |  |  |  |  |

| [14] = 1                                                                | [134126]    |  |  |  |  |

| [15] = 1                                                                | [143135]    |  |  |  |  |

Notes to Tables 2-10 and 2-11:

- (1) Any combination of byte enables is possible.

- (2) Byte enables can be used in the same manner with 8-bit words, i.e., in  $\times$ 16,  $\times$ 32,  $\times$ 64, and  $\times$ 128 modes.

Similar to all RAM blocks, M-RAM blocks can have different clocks on their inputs and outputs. All input registers—renwe, datain, address, and byte enable registers—are clocked together from either of the two clocks feeding the block. The output register can be bypassed. The eight labclk signals or local interconnect can drive the control signals for the A and B ports of the M-RAM block. LEs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals as shown in Figure 2–19.

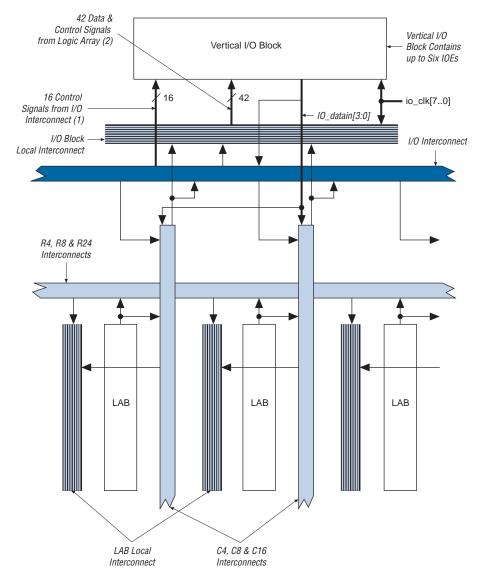

Figure 2-61. Column I/O Block Connection to the Interconnect

#### *Notes to Figure 2–61:*

- (1) The 16 control signals are composed of four output enables io\_boe[3..0], four clock enables io\_boe[3..0], four clocks io\_bclk[3..0], and four clear signals io\_bclr[3..0].

- (2) The 42 data and control signals consist of 12 data out lines; six lines each for DDR applications io\_dataouta[5..0] and io\_dataoutb[5..0], six output enables io\_coe[5..0], six input clock enables io\_cce\_in[5..0], six output clock enables io\_cce\_out[5..0], six clocks io\_cclk[5..0], and six clear signals io cclr[5..0].

Tables 2–25 and 2–26 show the performance specification for DDR SDRAM, RLDRAM II, QDR SRAM, QDRII SRAM, and ZBT SRAM interfaces in EP1S10 through EP1S40 devices and in EP1S60 and EP1S80 devices. The DDR SDRAM and QDR SRAM numbers in Table 2–25 have been verified with hardware characterization with third-party DDR SDRAM and QDR SRAM devices over temperature and voltage extremes.

| Table 2–25. External RAM Support in EP1S10 through EP1S40 Devices |                          |           |                              |               |                |               |                |               |

|-------------------------------------------------------------------|--------------------------|-----------|------------------------------|---------------|----------------|---------------|----------------|---------------|

|                                                                   | Maximum Clock Rate (MHz) |           |                              |               |                |               |                |               |

| DDR Memory Type                                                   | 1/U                      |           | 5 Speed Grade -6 Speed Grade |               | -7 Speed Grade |               | -8 Speed Grade |               |

|                                                                   |                          | Flip-Chip | Flip-Chip                    | Wire-<br>Bond | Flip-<br>Chip  | Wire-<br>Bond | Flip-<br>Chip  | Wire-<br>Bond |

| DDR SDRAM (1), (2)                                                | SSTL-2                   | 200       | 167                          | 133           | 133            | 100           | 100            | 100           |

| DDR SDRAM - side banks (2), (3), (4)                              | SSTL-2                   | 150       | 133                          | 110           | 133            | 100           | 100            | 100           |

| RLDRAM II (4)                                                     | 1.8-V HSTL               | 200       | (5)                          | (5)           | (5)            | (5)           | (5)            | (5)           |

| QDR SRAM (6)                                                      | 1.5-V HSTL               | 167       | 167                          | 133           | 133            | 100           | 100            | 100           |

| QDRII SRAM (6)                                                    | 1.5-V HSTL               | 200       | 167                          | 133           | 133            | 100           | 100            | 100           |

| ZBT SRAM (7)                                                      | LVTTL                    | 200       | 200                          | 200           | 167            | 167           | 133            | 133           |

#### Notes to Table 2-25:

- (1) These maximum clock rates apply if the Stratix device uses DQS phase-shift circuitry to interface with DDR SDRAM. DQS phase-shift circuitry is only available in the top and bottom I/O banks (I/O banks 3, 4, 7, and 8).

- (2) For more information on DDR SDRAM, see AN 342: Interfacing DDR SDRAM with Stratix & Stratix GX Devices.

- (3) DDR SDRAM is supported on the Stratix device side I/O banks (I/O banks 1, 2, 5, and 6) without dedicated DQS phase-shift circuitry. The read DQS signal is ignored in this mode.

- (4) These performance specifications are preliminary.

- (5) This device does not support RLDRAM II.

- (6) For more information on QDR or QDRII SRAM, see AN 349: QDR SRAM Controller Reference Design for Stratix & Stratix GX Devices.

- (7) For more information on ZBT SRAM, see AN 329: ZBT SRAM Controller Reference Design for Stratix & Stratix GX Devices.

For Stratix, the CRC is computed by the Quartus II software and downloaded into the device as a part of the configuration bit stream. The CRC\_ERROR pin reports a soft error when configuration SRAM data is corrupted, triggering device reconfiguration.

### **Custom-Built Circuitry**

Dedicated circuitry is built in the Stratix devices to perform error detection automatically. You can use the built-in dedicated circuitry for error detection using CRC feature in Stratix devices, eliminating the need for external logic. This circuitry will perform error detection automatically when enabled. This error detection circuitry in Stratix devices constantly checks for errors in the configuration SRAM cells while the device is in user mode. You can monitor one external pin for the error and use it to trigger a re-configuration cycle. Select the desired time between checks by adjusting a built-in clock divider.

#### **Software Interface**

In the Quartus II software version 4.1 and later, you can turn on the automated error detection CRC feature in the **Device & Pin Options** dialog box. This dialog box allows you to enable the feature and set the internal frequency of the CRC between 400 kHz to 100 MHz. This controls the rate that the CRC circuitry verifies the internal configuration SRAM bits in the FPGA device.

For more information on CRC, see AN 357: Error Detection Using CRC in Altera FPGA Devices.

# Temperature Sensing Diode

Stratix devices include a diode-connected transistor for use as a temperature sensor in power management. This diode is used with an external digital thermometer device such as a MAX1617A or MAX1619 from MAXIM Integrated Products. These devices steer bias current through the Stratix diode, measuring forward voltage and converting this reading to temperature in the form of an 8-bit signed number (7 bits plus sign). The external device's output represents the junction temperature of the Stratix device and can be used for intelligent power management.

The diode requires two pins (tempdiodep and tempdioden) on the Stratix device to connect to the external temperature-sensing device, as shown in Figure 3–5. The temperature sensing diode is a passive element and therefore can be used before the Stratix device is powered.

| Symbol              | Parameter                   | Conditions                     | Minimum                  | Typical          | Maximum                  | Unit |

|---------------------|-----------------------------|--------------------------------|--------------------------|------------------|--------------------------|------|

| V <sub>CCIO</sub>   | Output supply voltage       |                                | 1.65                     | 1.8              | 1.95                     | V    |

| V <sub>REF</sub>    | Reference voltage           |                                | 0.8                      | 0.9              | 1.0                      | V    |

| V <sub>TT</sub>     | Termination voltage         |                                | V <sub>REF</sub> - 0.04  | V <sub>REF</sub> | V <sub>REF</sub> + 0.04  | V    |

| V <sub>IH(DC)</sub> | High-level DC input voltage |                                | V <sub>REF</sub> + 0.125 |                  |                          | V    |

| V <sub>IL(DC)</sub> | Low-level DC input voltage  |                                |                          |                  | V <sub>REF</sub> - 0.125 | V    |

| V <sub>IH(AC)</sub> | High-level AC input voltage |                                | V <sub>REF</sub> + 0.275 |                  |                          | V    |

| V <sub>IL(AC)</sub> | Low-level AC input voltage  |                                |                          |                  | V <sub>REF</sub> - 0.275 | V    |

| V <sub>OH</sub>     | High-level output voltage   | $I_{OH} = -6.7 \text{ mA}$ (3) | V <sub>TT</sub> + 0.475  |                  |                          | V    |

| V <sub>OL</sub>     | Low-level output voltage    | $I_{OL} = 6.7 \text{ mA } (3)$ |                          |                  | V <sub>TT</sub> – 0.475  | V    |

| Table 4–19. SSTL-18 Class II Specifications |                             |                                 |                          |           |                          |      |  |  |

|---------------------------------------------|-----------------------------|---------------------------------|--------------------------|-----------|--------------------------|------|--|--|

| Symbol                                      | Parameter                   | Conditions                      | Minimum                  | Typical   | Maximum                  | Unit |  |  |

| V <sub>CCIO</sub>                           | Output supply voltage       |                                 | 1.65                     | 1.8       | 1.95                     | V    |  |  |

| $V_{REF}$                                   | Reference voltage           |                                 | 0.8                      | 0.9       | 1.0                      | V    |  |  |

| V <sub>TT</sub>                             | Termination voltage         |                                 | V <sub>REF</sub> - 0.04  | $V_{REF}$ | V <sub>REF</sub> + 0.04  | V    |  |  |

| V <sub>IH(DC)</sub>                         | High-level DC input voltage |                                 | V <sub>REF</sub> + 0.125 |           |                          | ٧    |  |  |

| V <sub>IL(DC)</sub>                         | Low-level DC input voltage  |                                 |                          |           | V <sub>REF</sub> – 0.125 | V    |  |  |

| V <sub>IH(AC)</sub>                         | High-level AC input voltage |                                 | V <sub>REF</sub> + 0.275 |           |                          | V    |  |  |

| V <sub>IL(AC)</sub>                         | Low-level AC input voltage  |                                 |                          |           | V <sub>REF</sub> - 0.275 | V    |  |  |

| V <sub>OH</sub>                             | High-level output voltage   | $I_{OH} = -13.4 \text{ mA}$ (3) | V <sub>TT</sub> + 0.630  |           |                          | V    |  |  |

| V <sub>OL</sub>                             | Low-level output voltage    | I <sub>OL</sub> = 13.4 mA (3)   |                          |           | V <sub>TT</sub> – 0.630  | V    |  |  |

| Table 4–20. SSTL-2 Class I Specifications |                             |                                |                         |           |                         |      |  |  |

|-------------------------------------------|-----------------------------|--------------------------------|-------------------------|-----------|-------------------------|------|--|--|

| Symbol                                    | Parameter                   | Conditions                     | Minimum                 | Typical   | Maximum                 | Unit |  |  |

| V <sub>CCIO</sub>                         | Output supply voltage       |                                | 2.375                   | 2.5       | 2.625                   | ٧    |  |  |

| $V_{TT}$                                  | Termination voltage         |                                | V <sub>REF</sub> - 0.04 | $V_{REF}$ | V <sub>REF</sub> + 0.04 | V    |  |  |

| $V_{REF}$                                 | Reference voltage           |                                | 1.15                    | 1.25      | 1.35                    | ٧    |  |  |

| V <sub>IH(DC)</sub>                       | High-level DC input voltage |                                | V <sub>REF</sub> + 0.18 |           | 3.0                     | V    |  |  |

| V <sub>IL(DC)</sub>                       | Low-level DC input voltage  |                                | -0.3                    |           | V <sub>REF</sub> – 0.18 | ٧    |  |  |

| V <sub>IH(AC)</sub>                       | High-level AC input voltage |                                | V <sub>REF</sub> + 0.35 |           |                         | V    |  |  |

| V <sub>IL(AC)</sub>                       | Low-level AC input voltage  |                                |                         |           | V <sub>REF</sub> - 0.35 | V    |  |  |

| V <sub>OH</sub>                           | High-level output voltage   | $I_{OH} = -8.1 \text{ mA}$ (3) | V <sub>TT</sub> + 0.57  |           |                         | V    |  |  |

| V <sub>OL</sub>                           | Low-level output voltage    | I <sub>OL</sub> = 8.1 mA (3)   |                         |           | V <sub>TT</sub> – 0.57  | ٧    |  |  |

| Table 4–21. SSTL-2 Class II Specifications |                             |                                 |                         |           |                         |      |  |  |

|--------------------------------------------|-----------------------------|---------------------------------|-------------------------|-----------|-------------------------|------|--|--|

| Symbol                                     | Parameter                   | Conditions                      | Minimum                 | Typical   | Maximum                 | Unit |  |  |

| V <sub>CCIO</sub>                          | Output supply voltage       |                                 | 2.375                   | 2.5       | 2.625                   | ٧    |  |  |

| V <sub>TT</sub>                            | Termination voltage         |                                 | V <sub>REF</sub> - 0.04 | $V_{REF}$ | V <sub>REF</sub> + 0.04 | V    |  |  |

| V <sub>REF</sub>                           | Reference voltage           |                                 | 1.15                    | 1.25      | 1.35                    | V    |  |  |

| V <sub>IH(DC)</sub>                        | High-level DC input voltage |                                 | V <sub>REF</sub> + 0.18 |           | V <sub>CCIO</sub> + 0.3 | V    |  |  |

| V <sub>IL(DC)</sub>                        | Low-level DC input voltage  |                                 | -0.3                    |           | V <sub>REF</sub> – 0.18 | V    |  |  |

| V <sub>IH(AC)</sub>                        | High-level AC input voltage |                                 | V <sub>REF</sub> + 0.35 |           |                         | V    |  |  |

| V <sub>IL(AC)</sub>                        | Low-level AC input voltage  |                                 |                         |           | V <sub>REF</sub> – 0.35 | V    |  |  |

| V <sub>OH</sub>                            | High-level output voltage   | $I_{OH} = -16.4 \text{ mA}$ (3) | V <sub>TT</sub> + 0.76  |           |                         | V    |  |  |

| V <sub>OL</sub>                            | Low-level output voltage    | I <sub>OL</sub> = 16.4 mA (3)   |                         |           | V <sub>TT</sub> – 0.76  | V    |  |  |

| Table 4–22. SSTL-3 Class I Specifications (Part 1 of 2) |                             |            |                         |           |                         |      |  |  |

|---------------------------------------------------------|-----------------------------|------------|-------------------------|-----------|-------------------------|------|--|--|

| Symbol                                                  | Parameter                   | Conditions | Minimum                 | Typical   | Maximum                 | Unit |  |  |

| V <sub>CCIO</sub>                                       | Output supply voltage       |            | 3.0                     | 3.3       | 3.6                     | V    |  |  |

| V <sub>TT</sub>                                         | Termination voltage         |            | V <sub>REF</sub> - 0.05 | $V_{REF}$ | V <sub>REF</sub> + 0.05 | V    |  |  |

| V <sub>REF</sub>                                        | Reference voltage           |            | 1.3                     | 1.5       | 1.7                     | V    |  |  |

| V <sub>IH(DC)</sub>                                     | High-level DC input voltage |            | V <sub>REF</sub> + 0.2  |           | V <sub>CCIO</sub> + 0.3 | V    |  |  |

| V <sub>IL(DC)</sub>                                     | Low-level DC input voltage  |            | -0.3                    |           | V <sub>REF</sub> - 0.2  | V    |  |  |

| V <sub>IH(AC)</sub>                                     | High-level AC input voltage |            | V <sub>REF</sub> + 0.4  |           |                         | V    |  |  |

Table 4–102 shows the reporting methodology used by the Quartus II software for minimum timing information for output pins.

**Table 4–102. Reporting Methodology For Minimum Timing For Single-Ended Output Pins (Part 1 of 2)** Notes (1), (2), (3)

|                        |                  |                  | Loadi | ng and T         | ermination               |            |                        | Measurement<br>Point |

|------------------------|------------------|------------------|-------|------------------|--------------------------|------------|------------------------|----------------------|

| I/O Standard           | $R_{UP}$         | $R_{	extsf{DN}}$ | $R_S$ | $\mathbf{R}_{T}$ | V <sub>CCIO</sub><br>(V) | VTT<br>(V) | C <sub>L</sub><br>(pF) | V <sub>MEAS</sub>    |

| 3.3-V LVTTL            | -                | _                | 0     | -                | 3.600                    | 3.600      | 10                     | 1.800                |

| 2.5-V LVTTL            | -                | _                | 0     | _                | 2.630                    | 2.630      | 10                     | 1.200                |

| 1.8-V LVTTL            | -                | _                | 0     | _                | 1.950                    | 1.950      | 10                     | 0.880                |

| 1.5-V LVTTL            | -                | -                | 0     | -                | 1.600                    | 1.600      | 10                     | 0.750                |

| 3.3-V LVCMOS           | -                | -                | 0     | -                | 3.600                    | 3.600      | 10                     | 1.800                |

| 2.5-V LVCMOS           | -                | _                | 0     | _                | 2.630                    | 2.630      | 10                     | 1.200                |

| 1.8-V LVCMOS           | -                | -                | 0     | -                | 1.950                    | 1.950      | 10                     | 0.880                |

| 1.5-V LVCMOS           | -                | -                | 0     | -                | 1.600                    | 1.600      | 10                     | 0.750                |

| 3.3-V GTL              | -                | _                | 0     | 25               | 3.600                    | 1.260      | 30                     | 0.860                |

| 2.5-V GTL              | -                | -                | 0     | 25               | 2.630                    | 1.260      | 30                     | 0.860                |

| 3.3-V GTL+             | -                | -                | 0     | 25               | 3.600                    | 1.650      | 30                     | 1.120                |

| 2.5-V GTL+             | -                | -                | 0     | 25               | 2.630                    | 1.650      | 30                     | 1.120                |

| 3.3-V SSTL-3 Class II  | -                | -                | 25    | 25               | 3.600                    | 1.750      | 30                     | 1.750                |

| 3.3-V SSTL-3 Class I   | -                | _                | 25    | 50               | 3.600                    | 1.750      | 30                     | 1.750                |

| 2.5-V SSTL-2 Class II  | -                | -                | 25    | 25               | 2.630                    | 1.390      | 30                     | 1.390                |

| 2.5-V SSTL-2 Class I   | -                | _                | 25    | 50               | 2.630                    | 1.390      | 30                     | 1.390                |

| 1.8-V SSTL-18 Class II | -                | _                | 25    | 25               | 1.950                    | 1.040      | 30                     | 1.040                |

| 1.8-V SSTL-18 Class I  | -                | _                | 25    | 50               | 1.950                    | 1.040      | 30                     | 1.040                |

| 1.5-V HSTL Class II    | _                | _                | 0     | 25               | 1.600                    | 0.800      | 20                     | 0.900                |

| 1.5-V HSTL Class I     | -                | _                | 0     | 50               | 1.600                    | 0.800      | 20                     | 0.900                |

| 1.8-V HSTL Class II    | -                | -                | 0     | 25               | 1.950                    | 0.900      | 20                     | 1.000                |

| 1.8-V HSTL Class I     | -                | -                | 0     | 50               | 1.950                    | 0.900      | 20                     | 1.000                |

| 3.3-V PCI (4)          | -/25             | 25/–             | 0     | -                | 3.600                    | 1.950      | 10                     | 1.026/2.214          |

| 3.3-V PCI-X 1.0 (4)    | -/25             | 25/–             | 0     | _                | 3.600                    | 1.950      | 10                     | 1.026/2.214          |

| 3.3-V Compact PCI (4)  | -/25             | 25/–             | 0     | _                | 3.600                    | 3.600      | 10                     | 1.026/2.214          |

| 3.3-V AGP 1× (4)       | <del>-</del> /25 | 25/–             | 0     | _                | 3.600                    | 3.600      | 10                     | 1.026/2.214          |

| Table 4–102. Reporting Methodology For Minimum Timi | ing For Single-Ended Output Pins (Part 2 of 2) |

|-----------------------------------------------------|------------------------------------------------|

| Notes (1), (2), (3)                                 |                                                |

| 1/0 0111     |                   | Measurement<br>Point |                |                  |                          |            |                        |                   |

|--------------|-------------------|----------------------|----------------|------------------|--------------------------|------------|------------------------|-------------------|

| I/O Standard | $\mathbf{R}_{UP}$ | $R_{DN}$             | R <sub>S</sub> | $\mathbf{R}_{T}$ | V <sub>CCIO</sub><br>(V) | VTT<br>(V) | C <sub>L</sub><br>(pF) | V <sub>MEAS</sub> |

| 3.3-V CTT    | _                 | =-                   | 25             | 50               | 3.600                    | 1.650      | 30                     | 1.650             |

#### Notes to Table 4–102:

- (1) Input measurement point at internal node is  $0.5 \times V_{CCINT}$ .

- (2) Output measuring point for data is V<sub>MEAS</sub>. When two values are given, the first is the measurement point on the rising edge and the other is for the falling edge.

- (3) Input stimulus edge rate is 0 to V<sub>CCINT</sub> in 0.5 ns (internal signal) from the driver preceding the I/O buffer.

- (4) The first value is for the output rising edge and the second value is for the output falling edge. The hyphen (-) indicates infinite resistance or disconnection.

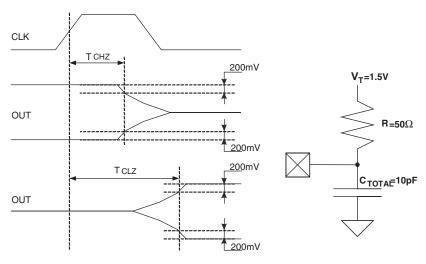

Figure 4–8 shows the measurement setup for output disable and output enable timing. The  $T_{CHZ}$  stands for clock to high Z time delay and is the same as  $T_{XZ}.$  The  $T_{CLZ}$  stands for clock to low Z (driving) time delay and is the same as  $T_{ZX}.$

Figure 4–8. Measurement Setup for  $T_{XZ}$  and  $T_{ZX}$

Tables 4–109 and 4–110 show the adder delays for the column and row IOE programmable delays. These delays are controlled with the Quartus II software logic options listed in the Parameter column.

| Table 4–109. Stratix                   | 1       |     | d Grade |     | d Grade | . , | d Grade | -8 Snee | ed Grade |      |

|----------------------------------------|---------|-----|---------|-----|---------|-----|---------|---------|----------|------|

| Parameter                              | Setting | Min | Max     | Min | Max     | Min | Max     | Min     | Max      | Unit |

| Decrease input delay to internal cells | Off     |     | 3,970   |     | 4,367   |     | 5.022   |         | 5,908    | ps   |

|                                        | Small   |     | 3,390   |     | 3,729   |     | 4,288   |         | 5,045    | ps   |

|                                        | Medium  |     | 2,810   |     | 3,091   |     | 3,554   |         | 4,181    | ps   |

|                                        | Large   |     | 224     |     | 235     |     | 270     |         | 318      | ps   |

|                                        | On      |     | 224     |     | 235     |     | 270     |         | 318      | ps   |

| Decrease input delay                   | Off     |     | 3,900   |     | 4,290   |     | 4,933   |         | 5,804    | ps   |

| to input register                      | On      |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

| Decrease input delay                   | Off     |     | 1,240   |     | 1,364   |     | 1,568   |         | 1,845    | ps   |

| to output register                     | On      |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

| Increase delay to output pin           | Off     |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

|                                        | On      |     | 397     |     | 417     |     | 417     |         | 417      | ps   |

| Increase delay to output enable pin    | Off     |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

|                                        | On      |     | 338     |     | 372     |     | 427     |         | 503      | ps   |

| Increase output clock                  | Off     |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

| enable delay                           | Small   |     | 540     |     | 594     |     | 683     |         | 804      | ps   |

|                                        | Large   |     | 1,016   |     | 1,118   |     | 1,285   |         | 1,512    | ps   |

|                                        | On      |     | 1,016   |     | 1,118   |     | 1,285   |         | 1,512    | ps   |

| Increase input clock                   | Off     |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

| enable delay                           | Small   |     | 540     |     | 594     |     | 683     |         | 804      | ps   |

|                                        | Large   |     | 1,016   |     | 1,118   |     | 1,285   |         | 1,512    | ps   |

|                                        | On      |     | 1,016   |     | 1,118   |     | 1,285   |         | 1,512    | ps   |

| Increase output                        | Off     |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

| enable clock enable<br>delay           | Small   |     | 540     |     | 594     |     | 683     |         | 804      | ps   |

|                                        | Large   |     | 1,016   |     | 1,118   |     | 1,285   |         | 1,512    | ps   |

|                                        | On      |     | 1,016   |     | 1,118   |     | 1,285   |         | 1,512    | ps   |

| Increase t <sub>ZX</sub> delay to      | Off     |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

| output pin                             | On      |     | 2,199   |     | 2,309   |     | 2,309   |         | 2,309    | ps   |

Tables 4–125 and 4–126 show the high-speed I/O timing for Stratix devices.

| Symbol                                                                                      | Conditions                         | -5 Speed Grade |     | -6 Speed Grade |     |     | -7 Speed Grade |     |     | -8 Speed Grade |     |     | Unit  |       |

|---------------------------------------------------------------------------------------------|------------------------------------|----------------|-----|----------------|-----|-----|----------------|-----|-----|----------------|-----|-----|-------|-------|

|                                                                                             |                                    | Min            | Тур | Max            | Min | Тур | Max            | Min | Тур | Max            | Min | Тур | Max   | Julii |

| f <sub>HSCLK</sub> (Clock<br>frequency)                                                     | W = 4 to 30<br>(Serdes used)       | 10             |     | 210            | 10  |     | 210            | 10  |     | 156            | 10  |     | 115.5 | MHz   |

| (LVDS,<br>LVPECL,                                                                           | W = 2 (Serdes bypass)              | 50             |     | 231            | 50  |     | 231            | 50  |     | 231            | 50  |     | 231   | MHz   |

| HyperTransport<br>technology)<br>f <sub>HSCLK</sub> = f <sub>HSDR</sub> /<br>W              | W = 2 (Serdes used)                | 150            |     | 420            | 150 |     | 420            | 150 |     | 312            | 150 |     | 231   | MHz   |

|                                                                                             | W = 1 (Serdes bypass)              | 100            |     | 462            | 100 |     | 462            | 100 |     | 462            | 100 |     | 462   | MHz   |

|                                                                                             | W = 1 (Serdes used)                | 300            |     | 717            | 300 |     | 717            | 300 |     | 624            | 300 |     | 462   | MHz   |

| f <sub>HSDR</sub> Device<br>operation<br>(LVDS,<br>LVPECL,<br>HyperTransport<br>technology) | J = 10                             | 300            |     | 840            | 300 |     | 840            | 300 |     | 640            | 300 |     | 462   | Mbps  |

|                                                                                             | J = 8                              | 300            |     | 840            | 300 |     | 840            | 300 |     | 640            | 300 |     | 462   | Mbps  |

|                                                                                             | J = 7                              | 300            |     | 840            | 300 |     | 840            | 300 |     | 640            | 300 |     | 462   | Mbps  |

|                                                                                             | J = 4                              | 300            |     | 840            | 300 |     | 840            | 300 |     | 640            | 300 |     | 462   | Mbps  |

|                                                                                             | J = 2                              | 100            |     | 462            | 100 |     | 462            | 100 |     | 640            | 100 |     | 462   | Mbps  |

|                                                                                             | J = 1 (LVDS<br>and LVPECL<br>only) | 100            |     | 462            | 100 |     | 462            | 100 |     | 640            | 100 |     | 462   | Mbps  |

| Cumbal            | Conditions                                                         | -5 Speed Grade |     | -6 Speed Grade |      |     | -7 Speed Grade |      |     | -8 Speed Grade |      |     | Heit |      |

|-------------------|--------------------------------------------------------------------|----------------|-----|----------------|------|-----|----------------|------|-----|----------------|------|-----|------|------|

| Symbol            | Conditions                                                         | Min            | Тур | Max            | Min  | Тур | Max            | Min  | Тур | Max            | Min  | Тур | Max  | Unit |

| t <sub>DUTY</sub> | LVDS ( $J = 2$ through 10)                                         | 47.5           | 50  | 52.5           | 47.5 | 50  | 52.5           | 47.5 | 50  | 52.5           | 47.5 | 50  | 52.5 | %    |

|                   | LVDS (J=1)<br>and LVPECL,<br>PCML,<br>HyperTransport<br>technology | 45             | 50  | 55             | 45   | 50  | 55             | 45   | 50  | 55             | 45   | 50  | 55   | %    |

| t <sub>LOCK</sub> | All                                                                |                |     | 100            |      |     | 100            |      |     | 100            |      |     | 100  | μs   |

### Notes to Table 4–125:

- (1) When J = 4, 7, 8, and 10, the SERDES block is used.

- (2) When J = 2 or J = 1, the SERDES is bypassed.

Tables 4–131 through 4–133 describe the Stratix device fast PLL specifications.

| Symbol                             | Parameter                                                                             | Min   | Max   | Unit    |

|------------------------------------|---------------------------------------------------------------------------------------|-------|-------|---------|

| f <sub>IN</sub>                    | CLKIN frequency (1), (2), (3)                                                         | 10    | 717   | MHz     |

| f <sub>INPFD</sub>                 | Input frequency to PFD                                                                | 10    | 500   | MHz     |

| f <sub>OUT</sub>                   | Output frequency for internal global or regional clock (3)                            | 9.375 | 420   | MHz     |

| f <sub>OUT_DIFFIO</sub>            | Output frequency for external clock driven out on a differential I/O data channel (2) | (5)   | (5)   |         |

| f <sub>VCO</sub>                   | VCO operating frequency                                                               | 300   | 1,000 | MHz     |

| t <sub>INDUTY</sub>                | CLKIN duty cycle                                                                      | 40    | 60    | %       |

| t <sub>INJITTER</sub>              | Period jitter for CLKIN pin                                                           |       | ±200  | ps      |

| t <sub>DUTY</sub>                  | Duty cycle for DFFIO 1× CLKOUT pin (6)                                                | 45    | 55    | %       |

| t <sub>JITTER</sub>                | Period jitter for DIFFIO clock out (6)                                                |       | (5)   | ps      |

| t <sub>LOCK</sub>                  | Time required for PLL to acquire lock                                                 | 10    | 100   | μs      |

| m                                  | Multiplication factors for <i>m</i> counter (6)                                       | 1     | 32    | Integer |

| <i>l</i> 0, <i>l</i> 1, <i>g</i> 0 | Multiplication factors for I0, I1, and g0 counter (7), (8)                            | 1     | 32    | Integer |

| t <sub>ARESET</sub>                | Minimum pulse width on areset signal                                                  | 10    |       | ns      |

| Table 4–132.          | Table 4–132. Fast PLL Specifications for -7 Speed Grades (Part 1 of 2)            |       |      |      |  |  |  |  |  |  |

|-----------------------|-----------------------------------------------------------------------------------|-------|------|------|--|--|--|--|--|--|

| Symbol                | Parameter                                                                         | Min   | Max  | Unit |  |  |  |  |  |  |

| f <sub>IN</sub>       | CLKIN frequency (1), (3)                                                          | 10    | 640  | MHz  |  |  |  |  |  |  |

| f <sub>INPFD</sub>    | Input frequency to PFD                                                            | 10    | 500  | MHz  |  |  |  |  |  |  |

| f <sub>OUT</sub>      | Output frequency for internal global or regional clock (4)                        | 9.375 | 420  | MHz  |  |  |  |  |  |  |

| fout_diffio           | Output frequency for external clock driven out on a differential I/O data channel | (5)   | (5)  | MHz  |  |  |  |  |  |  |

| f <sub>VCO</sub>      | VCO operating frequency                                                           | 300   | 700  | MHz  |  |  |  |  |  |  |

| t <sub>INDUTY</sub>   | CLKIN duty cycle                                                                  | 40    | 60   | %    |  |  |  |  |  |  |

| t <sub>INJITTER</sub> | Period jitter for CLKIN pin                                                       |       | ±200 | ps   |  |  |  |  |  |  |

| t <sub>DUTY</sub>     | Duty cycle for DFFIO 1× CLKOUT pin (6)                                            | 45    | 55   | %    |  |  |  |  |  |  |