Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 1846                                                    |

| Number of Logic Elements/Cells | 18460                                                   |

| Total RAM Bits                 | 1669248                                                 |

| Number of I/O                  | 361                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                         |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 484-BBGA, FCBGA                                         |

| Supplier Device Package        | 484-FBGA (23x23)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s20f484c6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Chapter | Date/Version        | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4       |                     | <ul> <li>Updated Table 4–123 on page 4–85 through Table 4–126 on page 4–92.</li> <li>Updated Note 3 in Table 4–123 on page 4–85.</li> <li>Table 4–125 on page 4–88: moved to correct order in chapter, and updated table.</li> <li>Updated Table 4–126 on page 4–92.</li> <li>Updated Table 4–127 on page 4–94.</li> <li>Updated Table 4–128 on page 4–95.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | April 2004, v3.0    | <ul> <li>Table 4–129 on page 4–96: updated table and added Note 10.</li> <li>Updated Table 4–131 and Table 4–132 on page 4–100.</li> <li>Updated Table 4–110 on page 4–74.</li> <li>Updated Table 4–123 on page 4–85.</li> <li>Updated Table 4–124 on page 4–87. through Table 4–126 on page 4–92.</li> <li>Added Note 10 to Table 4–129 on page 4–96.</li> <li>Moved Table 4–127 on page 4–94 to correct order in the chapter.</li> <li>Updated Table 4–131 on page 4–100 through Table 4–132 on page 4–100.</li> <li>Deleted t<sub>XZ</sub> and t<sub>ZX</sub> from Figure 4–4.</li> <li>Waveform was added to Figure 4–6.</li> <li>The minimum and maximum duty cycle values in Note 3 of Table 4–8 were moved to a new Table 4–9.</li> <li>Changes were made to values in SSTL-3 Class I and II rows in Table 4–17.</li> <li>Note 1 was added to Table 4–34.</li> <li>Added t<sub>SU_R</sub> and t<sub>SU_C</sub> rows in Table 4–38.</li> <li>Changed Table 4–55 title from "EP1S10 Column Pin Fast Regional Clock External I/O Timing Parameters" to "EP1S10 External I/O Timing on Column Pins Using Fast Regional Clock Networks."</li> <li>Changed values in Tables 4–46, 4–48 to 4–51, 4–128, and 4–131.</li> <li>Added t<sub>ARESET</sub> row in Tables 4–127 to 4–132.</li> <li>Deleted -5 Speed Grade column in Tables 4–117 to 4–119 and 4–122 to 4–123.</li> <li>Fixed differential waveform in Figure 4–1.</li> <li>Added "Definition of I/O Skew" section.</li> <li>Added d'Definition of I/O Skew" section.</li> <li>Added table 4–46.</li> <li>Values changed in the t<sub>MAKCLKHL</sub> row in Table 4–47.</li> <li>Values changed in the t<sub>MAKCLKHL</sub> row in Table 4–50.</li> <li>Added Table 4–51 to "Internal Timing Parameters" section.</li> <li>The timing information is preliminary in Tables 4–55 through 4–96.</li> <li>Table 4–111 was separated into 3 tables: Tables 4–111 to 4–113.</li> </ul> |

|         | November 2003, v2.2 | Updated Tables 4–127 through 4–129.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Section I–6 Altera Corporation

| Table 1–1. Stratix Device Features — EP1S10, EP1S20, EP1S25, EP1S30 |         |           |           |           |  |  |  |

|---------------------------------------------------------------------|---------|-----------|-----------|-----------|--|--|--|

| Feature                                                             | EP1S10  | EP1S20    | EP1S25    | EP1S30    |  |  |  |

| LEs                                                                 | 10,570  | 18,460    | 25,660    | 32,470    |  |  |  |

| M512 RAM blocks (32 × 18 bits)                                      | 94      | 194       | 224       | 295       |  |  |  |

| M4K RAM blocks (128 × 36 bits)                                      | 60      | 82        | 138       | 171       |  |  |  |

| M-RAM blocks (4K × 144 bits)                                        | 1       | 2         | 2         | 4         |  |  |  |

| Total RAM bits                                                      | 920,448 | 1,669,248 | 1,944,576 | 3,317,184 |  |  |  |

| DSP blocks                                                          | 6       | 10        | 10        | 12        |  |  |  |

| Embedded multipliers (1)                                            | 48      | 80        | 80        | 96        |  |  |  |

| PLLs                                                                | 6       | 6         | 6         | 10        |  |  |  |

| Maximum user I/O pins                                               | 426     | 586       | 706       | 726       |  |  |  |

| Table 1–2. Stratix Device Features — EP1S40, EP1S60, EP1S80 |           |           |           |  |  |  |  |

|-------------------------------------------------------------|-----------|-----------|-----------|--|--|--|--|

| Feature                                                     | EP1S40    | EP1S60    | EP1S80    |  |  |  |  |

| LEs                                                         | 41,250    | 57,120    | 79,040    |  |  |  |  |

| M512 RAM blocks (32 × 18 bits)                              | 384       | 574       | 767       |  |  |  |  |

| M4K RAM blocks (128 × 36 bits)                              | 183       | 292       | 364       |  |  |  |  |

| M-RAM blocks (4K × 144 bits)                                | 4         | 6         | 9         |  |  |  |  |

| Total RAM bits                                              | 3,423,744 | 5,215,104 | 7,427,520 |  |  |  |  |

| DSP blocks                                                  | 14        | 18        | 22        |  |  |  |  |

| Embedded multipliers (1)                                    | 112       | 144       | 176       |  |  |  |  |

| PLLs                                                        | 12        | 12        | 12        |  |  |  |  |

| Maximum user I/O pins                                       | 822       | 1,022     | 1,238     |  |  |  |  |

#### Note to Tables 1–1 and 1–2:

<sup>(1)</sup> This parameter lists the total number of  $9 \times 9$ -bit multipliers for each device. For the total number of  $18 \times 18$ -bit multipliers per device, divide the total number of  $9 \times 9$ -bit multipliers by 2. For the total number of  $36 \times 36$ -bit multipliers per device, divide the total number of  $9 \times 9$ -bit multipliers by 8.

Table 2–2 shows the Stratix device's routing scheme.

| Table 2–2. Strat            | Table 2–2. Stratix Device Routing Scheme |                |                    |                          |                 |                 |                  |                 |                 |                  |          |                |               |             |            |            |          |

|-----------------------------|------------------------------------------|----------------|--------------------|--------------------------|-----------------|-----------------|------------------|-----------------|-----------------|------------------|----------|----------------|---------------|-------------|------------|------------|----------|

|                             |                                          | Destination    |                    |                          |                 |                 |                  |                 |                 |                  |          |                |               |             |            |            |          |

| Source                      | LUT Chain                                | Register Chain | Local Interconnect | Direct Link Interconnect | R4 Interconnect | R8 Interconnect | R24 Interconnect | C4 Interconnect | C8 Interconnect | C16 Interconnect | TE       | M512 RAM Block | M4K RAM Block | M-RAM Block | DSP Blocks | Column 10E | Row IOE  |

| LUT Chain                   |                                          |                |                    |                          |                 |                 |                  |                 |                 |                  | >        |                |               |             |            |            |          |

| Register Chain              |                                          |                |                    |                          |                 |                 |                  |                 |                 |                  | <b>\</b> |                |               |             |            |            |          |

| Local<br>Interconnect       |                                          |                |                    |                          |                 |                 |                  |                 |                 |                  | <b>✓</b> | <b>✓</b>       | <b>✓</b>      | <b>✓</b>    | <b>✓</b>   | <b>✓</b>   | <b>\</b> |

| Direct Link<br>Interconnect |                                          |                | <b>✓</b>           |                          |                 |                 |                  |                 |                 |                  |          |                |               |             |            |            |          |

| R4 Interconnect             |                                          |                | <b>✓</b>           |                          | <b>✓</b>        |                 | <b>✓</b>         | <b>✓</b>        |                 | <b>✓</b>         |          |                |               |             |            |            |          |

| R8 Interconnect             |                                          |                | <b>✓</b>           |                          |                 | <b>✓</b>        |                  |                 | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| R24<br>Interconnect         |                                          |                |                    |                          | <b>✓</b>        |                 | ~                | <b>✓</b>        |                 | <b>✓</b>         |          |                |               |             |            |            |          |

| C4 Interconnect             |                                          |                | <b>✓</b>           |                          | <b>✓</b>        |                 |                  | <b>✓</b>        |                 |                  |          |                |               |             |            |            |          |

| C8 Interconnect             |                                          |                | <b>✓</b>           |                          |                 | <b>✓</b>        |                  |                 | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| C16<br>Interconnect         |                                          |                |                    |                          | <b>✓</b>        |                 | <b>\</b>         | <b>\</b>        |                 | <b>✓</b>         |          |                |               |             |            |            |          |

| LE                          | <b>✓</b>                                 | <b>✓</b>       | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        | <b>✓</b>        |                  | <b>✓</b>        | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| M512 RAM<br>Block           |                                          |                | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        | <b>✓</b>        |                  | <b>\</b>        | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| M4K RAM Block               |                                          |                | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        | <b>✓</b>        |                  | <b>✓</b>        | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| M-RAM Block                 |                                          |                |                    |                          |                 |                 |                  | <b>✓</b>        | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| DSP Blocks                  |                                          |                | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        | <b>✓</b>        |                  | <b>✓</b>        | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| Column IOE                  |                                          |                |                    | <b>✓</b>                 |                 |                 |                  | <b>✓</b>        | <b>✓</b>        | <b>✓</b>         |          |                |               |             |            |            |          |

| Row IOE                     |                                          |                |                    | <b>✓</b>                 |                 | <b>✓</b>        | <b>✓</b>         | <b>✓</b>        | <b>✓</b>        | <b>✓</b>         |          |                |               |             |            |            |          |

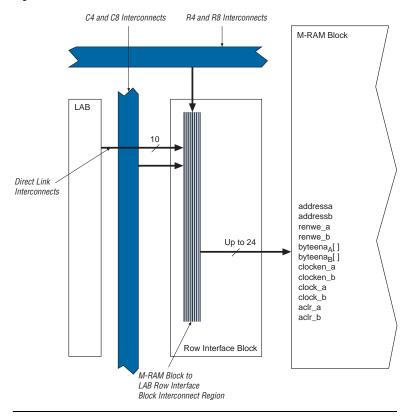

Figure 2–22. M-RAM Row Unit Interface to Interconnect

#### **Single-Port Mode**

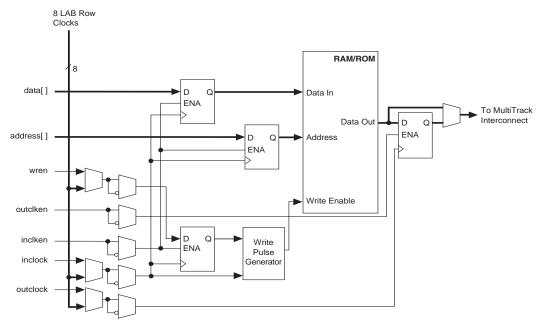

The memory blocks also support single-port mode, used when simultaneous reads and writes are not required. See Figure 2–28. A single block in a memory block can support up to two single-port mode RAM blocks in the M4K RAM blocks if each RAM block is less than or equal to 2K bits in size.

Figure 2–28. Single-Port Mode Note (1)

Note to Figure 2-28:

(1) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

Table 2–14 shows the summary of input register modes for the DSP block.

| Table 2–14. Input Register Modes |          |          |         |  |  |  |

|----------------------------------|----------|----------|---------|--|--|--|

| Register Input Mode              | 9 × 9    | 18 × 18  | 36 × 36 |  |  |  |

| Parallel input                   | <b>✓</b> | <b>✓</b> | ✓       |  |  |  |

| Shift register input             | ✓        | ✓        |         |  |  |  |

#### Multiplier

The multiplier supports  $9 \times 9$ -,  $18 \times 18$ -, or  $36 \times 36$ -bit multiplication. Each DSP block supports eight possible  $9 \times 9$ -bit or smaller multipliers. There are four multiplier blocks available for multipliers larger than  $9 \times 9$  bits but smaller than  $18 \times 18$  bits. There is one multiplier block available for multipliers larger than  $18 \times 18$  bits but smaller than or equal to  $36 \times 36$  bits. The ability to have several small multipliers is useful in applications such as video processing. Large multipliers greater than  $18 \times 18$  bits are useful for applications such as the mantissa multiplication of a single-precision floating-point number.

The multiplier operands can be signed or unsigned numbers, where the result is signed if either input is signed as shown in Table 2–15. The sign\_a and sign\_b signals provide dynamic control of each operand's representation: a logic 1 indicates the operand is a signed number, a logic 0 indicates the operand is an unsigned number. These sign signals affect all multipliers and adders within a single DSP block and you can register them to match the data path pipeline. The multipliers are full precision (that is, 18 bits for the 18-bit multiply, 36-bits for the 36-bit multiply, and so on) regardless of whether sign\_a or sign\_b set the operands as signed or unsigned numbers.

| Table 2–15. Multiplier Signed Representation |          |          |  |  |  |  |

|----------------------------------------------|----------|----------|--|--|--|--|

| Data A                                       | Data B   | Result   |  |  |  |  |

| Unsigned                                     | Unsigned | Unsigned |  |  |  |  |

| Unsigned                                     | Signed   | Signed   |  |  |  |  |

| Signed                                       | Unsigned | Signed   |  |  |  |  |

| Signed                                       | Signed   | Signed   |  |  |  |  |

single DSP block can implement two sums or differences from two  $18 \times 18$ -bit multipliers each or four sums or differences from two  $9 \times 9$ -bit multipliers each.

You can use the two-multipliers adder mode for complex multiplications, which are written as:

$$(a+jb)\times(c+jd)=[(a\times c)-(b\times d)]+j\times[(a\times d)+(b\times c)]$$

The two-multipliers adder mode allows a single DSP block to calculate the real part  $[(a \times c) - (b \times d)]$  using one subtractor and the imaginary part  $[(a \times d) + (b \times c)]$  using one adder, for data widths up to 18 bits. Two complex multiplications are possible for data widths up to 9 bits using four adder/subtractor/accumulator blocks. Figure 2–38 shows an 18-bit two-multipliers adder.

Figure 2–38. Two-Multipliers Adder Mode Implementing Complex Multiply

#### Four-Multipliers Adder Mode

In the four-multipliers adder mode, the DSP block adds the results of two first -stage adder/subtractor blocks. One sum of four  $18 \times 18$ -bit multipliers or two different sums of two sets of four  $9 \times 9$ -bit multipliers can be implemented in a single DSP block. The product width for each multiplier must be the same size. The four-multipliers adder mode is useful for FIR filter applications. Figure 2–39 shows the four multipliers adder mode.

clock signals are routed from LAB row clocks and are generated from specific LAB rows at the DSP block interface. The LAB row source for control signals, data inputs, and outputs is shown in Table 2–17.

| Table 2-17. D           | Table 2–17. DSP Block Signal Sources & Destinations |             |              |  |  |  |  |

|-------------------------|-----------------------------------------------------|-------------|--------------|--|--|--|--|

| LAB Row at<br>Interface | Control Signals<br>Generated                        | Data Inputs | Data Outputs |  |  |  |  |

| 1                       | signa                                               | A1[170]     | OA[170]      |  |  |  |  |

| 2                       | aclr0<br>accum_sload0                               | B1[170]     | OB[170]      |  |  |  |  |

| 3                       | addnsub1<br>clock0<br>ena0                          | A2[170]     | OC[170]      |  |  |  |  |

| 4                       | aclr1<br>clock1<br>ena1                             | B2[170]     | OD[170]      |  |  |  |  |

| 5                       | aclr2<br>clock2<br>ena2                             | A3[170]     | OE[170]      |  |  |  |  |

| 6                       | sign_b<br>clock3<br>ena3                            | B3[170]     | OF[170]      |  |  |  |  |

| 7                       | clear3<br>accum_sload1                              | A4[170]     | OG[170]      |  |  |  |  |

| 8                       | addnsub3                                            | B4[170]     | OH[170]      |  |  |  |  |

## PLLs & Clock Networks

Stratix devices provide a hierarchical clock structure and multiple PLLs with advanced features. The large number of clocking resources in combination with the clock synthesis precision provided by enhanced and fast PLLs provides a complete clock management solution.

### **Global & Hierarchical Clocking**

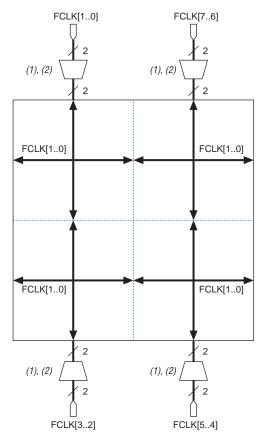

Stratix devices provide 16 dedicated global clock networks, 16 regional clock networks (four per device quadrant), and 8 dedicated fast regional clock networks (for EP1S10, EP1S20, and EP1S25 devices), and 16 dedicated fast regional clock networks (for EP1S30 EP1S40, and EP1S60, and EP1S80 devices). These clocks are organized into a hierarchical clock structure that allows for up to 22 clocks per device region with low skew and delay. This hierarchical clocking scheme provides up to 48 unique clock domains within Stratix devices.

Figure 2–44. EP1S25, EP1S20 & EP1S10 Device Fast Clock Pin Connections to Fast Regional Clocks

#### Notes to Figure 2-44:

- (1) This is a set of two multiplexers.

- (2) In addition to the FCLK pin inputs, there is also an input from the I/O interconnect.

Each IOE contains its own control signal selection for the following control signals: oe, ce\_in, ce\_out, aclr/preset, sclr/preset, clk\_in, and clk\_out. Figure 2–63 illustrates the control signal selection.

io bclk[3..0] io\_bce[3..0] io\_bclr[3..0] io\_boe[3..0] Dedicated I/O Clock [7..0] I/O Interconnect [15..0] io\_coe Local Interconnect io\_cclr Local Interconnect io\_cce\_out Local Interconnect io cce in Local Interconnect io\_cclk clk\_out ce\_out sclr/preset Local Interconnect

ce\_in

clk in

Figure 2-63. Control Signal Selection per IOE

In normal bidirectional operation, the input register can be used for input data requiring fast setup times. The input register can have its own clock input and clock enable separate from the OE and output registers. The output register can be used for data requiring fast clock-to-output performance. The OE register can be used for fast clock-to-output enable timing. The OE and output register share the same clock source and the same clock enable source from local interconnect in the associated LAB, dedicated I/O clocks, and the column and row interconnects. Figure 2–64 shows the IOE in bidirectional configuration.

aclr/preset

oe

Stratix, Stratix II, Cyclone<sup>®</sup>, and Cyclone II devices must be within the first 17 devices in a JTAG chain. All of these devices have the same JTAG controller. If any of the Stratix, Stratix II, Cyclone, and Cyclone II devices are in the 18th or after they will fail configuration. This does not affect SignalTap II.

For more information on JTAG, see the following documents:

- AN 39: IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices

- Jam Programming & Test Language Specification

## SignalTap II Embedded Logic Analyzer

Stratix devices feature the SignalTap II embedded logic analyzer, which monitors design operation over a period of time through the IEEE Std. 1149.1 (JTAG) circuitry. You can analyze internal logic at speed without bringing internal signals to the I/O pins. This feature is particularly important for advanced packages, such as FineLine BGA® packages, because it can be difficult to add a connection to a pin during the debugging process after a board is designed and manufactured.

## Configuration

The logic, circuitry, and interconnects in the Stratix architecture are configured with CMOS SRAM elements. Altera® devices are reconfigurable. Because every device is tested with a high-coverage production test program, you do not have to perform fault testing and can focus on simulation and design verification.

Stratix devices are configured at system power-up with data stored in an Altera serial configuration device or provided by a system controller. Altera offers in-system programmability (ISP)-capable configuration devices that configure Stratix devices via a serial data stream. Stratix devices can be configured in under 100 ms using 8-bit parallel data at 100 MHz. The Stratix device's optimized interface allows microprocessors to configure it serially or in parallel, and synchronously or asynchronously. The interface also enables microprocessors to treat Stratix devices as memory and configure them by writing to a virtual memory location, making reconfiguration easy. After a Stratix device has been configured, it can be reconfigured in-circuit by resetting the device and loading new data. Real-time changes can be made during system operation, enabling innovative reconfigurable computing applications.

### **Operating Modes**

The Stratix architecture uses SRAM configuration elements that require configuration data to be loaded each time the circuit powers up. The process of physically loading the SRAM data into the device is called configuration. During initialization, which occurs immediately after

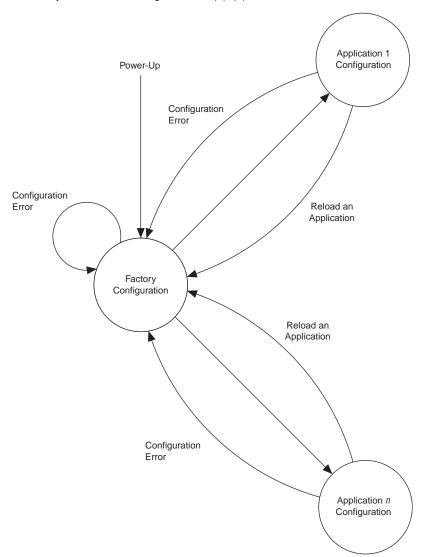

Figure 3–3. Remote Update Transition Diagram Notes (1), (2)

#### *Notes to Figure 3–3:*

- (1) Remote update of Application Configuration is controlled by a Nios embedded processor or user logic programmed in the Factory or Application configurations.

- (2) Up to seven pages can be specified allowing up to seven different configuration applications.

| Table 4–3. Stratix Device DC Operating Conditions Note (7) (Part 2 of 2) |                               |                                 |         |         |         |      |  |  |

|--------------------------------------------------------------------------|-------------------------------|---------------------------------|---------|---------|---------|------|--|--|

| Symbol                                                                   | Parameter                     | Conditions                      | Minimum | Typical | Maximum | Unit |  |  |

| R <sub>CONF</sub>                                                        | Value of I/O pin pull-        | $V_{CCIO} = 3.0 V (9)$          | 20      |         | 50      | kΩ   |  |  |

|                                                                          | up resistor before and during | V <sub>CCIO</sub> = 2.375 V (9) | 30      |         | 80      | kΩ   |  |  |

| configuration                                                            |                               | V <sub>CCIO</sub> = 1.71 V (9)  | 60      |         | 150     | kΩ   |  |  |

| Table 4–4.        | Table 4–4. LVTTL Specifications |                                                |         |         |      |  |  |  |  |

|-------------------|---------------------------------|------------------------------------------------|---------|---------|------|--|--|--|--|

| Symbol            | Parameter                       | Conditions                                     | Minimum | Maximum | Unit |  |  |  |  |

| V <sub>CCIO</sub> | Output supply voltage           |                                                | 3.0     | 3.6     | V    |  |  |  |  |

| V <sub>IH</sub>   | High-level input voltage        |                                                | 1.7     | 4.1     | V    |  |  |  |  |

| V <sub>IL</sub>   | Low-level input voltage         |                                                | -0.5    | 0.7     | V    |  |  |  |  |

| V <sub>OH</sub>   | High-level output voltage       | $I_{OH} = -4 \text{ to } -24 \text{ mA } (10)$ | 2.4     |         | V    |  |  |  |  |

| V <sub>OL</sub>   | Low-level output voltage        | I <sub>OL</sub> = 4 to 24 mA (10)              |         | 0.45    | V    |  |  |  |  |

| Table 4–5.        | Table 4–5. LVCMOS Specifications |                                              |                         |         |      |  |  |  |  |

|-------------------|----------------------------------|----------------------------------------------|-------------------------|---------|------|--|--|--|--|

| Symbol            | Parameter                        | Conditions                                   | Minimum                 | Maximum | Unit |  |  |  |  |

| V <sub>CCIO</sub> | Output supply voltage            |                                              | 3.0                     | 3.6     | V    |  |  |  |  |

| V <sub>IH</sub>   | High-level input voltage         |                                              | 1.7                     | 4.1     | V    |  |  |  |  |

| V <sub>IL</sub>   | Low-level input voltage          |                                              | -0.5                    | 0.7     | V    |  |  |  |  |

| V <sub>OH</sub>   | High-level output voltage        | $V_{CCIO} = 3.0,$ $I_{OH} = -0.1 \text{ mA}$ | V <sub>CCIO</sub> - 0.2 |         | V    |  |  |  |  |

| V <sub>OL</sub>   | Low-level output voltage         | $V_{CCIO} = 3.0,$ $I_{OL} = 0.1 \text{ mA}$  |                         | 0.2     | V    |  |  |  |  |

| Table 4–6.        | Table 4–6. 2.5-V I/O Specifications |                              |         |         |      |  |  |  |  |

|-------------------|-------------------------------------|------------------------------|---------|---------|------|--|--|--|--|

| Symbol            | Parameter                           | Conditions                   | Minimum | Maximum | Unit |  |  |  |  |

| V <sub>CCIO</sub> | Output supply voltage               |                              | 2.375   | 2.625   | V    |  |  |  |  |

| V <sub>IH</sub>   | High-level input voltage            |                              | 1.7     | 4.1     | V    |  |  |  |  |

| V <sub>IL</sub>   | Low-level input voltage             |                              | -0.5    | 0.7     | V    |  |  |  |  |

| V <sub>OH</sub>   | High-level output voltage           | I <sub>OH</sub> = -1 mA (10) | 2.0     |         | V    |  |  |  |  |

| V <sub>OL</sub>   | Low-level output voltage            | I <sub>OL</sub> = 1 mA (10)  |         | 0.4     | V    |  |  |  |  |

Figure 4–2. Transmitter Output Waveforms for Differential I/O Standards

# Single-Ended Waveform Positive Channel (p) = $V_{OH}$ $V_{CM}$ Negative Channel (n) = $V_{OL}$ Ground

## Differential Waveform $V_{OD} = 0 \text{ V}$ $V_{OD} = 0 \text{ V}$

Tables 4–10 through 4–33 recommend operating conditions, DC operating conditions, and capacitance for 1.5-V Stratix devices.

| Table 4–10. 3.3-V LVDS I/O Specifications (Part 1 of 2) |                                                 |                                                                                 |         |         |         |      |  |  |

|---------------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------|---------|---------|---------|------|--|--|

| Symbol                                                  | Parameter                                       | Conditions                                                                      | Minimum | Typical | Maximum | Unit |  |  |

| V <sub>CCIO</sub>                                       | I/O supply voltage                              |                                                                                 | 3.135   | 3.3     | 3.465   | V    |  |  |

| V <sub>ID</sub> (6)                                     | Input differential voltage swing (single-ended) | $0.1 \text{ V} \leq \text{V}_{\text{CM}} < 1.1 \text{ V}$<br>W = 1  through  10 | 300     |         | 1,000   | mV   |  |  |

|                                                         |                                                 | 1.1 V $\leq$ V <sub>CM</sub> $\leq$ 1.6 V $W = 1$                               | 200     |         | 1,000   | mV   |  |  |

|                                                         |                                                 | 1.1 V $\leq$ V <sub>CM</sub> $\leq$ 1.6 V<br>W = 2 through 10                   | 100     |         | 1,000   | mV   |  |  |

|                                                         |                                                 | 1.6 V < $V_{CM} \le 1.8 \text{ V}$<br>W = 1  through  10                        | 300     |         | 1,000   | mV   |  |  |

| Table 4–59. EP1S10 External I/O Timing on Row Pins Using Regional Clock Networks Note (1) |                |       |                |       |                |       |                |     |      |

|-------------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-----|------|

| Parameter                                                                                 | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |     |      |

|                                                                                           | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max | Unit |

| t <sub>INSU</sub>                                                                         | 2.161          |       | 2.336          |       | 2.685          |       | NA             |     | ns   |

| t <sub>INH</sub>                                                                          | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns   |

| t <sub>OUTCO</sub>                                                                        | 2.434          | 4.889 | 2.434          | 5.226 | 2.434          | 5.643 | NA             | NA  | ns   |

| t <sub>XZ</sub>                                                                           | 2.461          | 4.493 | 2.461          | 5.282 | 2.461          | 5.711 | NA             | NA  | ns   |

| t <sub>ZX</sub>                                                                           | 2.461          | 4.493 | 2.461          | 5.282 | 2.461          | 5.711 | NA             | NA  | ns   |

| t <sub>INSUPLL</sub>                                                                      | 1.057          |       | 1.172          |       | 1.315          |       | NA             |     | ns   |

| t <sub>INHPLL</sub>                                                                       | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns   |

| t <sub>OUTCOPLL</sub>                                                                     | 1.327          | 2.773 | 1.327          | 2.848 | 1.327          | 2.940 | NA             | NA  | ns   |

| t <sub>XZPLL</sub>                                                                        | 1.354          | 2.827 | 1.354          | 2.904 | 1.354          | 3.008 | NA             | NA  | ns   |

| t <sub>ZXPLL</sub>                                                                        | 1.354          | 2.827 | 1.354          | 2.904 | 1.354          | 3.008 | NA             | NA  | ns   |

| Table 4–60. EP1S10 External I/O Timing on Row Pins Using Global Clock Networks Note (1) |                |       |         |                |       |                |     |                |      |  |

|-----------------------------------------------------------------------------------------|----------------|-------|---------|----------------|-------|----------------|-----|----------------|------|--|

| Doromotor                                                                               | -5 Speed Grade |       | -6 Spee | -6 Speed Grade |       | -7 Speed Grade |     | -8 Speed Grade |      |  |

| Parameter                                                                               | Min            | Max   | Min     | Max            | Min   | Max            | Min | Max            | Unit |  |

| t <sub>INSU</sub>                                                                       | 1.787          |       | 1.944   |                | 2.232 |                | NA  |                | ns   |  |

| t <sub>INH</sub>                                                                        | 0.000          |       | 0.000   |                | 0.000 |                | NA  |                | ns   |  |

| t <sub>OUTCO</sub>                                                                      | 2.647          | 5.263 | 2.647   | 5.618          | 2.647 | 6.069          | NA  | NA             | ns   |  |

| t <sub>XZ</sub>                                                                         | 2.674          | 5.317 | 2.674   | 5.674          | 2.674 | 6.164          | NA  | NA             | ns   |  |

| t <sub>ZX</sub>                                                                         | 2.674          | 5.317 | 2.674   | 5.674          | 2.674 | 6.164          | NA  | NA             | ns   |  |

| t <sub>INSUPLL</sub>                                                                    | 1.371          |       | 1.1472  |                | 1.654 |                | NA  |                | ns   |  |

| t <sub>INHPLL</sub>                                                                     | 0.000          |       | 0.000   |                | 0.000 |                | NA  |                | ns   |  |

| t <sub>OUTCOPLL</sub>                                                                   | 1.144          | 2.459 | 1.144   | 2.548          | 1.144 | 2.601          | NA  | NA             | ns   |  |

| t <sub>XZPLL</sub>                                                                      | 1.171          | 2.513 | 1.171   | 2.604          | 1.171 | 2.669          | NA  | NA             | ns   |  |

| t <sup>ZXPLL</sup>                                                                      | 1.171          | 2.513 | 1.171   | 2.604          | 1.171 | 2.669          | NA  | NA             | ns   |  |

*Note to Tables 4–55 to 4–60:*

<sup>(1)</sup> Only EP1S25, EP1S30, and EP1S40 have speed grade of -8.

| Table 4–102. Reporting Methodology For Minimum Timi | ng For Single-Ended Output Pins (Part 2 of 2) |

|-----------------------------------------------------|-----------------------------------------------|

| Notes (1), (2), (3)                                 |                                               |

| 1/0 0111     | Loading and Termination |          |                |                  |                          |            | Measurement<br>Point   |                   |

|--------------|-------------------------|----------|----------------|------------------|--------------------------|------------|------------------------|-------------------|

| I/O Standard | $\mathbf{R}_{UP}$       | $R_{DN}$ | R <sub>S</sub> | $\mathbf{R}_{T}$ | V <sub>CCIO</sub><br>(V) | VTT<br>(V) | C <sub>L</sub><br>(pF) | V <sub>MEAS</sub> |

| 3.3-V CTT    | _                       | =-       | 25             | 50               | 3.600                    | 1.650      | 30                     | 1.650             |

#### Notes to Table 4–102:

- (1) Input measurement point at internal node is  $0.5 \times V_{CCINT}$ .

- (2) Output measuring point for data is V<sub>MEAS</sub>. When two values are given, the first is the measurement point on the rising edge and the other is for the falling edge.

- (3) Input stimulus edge rate is 0 to V<sub>CCINT</sub> in 0.5 ns (internal signal) from the driver preceding the I/O buffer.

- (4) The first value is for the output rising edge and the second value is for the output falling edge. The hyphen (-) indicates infinite resistance or disconnection.

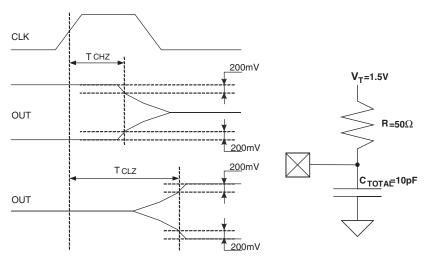

Figure 4–8 shows the measurement setup for output disable and output enable timing. The  $T_{CHZ}$  stands for clock to high Z time delay and is the same as  $T_{XZ}.$  The  $T_{CLZ}$  stands for clock to low Z (driving) time delay and is the same as  $T_{ZX}.$

Figure 4–8. Measurement Setup for  $T_{XZ}$  and  $T_{ZX}$

**Table 4–110. Stratix IOE Programmable Delays on Row Pins** Note (1) -5 Speed Grade -6 Speed Grade -7 Speed Grade -8 Speed Grade **Parameter** Settina Unit Min Max Min Max Min Max Min Max Decrease input delay Off 3,970 4,367 5,022 5,908 ps to internal cells Small 3,390 3.729 4,288 5,045 ps 2.810 3.091 3.554 Medium 4.181 ps Large 173 181 208 245 ps On 173 181 208 245 ps Decrease input delay Off 3.900 4.290 4.933 5,804 ps to input register On 0 0 0 0 ps Decrease input delay Off 1.240 1.364 1.568 1.845 ps to output register On 0 0 0 0 ps Increase delay to Off 0 0 0 0 ps output pin On 397 417 417 417 ps Increase delay to Off 0 0 0 0 ps output enable pin 383 441 On 348 518 ps 0 Increase output clock Off 0 0 0 ps enable delay 180 227 Small 198 267 ps Large 260 286 328 386 ps On 260 286 328 386 ps Increase input clock Off 0 0 0 0 ps enable delay Small 180 198 227 267 ps Large 260 286 328 386 ps On 260 286 328 386 ps Off Increase output 0 0 0 0 ps enable clock enable Small 540 594 683 804 ps delav 1.285 Large 1.016 1.118 1,512 ps On 1,016 1,118 1,285 1,512 ps Increase tzx delay to Off 0 0 0 0 ps output pin On 1.993 2.092 2.092 2.092 ps

Note to Table 4-109 and Table 4-110:

<sup>(1)</sup> The delay chain delays vary for different device densities. These timing values only apply to EP1S30 and EP1S40 devices. Reference the timing information reported by the Quartus II software for other devices.

Table 4–119. Stratix Maximum Input Clock Rate for CLK[1, 3, 8, 10] Pins in Wire-Bond Packages (Part 2 of 2)

| I/O Standard                  | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------|-------------------|-------------------|-------------------|------|

| SSTL-18 Class I               | 350               | 300               | 300               | MHz  |

| SSTL-18 Class II              | 350               | 300               | 300               | MHz  |

| 1.5-V HSTL Class I            | 350               | 300               | 300               | MHz  |

| 1.8-V HSTL Class I            | 350               | 300               | 300               | MHz  |

| CTT                           | 250               | 200               | 200               | MHz  |

| Differential 1.5-V HSTL<br>C1 | 350               | 300               | 300               | MHz  |

| LVPECL (1)                    | 645               | 622               | 622               | MHz  |

| PCML (1)                      | 275               | 275               | 275               | MHz  |

| LVDS (1)                      | 645               | 622               | 622               | MHz  |

| HyperTransport technology (1) | 500               | 450               | 450               | MHz  |

Note to Tables 4–114 through 4–119:

Tables 4–120 through 4–123 show the maximum output clock rate for column and row pins in Stratix devices.

Table 4–120. Stratix Maximum Output Clock Rate for PLL[5, 6, 11, 12] Pins in Flip-Chip Packages (Part 1 of 2)

| I/O Standard       | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |  |  |  |

|--------------------|-------------------|-------------------|-------------------|-------------------|------|--|--|--|

| LVTTL              | 350               | 300               | 250               | 250               | MHz  |  |  |  |

| 2.5 V              | 350               | 300               | 300               | 300               | MHz  |  |  |  |

| 1.8 V              | 250               | 250               | 250               | 250               | MHz  |  |  |  |

| 1.5 V              | 225               | 200               | 200               | 200               | MHz  |  |  |  |

| LVCMOS             | 350               | 300               | 250               | 250               | MHz  |  |  |  |

| GTL                | 200               | 167               | 125               | 125               | MHz  |  |  |  |

| GTL+               | 200               | 167               | 125               | 125               | MHz  |  |  |  |

| SSTL-3 Class I     | 200               | 167               | 167               | 133               | MHz  |  |  |  |

| SSTL-3 Class II    | 200               | 167               | 167               | 133               | MHz  |  |  |  |

| SSTL-2 Class I (3) | 200               | 200               | 167               | 167               | MHz  |  |  |  |

| SSTL-2 Class I (4) | 200               | 200               | 167               | 167               | MHz  |  |  |  |

| SSTL-2 Class I (5) | 150               | 134               | 134               | 134               | MHz  |  |  |  |

<sup>(1)</sup> These parameters are only available on row I/O pins.

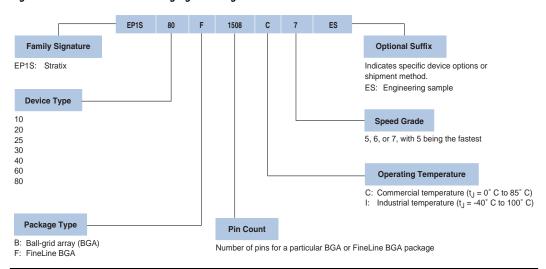

Figure 5-1. Stratix Device Packaging Ordering Information

| Mode 2–36                               | Port I/O Standards 2–102                            |

|-----------------------------------------|-----------------------------------------------------|

| Row & Column Interface Unit             | I/O Standards Supported for Enhanced PLL            |

| Signals 2–43                            | Pins 2–94                                           |

| Parity Bit Support 2–24                 | Lock Detect & Programmable Gated                    |

| Shift Register                          | Locked 2–98                                         |

| Memory Configuration 2–26               | PLL Locations 2–84                                  |

| Support 2–25                            | Programmable Bandwidth 2–91                         |

| Simple Dual-Port & Single-Port Memory   | Programmable Delay Chain 2-111                      |

| Configurations 2–23                     | Programmable Duty Cycle 2–98                        |

| Stratix IOE in DDR Input I/O            | Reconfiguration 2–90                                |

| Configuration 2–112                     |                                                     |

| Stratix IOE in DDR Output I/O           | Т                                                   |

| Configuration 2–114                     | ı                                                   |

| TriMatrix Memory 2–21                   | Testing                                             |

| True Dual-Port Memory                   | Temperature Sensing Diode 3–13                      |

| Configuration 2–22                      | Electrical Characteristics 3–14                     |

|                                         | External 3–14                                       |

| 0                                       | Temperature vs. Temperature-Sensing Diode           |

|                                         | Voltage 3–15                                        |

| Ordering Information 5–1                | Timing                                              |

| Device Pin-Outs 5–1                     | DSP                                                 |

| Packaging Ordering Information 5–2      | Block Internal Timing                               |

| Reference & Ordering Information 5–1    | Microparameter                                      |

| Output Registers 2–64                   | Descriptions 4–23                                   |

| Output Selection Multiplexer 2–64       | Microparameters 4–29                                |

|                                         | Dual-Port RAM Timing Microparameter                 |

| P                                       | Waveform 4–27                                       |

| P. 1                                    | External Timing in Stratix Devices 4–33             |

| Packaging                               | High-Speed I/O Timing 4–87                          |

| BGA Package Sizes 1–4                   | High-Speed Timing Specifications & Terminology 4–87 |

| Device Speed Grades 1–5                 | Internal Parameters 4–22                            |

| FineLine BGA Package Sizes 1–5          | IOE Internal Timing Microparameter                  |

| PCI-X 1.0 Specifications 4–10           | Descriptions 4–22                                   |

| Phase Shifting 2–103<br>PLL             | LE Internal Timing Microparameters 4–28             |

| Advanced Clear & Enable Control 2–98    | Logic Elements Internal Timing Microparam-          |

| Dynamically Programmable Counters & De- | eter Descriptions 4–22                              |

| lays in Stratix Device Enhanced         | Model 4–19                                          |

| PLLs 2–91                               | PLL Timing 4–94                                     |

| Enhanced                                | Preliminary & Final 4–19                            |

| Fast PLLs 2–81                          | Stratix Device Timing Model Status 4–19             |

| Fast PLL 2–100                          | Stratix JTAG                                        |

| Channel Layout EP1S10, EP1S20 or        | Timing Parameters & Values 3–4                      |

| EP1S25 Devices 2–138                    | TriMatrix Memory                                    |

| Channel Layout EP1S30 to EP1S80         | TriMatrix Memory Features 2–21                      |

| Devices 2–139                           | •                                                   |

Index-6 Altera Corporation