Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 1846                                                    |

| Number of Logic Elements/Cells | 18460                                                   |

| Total RAM Bits                 | 1669248                                                 |

| Number of I/O                  | 361                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                         |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 484-BBGA, FCBGA                                         |

| Supplier Device Package        | 484-FBGA (23x23)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s20f484c7 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

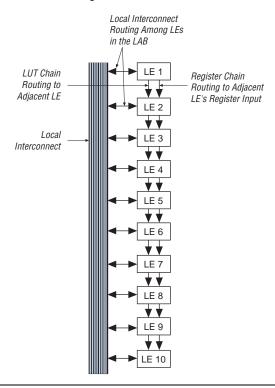

Figure 2-10. LUT Chain & Register Chain Interconnects

The C4 interconnects span four LABs, M512, or M4K blocks up or down from a source LAB. Every LAB has its own set of C4 interconnects to drive either up or down. Figure 2–11 shows the C4 interconnect connections from an LAB in a column. The C4 interconnects can drive and be driven by all types of architecture blocks, including DSP blocks, TriMatrix memory blocks, and vertical IOEs. For LAB interconnection, a primary LAB or its LAB neighbor can drive a given C4 interconnect. C4 interconnects can drive each other to extend their range as well as drive row interconnects for column-to-column connections.

Table 2–12 shows the input and output data signal connections for the column units (B1 to B6 and A1 to A6). It also shows the address and control signal input connections to the row units (R1 to R11).

| Unit Interface Block Input Clanele Output Cianele |                                              |                 |  |  |  |  |  |

|---------------------------------------------------|----------------------------------------------|-----------------|--|--|--|--|--|

| Unit Interface Block                              | Input Signals                                | Output Signals  |  |  |  |  |  |

| R1                                                | addressa[70]                                 |                 |  |  |  |  |  |

| R2                                                | addressa[158]                                |                 |  |  |  |  |  |

| R3                                                | byte_enable_a[70]<br>renwe_a                 |                 |  |  |  |  |  |

| R4                                                | -                                            |                 |  |  |  |  |  |

| R5                                                | -                                            |                 |  |  |  |  |  |

| R6                                                | clock_a<br>clocken_a<br>clock_b<br>clocken_b |                 |  |  |  |  |  |

| R7                                                | -                                            |                 |  |  |  |  |  |

| R8                                                | -                                            |                 |  |  |  |  |  |

| R9                                                | byte_enable_b[70]<br>renwe_b                 |                 |  |  |  |  |  |

| R10                                               | addressb[158]                                |                 |  |  |  |  |  |

| R11                                               | addressb[70]                                 |                 |  |  |  |  |  |

| B1                                                | datain_b[7160]                               | dataout_b[7160] |  |  |  |  |  |

| B2                                                | datain_b[5948]                               | dataout_b[5948] |  |  |  |  |  |

| B3                                                | datain_b[4736]                               | dataout_b[4736] |  |  |  |  |  |

| B4                                                | datain_b[3524]                               | dataout_b[3524] |  |  |  |  |  |

| B5                                                | datain_b[2312]                               | dataout_b[2312] |  |  |  |  |  |

| B6                                                | datain_b[110]                                | dataout_b[110]  |  |  |  |  |  |

| A1                                                | datain_a[7160]                               | dataout_a[7160] |  |  |  |  |  |

| A2                                                | datain_a[5948]                               | dataout_a[5948] |  |  |  |  |  |

| A3                                                | datain_a[4736]                               | dataout_a[4736] |  |  |  |  |  |

| A4                                                | datain_a[3524]                               | dataout_a[3524] |  |  |  |  |  |

| A5                                                | datain_a[2312]                               | dataout_a[2312] |  |  |  |  |  |

| A6                                                | datain_a[110]                                | dataout_a[110]  |  |  |  |  |  |

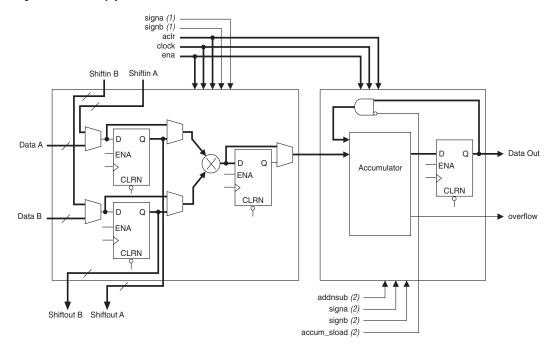

## Input Registers

A bank of optional input registers is located at the input of each multiplier and multiplicand inputs to the multiplier. When these registers are configured for parallel data inputs, they are driven by regular routing resources. You can use a clock signal, asynchronous clear signal, and a clock enable signal to independently control each set of A and B inputs for each multiplier in the DSP block. You select these control signals from a set of four different clock [3..0], aclr[3..0], and ena[3..0] signals that drive the entire DSP block.

You can also configure the input registers for a shift register application. In this case, the input registers feed the multiplier and drive two dedicated shift output lines:  $\mathtt{shiftoutA}$  and  $\mathtt{shiftoutB}$ . The shift outputs of one multiplier block directly feed the adjacent multiplier block in the same DSP block (or the next DSP block) as shown in Figure 2–33, to form a shift register chain. This chain can terminate in any block, that is, you can create any length of shift register chain up to 224 registers. You can use the input shift registers for FIR filter applications. One set of shift inputs can provide data for a filter, and the other are coefficients that are optionally loaded in serial or parallel. When implementing  $9 \times 9$ - and  $18 \times 18$ -bit multipliers, you do not need to implement external shift registers in LAB LEs. You implement all the filter circuitry within the DSP block and its routing resources, saving LE and general routing resources for general logic. External registers are needed for shift register inputs when using  $36 \times 36$ -bit multipliers.

## Multiply-Accumulator Mode

In multiply-accumulator mode (see Figure 2–37), the DSP block drives multiplied results to the adder/subtractor/accumulator block configured as an accumulator. You can implement one or two multiply-accumulators up to  $18 \times 18$  bits in one DSP block. The first and third multiplier subblocks are unused in this mode, because only one multiplier can feed one of two accumulators. The multiply-accumulator output can be up to 52 bits—a maximum of a 36-bit result with 16 bits of accumulation. The accum\_sload and overflow signals are only available in this mode. The addnsub signal can set the accumulator for decimation and the overflow signal indicates underflow condition.

Figure 2-37. Multiply-Accumulate Mode

## Notes to Figure 2-37:

- (1) These signals are not registered or registered once to match the data path pipeline.

- (2) These signals are not registered, registered once, or registered twice for latency to match the data path pipeline.

### Two-Multipliers Adder Mode

The two-multipliers adder mode uses the adder/subtractor/accumulator block to add or subtract the outputs of the multiplier block, which is useful for applications such as FFT functions and complex FIR filters. A

Table 2–19 shows the enhanced PLL and fast PLL features in Stratix devices.

| Feature                           | Enhanced PLL                                                    | Fast PLL                           |

|-----------------------------------|-----------------------------------------------------------------|------------------------------------|

| Clock multiplication and division | $m/(n \times post-scale counter)$ (1)                           | m/(post-scale counter) (2)         |

| Phase shift                       | Down to 156.25-ps increments (3), (4)                           | Down to 125-ps increments (3), (4) |

| Delay shift                       | 250-ps increments for ±3 ns                                     |                                    |

| Clock switchover                  | <b>✓</b>                                                        |                                    |

| PLL reconfiguration               | <b>✓</b>                                                        |                                    |

| Programmable bandwidth            | <b>✓</b>                                                        |                                    |

| Spread spectrum clocking          | ✓                                                               |                                    |

| Programmable duty cycle           | <b>✓</b>                                                        | ✓                                  |

| Number of internal clock outputs  | 6                                                               | 3 (5)                              |

| Number of external clock outputs  | Four differential/eight singled-ended or one single-ended $(6)$ | (7)                                |

| Number of feedback clock inputs   | 2 (8)                                                           |                                    |

#### Notes to Table 2-19:

- (1) For enhanced PLLs, *m*, *n*, range from 1 to 512 and post-scale counters *g*, *l*, *e* range from 1 to 1024 with 50% duty cycle. With a non-50% duty cycle the post-scale counters *g*, *l*, *e* range from 1 to 512.

- (2) For fast PLLs, *m* and post-scale counters range from 1 to 32.

- (3) The smallest phase shift is determined by the voltage controlled oscillator (VCO) period divided by 8.

- (4) For degree increments, Stratix devices can shift all output frequencies in increments of at least 45°. Smaller degree increments are possible depending on the frequency and divide parameters.

- (5) PLLs 7, 8, 9, and 10 have two output ports per PLL. PLLs 1, 2, 3, and 4 have three output ports per PLL.

- (6) Every Stratix device has two enhanced PLLs (PLLs 5 and 6) with either eight single-ended outputs or four differential outputs each. Two additional enhanced PLLs (PLLs 11 and 12) in EPIS80, EPIS60, and EPIS40 devices each have one single-ended output. Devices in the 780 pin FineLine BGA packages do not support PLLs 11 and 12.

- (7) Fast PLLs can drive to any I/O pin as an external clock. For high-speed differential I/O pins, the device uses a data channel to generate txclkout.

- (8) Every Stratix device has two enhanced PLLs with one single-ended or differential external feedback input per PLL.

## External Clock Inputs

Each fast PLL supports single-ended or differential inputs for source synchronous transmitters or for general-purpose use. Source-synchronous receivers support differential clock inputs. The fast PLL inputs are fed by CLK [0..3], CLK [8..11], and FPLL [7..10] CLK pins, as shown in Figure 2–50 on page 2–85.

Table 2–22 shows the I/O standards supported by fast PLL input pins.

| Table 2–22. Fast PLL Port I/O Stan | Table 2–22. Fast PLL Port I/O Standards (Part 1 of 2) |           |  |  |  |  |  |

|------------------------------------|-------------------------------------------------------|-----------|--|--|--|--|--|

| I/O Ctondovd                       | li li                                                 | nput      |  |  |  |  |  |

| I/O Standard                       | INCLK                                                 | PLLENABLE |  |  |  |  |  |

| LVTTL                              | ✓                                                     | ✓         |  |  |  |  |  |

| LVCMOS                             | ✓                                                     | ✓         |  |  |  |  |  |

| 2.5 V                              | ✓                                                     |           |  |  |  |  |  |

| 1.8 V                              | ✓                                                     |           |  |  |  |  |  |

| 1.5 V                              | ✓                                                     |           |  |  |  |  |  |

| 3.3-V PCI                          |                                                       |           |  |  |  |  |  |

| 3.3-V PCI-X 1.0                    |                                                       |           |  |  |  |  |  |

| LVPECL                             | <b>✓</b>                                              |           |  |  |  |  |  |

| 3.3-V PCML                         | <b>✓</b>                                              |           |  |  |  |  |  |

| LVDS                               | ✓                                                     |           |  |  |  |  |  |

| HyperTransport technology          | ✓                                                     |           |  |  |  |  |  |

| Differential HSTL                  | ✓                                                     |           |  |  |  |  |  |

| Differential SSTL                  |                                                       |           |  |  |  |  |  |

| 3.3-V GTL                          |                                                       |           |  |  |  |  |  |

| 3.3-V GTL+                         | ✓                                                     |           |  |  |  |  |  |

| 1.5-V HSTL Class I                 | ✓                                                     |           |  |  |  |  |  |

| 1.5-V HSTL Class II                |                                                       |           |  |  |  |  |  |

| 1.8-V HSTL Class I                 | ✓                                                     |           |  |  |  |  |  |

| 1.8-V HSTL Class II                |                                                       |           |  |  |  |  |  |

| SSTL-18 Class I                    | <b>✓</b>                                              |           |  |  |  |  |  |

| SSTL-18 Class II                   |                                                       |           |  |  |  |  |  |

| SSTL-2 Class I                     | ✓                                                     |           |  |  |  |  |  |

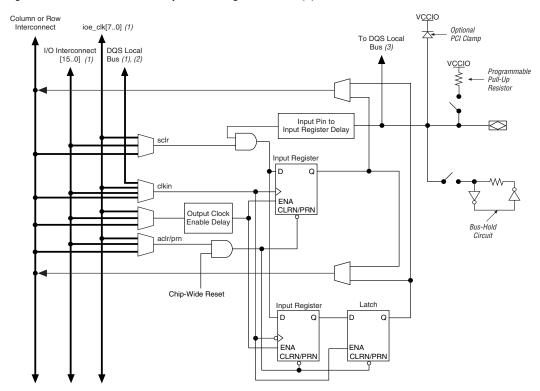

Figure 2–65. Stratix IOE in DDR Input I/O Configuration Note (1)

*Notes to Figure 2–65:*

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) This signal connection is only allowed on dedicated DQ function pins.

- (3) This signal is for dedicated DQS function pins only.

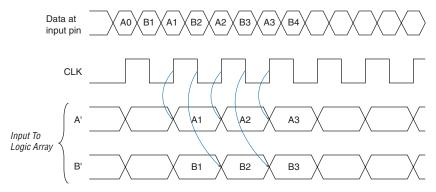

Figure 2-66. Input Timing Diagram in DDR Mode

When using the IOE for DDR outputs, the two output registers are configured to clock two data paths from LEs on rising clock edges. These output registers are multiplexed by the clock to drive the output pin at a  $\times 2$  rate. One output register clocks the first bit out on the clock high time, while the other output register clocks the second bit out on the clock low time. Figure 2–67 shows the IOE configured for DDR output. Figure 2–68 shows the DDR output timing diagram.

| Table 2-27. | DQS & DQ Bus Mode Support                                       | (Part 2 of 2) Note (   | 1)                      |                         |

|-------------|-----------------------------------------------------------------|------------------------|-------------------------|-------------------------|

| Device      | Package                                                         | Number of ×8<br>Groups | Number of ×16<br>Groups | Number of ×32<br>Groups |

| EP1S25      | 672-pin BGA<br>672-pin FineLine BGA                             | 16 (3)                 | 8                       | 4                       |

|             | 780-pin FineLine BGA<br>1,020-pin FineLine BGA                  | 20                     | 8                       | 4                       |

| EP1S30      | 956-pin BGA<br>780-pin FineLine BGA<br>1,020-pin FineLine BGA   | 20                     | 8                       | 4                       |

| EP1S40      | 956-pin BGA<br>1,020-pin FineLine BGA<br>1,508-pin FineLine BGA | 20                     | 8                       | 4                       |

| EP1S60      | 956-pin BGA<br>1,020-pin FineLine BGA<br>1,508-pin FineLine BGA | 20                     | 8                       | 4                       |

| EP1S80      | 956-pin BGA<br>1,508-pin FineLine BGA<br>1,923-pin FineLine BGA | 20                     | 8                       | 4                       |

#### *Notes to Table 2–27:*

- See the Selectable I/O Standards in Stratix & Stratix GX Devices chapter in the Stratix Device Handbook, Volume 2 for V<sub>RFF</sub> guidelines.

- (2) These packages have six groups in I/O banks 3 and 4 and six groups in I/O banks 7 and 8.

- (3) These packages have eight groups in I/O banks 3 and 4 and eight groups in I/O banks 7 and 8.

- (4) This package has nine groups in I/O banks 3 and 4 and nine groups in I/O banks 7 and 8.

- (5) These packages have three groups in I/O banks 3 and 4 and four groups in I/O banks 7 and 8.

A compensated delay element on each DQS pin automatically aligns input DQS synchronization signals with the data window of their corresponding DQ data signals. The DQS signals drive a local DQS bus in the top and bottom I/O banks. This DQS bus is an additional resource to the I/O clocks and is used to clock DQ input registers with the DQS signal.

Two separate single phase-shifting reference circuits are located on the top and bottom of the Stratix device. Each circuit is driven by a system reference clock through the CLK pins that is the same frequency as the DQS signal. Clock pins CLK [15..12] p feed the phase-shift circuitry on the top of the device and clock pins CLK [7..4] p feed the phase-shift circuitry on the bottom of the device. The phase-shifting reference circuit on the top of the device controls the compensated delay elements for all 10 DQS pins located at the top of the device. The phase-shifting reference circuit on the bottom of the device controls the compensated delay elements for all 10 DQS pins located on the bottom of the device. All 10 delay elements (DQS signals) on either the top or bottom of the device

| Symbol            | Parameter                 | Conditions                  | Minimum                    | Typical | Maximum                     | Unit |

|-------------------|---------------------------|-----------------------------|----------------------------|---------|-----------------------------|------|

| V <sub>CCIO</sub> | Output supply voltage     |                             | 3.0                        |         | 3.6                         | V    |

| V <sub>IH</sub>   | High-level input voltage  |                             | 0.5 ×<br>V <sub>CCIO</sub> |         | V <sub>CCIO</sub> + 0.5     | V    |

| V <sub>IL</sub>   | Low-level input voltage   |                             | -0.5                       |         | 0.35 ×<br>V <sub>CCIO</sub> | V    |

| V <sub>IPU</sub>  | Input pull-up voltage     |                             | 0.7 ×<br>V <sub>CCIO</sub> |         |                             | V    |

| V <sub>OH</sub>   | High-level output voltage | $I_{OUT} = -500 \mu A$      | 0.9 ×<br>V <sub>CCIO</sub> |         |                             | V    |

| V <sub>OL</sub>   | Low-level output voltage  | I <sub>OUT</sub> = 1,500 μA |                            |         | 0.1 ×<br>V <sub>CCIO</sub>  | V    |

| Table 4–16.      | Table 4–16. GTL+ I/O Specifications |                             |                        |         |                        |      |  |  |  |

|------------------|-------------------------------------|-----------------------------|------------------------|---------|------------------------|------|--|--|--|

| Symbol           | Parameter                           | Conditions                  | Minimum                | Typical | Maximum                | Unit |  |  |  |

| $V_{TT}$         | Termination voltage                 |                             | 1.35                   | 1.5     | 1.65                   | V    |  |  |  |

| V <sub>REF</sub> | Reference voltage                   |                             | 0.88                   | 1.0     | 1.12                   | V    |  |  |  |

| V <sub>IH</sub>  | High-level input voltage            |                             | V <sub>REF</sub> + 0.1 |         |                        | V    |  |  |  |

| V <sub>IL</sub>  | Low-level input voltage             |                             |                        |         | V <sub>REF</sub> - 0.1 | V    |  |  |  |

| V <sub>OL</sub>  | Low-level output voltage            | I <sub>OL</sub> = 34 mA (3) |                        |         | 0.65                   | V    |  |  |  |

| Table 4–17. GTL I/O Specifications |                          |                             |                         |         |                         |      |  |  |

|------------------------------------|--------------------------|-----------------------------|-------------------------|---------|-------------------------|------|--|--|

| Symbol                             | Parameter                | Conditions                  | Minimum                 | Typical | Maximum                 | Unit |  |  |

| $V_{TT}$                           | Termination voltage      |                             | 1.14                    | 1.2     | 1.26                    | V    |  |  |

| $V_{REF}$                          | Reference voltage        |                             | 0.74                    | 0.8     | 0.86                    | V    |  |  |

| V <sub>IH</sub>                    | High-level input voltage |                             | V <sub>REF</sub> + 0.05 |         |                         | V    |  |  |

| V <sub>IL</sub>                    | Low-level input voltage  |                             |                         |         | V <sub>REF</sub> – 0.05 | V    |  |  |

| V <sub>OL</sub>                    | Low-level output voltage | I <sub>OL</sub> = 40 mA (3) |                         |         | 0.4                     | V    |  |  |

device. Decoupling capacitors were not used in this measurement. To factor in the current for decoupling capacitors, sum up the current for each capacitor using the following equation:

$$I = C (dV/dt)$$

If the regulator or power supply minimum output current is more than the Stratix device requires, then the device may consume more current than the maximum current listed in Table 4–34. However, the device does not require any more current to successfully power up than what is listed in Table 4–34.

| Table 4–34. Stratix Power-Up Current (I <sub>CCINT</sub> ) Requirements Note (1) |                |         |       |  |  |  |

|----------------------------------------------------------------------------------|----------------|---------|-------|--|--|--|

| Dovino                                                                           | Power-Up Curre | Unit    |       |  |  |  |

| Device                                                                           | Typical        | Maximum | UIIIL |  |  |  |

| EP1S10                                                                           | 250            | 700     | mA    |  |  |  |

| EP1S20                                                                           | 400            | 1,200   | mA    |  |  |  |

| EP1S25                                                                           | 500            | 1,500   | mA    |  |  |  |

| EP1S30                                                                           | 550            | 1,900   | mA    |  |  |  |

| EP1S40                                                                           | 650            | 2,300   | mA    |  |  |  |

| EP1S60                                                                           | 800            | 2,600   | mA    |  |  |  |

| EP1S80                                                                           | 1,000          | 3,000   | mA    |  |  |  |

Note to Table 4-34:

The exact amount of current consumed varies according to the process, temperature, and power ramp rate. Stratix devices typically require less current during power up than shown in Table 4–34. The user-mode current during device operation is generally higher than the power-up current.

The duration of the  $I_{CCINT}$  power-up requirement depends on the  $V_{CCINT}$  voltage supply rise time. The power-up current consumption drops when the  $V_{CCINT}$  supply reaches approximately 0.75 V.

<sup>(1)</sup> The maximum test conditions are for  $0^{\circ}$  C and typical test conditions are for  $40^{\circ}$  C

|                          | T .                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                   | Parameter                                                                                                                                                                                                                                                                                                                                                 |

| t <sub>M512RC</sub>      | Synchronous read cycle time                                                                                                                                                                                                                                                                                                                               |

| t <sub>M512WC</sub>      | Synchronous write cycle time                                                                                                                                                                                                                                                                                                                              |

| t <sub>M512WERESU</sub>  | Write or read enable setup time before clock                                                                                                                                                                                                                                                                                                              |

| t <sub>M512WEREH</sub>   | Write or read enable hold time after clock                                                                                                                                                                                                                                                                                                                |

| t <sub>M512CLKENSU</sub> | Clock enable setup time before clock                                                                                                                                                                                                                                                                                                                      |

| t <sub>M512CLKENH</sub>  | Clock enable hold time after clock                                                                                                                                                                                                                                                                                                                        |

| t <sub>M512DATASU</sub>  | Data setup time before clock                                                                                                                                                                                                                                                                                                                              |

| t <sub>M512DATAH</sub>   | Data hold time after clock                                                                                                                                                                                                                                                                                                                                |

| t <sub>M512WADDRSU</sub> | Write address setup time before clock                                                                                                                                                                                                                                                                                                                     |

| t <sub>M512WADDRH</sub>  | Write address hold time after clock                                                                                                                                                                                                                                                                                                                       |

| t <sub>M512RADDRSU</sub> | Read address setup time before clock                                                                                                                                                                                                                                                                                                                      |

| t <sub>M512RADDRH</sub>  | Read address hold time after clock                                                                                                                                                                                                                                                                                                                        |

| t <sub>M512DATACO1</sub> | Clock-to-output delay when using output registers                                                                                                                                                                                                                                                                                                         |

| t <sub>M512DATACO2</sub> | Clock-to-output delay without output registers                                                                                                                                                                                                                                                                                                            |

| t <sub>M512CLKHL</sub>   | Register minimum clock high or low time. This is a limit on the min time for the clock on the registers in these blocks. The actual performance is dependent upon the internal point-to-point delays in the blocks and may give slower performance as shown in Table 4–36 on page 4–20 and as reported by the timing analyzer in the Quartus II software. |

| t <sub>M512CLR</sub>     | Minimum clear pulse width                                                                                                                                                                                                                                                                                                                                 |

| Table 4–41. M4K Block Internal Timing Microparameter Descriptions (Part 1 of 2) |                                              |  |  |  |  |  |

|---------------------------------------------------------------------------------|----------------------------------------------|--|--|--|--|--|

| Symbol                                                                          | Parameter                                    |  |  |  |  |  |

| t <sub>M4KRC</sub>                                                              | Synchronous read cycle time                  |  |  |  |  |  |

| t <sub>M4KWC</sub>                                                              | Synchronous write cycle time                 |  |  |  |  |  |

| t <sub>M4KWERESU</sub>                                                          | Write or read enable setup time before clock |  |  |  |  |  |

| t <sub>M4KWEREH</sub>                                                           | Write or read enable hold time after clock   |  |  |  |  |  |

| t <sub>M4KCLKENSU</sub>                                                         | Clock enable setup time before clock         |  |  |  |  |  |

| t <sub>M4KCLKENH</sub>                                                          | Clock enable hold time after clock           |  |  |  |  |  |

| t <sub>M4KBESU</sub>                                                            | Byte enable setup time before clock          |  |  |  |  |  |

| t <sub>M4KBEH</sub>                                                             | Byte enable hold time after clock            |  |  |  |  |  |

| t <sub>M4KDATAASU</sub>                                                         | A port data setup time before clock          |  |  |  |  |  |

| Table 4–50. M-RAM Block Internal Timing Microparameters (Part 2 of 2) |       |       |       |       |       |       |       |       |      |

|-----------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Symbol                                                                | -     | -5    |       | -6    |       | -7    |       | -8    |      |

| - Symbol                                                              | Min   | Max   | Min   | Max   | Min   | Max   | Min   | Max   | Unit |

| t <sub>MRAMBESU</sub>                                                 | 25    |       | 25    |       | 28    |       | 33    |       | ps   |

| t <sub>MRAMBEH</sub>                                                  | 18    |       | 20    |       | 23    |       | 27    |       | ps   |

| t <sub>MRAMDATAASU</sub>                                              | 25    |       | 25    |       | 28    |       | 33    |       | ps   |

| t <sub>MRAMDATAAH</sub>                                               | 18    |       | 20    |       | 23    |       | 27    |       | ps   |

| t <sub>MRAMADDRASU</sub>                                              | 25    |       | 25    |       | 28    |       | 33    |       | ps   |

| t <sub>MRAMADDRAH</sub>                                               | 18    |       | 20    |       | 23    |       | 27    |       | ps   |

| t <sub>MRAMDATABSU</sub>                                              | 25    |       | 25    |       | 28    |       | 33    |       | ps   |

| t <sub>MRAMDATABH</sub>                                               | 18    |       | 20    |       | 23    |       | 27    |       | ps   |

| t <sub>MRAMADDRBSU</sub>                                              | 25    |       | 25    |       | 28    |       | 33    |       | ps   |

| t <sub>MRAMADDRBH</sub>                                               | 18    |       | 20    |       | 23    |       | 27    |       | ps   |

| t <sub>MRAMDATACO1</sub>                                              |       | 1,038 |       | 1,053 |       | 1,210 |       | 1,424 | ps   |

| t <sub>MRAMDATACO2</sub>                                              |       | 4,362 |       | 4,939 |       | 5,678 |       | 6,681 | ps   |

| t <sub>MRAMCLKHL</sub>                                                | 1,000 |       | 1,111 |       | 1,190 |       | 1,400 |       | ps   |

| t <sub>MRAMCLR</sub>                                                  | 135   |       | 150   |       | 172   |       | 202   |       | ps   |

| Table 4–51. Routing Delay Internal Timing Parameters |     |     |     |     |     |     |     |     |      |

|------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| Symbol                                               | -5  |     | -6  |     | -7  |     | -8  |     | Unit |

|                                                      | Min | Max | Min | Max | Min | Max | Min | Max |      |

| t <sub>R4</sub>                                      |     | 268 |     | 295 |     | 339 |     | 390 | ps   |

| t <sub>R8</sub>                                      |     | 371 |     | 349 |     | 401 |     | 461 | ps   |

| t <sub>R24</sub>                                     |     | 465 |     | 512 |     | 588 |     | 676 | ps   |

| t <sub>C4</sub>                                      |     | 440 |     | 484 |     | 557 |     | 641 | ps   |

| t <sub>C8</sub>                                      |     | 577 |     | 634 |     | 730 |     | 840 | ps   |

| t <sub>C16</sub>                                     |     | 445 |     | 489 |     | 563 |     | 647 | ps   |

| t <sub>LOCAL</sub>                                   |     | 313 |     | 345 |     | 396 |     | 455 | ps   |

Routing delays vary depending on the load on that specific routing line. The Quartus II software reports the routing delay information when running the timing analysis for a design.

| Table 4–53. Stratix Regional Clock External I/O Ti | iming Parameters (Part 2 |

|----------------------------------------------------|--------------------------|

| <b>of 2)</b> Notes (1), (2)                        |                          |

|                                                    |                          |

| Symbol             | Parameter                                                                                                                              |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>XZPLL</sub> | Synchronous IOE output enable register to output pin disable delay using regional clock fed by Enhanced PLL with default phase setting |

| t <sub>ZXPLL</sub> | Synchronous IOE output enable register to output pin enable delay using regional clock fed by Enhanced PLL with default phase setting  |

#### *Notes to Table 4–53:*

- (1) These timing parameters are sample-tested only.

- (2) These timing parameters are for column and row IOE pins. You should use the Quartus II software to verify the external timing for any pin.

Table 4–54 shows the external I/O timing parameters when using global clock networks.

| <b>Table 4–54. Stratix Global Clock External I/O Timing Parameters</b> Notes (1), (2) |                                                                                                                                       |  |  |  |  |

|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol                                                                                | Parameter                                                                                                                             |  |  |  |  |

| t <sub>INSU</sub>                                                                     | Setup time for input or bidirectional pin using IOE input register with global clock fed by ${\tt CLK}$ pin                           |  |  |  |  |

| t <sub>INH</sub>                                                                      | Hold time for input or bidirectional pin using IOE input register with global clock fed by ${\tt CLK}$ pin                            |  |  |  |  |

| t <sub>OUTCO</sub>                                                                    | Clock-to-output delay output or bidirectional pin using IOE output register with global clock fed by CLK pin                          |  |  |  |  |

| t <sub>INSUPLL</sub>                                                                  | Setup time for input or bidirectional pin using IOE input register with global clock fed by Enhanced PLL with default phase setting   |  |  |  |  |

| t <sub>INHPLL</sub>                                                                   | Hold time for input or bidirectional pin using IOE input register with global clock fed by Enhanced PLL with default phase setting    |  |  |  |  |

| t <sub>OUTCOPLL</sub>                                                                 | Clock-to-output delay output or bidirectional pin using IOE output register with global clock Enhanced PLL with default phase setting |  |  |  |  |

| t <sub>XZPLL</sub>                                                                    | Synchronous IOE output enable register to output pin disable delay using global clock fed by Enhanced PLL with default phase setting  |  |  |  |  |

| t <sub>ZXPLL</sub>                                                                    | Synchronous IOE output enable register to output pin enable delay using global clock fed by Enhanced PLL with default phase setting   |  |  |  |  |

#### Notes to Table 4-54:

- (1) These timing parameters are sample-tested only.

- (2) These timing parameters are for column and row IOE pins. You should use the Quartus II software to verify the external timing for any pin.

| Table 4–59. EP1S10 External I/O Timing on Row Pins Using Regional Clock Networks Note (1) |                |       |                |       |                |       |                |     |      |

|-------------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-----|------|

| Parameter                                                                                 | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |     |      |

|                                                                                           | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max | Unit |

| t <sub>INSU</sub>                                                                         | 2.161          |       | 2.336          |       | 2.685          |       | NA             |     | ns   |

| t <sub>INH</sub>                                                                          | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns   |

| t <sub>OUTCO</sub>                                                                        | 2.434          | 4.889 | 2.434          | 5.226 | 2.434          | 5.643 | NA             | NA  | ns   |

| t <sub>XZ</sub>                                                                           | 2.461          | 4.493 | 2.461          | 5.282 | 2.461          | 5.711 | NA             | NA  | ns   |

| t <sub>ZX</sub>                                                                           | 2.461          | 4.493 | 2.461          | 5.282 | 2.461          | 5.711 | NA             | NA  | ns   |

| t <sub>INSUPLL</sub>                                                                      | 1.057          |       | 1.172          |       | 1.315          |       | NA             |     | ns   |

| t <sub>INHPLL</sub>                                                                       | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns   |

| t <sub>OUTCOPLL</sub>                                                                     | 1.327          | 2.773 | 1.327          | 2.848 | 1.327          | 2.940 | NA             | NA  | ns   |

| t <sub>XZPLL</sub>                                                                        | 1.354          | 2.827 | 1.354          | 2.904 | 1.354          | 3.008 | NA             | NA  | ns   |

| t <sub>ZXPLL</sub>                                                                        | 1.354          | 2.827 | 1.354          | 2.904 | 1.354          | 3.008 | NA             | NA  | ns   |

| Table 4–60. EP1S10 External I/O Timing on Row Pins Using Global Clock Networks Note (1) |                |       |                |       |                |       |                |     |      |

|-----------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-----|------|

| Doromotor                                                                               | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |     | 1111 |

| Parameter                                                                               | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max | Unit |

| t <sub>INSU</sub>                                                                       | 1.787          |       | 1.944          |       | 2.232          |       | NA             |     | ns   |

| t <sub>INH</sub>                                                                        | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns   |

| t <sub>OUTCO</sub>                                                                      | 2.647          | 5.263 | 2.647          | 5.618 | 2.647          | 6.069 | NA             | NA  | ns   |

| t <sub>XZ</sub>                                                                         | 2.674          | 5.317 | 2.674          | 5.674 | 2.674          | 6.164 | NA             | NA  | ns   |

| t <sub>ZX</sub>                                                                         | 2.674          | 5.317 | 2.674          | 5.674 | 2.674          | 6.164 | NA             | NA  | ns   |

| t <sub>INSUPLL</sub>                                                                    | 1.371          |       | 1.1472         |       | 1.654          |       | NA             |     | ns   |

| t <sub>INHPLL</sub>                                                                     | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns   |

| t <sub>OUTCOPLL</sub>                                                                   | 1.144          | 2.459 | 1.144          | 2.548 | 1.144          | 2.601 | NA             | NA  | ns   |

| t <sub>XZPLL</sub>                                                                      | 1.171          | 2.513 | 1.171          | 2.604 | 1.171          | 2.669 | NA             | NA  | ns   |

| t <sup>ZXPLL</sup>                                                                      | 1.171          | 2.513 | 1.171          | 2.604 | 1.171          | 2.669 | NA             | NA  | ns   |

*Note to Tables 4–55 to 4–60:*

<sup>(1)</sup> Only EP1S25, EP1S30, and EP1S40 have speed grade of -8.

| Parameter            | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | 11!4 |

|----------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-------|------|

|                      | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max   | Unit |

| t <sub>XZ</sub>      | 2.754          | 5.406 | 2.754          | 5.848 | 2.754          | 6.412 | 2.754          | 7.159 | ns   |

| t <sub>ZX</sub>      | 2.754          | 5.406 | 2.754          | 5.848 | 2.754          | 6.412 | 2.754          | 7.159 | ns   |

| t <sub>INSUPLL</sub> | 1.265          |       | 1.236          |       | 1.403          |       | 1.756          |       | ns   |

| t <sub>INHPLL</sub>  | 0.000          |       | 0.000          |       | 0.000          |       | 0.000          |       | ns   |

| toutcopll            | 1.068          | 2.302 | 1.068          | 2.483 | 1.068          | 2.510 | 1.068          | 2.423 | ns   |

| t <sub>XZPLL</sub>   | 1.008          | 2.176 | 1.008          | 2.351 | 1.008          | 2.386 | 1.008          | 2.308 | ns   |

| t <sub>ZXPLL</sub>   | 1.008          | 2.176 | 1.008          | 2.351 | 1.008          | 2.386 | 1.008          | 2.308 | ns   |

| Table 4–76. EP1S30 External I/O Timing on Row Pins Using Fast Regional Clock Networks |                |       |                |       |                |       |                |       |       |

|---------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-------|-------|

|                                                                                       | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | 11-14 |

| Parameters                                                                            | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max   | Unit  |

| t <sub>INSU</sub>                                                                     | 2.616          |       | 2.808          |       | 3.223          |       | 3.797          |       | ns    |

| t <sub>INH</sub>                                                                      | 0.000          |       | 0.000          |       | 0.000          |       | 0.000          |       | ns    |

| t <sub>outco</sub>                                                                    | 2.542          | 5.114 | 2.542          | 5.502 | 2.542          | 5.965 | 2.542          | 6.581 | ns    |

| t <sub>XZ</sub>                                                                       | 2.569          | 5.168 | 2.569          | 5.558 | 2.569          | 6.033 | 2.569          | 6.663 | ns    |

| t <sub>ZX</sub>                                                                       | 2.569          | 5.168 | 2.569          | 5.558 | 2.569          | 6.033 | 2.569          | 6.663 | ns    |

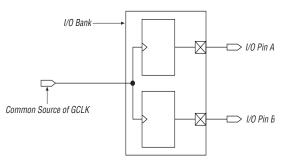

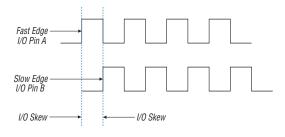

## Definition of I/O Skew

I/O skew is defined as the absolute value of the worst-case difference in clock-to-out times ( $t_{\rm CO}$ ) between any two output registers fed by a common clock source.

I/O bank skew is made up of the following components:

- Clock network skews: This is the difference between the arrival times of the clock at the clock input port of the two IOE registers.

- Package skews: This is the package trace length differences between (I/O pad A to I/O pin A) and (I/O pad B to I/O pin B).

Figure 4–5 shows an example of two IOE registers located in the same bank, being fed by a common clock source. The clock can come from an input pin or from a PLL output.

Figure 4-5. I/O Skew within an I/O Bank

process and operating conditions. Run the timing analyzer in the Quartus II software at the fast and slow operating conditions to see the phase shift range that is achieved below these frequencies.

| Table 4–135. Stratix DLL Low Frequency Limit for Full Phase Shift |                                           |      |  |  |  |

|-------------------------------------------------------------------|-------------------------------------------|------|--|--|--|

| Phase Shift                                                       | Minimum Frequency for<br>Full Phase Shift | Unit |  |  |  |

| 72°                                                               | 119                                       | MHz  |  |  |  |

| 90°                                                               | 149                                       | MHz  |  |  |  |

| Mode 2–36                               | Port I/O Standards 2–102                            |

|-----------------------------------------|-----------------------------------------------------|

| Row & Column Interface Unit             | I/O Standards Supported for Enhanced PLL            |

| Signals 2–43                            | Pins 2–94                                           |

| Parity Bit Support 2–24                 | Lock Detect & Programmable Gated                    |

| Shift Register                          | Locked 2–98                                         |

| Memory Configuration 2–26               | PLL Locations 2–84                                  |

| Support 2–25                            | Programmable Bandwidth 2–91                         |

| Simple Dual-Port & Single-Port Memory   | Programmable Delay Chain 2-111                      |

| Configurations 2–23                     | Programmable Duty Cycle 2–98                        |

| Stratix IOE in DDR Input I/O            | Reconfiguration 2–90                                |

| Configuration 2–112                     |                                                     |

| Stratix IOE in DDR Output I/O           | Т                                                   |

| Configuration 2–114                     | ı                                                   |

| TriMatrix Memory 2–21                   | Testing                                             |

| True Dual-Port Memory                   | Temperature Sensing Diode 3–13                      |

| Configuration 2–22                      | Electrical Characteristics 3–14                     |

|                                         | External 3–14                                       |

| 0                                       | Temperature vs. Temperature-Sensing Diode           |

|                                         | Voltage 3–15                                        |

| Ordering Information 5–1                | Timing                                              |

| Device Pin-Outs 5–1                     | DSP                                                 |

| Packaging Ordering Information 5–2      | Block Internal Timing                               |

| Reference & Ordering Information 5–1    | Microparameter                                      |

| Output Registers 2–64                   | Descriptions 4–23                                   |

| Output Selection Multiplexer 2–64       | Microparameters 4–29                                |

|                                         | Dual-Port RAM Timing Microparameter                 |

| P                                       | Waveform 4–27                                       |

| P. 1                                    | External Timing in Stratix Devices 4–33             |

| Packaging                               | High-Speed I/O Timing 4–87                          |

| BGA Package Sizes 1–4                   | High-Speed Timing Specifications & Terminology 4–87 |

| Device Speed Grades 1–5                 | Internal Parameters 4–22                            |

| FineLine BGA Package Sizes 1–5          | IOE Internal Timing Microparameter                  |

| PCI-X 1.0 Specifications 4–10           | Descriptions 4–22                                   |

| Phase Shifting 2–103<br>PLL             | LE Internal Timing Microparameters 4–28             |

| Advanced Clear & Enable Control 2–98    | Logic Elements Internal Timing Microparam-          |

| Dynamically Programmable Counters & De- | eter Descriptions 4–22                              |

| lays in Stratix Device Enhanced         | Model 4–19                                          |

| PLLs 2–91                               | PLL Timing 4–94                                     |

| Enhanced                                | Preliminary & Final 4–19                            |

| Fast PLLs 2–81                          | Stratix Device Timing Model Status 4–19             |

| Fast PLL 2–100                          | Stratix JTAG                                        |

| Channel Layout EP1S10, EP1S20 or        | Timing Parameters & Values 3–4                      |

| EP1S25 Devices 2–138                    | TriMatrix Memory                                    |

| Channel Layout EP1S30 to EP1S80         | TriMatrix Memory Features 2–21                      |

| Devices 2–139                           | •                                                   |

Index-6 Altera Corporation