Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 1846                                                     |

| Number of Logic Elements/Cells | 18460                                                    |

| Total RAM Bits                 | 1669248                                                  |

| Number of I/O                  | 361                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 484-BBGA, FCBGA                                          |

| Supplier Device Package        | 484-FBGA (23x23)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s20f484c7n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Altera Corporation Section I–5

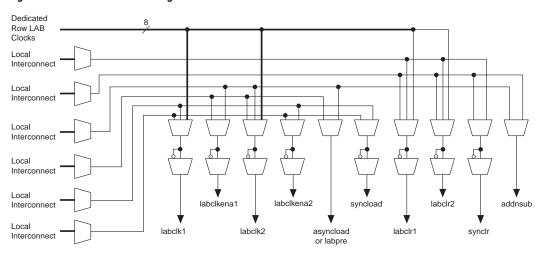

With the LAB-wide addnsub control signal, a single LE can implement a one-bit adder and subtractor. This saves LE resources and improves performance for logic functions such as DSP correlators and signed multipliers that alternate between addition and subtraction depending on data.

The LAB row clocks [7..0] and LAB local interconnect generate the LAB-wide control signals. The MultiTrack $^{\text{IM}}$  interconnect's inherent low skew allows clock and control signal distribution in addition to data. Figure 2–4 shows the LAB control signal generation circuit.

Figure 2-4. LAB-Wide Control Signals

## **Logic Elements**

The smallest unit of logic in the Stratix architecture, the LE, is compact and provides advanced features with efficient logic utilization. Each LE contains a four-input LUT, which is a function generator that can implement any function of four variables. In addition, each LE contains a programmable register and carry chain with carry select capability. A single LE also supports dynamic single bit addition or subtraction mode selectable by an LAB-wide control signal. Each LE drives all types of interconnects: local, row, column, LUT chain, register chain, and direct link interconnects. See Figure 2–5.

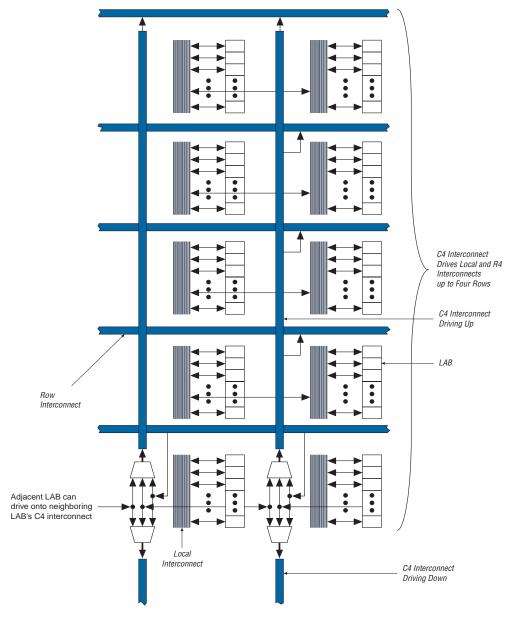

Figure 2–11. C4 Interconnect Connections Note (1)

Note to Figure 2–11:

(1) Each C4 interconnect can drive either up or down four rows.

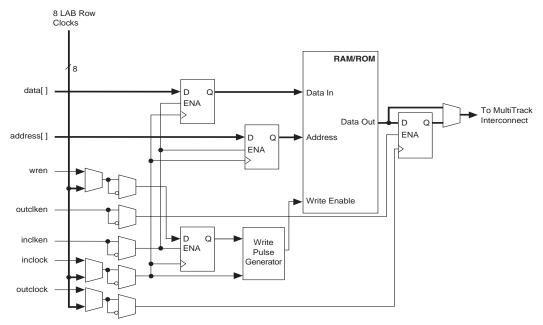

## **Single-Port Mode**

The memory blocks also support single-port mode, used when simultaneous reads and writes are not required. See Figure 2–28. A single block in a memory block can support up to two single-port mode RAM blocks in the M4K RAM blocks if each RAM block is less than or equal to 2K bits in size.

Figure 2–28. Single-Port Mode Note (1)

Note to Figure 2-28:

(1) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

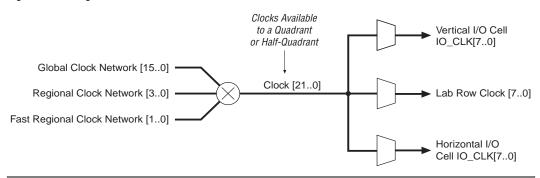

Figure 2-46. Regional Clock Bus

IOE clocks have horizontal and vertical block regions that are clocked by eight I/O clock signals chosen from the 22 quadrant or half-quadrant clock resources. Figures 2–47 and 2–48 show the quadrant and half-quadrant relationship to the I/O clock regions, respectively. The vertical regions (column pins) have less clock delay than the horizontal regions (row pins).

Any of the four external output counters can drive the single-ended or differential clock outputs for PLLs 5 and 6. This means one counter or frequency can drive all output pins available from PLL 5 or PLL 6. Each pair of output pins (four pins total) has dedicated VCC and GND pins to reduce the output clock's overall jitter by providing improved isolation from switching I/O pins.

For PLLs 5 and 6, each pin of a single-ended output pair can either be in phase or 180° out of phase. The clock output pin pairs support the same I/O standards as standard output pins (in the top and bottom banks) as well as LVDS, LVPECL, 3.3-V PCML, HyperTransport technology, differential HSTL, and differential SSTL. Table 2–20 shows which I/O standards the enhanced PLL clock pins support. When in single-ended or differential mode, the two outputs operate off the same power supply. Both outputs use the same standards in single-ended mode to maintain performance. You can also use the external clock output pins as user output pins if external enhanced PLL clocking is not needed.

| Table 2–20. I/O Standards Supported for Enhanced PLL Pins (Part 1 of 2) |          |          |           |        |  |  |

|-------------------------------------------------------------------------|----------|----------|-----------|--------|--|--|

| L/O Ctondovd                                                            |          | Output   |           |        |  |  |

| I/O Standard                                                            | INCLK    | FBIN     | PLLENABLE | EXTCLK |  |  |

| LVTTL                                                                   | <b>✓</b> | <b>✓</b> | <b>✓</b>  | ✓      |  |  |

| LVCMOS                                                                  | <b>✓</b> | <b>✓</b> | ✓         | ✓      |  |  |

| 2.5 V                                                                   | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |

| 1.8 V                                                                   | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |

| 1.5 V                                                                   | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |

| 3.3-V PCI                                                               | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |

| 3.3-V PCI-X 1.0                                                         | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |

| LVPECL                                                                  | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |

| 3.3-V PCML                                                              | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |

| LVDS                                                                    | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |

| HyperTransport technology                                               | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |

| Differential HSTL                                                       | <b>✓</b> |          |           | ✓      |  |  |

| Differential SSTL                                                       |          |          |           | ✓      |  |  |

| 3.3-V GTL                                                               | <b>✓</b> | ✓        |           | ✓      |  |  |

| 3.3-V GTL+                                                              | <b>✓</b> | ✓        |           | ✓      |  |  |

| 1.5-V HSTL Class I                                                      | <b>✓</b> | ✓        |           | ✓      |  |  |

#### Clock Feedback

The following four feedback modes in Stratix device enhanced PLLs allow multiplication and/or phase and delay shifting:

- Zero delay buffer: The external clock output pin is phase-aligned with the clock input pin for zero delay. Altera recommends using the same I/O standard on the input clock and the output clocks for optimum performance.

- External feedback: The external feedback input pin, FBIN, is phase-aligned with the clock input, CLK, pin. Aligning these clocks allows you to remove clock delay and skew between devices. This mode is only possible for PLLs 5 and 6. PLLs 5 and 6 each support feedback for one of the dedicated external outputs, either one single-ended or one differential pair. In this mode, one *e* counter feeds back to the PLL FBIN input, becoming part of the feedback loop. Altera recommends using the same I/O standard on the input clock, the FBIN pin, and the output clocks for optimum performance.

- Normal mode: If an internal clock is used in this mode, it is phasealigned to the input clock pin. The external clock output pin will have a phase delay relative to the clock input pin if connected in this mode. You define which internal clock output from the PLL should be phase-aligned to the internal clock pin.

- No compensation: In this mode, the PLL will not compensate for any clock networks or external clock outputs.

#### Phase & Delay Shifting

Stratix device enhanced PLLs provide advanced programmable phase and clock delay shifting. These parameters are set in the Quartus II software.

#### Phase Delay

The Quartus II software automatically sets the phase taps and counter settings according to the phase shift entry. You enter a desired phase shift and the Quartus II software automatically sets the closest setting achievable. This type of phase shift is not reconfigurable during system operation. For phase shifting, enter a phase shift (in degrees or time units) for each PLL clock output port or for all outputs together in one shift. You can select phase-shifting values in time units with a resolution of 156.25 to 416.66 ps. This resolution is a function of frequency input and the multiplication and division factors (that is, it is a function of the VCO period), with the finest step being equal to an eighth (×0.125) of the VCO period. Each clock output counter can choose a different phase of the

The variation due to process, voltage, and temperature is about ±15% on the delay settings. PLL reconfiguration can control the clock delay shift elements, but not the VCO phase shift multiplexers, during system operation.

#### Spread-Spectrum Clocking

Stratix device enhanced PLLs use spread-spectrum technology to reduce electromagnetic interference generation from a system by distributing the energy over a broader frequency range. The enhanced PLL typically provides 0.5% down spread modulation using a triangular profile. The modulation frequency is programmable. Enabling spread-spectrum for a PLL affects all of its outputs.

#### Lock Detect

The lock output indicates that there is a stable clock output signal in phase with the reference clock. Without any additional circuitry, the lock signal may toggle as the PLL begins tracking the reference clock. You may need to gate the lock signal for use as a system control. The lock signal from the locked port can drive the logic array or an output pin.

Whenever the PLL loses lock (for example, inclk jitter, clock switchover, PLL reconfiguration, power supply noise, and so on), the PLL must be reset with the areset signal to guarantee correct phase relationship between the PLL output clocks. If the phase relationship between the input clock versus output clock, and between different output clocks from the PLL is not important in the design, then the PLL need not be reset.

See the *Stratix FPGA Errata Sheet* for more information on implementing the gated lock signal in a design.

#### Programmable Duty Cycle

The programmable duty cycle allows enhanced PLLs to generate clock outputs with a variable duty cycle. This feature is supported on each enhanced PLL post-scale counter (*g*0..*g*3, *l*0..*l*3, *e*0..*e*3). The duty cycle setting is achieved by a low and high time count setting for the post-scale dividers. The Quartus II software uses the frequency input and the required multiply or divide rate to determine the duty cycle choices.

#### Advanced Clear & Enable Control

There are several control signals for clearing and enabling PLLs and their outputs. You can use these signals to control PLL resynchronization and gate PLL output clocks for low-power applications.

Table 2–32 shows I/O standard support for each I/O bank.

| I/O Standard                      | Top & Bottom Banks<br>(3, 4, 7 & 8) | Left & Right Banks<br>(1, 2, 5 & 6) | Enhanced PLL Externa<br>Clock Output Banks<br>(9, 10, 11 & 12) |  |  |

|-----------------------------------|-------------------------------------|-------------------------------------|----------------------------------------------------------------|--|--|

| LVTTL                             | <b>✓</b>                            | <b>✓</b>                            | <b>✓</b>                                                       |  |  |

| LVCMOS                            | ✓                                   | <b>✓</b>                            | <b>✓</b>                                                       |  |  |

| 2.5 V                             | ✓                                   | ✓                                   | ✓                                                              |  |  |

| 1.8 V                             | ✓                                   | ✓                                   | ✓                                                              |  |  |

| 1.5 V                             | ✓                                   | <b>✓</b>                            | <b>✓</b>                                                       |  |  |

| 3.3-V PCI                         | <b>✓</b>                            |                                     | <b>✓</b>                                                       |  |  |

| 3.3-V PCI-X 1.0                   | <b>✓</b>                            |                                     | <b>✓</b>                                                       |  |  |

| LVPECL                            |                                     | <b>✓</b>                            | <b>✓</b>                                                       |  |  |

| 3.3-V PCML                        |                                     | ✓                                   | <b>✓</b>                                                       |  |  |

| LVDS                              |                                     | <b>✓</b>                            | <b>✓</b>                                                       |  |  |

| HyperTransport technology         |                                     | <b>✓</b>                            | <b>✓</b>                                                       |  |  |

| Differential HSTL (clock inputs)  | <b>✓</b>                            | <b>✓</b>                            |                                                                |  |  |

| Differential HSTL (clock outputs) |                                     |                                     | ✓                                                              |  |  |

| Differential SSTL (clock outputs) |                                     |                                     | ✓                                                              |  |  |

| 3.3-V GTL                         | ✓                                   |                                     | ✓                                                              |  |  |

| 3.3-V GTL+                        | ✓                                   | ✓                                   | <b>✓</b>                                                       |  |  |

| 1.5-V HSTL Class I                | ✓                                   | ✓                                   | ✓                                                              |  |  |

| 1.5-V HSTL Class II               | ✓                                   |                                     | ✓                                                              |  |  |

| 1.8-V HSTL Class I                | ✓                                   | ✓                                   | <b>✓</b>                                                       |  |  |

| 1.8-V HSTL Class II               | ✓                                   |                                     | ✓                                                              |  |  |

| SSTL-18 Class I                   | ✓                                   | ✓                                   | ✓                                                              |  |  |

| SSTL-18 Class II                  | ✓                                   |                                     | ✓                                                              |  |  |

| SSTL-2 Class I                    | ✓                                   | <b>✓</b>                            | <b>✓</b>                                                       |  |  |

| SSTL-2 Class II                   | ✓                                   | ✓                                   | <b>✓</b>                                                       |  |  |

| SSTL-3 Class I                    | <b>✓</b>                            | <b>✓</b>                            | <b>✓</b>                                                       |  |  |

Table 2–37 shows the number of channels that each fast PLL can clock in EP1S10, EP1S20, and EP1S25 devices. Tables 2–38 through Table 2–41 show this information for EP1S30, EP1S40, EP1S60, and EP1S80 devices.

| Table 2- | Table 2-37. EP1S10, EP1S20 & EP1S25 Device Differential Channels (Part 1 of 2) Note (1) |                 |          |                 |       |                  |       |       |  |

|----------|-----------------------------------------------------------------------------------------|-----------------|----------|-----------------|-------|------------------|-------|-------|--|

|          |                                                                                         | Transmitter/    | Total    | otal Maximum    |       | Center Fast PLLs |       |       |  |

| Device   | Package                                                                                 | Receiver        | Channels | Speed<br>(Mbps) | PLL 1 | PLL 2            | PLL 3 | PLL 4 |  |

| EP1S10   | 484-pin FineLine BGA                                                                    | Transmitter (2) | 20       | 840 (4)         | 5     | 5                | 5     | 5     |  |

|          |                                                                                         |                 |          | 840 (3)         | 10    | 10               | 10    | 10    |  |

|          |                                                                                         | Receiver        | 20       | 840 (4)         | 5     | 5                | 5     | 5     |  |

|          |                                                                                         |                 |          | 840 (3)         | 10    | 10               | 10    | 10    |  |

|          | 672-pin FineLine BGA                                                                    | Transmitter (2) | 36       | 624 (4)         | 9     | 9                | 9     | 9     |  |

|          | 672-pin BGA                                                                             |                 |          | 624 (3)         | 18    | 18               | 18    | 18    |  |

|          |                                                                                         | Receiver        | 36       | 624 (4)         | 9     | 9                | 9     | 9     |  |

|          |                                                                                         |                 |          | 624 (3)         | 18    | 18               | 18    | 18    |  |

|          | 780-pin FineLine BGA                                                                    | Transmitter (2) | ļ .      | 840 (4)         | 11    | 11               | 11    | 11    |  |

|          |                                                                                         |                 |          | 840 (3)         | 22    | 22               | 22    | 22    |  |

|          |                                                                                         | Receiver        | 44       | 840 (4)         | 11    | 11               | 11    | 11    |  |

|          |                                                                                         |                 |          | 840 (3)         | 22    | 22               | 22    | 22    |  |

| EP1S20   | 484-pin FineLine BGA                                                                    | Transmitter (2) | 24       | 840 (4)         | 6     | 6                | 6     | 6     |  |

|          |                                                                                         |                 |          | 840 (3)         | 12    | 12               | 12    | 12    |  |

|          |                                                                                         | Receiver        | 20       | 840 (4)         | 5     | 5                | 5     | 5     |  |

|          |                                                                                         |                 |          | 840 (3)         | 10    | 10               | 10    | 10    |  |

|          | 672-pin FineLine BGA                                                                    | Transmitter (2) | 48       | 624 (4)         | 12    | 12               | 12    | 12    |  |

|          | 672-pin BGA                                                                             |                 |          | 624 (3)         | 24    | 24               | 24    | 24    |  |

|          |                                                                                         | Receiver        | 50       | 624 (4)         | 13    | 12               | 12    | 13    |  |

|          |                                                                                         |                 |          | 624 (3)         | 25    | 25               | 25    | 25    |  |

|          | 780-pin FineLine BGA                                                                    | Transmitter (2) | 66       | 840 (4)         | 17    | 16               | 16    | 17    |  |

|          |                                                                                         |                 |          | 840 (3)         | 33    | 33               | 33    | 33    |  |

|          |                                                                                         | Receiver        | 66       | 840 (4)         | 17    | 16               | 16    | 17    |  |

|          |                                                                                         |                 |          | 840 (3)         | 33    | 33               | 33    | 33    |  |

configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power-up, and before and during configuration. Together, the configuration and initialization processes are called command mode. Normal device operation is called user mode.

SRAM configuration elements allow Stratix devices to be reconfigured incircuit by loading new configuration data into the device. With real-time reconfiguration, the device is forced into command mode with a device pin. The configuration process loads different configuration data, reinitializes the device, and resumes user-mode operation. You can perform in-field upgrades by distributing new configuration files either within the system or remotely.

PORSEL is a dedicated input pin used to select POR delay times of 2 ms or 100 ms during power-up. When the PORSEL pin is connected to ground, the POR time is 100 ms; when the PORSEL pin is connected to  $V_{\rm CC}$ , the POR time is 2 ms.

The nio\_pullup pin enables a built-in weak pull-up resistor to pull all user I/O pins to  $V_{CCIO}$  before and during device configuration. If nio\_pullup is connected to  $V_{CC}$  during configuration, the weak pull-ups on all user I/O pins are disabled. If connected to ground, the pull-ups are enabled during configuration. The nio\_pullup pin can be pulled to 1.5, 1.8, 2.5, or 3.3 V for a logic level high.

VCCSEL is a dedicated input that is used to choose whether all dedicated configuration and JTAG input pins can accept 1.5 V/1.8 V or 2.5 V/3.3 V during configuration. A logic low sets 3.3 V/2.5 V, and a logic high sets 1.8 V/1.5 V. VCCSEL affects the following pins: TDI, TMS, TCK, TRST, MSEL0, MSEL1, MSEL2, nCONFIG, nCE, DCLK, PLL\_ENA, CONF\_DONE, nSTATUS. The VCCSEL pin can be pulled to 1.5, 1.8, 2.5, or 3.3 V for a logic level high.

The VCCSEL signal does not control the dual-purpose configuration pins such as the DATA [7..0] and PPA pins (nws, nrs, cs, nrcs, and RDYnbsy). During configuration, these dual-purpose pins will drive out voltage levels corresponding to the  $V_{\rm CCIO}$  supply voltage that powers the I/O bank containing the pin. After configuration, the dual-purpose pins use I/O standards specified in the user design.

TDO and nCEO drive out at the same voltages as the  $V_{CCIO}$  supply that powers the I/O bank containing the pin. Users must select the  $V_{CCIO}$  supply for bank containing TDO accordingly. For example, when using the ByteBlaster MV cable, the  $V_{CCIO}$  for the bank containing TDO must be powered up at 3.3 V.

#### **Configuring Stratix FPGAs with JRunner**

JRunner is a software driver that configures Altera FPGAs, including Stratix FPGAs, through the ByteBlaster II or ByteBlasterMV cables in JTAG mode. The programming input file supported is in Raw Binary File (.rbf) format. JRunner also requires a Chain Description File (.cdf) generated by the Quartus II software. JRunner is targeted for embedded JTAG configuration. The source code is developed for the Windows NT operating system (OS), but can be customized to run on other platforms. For more information on the JRunner software driver, see the JRunner Software Driver: An Embedded Solution to the JTAG Configuration White Paper and the source files on the Altera web site (www.altera.com).

#### **Configuration Schemes**

You can load the configuration data for a Stratix device with one of five configuration schemes (see Table 3–5), chosen on the basis of the target application. You can use a configuration device, intelligent controller, or the JTAG port to configure a Stratix device. A configuration device can automatically configure a Stratix device at system power-up.

Multiple Stratix devices can be configured in any of five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.

| Table 3–5. Data Sources for Configuration |                                                                                                                     |  |  |  |  |  |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Configuration Scheme                      | Data Source                                                                                                         |  |  |  |  |  |

| Configuration device                      | Enhanced or EPC2 configuration device                                                                               |  |  |  |  |  |

| Passive serial (PS)                       | MasterBlaster, ByteBlasterMV, or ByteBlaster II download cable or serial data source                                |  |  |  |  |  |

| Passive parallel asynchronous (PPA)       | Parallel data source                                                                                                |  |  |  |  |  |

| Fast passive parallel                     | Parallel data source                                                                                                |  |  |  |  |  |

| JTAG                                      | MasterBlaster, ByteBlasterMV, or ByteBlaster II download cable, a microprocessor with a Jam or JBC file, or JRunner |  |  |  |  |  |

## **Partial Reconfiguration**

The enhanced PLLs within the Stratix device family support partial reconfiguration of their multiply, divide, and time delay settings without reconfiguring the entire device. You can use either serial data from the logic array or regular I/O pins to program the PLL's counter settings in a serial chain. This option provides considerable flexibility for frequency

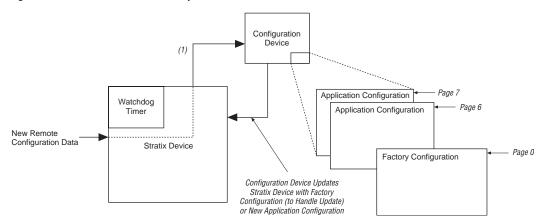

Figure 3-2. Stratix Device Remote Update

#### Note to Figure 3-2:

(1) When the Stratix device is configured with the factory configuration, it can handle update data from EPC16, EPC8, or EPC4 configuration device pages and point to the next page in the configuration device.

| Table 4–43. Routing Delay Internal Timing Microparameter Descriptions (Part 2 of 2) |                                                                                                                                                |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Symbol Parameter                                                                    |                                                                                                                                                |  |  |  |  |  |  |

| t <sub>C4</sub>                                                                     | Delay for a C4 line with average loading; covers a distance of four LAB rows.                                                                  |  |  |  |  |  |  |

| t <sub>C8</sub>                                                                     | Delay for a C8 line with average loading; covers a distance of eight LAB rows.                                                                 |  |  |  |  |  |  |

| t <sub>C16</sub>                                                                    | Delay for a C16 line with average loading; covers a distance of 16 LAB rows.                                                                   |  |  |  |  |  |  |

| t <sub>LOCAL</sub>                                                                  | Local interconnect delay, for connections within a LAB, and for the final routing hop of connections to LABs, DSP blocks, RAM blocks and I/Os. |  |  |  |  |  |  |

| Table 4–44. LE Internal Timing Microparameters |      |     |      |     |      |     |      |     |      |

|------------------------------------------------|------|-----|------|-----|------|-----|------|-----|------|

| Parameter                                      | -    | -5  |      | -6  |      | -7  |      | -8  |      |

|                                                | Min  | Max | Min  | Max | Min  | Max | Min  | Max | Unit |

| t <sub>SU</sub>                                | 10   |     | 10   |     | 11   |     | 13   |     | ps   |

| t <sub>H</sub>                                 | 100  |     | 100  |     | 114  |     | 135  |     | ps   |

| t <sub>CO</sub>                                |      | 156 |      | 176 |      | 202 |      | 238 | ps   |

| t <sub>LUT</sub>                               |      | 366 |      | 459 |      | 527 |      | 621 | ps   |

| t <sub>CLR</sub>                               | 100  |     | 100  |     | 114  |     | 135  |     | ps   |

| t <sub>PRE</sub>                               | 100  |     | 100  |     | 114  |     | 135  |     | ps   |

| t <sub>CLKHL</sub>                             | 1000 |     | 1111 |     | 1190 |     | 1400 |     | ps   |

| Table 4–45. IOE Internal TSU Microparameter by Device Density (Part 1 of 2) |                   |     |     |     |     |     |     |     |     |    |

|-----------------------------------------------------------------------------|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|----|

|                                                                             | Cumbal            | -   | -5  |     | -6  |     | -7  |     | -8  |    |

| Device                                                                      | Symbol            | Min | Max | Min | Max | Min | Max | Min | Max |    |

| EP1S10                                                                      | t <sub>SU_R</sub> | 76  |     | 80  |     | 80  |     | 80  |     | ps |

|                                                                             | t <sub>SU_C</sub> | 176 |     | 80  |     | 80  |     | 80  |     | ps |

| EP1S20                                                                      | t <sub>SU_R</sub> | 76  |     | 80  |     | 80  |     | 80  |     | ps |

|                                                                             | t <sub>SU_C</sub> | 76  |     | 80  |     | 80  |     | 80  |     | ps |

| EP1S25                                                                      | t <sub>SU_R</sub> | 276 |     | 280 |     | 280 |     | 280 |     | ps |

|                                                                             | t <sub>SU_C</sub> | 276 |     | 280 |     | 280 |     | 280 |     | ps |

| EP1S30                                                                      | t <sub>SU_R</sub> | 76  |     | 80  |     | 80  |     | 80  |     | ps |

|                                                                             | t <sub>SU_C</sub> | 176 |     | 180 |     | 180 |     | 180 |     | ps |

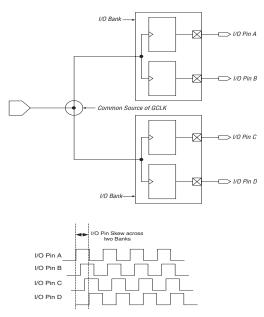

Figure 4–6 shows the case where four IOE registers are located in two different I/O banks.

Figure 4-6. I/O Skew Across Two I/O Banks

Table 4–97 defines the timing parameters used to define the timing for horizontal I/O pins (side banks 1, 2, 5, 6) and vertical I/O pins (top and bottom banks 3, 4, 7, 8). The timing parameters define the skew within an I/O bank, across two neighboring I/O banks on the same side of the device, across all horizontal I/O banks, across all vertical I/O banks, and the skew for the overall device.

| Table 4–97. Output Pin Timing Skew Definitions (Part 1 of 2) |                                                                |  |  |  |  |  |

|--------------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|--|

| Symbol Definition                                            |                                                                |  |  |  |  |  |

| t <sub>SB_HIO</sub>                                          | Row I/O (HIO) within one I/O bank (1)                          |  |  |  |  |  |

| t <sub>SB_VIO</sub>                                          | Column I/O (VIO) within one I/O bank (1)                       |  |  |  |  |  |

| t <sub>SS_HIO</sub>                                          | Row I/O (HIO) same side of the device, across two banks (2)    |  |  |  |  |  |

| t <sub>SS_VIO</sub>                                          | Column I/O (VIO) same side of the device, across two banks (2) |  |  |  |  |  |

Table 4–116. Stratix Maximum Input Clock Rate for CLK[1, 3, 8, 10] Pins in Flip-Chip Packages

| I/O Standard                  | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------|-------------------|-------------------|-------------------|-------------------|------|

| LVTTL                         | 422               | 422               | 390               | 390               | MHz  |

| 2.5 V                         | 422               | 422               | 390               | 390               | MHz  |

| 1.8 V                         | 422               | 422               | 390               | 390               | MHz  |

| 1.5 V                         | 422               | 422               | 390               | 390               | MHz  |

| LVCMOS                        | 422               | 422               | 390               | 390               | MHz  |

| GTL+                          | 300               | 250               | 200               | 200               | MHz  |

| SSTL-3 Class I                | 400               | 350               | 300               | 300               | MHz  |

| SSTL-3 Class II               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-2 Class I                | 400               | 350               | 300               | 300               | MHz  |

| SSTL-2 Class II               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-18 Class I               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-18 Class II              | 400               | 350               | 300               | 300               | MHz  |

| 1.5-V HSTL Class I            | 400               | 350               | 300               | 300               | MHz  |

| 1.8-V HSTL Class I            | 400               | 350               | 300               | 300               | MHz  |

| СТТ                           | 300               | 250               | 200               | 200               | MHz  |

| Differential 1.5-V HSTL<br>C1 | 400               | 350               | 300               | 300               | MHz  |

| LVPECL (1)                    | 645               | 645               | 640               | 640               | MHz  |

| PCML (1)                      | 300               | 275               | 275               | 275               | MHz  |

| LVDS (1)                      | 645               | 645               | 640               | 640               | MHz  |

| HyperTransport technology (1) | 500               | 500               | 450               | 450               | MHz  |

Table 4–117. Stratix Maximum Input Clock Rate for CLK[7..4] & CLK[15..12] Pins in Wire-Bond Packages (Part 1 of 2)

| I/O Standard | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|--------------|-------------------|-------------------|-------------------|------|

| LVTTL        | 422               | 390               | 390               | MHz  |

| 2.5 V        | 422               | 390               | 390               | MHz  |

| 1.8 V        | 422               | 390               | 390               | MHz  |

| 1.5 V        | 422               | 390               | 390               | MHz  |

| LVCMOS       | 422               | 390               | 390               | MHz  |

| GTL          | 250               | 200               | 200               | MHz  |

# High-Speed I/O Specification

${\it Table 4-124 provides high-speed timing specifications definitions.}$

| Table 4–124. High-Speed Timing Specifications & Terminology |                                                                                                                                                                                                                   |  |  |  |  |  |  |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| High-Speed Timing Specification                             | Terminology                                                                                                                                                                                                       |  |  |  |  |  |  |

| tc                                                          | High-speed receiver/transmitter input and output clock period.                                                                                                                                                    |  |  |  |  |  |  |

| f <sub>HSCLK</sub>                                          | High-speed receiver/transmitter input and output clock frequency.                                                                                                                                                 |  |  |  |  |  |  |

| t <sub>RISE</sub>                                           | Low-to-high transmission time.                                                                                                                                                                                    |  |  |  |  |  |  |

| t <sub>FALL</sub>                                           | High-to-low transmission time.                                                                                                                                                                                    |  |  |  |  |  |  |

| Timing unit interval (TUI)                                  | The timing budget allowed for skew, propagation delays, and data sampling window. (TUI = $1/(Receiver\ Input\ Clock\ Frequency \times Multiplication\ Factor) = t_C/w)$ .                                         |  |  |  |  |  |  |

| f <sub>HSDR</sub>                                           | Maximum LVDS data transfer rate (f <sub>HSDR</sub> = 1/TUI).                                                                                                                                                      |  |  |  |  |  |  |

| Channel-to-channel skew (TCCS)                              | The timing difference between the fastest and slowest output edges, including $t_{\text{CO}}$ variation and clock skew. The clock is included in the TCCS measurement.                                            |  |  |  |  |  |  |

| Sampling window (SW)                                        | The period of time during which the data must be valid to be captured correctly. The setup and hold times determine the ideal strobe position within the sampling window. $SW = t_{SW} \ (max) - t_{SW} \ (min).$ |  |  |  |  |  |  |

| Input jitter (peak-to-peak)                                 | Peak-to-peak input jitter on high-speed PLLs.                                                                                                                                                                     |  |  |  |  |  |  |

| Output jitter (peak-to-peak)                                | Peak-to-peak output jitter on high-speed PLLs.                                                                                                                                                                    |  |  |  |  |  |  |

| t <sub>DUTY</sub>                                           | Duty cycle on high-speed transmitter output clock.                                                                                                                                                                |  |  |  |  |  |  |

| t <sub>LOCK</sub>                                           | Lock time for high-speed transmitter and receiver PLLs.                                                                                                                                                           |  |  |  |  |  |  |

| J                                                           | Deserialization factor (width of internal data bus).                                                                                                                                                              |  |  |  |  |  |  |

| W                                                           | PLL multiplication factor.                                                                                                                                                                                        |  |  |  |  |  |  |

Tables 4–125 and 4–126 show the high-speed I/O timing for Stratix devices.

| Symbol                                                                                                                                         | Conditions                         | -5 Speed Grade |     | -6 Speed Grade |     |     | -7 Speed Grade |     |     | -8 Speed Grade |     |     | Unit  |       |

|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|-----|----------------|-----|-----|----------------|-----|-----|----------------|-----|-----|-------|-------|

|                                                                                                                                                |                                    | Min            | Тур | Max            | Min | Тур | Max            | Min | Тур | Max            | Min | Тур | Max   | UIIII |

| f <sub>HSCLK</sub> (Clock<br>frequency)<br>(LVDS,<br>LVPECL,<br>HyperTransport<br>technology)<br>f <sub>HSCLK</sub> = f <sub>HSDR</sub> /<br>W | W = 4 to 30<br>(Serdes used)       | 10             |     | 210            | 10  |     | 210            | 10  |     | 156            | 10  |     | 115.5 | MHz   |

|                                                                                                                                                | W = 2 (Serdes bypass)              | 50             |     | 231            | 50  |     | 231            | 50  |     | 231            | 50  |     | 231   | MHz   |

|                                                                                                                                                | W = 2 (Serdes used)                | 150            |     | 420            | 150 |     | 420            | 150 |     | 312            | 150 |     | 231   | MHz   |

|                                                                                                                                                | W = 1 (Serdes bypass)              | 100            |     | 462            | 100 |     | 462            | 100 |     | 462            | 100 |     | 462   | MHz   |

|                                                                                                                                                | W = 1 (Serdes used)                | 300            |     | 717            | 300 |     | 717            | 300 |     | 624            | 300 |     | 462   | MHz   |

| f <sub>HSDR</sub> Device<br>operation<br>(LVDS,<br>LVPECL,<br>HyperTransport<br>technology)                                                    | J = 10                             | 300            |     | 840            | 300 |     | 840            | 300 |     | 640            | 300 |     | 462   | Mbps  |

|                                                                                                                                                | J = 8                              | 300            |     | 840            | 300 |     | 840            | 300 |     | 640            | 300 |     | 462   | Mbps  |

|                                                                                                                                                | J = 7                              | 300            |     | 840            | 300 |     | 840            | 300 |     | 640            | 300 |     | 462   | Mbps  |

|                                                                                                                                                | J = 4                              | 300            |     | 840            | 300 |     | 840            | 300 |     | 640            | 300 |     | 462   | Mbps  |

|                                                                                                                                                | J = 2                              | 100            |     | 462            | 100 |     | 462            | 100 |     | 640            | 100 |     | 462   | Mbps  |

|                                                                                                                                                | J = 1 (LVDS<br>and LVPECL<br>only) | 100            |     | 462            | 100 |     | 462            | 100 |     | 640            | 100 |     | 462   | Mbps  |

| Table 4–129. Enhanced PLL Specifications for -7 Speed Grade (Part 2 of 2) |                                                                                                                   |     |     |                                                            |              |  |  |  |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|------------------------------------------------------------|--------------|--|--|--|

| Symbol                                                                    | Parameter                                                                                                         | Min | Тур | Max                                                        | Unit         |  |  |  |

| t <sub>OUTDUTY</sub>                                                      | Duty cycle for external clock output (when set to 50%)                                                            | 45  |     | 55                                                         | %            |  |  |  |

| t <sub>JITTER</sub>                                                       | Period jitter for external clock output (6)                                                                       |     |     | ±100 ps for >200-MHz outclk<br>±20 mUI for <200-MHz outclk | ps or<br>mUI |  |  |  |

| t <sub>CONFIG5,6</sub>                                                    | Time required to reconfigure the scan chains for PLLs 5 and 6                                                     |     |     | 289/f <sub>SCANCLK</sub>                                   |              |  |  |  |

| t <sub>CONFIG11,12</sub>                                                  | Time required to reconfigure the scan chains for PLLs 11 and 12                                                   |     |     | 193/f <sub>SCANCLK</sub>                                   |              |  |  |  |

| t <sub>SCANCLK</sub>                                                      | scanclk frequency (5)                                                                                             |     |     | 22                                                         | MHz          |  |  |  |

| t <sub>DLOCK</sub>                                                        | Time required to lock dynamically (after switchover or reconfiguring any non-post-scale counters/delays) (7) (11) | (9) |     | 100                                                        | μs           |  |  |  |

| t <sub>LOCK</sub>                                                         | Time required to lock from end of device configuration (11)                                                       | 10  |     | 400                                                        | μs           |  |  |  |

| f <sub>VCO</sub>                                                          | PLL internal VCO operating range                                                                                  | 300 |     | 600 (8)                                                    | MHz          |  |  |  |

| t <sub>LSKEW</sub>                                                        | Clock skew between two external clock outputs driven by the same counter                                          |     | ±50 |                                                            | ps           |  |  |  |

| t <sub>SKEW</sub>                                                         | Clock skew between two external clock outputs driven by the different counters with the same settings             |     | ±75 |                                                            | ps           |  |  |  |

| f <sub>SS</sub>                                                           | Spread spectrum modulation frequency                                                                              | 30  |     | 150                                                        | kHz          |  |  |  |

| % spread                                                                  | Percentage spread for spread spectrum frequency (10)                                                              | 0.5 |     | 0.6                                                        | %            |  |  |  |

| t <sub>ARESET</sub>                                                       | Minimum pulse width on areset signal                                                                              | 10  |     |                                                            | ns           |  |  |  |

| Table 4–130. Enhanced PLL Specifications for -8 Speed Grade (Part 1 of 3) |                                          |               |     |          |      |  |  |  |

|---------------------------------------------------------------------------|------------------------------------------|---------------|-----|----------|------|--|--|--|

| Symbol                                                                    | Parameter                                | Min           | Тур | Max      | Unit |  |  |  |

| f <sub>IN</sub>                                                           | Input clock frequency                    | 3<br>(1), (2) |     | 480      | MHz  |  |  |  |

| f <sub>INPFD</sub>                                                        | Input frequency to PFD                   | 3             |     | 420      | MHz  |  |  |  |

| f <sub>INDUTY</sub>                                                       | Input clock duty cycle                   | 40            |     | 60       | %    |  |  |  |

| f <sub>EINDUTY</sub>                                                      | External feedback clock input duty cycle | 40            |     | 60       | %    |  |  |  |

| t <sub>INJITTER</sub>                                                     | Input clock period jitter                |               |     | ±200 (3) | ps   |  |  |  |

## 5. Reference & Ordering Information

\$51005-2.1

## Software

Stratix® devices are supported by the Altera® Quartus® II design software, which provides a comprehensive environment for system-on-a-programmable-chip (SOPC) design. The Quartus II software includes HDL and schematic design entry, compilation and logic synthesis, full simulation and advanced timing analysis, SignalTap® II logic analyzer, and device configuration. See the *Design Software Selector Guide* for more details on the Quartus II software features.

The Quartus II software supports the Windows XP/2000/NT/98, Sun Solaris, Linux Red Hat v7.1 and HP-UX operating systems. It also supports seamless integration with industry-leading EDA tools through the NativeLink® interface.

## **Device Pin-Outs**

Stratix device pin-outs can be found on the Altera web site (www.altera.com).

## Ordering Information

Figure 5–1 describes the ordering codes for Stratix devices. For more information on a specific package, see the *Package Information for Stratix Devices* chapter.