Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 1846                                                    |

| Number of Logic Elements/Cells | 18460                                                   |

| Total RAM Bits                 | 1669248                                                 |

| Number of I/O                  | 361                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                         |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                      |

| Package / Case                 | 484-BBGA, FCBGA                                         |

| Supplier Device Package        | 484-FBGA (23x23)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s20f484i6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

vi Altera Corporation

| Chapter | Date/Version         | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2       | July 2005 v3.2       | <ul> <li>Added "Clear Signals" section.</li> <li>Updated "Power Sequencing &amp; Hot Socketing" section.</li> <li>Format changes.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | September 2004, v3.1 | <ul> <li>Updated fast regional clock networks description on page 2–73.</li> <li>Deleted the word preliminary from the "specification for the maximum time to relock is 100 µs" on page 2–90.</li> <li>Added information about differential SSTL and HSTL outputs in "External Clock Outputs" on page 2–92.</li> <li>Updated notes in Figure 2–55 on page 2–93.</li> <li>Added information about <i>m</i> counter to "Clock Multiplication &amp; Division" on page 2–101.</li> <li>Updated Note 1 in Table 2–58 on page 2–101.</li> <li>Updated description of "Clock Multiplication &amp; Division" on page 2–88.</li> <li>Updated Table 2–22 on page 2–102.</li> <li>Added references to AN 349 and AN 329 to "External RAM Interfacing" on page 2–115.</li> <li>Table 2–25 on page 2–116: updated the table, updated Notes 3 and 4. Notes 4, 5, and 6, are now Notes 5, 6, and 7, respectively.</li> <li>Updated Table 2–26 on page 2–117.</li> <li>Added information about PCI Compliance to page 2–120.</li> <li>Table 2–32 on page 2–126: updated the table and deleted Note 1.</li> <li>Updated reference to device pin-outs now being available on the web on page 2–130.</li> <li>Added Notes 4 and 5 to Table 2–36 on page 2–130.</li> <li>Updated Note 3 in Table 2–37 on page 2–131.</li> <li>Updated Note 5 in Table 2–41 on page 2–135.</li> </ul> |

|         | April 2004, v3.0     | <ul> <li>Added note 3 to rows 11 and 12 in Table 2–18.</li> <li>Deleted "Stratix and Stratix GX Device PLL Availability" table.</li> <li>Added I/O standards row in Table 2–28 that support max and min strength.</li> <li>Row clk [1,3,8,10] was removed from Table 2–30.</li> <li>Added checkmarks in Enhanced column for LVPECL, 3.3-V PCML, LVDS, and HyperTransport technology rows in Table 2–32.</li> <li>Removed the Left and Right I/O Banks row in Table 2–34.</li> <li>Changed RCLK values in Figures 2–50 and 2–51.</li> <li>External RAM Interfacing section replaced.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | November 2003, v2.2  | <ul> <li>Added 672-pin BGA package information in Table 2–37.</li> <li>Removed support for series and parallel on-chip termination.</li> <li>Termination Technology renamed differential on-chip termination.</li> <li>Updated the number of channels per PLL in Tables 2-38 through 2-42.</li> <li>Updated Figures 2–65 and 2–67.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | October 2003, v2.1   | <ul> <li>Updated DDR I information.</li> <li>Updated Table 2–22.</li> <li>Added Tables 2–25, 2–29, 2–30, and 2–72.</li> <li>Updated Figures 2–59, 2–65, and 2–67.</li> <li>Updated the Lock Detect section.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Section I–2 Altera Corporation

Section I–8 Altera Corporation

C8 interconnects span eight LABs, M512, or M4K blocks up or down from a source LAB. Every LAB has its own set of C8 interconnects to drive either up or down. C8 interconnect connections between the LABs in a column are similar to the C4 connections shown in Figure 2–11 with the exception that they connect to eight LABs above and below. The C8 interconnects can drive and be driven by all types of architecture blocks similar to C4 interconnects. C8 interconnects can drive each other to extend their range as well as R8 interconnects for column-to-column connections. C8 interconnects are faster than two C4 interconnects.

C16 column interconnects span a length of 16 LABs and provide the fastest resource for long column connections between LABs, TriMatrix memory blocks, DSP blocks, and IOEs. C16 interconnects can cross M-RAM blocks and also drive to row and column interconnects at every fourth LAB. C16 interconnects drive LAB local interconnects via C4 and R4 interconnects and do not drive LAB local interconnects directly.

All embedded blocks communicate with the logic array similar to LAB-to-LAB interfaces. Each block (i.e., TriMatrix memory and DSP blocks) connects to row and column interconnects and has local interconnect regions driven by row and column interconnects. These blocks also have direct link interconnects for fast connections to and from a neighboring LAB. All blocks are fed by the row LAB clocks, labclk [7..0].

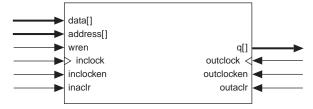

In addition to true dual-port memory, the memory blocks support simple dual-port and single-port RAM. Simple dual-port memory supports a simultaneous read and write and can either read old data before the write occurs or just read the don't care bits. Single-port memory supports non-simultaneous reads and writes, but the q[] port will output the data once it has been written to the memory (if the outputs are not registered) or after the next rising edge of the clock (if the outputs are registered). For more information, see Chapter 2, TriMatrix Embedded Memory Blocks in Stratix & Stratix GX Devices of the *Stratix Device Handbook, Volume 2*. Figure 2–13 shows these different RAM memory port configurations for TriMatrix memory.

Figure 2–13. Simple Dual-Port & Single-Port Memory Configurations

# data[] rdaddress[] wraddress[] rden wren q[] inclock outclock inclocken outclocken inaclr outaclr

### Single-Port Memory (1)

Simple Dual-Port Memory

Note to Figure 2-13:

Two single-port memory blocks can be implemented in a single M4K block as long as each of the two independent block sizes is equal to or less than half of the M4K block size.

The memory blocks also enable mixed-width data ports for reading and writing to the RAM ports in dual-port RAM configuration. For example, the memory block can be written in  $\times 1$  mode at port A and read out in  $\times 16$  mode from port B.

M512 RAM blocks can have different clocks on its inputs and outputs. The wren, datain, and write address registers are all clocked together from one of the two clocks feeding the block. The read address, rden, and output registers can be clocked by either of the two clocks driving the block. This allows the RAM block to operate in read/write or input/output clock modes. Only the output register can be bypassed. The eight labelk signals or local interconnect can drive the inclock, outclock, wren, rden, inclr, and outclr signals. Because of the advanced interconnect between the LAB and M512 RAM blocks, LEs can also control the wren and rden signals and the RAM clock, clock enable, and asynchronous clear signals. Figure 2–15 shows the M512 RAM block control signal generation logic.

The RAM blocks within Stratix devices have local interconnects to allow LEs and interconnects to drive into RAM blocks. The M512 RAM block local interconnect is driven by the R4, R8, C4, C8, and direct link interconnects from adjacent LABs. The M512 RAM blocks can communicate with LABs on either the left or right side through these row interconnects or with LAB columns on the left or right side with the column interconnects. Up to 10 direct link input connections to the M512 RAM block are possible from the left adjacent LABs and another 10 possible from the right adjacent LAB. M512 RAM outputs can also connect to left and right LABs through 10 direct link interconnects. The M512 RAM block has equal opportunity for access and performance to and from LABs on either its left or right side. Figure 2–16 shows the M512 RAM block to logic array interface.

| Table 2–9. M-RAM | Table 2–9. M-RAM Block Configurations (True Dual-Port) |          |          |          |  |  |  |  |  |  |

|------------------|--------------------------------------------------------|----------|----------|----------|--|--|--|--|--|--|

| Dovt A           | Port B                                                 |          |          |          |  |  |  |  |  |  |

| Port A           | 64K × 9                                                | 32K × 18 | 16K × 36 | 8K × 72  |  |  |  |  |  |  |

| 64K × 9          | <b>✓</b>                                               | ✓        | ✓        | ✓        |  |  |  |  |  |  |

| 32K × 18         | ✓                                                      | ✓        | ✓        | <b>✓</b> |  |  |  |  |  |  |

| 16K × 36         | <b>✓</b>                                               | ✓        | ✓        | ✓        |  |  |  |  |  |  |

| 8K × 72          | ✓                                                      | ✓        | ✓        | <b>✓</b> |  |  |  |  |  |  |

The read and write operation of the memory is controlled by the WREN signal, which sets the ports into either read or write modes. There is no separate read enable (RE) signal.

Writing into RAM is controlled by both the WREN and byte enable (byteena) signals for each port. The default value for the byteena signal is high, in which case writing is controlled only by the WREN signal. The byte enables are available for the ×18, ×36, and ×72 modes. In the ×144 simple dual-port mode, the two sets of byteena signals (byteena\_a and byteena\_b) are combined to form the necessary 16 byte enables. Tables 2–10 and 2–11 summarize the byte selection.

| Table 2–10. Byte | Table 2–10. Byte Enable for M-RAM Blocks Notes (1), (2) |            |            |  |  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------|------------|------------|--|--|--|--|--|--|--|--|

| byteena[30]      | datain ×18                                              | datain ×36 | datain ×72 |  |  |  |  |  |  |  |  |

| [0] = 1          | [80]                                                    | [80]       | [80]       |  |  |  |  |  |  |  |  |

| [1] = 1          | [179]                                                   | [179]      | [179]      |  |  |  |  |  |  |  |  |

| [2] = 1          | _                                                       | [2618]     | [2618]     |  |  |  |  |  |  |  |  |

| [3] = 1          | -                                                       | [3527]     | [3527]     |  |  |  |  |  |  |  |  |

| [4] = 1          | _                                                       | _          | [4436]     |  |  |  |  |  |  |  |  |

| [5] = 1          | _                                                       | _          | [5345]     |  |  |  |  |  |  |  |  |

| [6] = 1          | _                                                       | _          | [6254]     |  |  |  |  |  |  |  |  |

| [7] = 1          | _                                                       | _          | [7163]     |  |  |  |  |  |  |  |  |

blocks facing to the left, and another 10 possible from the right adjacent LABs for M-RAM blocks facing to the right. For column interfacing, every M-RAM column unit connects to the right and left column lines, allowing each M-RAM column unit to communicate directly with three columns of LABs. Figures 2–21 through 2–23 show the interface between the M-RAM block and the logic array.

## Control Signals

The fast PLL has the same lock output, pllenable input, and are set input control signals as the enhanced PLL.

If the input clock stops and causes the PLL to lose lock, then the PLL must be reset for correct phase shift operation.

For more information on high-speed differential I/O support, see "High-Speed Differential I/O Support" on page 2–130.

# I/O Structure

IOEs provide many features, including:

- Dedicated differential and single-ended I/O buffers

- 3.3-V, 64-bit, 66-MHz PCI compliance

- 3.3-V, 64-bit, 133-MHz PCI-X 1.0 compliance

- Joint Test Action Group (JTAG) boundary-scan test (BST) support

- Differential on-chip termination for LVDS I/O standard

- Programmable pull-up during configuration

- Output drive strength control

- Slew-rate control

- Tri-state buffers

- Bus-hold circuitry

- Programmable pull-up resistors

- Programmable input and output delays

- Open-drain outputs

- DQ and DQS I/O pins

- Double-data rate (DDR) Registers

The IOE in Stratix devices contains a bidirectional I/O buffer, six registers, and a latch for a complete embedded bidirectional single data rate or DDR transfer. Figure 2–59 shows the Stratix IOE structure. The IOE contains two input registers (plus a latch), two output registers, and two output enable registers. The design can use both input registers and the latch to capture DDR input and both output registers to drive DDR outputs. Additionally, the design can use the output enable (OE) register for fast clock-to-output enable timing. The negative edge-clocked OE register is used for DDR SDRAM interfacing. The Quartus II software automatically duplicates a single OE register that controls multiple output or bidirectional pins.

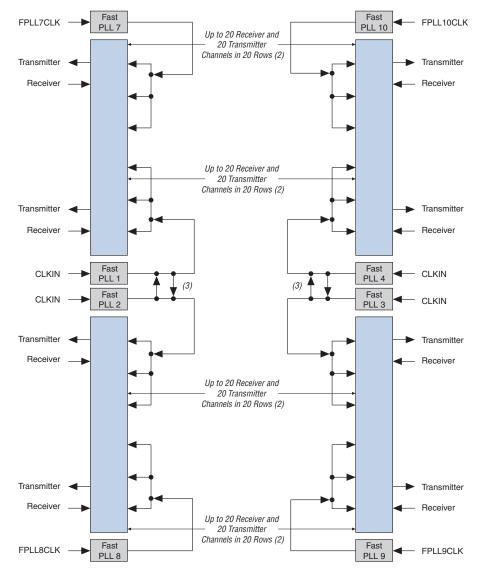

Table 2–37 shows the number of channels that each fast PLL can clock in EP1S10, EP1S20, and EP1S25 devices. Tables 2–38 through Table 2–41 show this information for EP1S30, EP1S40, EP1S60, and EP1S80 devices.

| Table 2- | 37. EP1\$10, EP1\$20 & I | EP1S25 Device l | Differential | Channels (      | Part 1 of        | <b>2)</b> Note ( | 1)    |       |  |

|----------|--------------------------|-----------------|--------------|-----------------|------------------|------------------|-------|-------|--|

|          |                          | Transmitter/    | Total        | Maximum         | Center Fast PLLs |                  |       |       |  |

| Device   | Package                  | Receiver        | Channels     | Speed<br>(Mbps) | PLL 1            | PLL 2            | PLL 3 | PLL 4 |  |

| EP1S10   | 484-pin FineLine BGA     | Transmitter (2) | 20           | 840 (4)         | 5                | 5                | 5     | 5     |  |

|          |                          |                 |              | 840 (3)         | 10               | 10               | 10    | 10    |  |

|          |                          | Receiver        | 20           | 840 (4)         | 5                | 5                | 5     | 5     |  |

|          |                          |                 |              | 840 (3)         | 10               | 10               | 10    | 10    |  |

|          | 672-pin FineLine BGA     | Transmitter (2) | 36           | 624 (4)         | 9                | 9                | 9     | 9     |  |

|          | 672-pin BGA              |                 |              | 624 (3)         | 18               | 18               | 18    | 18    |  |

|          |                          | Receiver        | 36           | 624 (4)         | 9                | 9                | 9     | 9     |  |

|          |                          |                 |              | 624 (3)         | 18               | 18               | 18    | 18    |  |

|          | 780-pin FineLine BGA     | Transmitter (2) | 44           | 840 (4)         | 11               | 11               | 11    | 11    |  |

|          |                          |                 |              | 840 (3)         | 22               | 22               | 22    | 22    |  |

|          |                          | Receiver        | 44           | 840 (4)         | 11               | 11               | 11    | 11    |  |

|          |                          |                 |              | 840 (3)         | 22               | 22               | 22    | 22    |  |

| EP1S20   | 484-pin FineLine BGA     | Transmitter (2) | +            | 840 (4)         | 6                | 6                | 6     | 6     |  |

|          |                          |                 |              | 840 (3)         | 12               | 12               | 12    | 12    |  |

|          |                          | Receiver        | 20           | 840 (4)         | 5                | 5                | 5     | 5     |  |

|          |                          |                 |              | 840 (3)         | 10               | 10               | 10    | 10    |  |

|          | 672-pin FineLine BGA     | Transmitter (2) | 48           | 624 (4)         | 12               | 12               | 12    | 12    |  |

|          | 672-pin BGA              |                 |              | 624 (3)         | 24               | 24               | 24    | 24    |  |

|          |                          | Receiver        | 50           | 624 (4)         | 13               | 12               | 12    | 13    |  |

|          |                          |                 |              | 624 (3)         | 25               | 25               | 25    | 25    |  |

|          | 780-pin FineLine BGA     | Transmitter (2) | 66           | 840 (4)         | 17               | 16               | 16    | 17    |  |

|          |                          |                 |              | 840 (3)         | 33               | 33               | 33    | 33    |  |

|          |                          | Receiver        | 66           | 840 (4)         | 17               | 16               | 16    | 17    |  |

|          |                          |                 |              | 840 (3)         | 33               | 33               | 33    | 33    |  |

|                       | Transmitter/    | Total                 | Maximum<br>Speed<br>(Mbps) | C          | Center Fast PLLs |            |            |            | Corner Fast PLLs (2), (3) |            |            |  |

|-----------------------|-----------------|-----------------------|----------------------------|------------|------------------|------------|------------|------------|---------------------------|------------|------------|--|

| Package               | Receiver        | Channels              |                            | PLL1       | PLL2             | PLL3       | PLL4       | PLL7       | PLL8                      | PLL9       | PLL10      |  |

| 1,508-pin<br>FineLine | Transmitter (4) | 80 (72)<br><i>(7)</i> | 840                        | 10<br>(10) | 10<br>(10)       | 10<br>(10) | 10<br>(10) | 20<br>(8)  | 20<br>(8)                 | 20 (8)     | 20 (8)     |  |

| BGA                   |                 |                       | 840 (5),(8)                | 20<br>(20) | 20<br>(20)       | 20<br>(20) | 20<br>(20) | 20<br>(8)  | 20<br>(8)                 | 20 (8)     | 20 (8)     |  |

|                       | Receiver        | 80 (56)<br>(7)        | 840                        | 20         | 20               | 20         | 20         | 10<br>(14) | 10<br>(14)                | 10<br>(14) | 10<br>(14) |  |

|                       |                 |                       | 840 (5),(8)                | 40         | 40               | 40         | 40         | 10<br>(14) | 10<br>(14)                | 10<br>(14) | 10<br>(14) |  |

#### Notes to Tables 2–38 through 2–41:

- (1) The first row for each transmitter or receiver reports the number of channels driven directly by the PLL. The second row below it shows the maximum channels a PLL can drive if cross bank channels are used from the adjacent center PLL. For example, in the 780-pin FineLine BGA EP1S30 device, PLL 1 can drive a maximum of 18 transmitter channels at 840 Mbps or a maximum of 35 transmitter channels at 840 Mbps. The Quartus II software may also merge transmitter and receiver PLLs when a receiver is driving a transmitter. In this case, one fast PLL can drive both the maximum numbers of receiver and transmitter channels.

- (2) Some of the channels accessible by the center fast PLL and the channels accessible by the corner fast PLL overlap. Therefore, the total number of channels is not the addition of the number of channels accessible by PLLs 1, 2, 3, and 4 with the number of channels accessible by PLLs 7, 8, 9, and 10. For more information on which channels overlap, see the Stratix device pin-outs at www.altera.com.

- (3) The corner fast PLLs in this device support a data rate of 840 Mbps for channels labeled "high" speed in the device pin-outs at www.altera.com.

- (4) The numbers of channels listed include the transmitter clock output (tx\_outclock) channel. An extra data channel can be used if a DDR clock is needed.

- (5) These channels span across two I/O banks per side of the device. When a center PLL clocks channels in the opposite bank on the same side of the device it is called cross-bank PLL support. Both center PLLs can clock cross-bank channels simultaneously if say PLL\_1 is clocking all receiver channels and PLL\_2 is clocking all transmitter channels. You cannot have two adjacent PLLs simultaneously clocking cross-bank receiver channels or two adjacent PLLs simultaneously clocking transmitter channels. Cross-bank allows for all receiver channels on one side of the device to be clocked on one clock while all transmitter channels on the device are clocked on the other center PLL. Crossbank PLLs are supported at full-speed, 840 Mbps. For wire-bond devices, the full-speed is 624 Mbps.

- (6) PLLs 7, 8, 9, and 10 are not available in this device.

- (7) The number in parentheses is the number of slow-speed channels, guaranteed to operate at up to 462 Mbps. These channels are independent of the high-speed differential channels. For the location of these channels, see the device pin-outs at www.altera.com.

- (8) See the Stratix device pin-outs at www.altera.com. Channels marked "high" speed are 840 MBps and "low" speed channels are 462 MBps.

The high-speed differential I/O circuitry supports the following high speed I/O interconnect standards and applications:

- UTOPIA IV

- SPI-4 Phase 2 (POS-PHY Level 4)

- SFI-4

- 10G Ethernet XSBI

Figure 2-75. Fast PLL & Channel Layout in the EP1S30 to EP1S80 Devices Note (1)

#### Notes to Figure 2-75:

- (1) Wire-bond packages support up to 624 Mbps.

- (2) See Table 2–38 through 2–41 for the number of channels each device supports.

- (3) There is a multiplexer here to select the PLL clock source. If a PLL uses this multiplexer to clock channels outside of its bank quadrant, those clocked channels support up to 840 Mbps for "high" speed channels and 462 Mbps for "low" speed channels as labeled in the device pin-outs at www.altera.com.

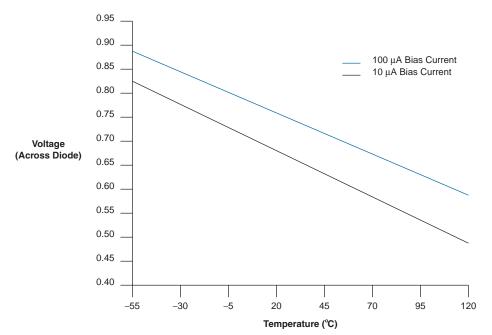

The temperature-sensing diode works for the entire operating range shown in Figure 3–6.

Figure 3-6. Temperature vs. Temperature-Sensing Diode Voltage

| Table 4–41. M4<br>2 of 2) | IK Block Internal Timing Microparameter Descriptions (Part                                                                                                                                                                                                                                                                                               |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                    | Parameter                                                                                                                                                                                                                                                                                                                                                |

| t <sub>M4KDATAAH</sub>    | A port data hold time after clock                                                                                                                                                                                                                                                                                                                        |

| t <sub>M4KADDRASU</sub>   | A port address setup time before clock                                                                                                                                                                                                                                                                                                                   |

| t <sub>M4KADDRAH</sub>    | A port address hold time after clock                                                                                                                                                                                                                                                                                                                     |

| t <sub>M4KDATABSU</sub>   | B port data setup time before clock                                                                                                                                                                                                                                                                                                                      |

| t <sub>M4KDATABH</sub>    | B port data hold time after clock                                                                                                                                                                                                                                                                                                                        |

| t <sub>M4KADDRBSU</sub>   | B port address setup time before clock                                                                                                                                                                                                                                                                                                                   |

| t <sub>M4KADDRBH</sub>    | B port address hold time after clock                                                                                                                                                                                                                                                                                                                     |

| t <sub>M4KDATACO1</sub>   | Clock-to-output delay when using output registers                                                                                                                                                                                                                                                                                                        |

| t <sub>M4KDATACO2</sub>   | Clock-to-output delay without output registers                                                                                                                                                                                                                                                                                                           |

| t <sub>M4KCLKHL</sub>     | Register minimum clock high or low time. This is a limit on the min time for the clock on the registers in these blocks. The actual performance is dependent upon the internal point-to-point delays in the blocks and may give slower performance as shown inTable 4–36 on page 4–20 and as reported by the timing analyzer in the Quartus II software. |

Minimum clear pulse width

$t_{\mathsf{M4KCLR}}$

| Table 4–42. M-<br>Descriptions (F | RAM Block Internal Timing Microparameter<br>Part 1 of 2) |

|-----------------------------------|----------------------------------------------------------|

| Symbol                            | Parameter                                                |

| t <sub>MRAMRC</sub>               | Synchronous read cycle time                              |

| t <sub>MRAMWC</sub>               | Synchronous write cycle time                             |

| t <sub>MRAMWERESU</sub>           | Write or read enable setup time before clock             |

| t <sub>MRAMWEREH</sub>            | Write or read enable hold time after clock               |

| t <sub>MRAMCLKENSU</sub>          | Clock enable setup time before clock                     |

| t <sub>MRAMCLKENH</sub>           | Clock enable hold time after clock                       |

| t <sub>MRAMBESU</sub>             | Byte enable setup time before clock                      |

| t <sub>MRAMBEH</sub>              | Byte enable hold time after clock                        |

| t <sub>MRAMDATAASU</sub>          | A port data setup time before clock                      |

| t <sub>MRAMDATAAH</sub>           | A port data hold time after clock                        |

| t <sub>MRAMADDRASU</sub>          | A port address setup time before clock                   |

| t <sub>MRAMADDRAH</sub>           | A port address hold time after clock                     |

| t <sub>MRAMDATABSU</sub>          | B port setup time before clock                           |

| Table 4-81. I         | EP1S40 Ext     | ternal I/O T | iming on C | Column Pin     | s Using Glo | obal Clock | Networks |       |      |  |

|-----------------------|----------------|--------------|------------|----------------|-------------|------------|----------|-------|------|--|

| Davamatav             | -5 Speed Grade |              | -6 Spee    | -6 Speed Grade |             | d Grade    | -8 Spee  | Hait  |      |  |

| Parameter             | Min            | Max          | Min        | Max            | Min         | Max        | Min      | Max   | Unit |  |

| t <sub>INSU</sub>     | 2.126          |              | 2.268      |                | 2.558       |            | 2.930    |       | ns   |  |

| t <sub>INH</sub>      | 0.000          |              | 0.000      |                | 0.000       |            | 0.000    |       | ns   |  |

| t <sub>OUTCO</sub>    | 2.856          | 5.585        | 2.856      | 5.987          | 2.856       | 6.541      | 2.847    | 7.253 | ns   |  |

| t <sub>XZ</sub>       | 2.796          | 5.459        | 2.796      | 5.855          | 2.796       | 6.417      | 2.787    | 7.138 | ns   |  |

| t <sub>ZX</sub>       | 2.796          | 5.459        | 2.796      | 5.855          | 2.796       | 6.417      | 2.787    | 7.138 | ns   |  |

| t <sub>INSUPLL</sub>  | 1.466          |              | 1.455      |                | 1.711       |            | 1.906    |       | ns   |  |

| t <sub>INHPLL</sub>   | 0.000          |              | 0.000      |                | 0.000       |            | 0.000    |       | ns   |  |

| t <sub>OUTCOPLL</sub> | 1.092          | 2.345        | 1.092      | 2.510          | 1.092       | 2.455      | 1.089    | 2.473 | ns   |  |

| t <sub>XZPLL</sub>    | 1.032          | 2.219        | 1.032      | 2.378          | 1.032       | 2.331      | 1.029    | 2.358 | ns   |  |

| t <sub>ZXPLL</sub>    | 1.032          | 2.219        | 1.032      | 2.378          | 1.032       | 2.331      | 1.029    | 2.358 | ns   |  |

| Table 4–82. EP1\$40 External I/O Timing on Row Pins Using Fast Regional Clock Networks |         |         |                |       |                 |       |                |       |      |  |

|----------------------------------------------------------------------------------------|---------|---------|----------------|-------|-----------------|-------|----------------|-------|------|--|

| Doromotor                                                                              | -5 Spee | d Grade | -6 Speed Grade |       | -7 Speed Grade  |       | -8 Speed Grade |       | Unit |  |

| Parameter                                                                              | Min     | Max     | Min            | Max   | Min Max Min Max | Unit  |                |       |      |  |

| t <sub>INSU</sub>                                                                      | 2.472   |         | 2.685          |       | 3.083           |       | 3.056          |       | ns   |  |

| t <sub>INH</sub>                                                                       | 0.000   |         | 0.000          |       | 0.000           |       | 0.000          |       | ns   |  |

| t <sub>OUTCO</sub>                                                                     | 2.631   | 5.258   | 2.631          | 5.625 | 2.631           | 6.105 | 2.745          | 7.324 | ns   |  |

| t <sub>XZ</sub>                                                                        | 2.658   | 5.312   | 2.658          | 5.681 | 2.658           | 6.173 | 2.772          | 7.406 | ns   |  |

| t <sub>ZX</sub>                                                                        | 2.658   | 5.312   | 2.658          | 5.681 | 2.658           | 6.173 | 2.772          | 7.406 | ns   |  |

Tables 4–105 through 4–108 show the output adder delays associated with column and row I/O pins for both fast and slow slew rates. If an I/O standard is selected other than 3.3-V LVTTL 4mA or LVCMOS 2 mA with a fast slew rate, add the selected delay to the external  $t_{\rm OUTCO}$ ,  $t_{\rm OUTCOPLL}$ ,  $t_{\rm XZ}$ ,  $t_{\rm XZPLL}$ , and  $t_{\rm ZXPLL}$  I/O parameters shown in Table 4–55 on page 4–36 through Table 4–96 on page 4–56.

| Table 4–105.    | Stratix I/O S | Standard | Output De | lay Adde | rs for Fas | t Slew Ra | ate on Col | umn Pins | (Part 1 o | f 2) |

|-----------------|---------------|----------|-----------|----------|------------|-----------|------------|----------|-----------|------|

| Donomo          |               | -5 Spee  | d Grade   | -6 Spee  | d Grade    | -7 Spee   | d Grade    | -8 Spee  | ed Grade  | 11   |

| Parame          | ter           | Min      | Max       | Min      | Max        | Min       | Max        | Min      | Max       | Unit |

| LVCMOS          | 2 mA          |          | 1,895     |          | 1,990      |           | 1,990      |          | 1,990     | ps   |

|                 | 4 mA          |          | 956       |          | 1,004      |           | 1,004      |          | 1,004     | ps   |

|                 | 8 mA          |          | 189       |          | 198        |           | 198        |          | 198       | ps   |

|                 | 12 mA         |          | 0         |          | 0          |           | 0          |          | 0         | ps   |

|                 | 24 mA         |          | -157      |          | -165       |           | -165       |          | -165      | ps   |

| 3.3-V LVTTL     | 4 mA          |          | 1,895     |          | 1,990      |           | 1,990      |          | 1,990     | ps   |

|                 | 8 mA          |          | 1,347     |          | 1,414      |           | 1,414      |          | 1,414     | ps   |

|                 | 12 mA         |          | 636       |          | 668        |           | 668        |          | 668       | ps   |

|                 | 16 mA         |          | 561       |          | 589        |           | 589        |          | 589       | ps   |

|                 | 24 mA         |          | 0         |          | 0          |           | 0          |          | 0         | ps   |

| 2.5-V LVTTL     | 2 mA          |          | 2,517     |          | 2,643      |           | 2,643      |          | 2,643     | ps   |

|                 | 8 mA          |          | 834       |          | 875        |           | 875        |          | 875       | ps   |

|                 | 12 mA         |          | 504       |          | 529        |           | 529        |          | 529       | ps   |

|                 | 16 mA         |          | 194       |          | 203        |           | 203        |          | 203       | ps   |

| 1.8-V LVTTL     | 2 mA          |          | 1,304     |          | 1,369      |           | 1,369      |          | 1,369     | ps   |

|                 | 8 mA          |          | 960       |          | 1,008      |           | 1,008      |          | 1,008     | ps   |

|                 | 12 mA         |          | 960       |          | 1,008      |           | 1,008      |          | 1,008     | ps   |

| 1.5-V LVTTL     | 2 mA          |          | 6,680     |          | 7,014      |           | 7,014      |          | 7,014     | ps   |

|                 | 4 mA          |          | 3,275     |          | 3,439      |           | 3,439      |          | 3,439     | ps   |

|                 | 8 mA          |          | 1,589     |          | 1,668      |           | 1,668      |          | 1,668     | ps   |

| GTL             |               |          | 16        |          | 17         |           | 17         |          | 17        | ps   |

| GTL+            |               |          | 9         |          | 9          |           | 9          |          | 9         | ps   |

| 3.3-V PCI       |               |          | 50        |          | 52         |           | 52         |          | 52        | ps   |

| 3.3-V PCI-X 1.0 | )             |          | 50        |          | 52         |           | 52         |          | 52        | ps   |

| Compact PCI     |               |          | 50        |          | 52         |           | 52         |          | 52        | ps   |

| AGP 1×          |               |          | 50        |          | 52         |           | 52         |          | 52        | ps   |

| AGP 2×          |               |          | 1,895     |          | 1,990      |           | 1,990      |          | 1,990     | ps   |

Tables 4–109 and 4–110 show the adder delays for the column and row IOE programmable delays. These delays are controlled with the Quartus II software logic options listed in the Parameter column.

| Table 4–109. Stratix                |         |     | d Grade |     | d Grade | . , | d Grade | -8 Snee | ed Grade |      |

|-------------------------------------|---------|-----|---------|-----|---------|-----|---------|---------|----------|------|

| Parameter                           | Setting | Min | Max     | Min | Max     | Min | Max     | Min     | Max      | Unit |

| Decrease input delay                | Off     |     | 3,970   |     | 4,367   |     | 5,022   |         | 5,908    | ps   |

| to internal cells                   | Small   |     | 3,390   |     | 3,729   |     | 4,288   |         | 5,045    | ps   |

|                                     | Medium  |     | 2,810   |     | 3,091   |     | 3,554   |         | 4,181    | ps   |

|                                     | Large   |     | 224     |     | 235     |     | 270     |         | 318      | ps   |

|                                     | On      |     | 224     |     | 235     |     | 270     |         | 318      | ps   |

| Decrease input delay                | Off     |     | 3,900   |     | 4,290   |     | 4,933   |         | 5,804    | ps   |

| to input register                   | On      |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

| Decrease input delay                | Off     |     | 1,240   |     | 1,364   |     | 1,568   |         | 1,845    | ps   |

| to output register                  | On      |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

| Increase delay to                   | Off     |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

| output pin                          | On      |     | 397     |     | 417     |     | 417     |         | 417      | ps   |

| Increase delay to output enable pin | Off     |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

|                                     | On      |     | 338     |     | 372     |     | 427     |         | 503      | ps   |

| Increase output clock               | Off     |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

| enable delay                        | Small   |     | 540     |     | 594     |     | 683     |         | 804      | ps   |

|                                     | Large   |     | 1,016   |     | 1,118   |     | 1,285   |         | 1,512    | ps   |

|                                     | On      |     | 1,016   |     | 1,118   |     | 1,285   |         | 1,512    | ps   |

| Increase input clock                | Off     |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

| enable delay                        | Small   |     | 540     |     | 594     |     | 683     |         | 804      | ps   |

|                                     | Large   |     | 1,016   |     | 1,118   |     | 1,285   |         | 1,512    | ps   |

|                                     | On      |     | 1,016   |     | 1,118   |     | 1,285   |         | 1,512    | ps   |

| Increase output                     | Off     |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

| enable clock enable delay           | Small   |     | 540     |     | 594     |     | 683     |         | 804      | ps   |

| uciay                               | Large   |     | 1,016   |     | 1,118   |     | 1,285   |         | 1,512    | ps   |

|                                     | On      |     | 1,016   |     | 1,118   |     | 1,285   |         | 1,512    | ps   |

| Increase t <sub>ZX</sub> delay to   | Off     |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

| output pin                          | On      |     | 2,199   |     | 2,309   |     | 2,309   |         | 2,309    | ps   |

Table 4–121. Stratix Maximum Output Clock Rate (Using I/O Pins) for PLL[1, 2, 3, 4] Pins in Flip-Chip Packages

| I/O Standard                  | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |  |

|-------------------------------|-------------------|-------------------|-------------------|-------------------|------|--|

| LVTTL                         | 400               | 350               | 300               | 300               | MHz  |  |

| 2.5 V                         | 400               | 350               | 300               | 300               | MHz  |  |

| 1.8 V                         | 400               | 350               | 300               | 300               | MHz  |  |

| 1.5 V                         | 350               | 300               | 300 300           |                   | MHz  |  |

| LVCMOS                        | 400               | 350               | 300 300           |                   | MHz  |  |

| GTL                           | 200               | 167               | 125               | 125               | MHz  |  |

| GTL+                          | 200               | 167               | 125               | 125               | MHz  |  |

| SSTL-3 Class I                | 167               | 150               | 133               | 133               | MHz  |  |

| SSTL-3 Class II               | 167               | 150               | 133               | 133               | MHz  |  |

| SSTL-2 Class I                | 150               | 133               | 133               | 133               | MHz  |  |

| SSTL-2 Class II               | 150               | 133               | 133               | 133               | MHz  |  |

| SSTL-18 Class I               | 150               | 133               | 133               | 133               | MHz  |  |

| SSTL-18 Class II              | 150               | 133               | 133               | 133               | MHz  |  |

| 1.5-V HSTL Class I            | 250               | 225               | 200               | 200               | MHz  |  |

| 1.5-V HSTL Class II           | 225               | 225               | 200               | 200               | MHz  |  |

| 1.8-V HSTL Class I            | 250               | 225               | 200               | 200               | MHz  |  |

| 1.8-V HSTL Class II           | 225               | 225               | 200               | 200               | MHz  |  |

| 3.3-V PCI                     | 250               | 225               | 200               | 200               | MHz  |  |

| 3.3-V PCI-X 1.0               | 225               | 225               | 200               | 200               | MHz  |  |

| Compact PCI                   | 400               | 350               | 300               | 300               | MHz  |  |

| AGP 1×                        | 400               | 350               | 300               | 300               | MHz  |  |

| AGP 2×                        | 400               | 350               | 300               | 300               | MHz  |  |

| CTT                           | 300               | 250               | 200               | 200               | MHz  |  |

| LVPECL (2)                    | 717               | 717               | 500               | 500               | MHz  |  |

| PCML (2)                      | 420               | 420               | 420               | 420               | MHz  |  |

| LVDS (2)                      | 717               | 717               | 500               | 500               | MHz  |  |

| HyperTransport technology (2) | 420               | 420               | 420               | 420               | MHz  |  |

# Table 4–123. Stratix Maximum Output Clock Rate (Using I/O Pins) for PLL[1, 2, 3, 4] Pins in Wire-Bond Packages (Part 2 of 2)

| I/O Standard                  | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |  |  |  |  |

|-------------------------------|-------------------|-------------------|-------------------|------|--|--|--|--|

| LVDS (2)                      | 400               | 311               | 311               | MHz  |  |  |  |  |

| HyperTransport technology (2) | 420               | 400               | 400               | MHz  |  |  |  |  |

## Notes to Tables 4-120 through 4-123:

- (1) Differential SSTL-2 outputs are only available on column clock pins.

- (2) These parameters are only available on row I/O pins.

- (3) SSTL-2 in maximum drive strength condition. See Table 4–101 on page 4–62 for more information on exact loading conditions for each I/O standard.

- (4) SSTL-2 in minimum drive strength with  $\leq$ 10pF output load condition.

- (5) SSTL-2 in minimum drive strength with > 10pF output load condition.

- (6) Differential SSTL-2 outputs are only supported on column clock pins.

| Symbol                                | Conditions                                                            | -6 Speed Grade |     | -7 Speed Grade |       |     | -8 Speed Grade |       |     |      |      |

|---------------------------------------|-----------------------------------------------------------------------|----------------|-----|----------------|-------|-----|----------------|-------|-----|------|------|

|                                       |                                                                       | Min            | Тур | Max            | Min   | Тур | Max            | Min   | Тур | Max  | Unit |

| SW                                    | PCML (J = 4, 7, 8, 10) only                                           | 800            |     |                | 800   |     |                | 800   |     |      | ps   |

|                                       | PCML (J = 2) only                                                     | 1,200          |     |                | 1,200 |     |                | 1,200 |     |      | ps   |

|                                       | PCML (J = 1) only                                                     | 1,700          |     |                | 1,700 |     |                | 1,700 |     |      | ps   |

|                                       | LVDS and LVPECL (J = 1) only                                          | 550            |     |                | 550   |     |                | 550   |     |      | ps   |

|                                       | LVDS, LVPECL,<br>HyperTransport technology<br>(J = 2 through 10) only | 500            |     |                | 500   |     |                | 500   |     |      | ps   |

| Input jitter tolerance (peak-to-peak) | All                                                                   |                |     | 250            |       |     | 250            |       |     | 250  | ps   |

| Output jitter (peak-to-<br>peak)      | All                                                                   |                |     | 200            |       |     | 200            |       |     | 200  | ps   |

| Output t <sub>RISE</sub>              | LVDS                                                                  | 80             | 110 | 120            | 80    | 110 | 120            | 80    | 110 | 120  | ps   |

|                                       | HyperTransport technology                                             | 120            | 170 | 200            | 120   | 170 | 200            | 120   | 170 | 200  | ps   |

|                                       | LVPECL                                                                | 100            | 135 | 150            | 100   | 135 | 150            | 100   | 135 | 150  | ps   |

|                                       | PCML                                                                  | 80             | 110 | 135            | 80    | 110 | 135            | 80    | 110 | 135  | ps   |

| Output t <sub>FALL</sub>              | LVDS                                                                  | 80             | 110 | 120            | 80    | 110 | 120            | 80    | 110 | 120  | ps   |

|                                       | HyperTransport                                                        | 110            | 170 | 200            | 110   | 170 | 200            | 110   | 170 | 200  | ps   |

|                                       | LVPECL                                                                | 100            | 135 | 160            | 100   | 135 | 160            | 100   | 135 | 160  | ps   |

|                                       | PCML                                                                  | 110            | 145 | 175            | 110   | 145 | 175            | 110   | 145 | 175  | ps   |

| touty                                 | LVDS (J = 2 through10) only                                           | 47.5           | 50  | 52.5           | 47.5  | 50  | 52.5           | 47.5  | 50  | 52.5 | %    |

|                                       | LVDS (J =1) and LVPECL,<br>PCML, HyperTransport<br>technology         | 45             | 50  | 55             | 45    | 50  | 55             | 45    | 50  | 55   | %    |

| t <sub>LOCK</sub>                     | All                                                                   |                |     | 100            |       |     | 100            |       |     | 100  | μs   |

Table 4–126. High-Speed I/O Specifications for Wire-Bond Packages (Part 2 of 2)