Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 1846                                                    |

| Number of Logic Elements/Cells | 18460                                                   |

| Total RAM Bits                 | 1669248                                                 |

| Number of I/O                  | 426                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                         |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 672-BBGA                                                |

| Supplier Device Package        | 672-FBGA (27x27)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s20f672c6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| DSP Block Interface                                                                                                                                                                                                                                                                                                                                              | 2–70                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| PLLs & Clock Networks                                                                                                                                                                                                                                                                                                                                            |                     |

| Global & Hierarchical Clocking                                                                                                                                                                                                                                                                                                                                   | 2–73                |

| Enhanced & Fast PLLs                                                                                                                                                                                                                                                                                                                                             |                     |

| Enhanced PLLs                                                                                                                                                                                                                                                                                                                                                    |                     |

| Fast PLLs                                                                                                                                                                                                                                                                                                                                                        | 2–100               |

| I/O Structure                                                                                                                                                                                                                                                                                                                                                    | 2–104               |

| Double-Data Rate I/O Pins                                                                                                                                                                                                                                                                                                                                        |                     |

| External RAM Interfacing                                                                                                                                                                                                                                                                                                                                         |                     |

| Programmable Drive Strength                                                                                                                                                                                                                                                                                                                                      |                     |

| Open-Drain Output                                                                                                                                                                                                                                                                                                                                                | 2–120               |

| Slew-Rate Control                                                                                                                                                                                                                                                                                                                                                | 2–120               |

| Bus Hold                                                                                                                                                                                                                                                                                                                                                         |                     |

| Programmable Pull-Up Resistor                                                                                                                                                                                                                                                                                                                                    |                     |

| Advanced I/O Standard Support                                                                                                                                                                                                                                                                                                                                    |                     |

| Differential On-Chip Termination                                                                                                                                                                                                                                                                                                                                 |                     |

| MultiVolt I/O Interface                                                                                                                                                                                                                                                                                                                                          |                     |

| High-Speed Differential I/O Support                                                                                                                                                                                                                                                                                                                              |                     |

| Dedicated Circuitry                                                                                                                                                                                                                                                                                                                                              |                     |

| Byte Alignment                                                                                                                                                                                                                                                                                                                                                   |                     |

| Power Sequencing & Hot Socketing                                                                                                                                                                                                                                                                                                                                 |                     |

| IEEE Std. 1149.1 (JTAG) Boundary-Scan Support SignalTap II Embedded Logic Analyzer Configuration Operating Modes Configuring Stratix FPGAs with JRunner Configuration Schemes Partial Reconfiguration Remote Update Configuration Modes Stratix Automated Single Event Upset (SEU) Detection Custom-Built Circuitry Software Interface Temperature Sensing Diode |                     |

| Chapter 4. DC & Switching Characteristics Operating Conditions Power Consumption Timing Model                                                                                                                                                                                                                                                                    | 4–1<br>4–17<br>4–19 |

| Preliminary & Final Timing                                                                                                                                                                                                                                                                                                                                       |                     |

| Performance                                                                                                                                                                                                                                                                                                                                                      |                     |

| Internal Timing Parameters                                                                                                                                                                                                                                                                                                                                       |                     |

| External Timing Parameters                                                                                                                                                                                                                                                                                                                                       |                     |

| Stratix External I/O Timing                                                                                                                                                                                                                                                                                                                                      |                     |

| I/O Timing Measurement Methodology                                                                                                                                                                                                                                                                                                                               |                     |

| External I/O Delay Parameters                                                                                                                                                                                                                                                                                                                                    | 4–66                |

functions. Another special packing mode allows the register output to feed back into the LUT of the same LE so that the register is packed with its own fan-out LUT. This provides another mechanism for improved fitting. The LE can also drive out registered and unregistered versions of the LUT output.

### **LUT Chain & Register Chain**

In addition to the three general routing outputs, the LEs within an LAB have LUT chain and register chain outputs. LUT chain connections allow LUTs within the same LAB to cascade together for wide input functions. Register chain outputs allow registers within the same LAB to cascade together. The register chain output allows an LAB to use LUTs for a single combinatorial function and the registers to be used for an unrelated shift register implementation. These resources speed up connections between LABs while saving local interconnect resources. See "MultiTrack Interconnect" on page 2–14 for more information on LUT chain and register chain connections.

### addnsub Signal

The LE's dynamic adder/subtractor feature saves logic resources by using one set of LEs to implement both an adder and a subtractor. This feature is controlled by the LAB-wide control signal addnsub. The addnsub signal sets the LAB to perform either A+B or A-B. The LUT computes addition, and subtraction is computed by adding the two's complement of the intended subtractor. The LAB-wide signal converts to two's complement by inverting the B bits within the LAB and setting carry-in = 1 to add one to the least significant bit (LSB). The LSB of an adder/subtractor must be placed in the first LE of the LAB, where the LAB-wide addnsub signal automatically sets the carry-in to 1. The Quartus II Compiler automatically places and uses the adder/subtractor feature when using adder/subtractor parameterized functions.

## **LE Operating Modes**

The Stratix LE can operate in one of the following modes:

- Normal mode

- Dynamic arithmetic mode

Each mode uses LE resources differently. In each mode, eight available inputs to the LE—the four data inputs from the LAB local interconnect; carry-in0 and carry-in1 from the previous LE; the LAB carry-in from the previous carry-chain LAB; and the register chain connection—are directed to different destinations to implement the desired logic function. LAB-wide signals provide clock, asynchronous clear,

# TriMatrix Memory

TriMatrix memory consists of three types of RAM blocks: M512, M4K, and M-RAM blocks. Although these memory blocks are different, they can all implement various types of memory with or without parity, including true dual-port, simple dual-port, and single-port RAM, ROM, and FIFO buffers. Table 2–3 shows the size and features of the different RAM blocks.

| Table 2–3. TriMatrix Memory Features (Part 1 of 2) |                                  |                                  |                                |  |  |  |  |  |

|----------------------------------------------------|----------------------------------|----------------------------------|--------------------------------|--|--|--|--|--|

| Memory Feature                                     | M512 RAM Block<br>(32 × 18 Bits) | M4K RAM Block<br>(128 × 36 Bits) | M-RAM Block<br>(4K × 144 Bits) |  |  |  |  |  |

| Maximum performance                                | (1)                              | (1)                              | (1)                            |  |  |  |  |  |

| True dual-port memory                              |                                  | <b>✓</b>                         | <b>✓</b>                       |  |  |  |  |  |

| Simple dual-port memory                            | ✓                                | ~                                | <b>✓</b>                       |  |  |  |  |  |

| Single-port memory                                 | ✓                                | ✓                                | ✓                              |  |  |  |  |  |

| Shift register                                     | <b>✓</b>                         | ✓                                |                                |  |  |  |  |  |

| ROM                                                | ✓                                | ✓                                | (2)                            |  |  |  |  |  |

| FIFO buffer                                        | ✓                                | ✓                                | ✓                              |  |  |  |  |  |

| Byte enable                                        |                                  | ✓                                | ✓                              |  |  |  |  |  |

| Parity bits                                        | ✓                                | ✓                                | ✓                              |  |  |  |  |  |

| Mixed clock mode                                   | ✓                                | ✓                                | ✓                              |  |  |  |  |  |

| Memory initialization                              | ✓                                | ✓                                |                                |  |  |  |  |  |

| Simple dual-port<br>memory mixed width<br>support  | <b>✓</b>                         | ~                                | ~                              |  |  |  |  |  |

| True dual-port memory mixed width support          |                                  | ~                                | ~                              |  |  |  |  |  |

| Power-up conditions                                | Outputs cleared                  | Outputs cleared                  | Outputs<br>unknown             |  |  |  |  |  |

| Register clears                                    | Input and output registers       | Input and output registers       | Output registers               |  |  |  |  |  |

| Mixed-port read-<br>during-write                   | Unknown<br>output/old data       | Unknown<br>output/old data       | Unknown output                 |  |  |  |  |  |

## **Input/Output Clock Mode**

Input/output clock mode can be implemented for both the true and simple dual-port memory modes. On each of the two ports, A or B, one clock controls all registers for inputs into the memory block: data input, wren, and address. The other clock controls the block's data output registers. Each memory block port, A or B, also supports independent clock enables and asynchronous clear signals for input and output registers. Figures 2–25 and 2–26 show the memory block in input/output clock mode.

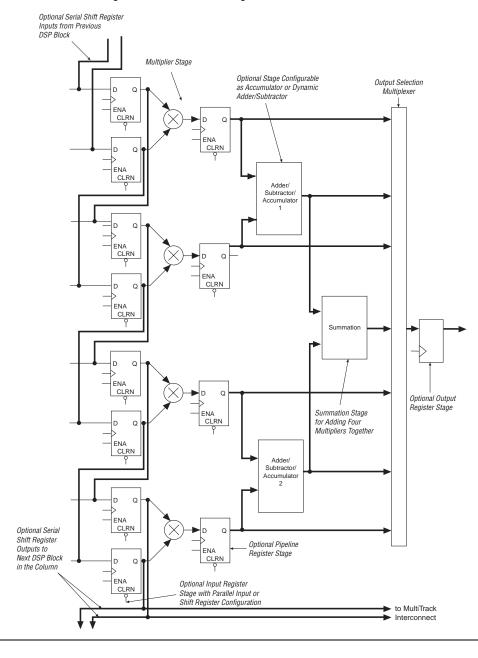

Figure 2–30. DSP Block Diagram for 18 imes 18-Bit Configuration

Accumulator Feedback accum\_sload0 (2) Result A ■ overflow0 Adder/ Subtractor/ addnsub1 (2) Accumulator1 Output Selection Multiplexer Result B signa (2) Summation Output signb (2) Register Block Result C Adder/ addnsub3 (2) Subtractor/ Accumulator2 overflow1 Result D accum\_sload1 (2) Accumulator Feedback

Figure 2–34. Adder/Output Blocks Note (1)

#### Notes to Figure 2–34:

- (1) Adder/output block shown in Figure 2–34 is in 18 × 18-bit mode. In 9 × 9-bit mode, there are four adder/subtractor blocks and two summation blocks.

- (2) These signals are either not registered, registered once, or registered twice to match the data path pipeline.

Any of the four external output counters can drive the single-ended or differential clock outputs for PLLs 5 and 6. This means one counter or frequency can drive all output pins available from PLL 5 or PLL 6. Each pair of output pins (four pins total) has dedicated VCC and GND pins to reduce the output clock's overall jitter by providing improved isolation from switching I/O pins.

For PLLs 5 and 6, each pin of a single-ended output pair can either be in phase or 180° out of phase. The clock output pin pairs support the same I/O standards as standard output pins (in the top and bottom banks) as well as LVDS, LVPECL, 3.3-V PCML, HyperTransport technology, differential HSTL, and differential SSTL. Table 2–20 shows which I/O standards the enhanced PLL clock pins support. When in single-ended or differential mode, the two outputs operate off the same power supply. Both outputs use the same standards in single-ended mode to maintain performance. You can also use the external clock output pins as user output pins if external enhanced PLL clocking is not needed.

| Table 2–20. I/O Standards Supported for Enhanced PLL Pins (Part 1 of 2) |              |          |           |        |  |  |  |  |

|-------------------------------------------------------------------------|--------------|----------|-----------|--------|--|--|--|--|

| L/O Ctondovd                                                            |              | Output   |           |        |  |  |  |  |

| I/O Standard                                                            | INCLK FBIN F |          | PLLENABLE | EXTCLK |  |  |  |  |

| LVTTL                                                                   | <b>✓</b>     | <b>✓</b> | <b>✓</b>  | ✓      |  |  |  |  |

| LVCMOS                                                                  | <b>✓</b>     | <b>✓</b> | ✓         | ✓      |  |  |  |  |

| 2.5 V                                                                   | <b>✓</b>     | <b>✓</b> |           | ✓      |  |  |  |  |

| 1.8 V                                                                   | <b>✓</b>     | <b>✓</b> |           | ✓      |  |  |  |  |

| 1.5 V                                                                   | <b>✓</b>     | <b>✓</b> |           | ✓      |  |  |  |  |

| 3.3-V PCI                                                               | <b>✓</b>     | <b>✓</b> |           | ✓      |  |  |  |  |

| 3.3-V PCI-X 1.0                                                         | <b>✓</b>     | <b>✓</b> |           | ✓      |  |  |  |  |

| LVPECL                                                                  | <b>✓</b>     | <b>✓</b> |           | ✓      |  |  |  |  |

| 3.3-V PCML                                                              | <b>✓</b>     | <b>✓</b> |           | ✓      |  |  |  |  |

| LVDS                                                                    | <b>✓</b>     | <b>✓</b> |           | ✓      |  |  |  |  |

| HyperTransport technology                                               | <b>✓</b>     | <b>✓</b> |           | ✓      |  |  |  |  |

| Differential HSTL                                                       | <b>✓</b>     |          |           | ✓      |  |  |  |  |

| Differential SSTL                                                       |              |          |           | ✓      |  |  |  |  |

| 3.3-V GTL                                                               | <b>✓</b>     | ✓        |           | ✓      |  |  |  |  |

| 3.3-V GTL+                                                              | <b>✓</b>     | ✓        |           | ✓      |  |  |  |  |

| 1.5-V HSTL Class I                                                      | <b>✓</b>     | ✓        |           | ✓      |  |  |  |  |

#### Clock Feedback

The following four feedback modes in Stratix device enhanced PLLs allow multiplication and/or phase and delay shifting:

- Zero delay buffer: The external clock output pin is phase-aligned with the clock input pin for zero delay. Altera recommends using the same I/O standard on the input clock and the output clocks for optimum performance.

- External feedback: The external feedback input pin, FBIN, is phase-aligned with the clock input, CLK, pin. Aligning these clocks allows you to remove clock delay and skew between devices. This mode is only possible for PLLs 5 and 6. PLLs 5 and 6 each support feedback for one of the dedicated external outputs, either one single-ended or one differential pair. In this mode, one *e* counter feeds back to the PLL FBIN input, becoming part of the feedback loop. Altera recommends using the same I/O standard on the input clock, the FBIN pin, and the output clocks for optimum performance.

- Normal mode: If an internal clock is used in this mode, it is phasealigned to the input clock pin. The external clock output pin will have a phase delay relative to the clock input pin if connected in this mode. You define which internal clock output from the PLL should be phase-aligned to the internal clock pin.

- No compensation: In this mode, the PLL will not compensate for any clock networks or external clock outputs.

#### Phase & Delay Shifting

Stratix device enhanced PLLs provide advanced programmable phase and clock delay shifting. These parameters are set in the Quartus II software.

#### Phase Delay

The Quartus II software automatically sets the phase taps and counter settings according to the phase shift entry. You enter a desired phase shift and the Quartus II software automatically sets the closest setting achievable. This type of phase shift is not reconfigurable during system operation. For phase shifting, enter a phase shift (in degrees or time units) for each PLL clock output port or for all outputs together in one shift. You can select phase-shifting values in time units with a resolution of 156.25 to 416.66 ps. This resolution is a function of frequency input and the multiplication and division factors (that is, it is a function of the VCO period), with the finest step being equal to an eighth (×0.125) of the VCO period. Each clock output counter can choose a different phase of the

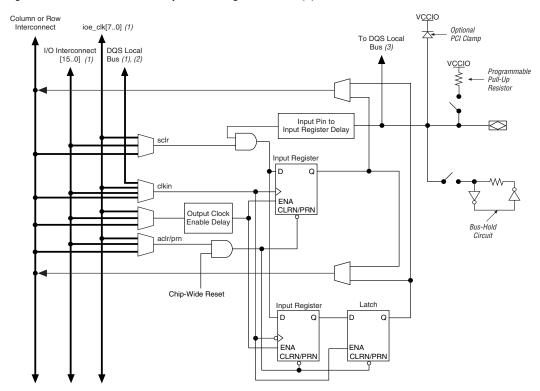

Figure 2–65. Stratix IOE in DDR Input I/O Configuration Note (1)

*Notes to Figure 2–65:*

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) This signal connection is only allowed on dedicated DQ function pins.

- (3) This signal is for dedicated DQS function pins only.

Stratix, Stratix II, Cyclone<sup>®</sup>, and Cyclone II devices must be within the first 17 devices in a JTAG chain. All of these devices have the same JTAG controller. If any of the Stratix, Stratix II, Cyclone, and Cyclone II devices are in the 18th or after they will fail configuration. This does not affect SignalTap II.

For more information on JTAG, see the following documents:

- AN 39: IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices

- Jam Programming & Test Language Specification

# SignalTap II Embedded Logic Analyzer

Stratix devices feature the SignalTap II embedded logic analyzer, which monitors design operation over a period of time through the IEEE Std. 1149.1 (JTAG) circuitry. You can analyze internal logic at speed without bringing internal signals to the I/O pins. This feature is particularly important for advanced packages, such as FineLine BGA® packages, because it can be difficult to add a connection to a pin during the debugging process after a board is designed and manufactured.

# Configuration

The logic, circuitry, and interconnects in the Stratix architecture are configured with CMOS SRAM elements. Altera® devices are reconfigurable. Because every device is tested with a high-coverage production test program, you do not have to perform fault testing and can focus on simulation and design verification.

Stratix devices are configured at system power-up with data stored in an Altera serial configuration device or provided by a system controller. Altera offers in-system programmability (ISP)-capable configuration devices that configure Stratix devices via a serial data stream. Stratix devices can be configured in under 100 ms using 8-bit parallel data at 100 MHz. The Stratix device's optimized interface allows microprocessors to configure it serially or in parallel, and synchronously or asynchronously. The interface also enables microprocessors to treat Stratix devices as memory and configure them by writing to a virtual memory location, making reconfiguration easy. After a Stratix device has been configured, it can be reconfigured in-circuit by resetting the device and loading new data. Real-time changes can be made during system operation, enabling innovative reconfigurable computing applications.

# **Operating Modes**

The Stratix architecture uses SRAM configuration elements that require configuration data to be loaded each time the circuit powers up. The process of physically loading the SRAM data into the device is called configuration. During initialization, which occurs immediately after

For Stratix, the CRC is computed by the Quartus II software and downloaded into the device as a part of the configuration bit stream. The CRC\_ERROR pin reports a soft error when configuration SRAM data is corrupted, triggering device reconfiguration.

## **Custom-Built Circuitry**

Dedicated circuitry is built in the Stratix devices to perform error detection automatically. You can use the built-in dedicated circuitry for error detection using CRC feature in Stratix devices, eliminating the need for external logic. This circuitry will perform error detection automatically when enabled. This error detection circuitry in Stratix devices constantly checks for errors in the configuration SRAM cells while the device is in user mode. You can monitor one external pin for the error and use it to trigger a re-configuration cycle. Select the desired time between checks by adjusting a built-in clock divider.

#### **Software Interface**

In the Quartus II software version 4.1 and later, you can turn on the automated error detection CRC feature in the **Device & Pin Options** dialog box. This dialog box allows you to enable the feature and set the internal frequency of the CRC between 400 kHz to 100 MHz. This controls the rate that the CRC circuitry verifies the internal configuration SRAM bits in the FPGA device.

For more information on CRC, see AN 357: Error Detection Using CRC in Altera FPGA Devices.

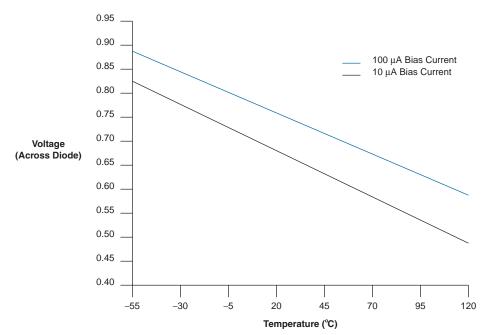

# Temperature Sensing Diode

Stratix devices include a diode-connected transistor for use as a temperature sensor in power management. This diode is used with an external digital thermometer device such as a MAX1617A or MAX1619 from MAXIM Integrated Products. These devices steer bias current through the Stratix diode, measuring forward voltage and converting this reading to temperature in the form of an 8-bit signed number (7 bits plus sign). The external device's output represents the junction temperature of the Stratix device and can be used for intelligent power management.

The diode requires two pins (tempdiodep and tempdioden) on the Stratix device to connect to the external temperature-sensing device, as shown in Figure 3–5. The temperature sensing diode is a passive element and therefore can be used before the Stratix device is powered.

The temperature-sensing diode works for the entire operating range shown in Figure 3–6.

Figure 3-6. Temperature vs. Temperature-Sensing Diode Voltage

| Table 4–25. 3.3-V AGP 1× Specifications (Part 2 of 2) |                                              |                             |                       |  |                         |   |  |  |  |

|-------------------------------------------------------|----------------------------------------------|-----------------------------|-----------------------|--|-------------------------|---|--|--|--|

| Symbol                                                | Parameter Conditions Minimum Typical Maximum |                             |                       |  |                         |   |  |  |  |

| $V_{OH}$                                              | High-level output voltage                    | $I_{OUT} = -0.5 \text{ mA}$ | $0.9 \times V_{CCIO}$ |  | 3.6                     | V |  |  |  |

| V <sub>OL</sub>                                       | Low-level output voltage                     | I <sub>OUT</sub> = 1.5 mA   |                       |  | 0.1 × V <sub>CCIO</sub> | V |  |  |  |

| Table 4-26           | Table 4–26. 1.5-V HSTL Class I Specifications |                               |                         |         |                        |      |  |  |  |  |  |

|----------------------|-----------------------------------------------|-------------------------------|-------------------------|---------|------------------------|------|--|--|--|--|--|

| Symbol               | Parameter                                     | Conditions                    | Minimum                 | Typical | Maximum                | Unit |  |  |  |  |  |

| V <sub>CCIO</sub>    | Output supply voltage                         |                               | 1.4                     | 1.5     | 1.6                    | V    |  |  |  |  |  |

| V <sub>REF</sub>     | Input reference voltage                       |                               | 0.68                    | 0.75    | 0.9                    | V    |  |  |  |  |  |

| V <sub>TT</sub>      | Termination voltage                           |                               | 0.7                     | 0.75    | 0.8                    | V    |  |  |  |  |  |

| V <sub>IH</sub> (DC) | DC high-level input voltage                   |                               | V <sub>REF</sub> + 0.1  |         |                        | V    |  |  |  |  |  |

| V <sub>IL</sub> (DC) | DC low-level input voltage                    |                               | -0.3                    |         | V <sub>REF</sub> – 0.1 | V    |  |  |  |  |  |

| V <sub>IH</sub> (AC) | AC high-level input voltage                   |                               | V <sub>REF</sub> + 0.2  |         |                        | V    |  |  |  |  |  |

| V <sub>IL</sub> (AC) | AC low-level input voltage                    |                               |                         |         | V <sub>REF</sub> - 0.2 | V    |  |  |  |  |  |

| V <sub>OH</sub>      | High-level output voltage                     | $I_{OH} = -8 \text{ mA } (3)$ | V <sub>CCIO</sub> - 0.4 |         |                        | V    |  |  |  |  |  |

| V <sub>OL</sub>      | Low-level output voltage                      | I <sub>OL</sub> = 8 mA (3)    |                         |         | 0.4                    | V    |  |  |  |  |  |

| Symbol               | Parameter                   | Conditions                     | Minimum                 | Typical | Maximum                | Unit |

|----------------------|-----------------------------|--------------------------------|-------------------------|---------|------------------------|------|

| V <sub>CCIO</sub>    | Output supply voltage       |                                | 1.4                     | 1.5     | 1.6                    | V    |

| V <sub>REF</sub>     | Input reference voltage     |                                | 0.68                    | 0.75    | 0.9                    | V    |

| V <sub>TT</sub>      | Termination voltage         |                                | 0.7                     | 0.75    | 0.8                    | V    |

| V <sub>IH</sub> (DC) | DC high-level input voltage |                                | V <sub>REF</sub> + 0.1  |         |                        | V    |

| V <sub>IL</sub> (DC) | DC low-level input voltage  |                                | -0.3                    |         | V <sub>REF</sub> – 0.1 | V    |

| V <sub>IH</sub> (AC) | AC high-level input voltage |                                | V <sub>REF</sub> + 0.2  |         |                        | V    |

| V <sub>IL</sub> (AC) | AC low-level input voltage  |                                |                         |         | V <sub>REF</sub> - 0.2 | V    |

| V <sub>OH</sub>      | High-level output voltage   | $I_{OH} = -16 \text{ mA } (3)$ | V <sub>CCIO</sub> - 0.4 |         |                        | V    |

| V <sub>OL</sub>      | Low-level output voltage    | $I_{OL} = 16 \text{ mA } (3)$  |                         |         | 0.4                    | V    |

Table 4–52 shows the external I/O timing parameters when using fast regional clock networks.

| <b>Table 4–52. Stratix Fast Regional Clock External I/O Timing Parameters</b> Notes (1), (2) |                                                                                                                      |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Symbol                                                                                       | Parameter                                                                                                            |  |  |  |  |  |  |

| t <sub>INSU</sub>                                                                            | Setup time for input or bidirectional pin using IOE input register with fast regional clock fed by FCLK pin          |  |  |  |  |  |  |

| t <sub>INH</sub>                                                                             | Hold time for input or bidirectional pin using IOE input register with fast regional clock fed by FCLK pin           |  |  |  |  |  |  |

| t <sub>outco</sub>                                                                           | Clock-to-output delay output or bidirectional pin using IOE output register with fast regional clock fed by FCLK pin |  |  |  |  |  |  |

| t <sub>XZ</sub>                                                                              | Synchronous IOE output enable register to output pin disable delay using fast regional clock fed by FCLK pin         |  |  |  |  |  |  |

| t <sub>ZX</sub>                                                                              | Synchronous IOE output enable register to output pin enable delay using fast regional clock fed by FCLK pin          |  |  |  |  |  |  |

Notes to Table 4-52:

- (1) These timing parameters are sample-tested only.

- (2) These timing parameters are for column and row IOE pins. You should use the Quartus II software to verify the external timing for any pin.

Table 4–53 shows the external I/O timing parameters when using regional clock networks.

| Symbol                | Parameter                                                                                                                               |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>INSU</sub>     | Setup time for input or bidirectional pin using IOE input register with regional clock fed by CLK pin                                   |

| t <sub>INH</sub>      | Hold time for input or bidirectional pin using IOE input register with regional clock fed by CLK pin                                    |

| t <sub>OUTCO</sub>    | Clock-to-output delay output or bidirectional pin using IOE output register with regional clock fed by CLK pin                          |

| t <sub>INSUPLL</sub>  | Setup time for input or bidirectional pin using IOE input register with regional clock fed by Enhanced PLL with default phase setting   |

| t <sub>INHPLL</sub>   | Hold time for input or bidirectional pin using IOE input register with regional clock fed by Enhanced PLL with default phase setting    |

| t <sub>OUTCOPLL</sub> | Clock-to-output delay output or bidirectional pin using IOE output register with regional clock Enhanced PLL with default phase setting |

Tables 4–67 through 4–72 show the external timing parameters on column and row pins for EP1S25 devices.

| Table 4–67. I      | Table 4–67. EP1S25 External I/O Timing on Column Pins Using Fast Regional Clock Networks |       |                |       |                |       |                |       |    |  |  |

|--------------------|------------------------------------------------------------------------------------------|-------|----------------|-------|----------------|-------|----------------|-------|----|--|--|

|                    | -5 Speed Grade                                                                           |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | 11 |  |  |

| Parameter          | Min                                                                                      | Max   | Min            | Max   | Max Min Max    | Min   | Max            | Unit  |    |  |  |

| t <sub>INSU</sub>  | 2.412                                                                                    |       | 2.613          |       | 2.968          |       | 3.468          |       | ns |  |  |

| t <sub>INH</sub>   | 0.000                                                                                    |       | 0.000          |       | 0.000          |       | 0.000          |       | ns |  |  |

| t <sub>OUTCO</sub> | 2.196                                                                                    | 4.475 | 2.196          | 4.748 | 2.196          | 5.118 | 2.196          | 5.603 | ns |  |  |

| t <sub>XZ</sub>    | 2.136                                                                                    | 4.349 | 2.136          | 4.616 | 2.136          | 4.994 | 2.136          | 5.488 | ns |  |  |

| t <sub>ZX</sub>    | 2.136                                                                                    | 4.349 | 2.136          | 4.616 | 2.136          | 4.994 | 2.136          | 5.488 | ns |  |  |

| Table 4–68. I        | Table 4–68. EP1S25 External I/O Timing on Column Pins Using Regional Clock Networks |         |         |                |       |                |       |                |      |  |  |

|----------------------|-------------------------------------------------------------------------------------|---------|---------|----------------|-------|----------------|-------|----------------|------|--|--|

|                      | -5 Spee                                                                             | d Grade | -6 Spee | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |      |  |  |

| Parameter            | Min                                                                                 | Max     | Min     | Max            | Min   | Max            | Min   | Max            | Unit |  |  |

| t <sub>INSU</sub>    | 1.535                                                                               |         | 1.661   |                | 1.877 |                | 2.125 |                | ns   |  |  |

| t <sub>INH</sub>     | 0.000                                                                               |         | 0.000   |                | 0.000 |                | 0.000 |                | ns   |  |  |

| t <sub>оитсо</sub>   | 2.739                                                                               | 5.396   | 2.739   | 5.746          | 2.739 | 6.262          | 2.739 | 6.946          | ns   |  |  |

| t <sub>XZ</sub>      | 2.679                                                                               | 5.270   | 2.679   | 5.614          | 2.679 | 6.138          | 2.679 | 6.831          | ns   |  |  |

| t <sub>ZX</sub>      | 2.679                                                                               | 5.270   | 2.679   | 5.614          | 2.679 | 6.138          | 2.679 | 6.831          | ns   |  |  |

| t <sub>INSUPLL</sub> | 0.934                                                                               |         | 0.980   |                | 1.092 |                | 1.231 |                | ns   |  |  |

| t <sub>INHPLL</sub>  | 0.000                                                                               |         | 0.000   |                | 0.000 |                | 0.000 |                | ns   |  |  |

| toutcopll            | 1.316                                                                               | 2.733   | 1.316   | 2.839          | 1.316 | 2.921          | 1.316 | 3.110          | ns   |  |  |

| t <sup>XZPLL</sup>   | 1.256                                                                               | 2.607   | 1.256   | 2.707          | 1.256 | 2.797          | 1.256 | 2.995          | ns   |  |  |

| t <sub>ZXPLL</sub>   | 1.256                                                                               | 2.607   | 1.256   | 2.707          | 1.256 | 2.797          | 1.256 | 2.995          | ns   |  |  |

Tables 4–85 through 4–90 show the external timing parameters on column and row pins for EP1S60 devices.

| Table 4–85. EP1S60 External I/O Timing on Column Pins Using Fast Regional Clock Networks Note (1) |                |       |                |       |                |       |                |     |      |  |  |

|---------------------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-----|------|--|--|

| Parameter                                                                                         | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |     | 11   |  |  |

|                                                                                                   | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max | Unit |  |  |

| t <sub>INSU</sub>                                                                                 | 3.029          |       | 3.277          |       | 3.733          |       | NA             |     | ns   |  |  |

| t <sub>INH</sub>                                                                                  | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns   |  |  |

| t <sub>OUTCO</sub>                                                                                | 2.446          | 4.871 | 2.446          | 5.215 | 2.446          | 5.685 | NA             | NA  | ns   |  |  |

| t <sub>XZ</sub>                                                                                   | 2.386          | 4.745 | 2.386          | 5.083 | 2.386          | 5.561 | NA             | NA  | ns   |  |  |

| t <sub>ZX</sub>                                                                                   | 2.386          | 4.745 | 2.386          | 5.083 | 2.386          | 5.561 | NA             | NA  | ns   |  |  |

| Table 4–86. EP1S60 External I/O Timing on Column Pins Using Regional Clock Networks Note (1) |                |       |                |       |                |       |                |     |      |

|----------------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-----|------|

| Parameter                                                                                    | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |     |      |

|                                                                                              | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max | Unit |

| t <sub>INSU</sub>                                                                            | 2.491          |       | 2.691          |       | 3.060          |       | NA             |     | ns   |

| t <sub>INH</sub>                                                                             | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns   |

| t <sub>OUTCO</sub>                                                                           | 2.767          | 5.409 | 2.767          | 5.801 | 2.767          | 6.358 | NA             | NA  | ns   |

| t <sub>XZ</sub>                                                                              | 2.707          | 5.283 | 2.707          | 5.669 | 2.707          | 6.234 | NA             | NA  | ns   |

| t <sub>ZX</sub>                                                                              | 2.707          | 5.283 | 2.707          | 5.669 | 2.707          | 6.234 | NA             | NA  | ns   |

| t <sub>INSUPLL</sub>                                                                         | 1.233          |       | 1.270          |       | 1.438          |       | NA             |     | ns   |

| t <sub>INHPLL</sub>                                                                          | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns   |

| t <sub>OUTCOPLL</sub>                                                                        | 1.078          | 2.278 | 1.078          | 2.395 | 1.078          | 2.428 | NA             | NA  | ns   |

| t <sub>XZPLL</sub>                                                                           | 1.018          | 2.152 | 1.018          | 2.263 | 1.018          | 2.304 | NA             | NA  | ns   |

| t <sub>ZXPLL</sub>                                                                           | 1.018          | 2.152 | 1.018          | 2.263 | 1.018          | 2.304 | NA             | NA  | ns   |

| Table 4–89. EP1S60 External I/O Timing on Row Pins Using Regional Clock Networks Note (1) |                |       |                |       |                |       |                |     |      |

|-------------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-----|------|

| Parameter                                                                                 | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |     |      |

|                                                                                           | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max | Unit |

| t <sub>INSU</sub>                                                                         | 2.775          |       | 2.990          |       | 3.407          |       | NA             |     | ns   |

| t <sub>INH</sub>                                                                          | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns   |

| t <sub>OUTCO</sub>                                                                        | 2.867          | 5.644 | 2.867          | 6.057 | 2.867          | 6.600 | NA             | NA  | ns   |

| t <sub>XZ</sub>                                                                           | 2.894          | 5.698 | 2.894          | 6.113 | 2.894          | 6.668 | NA             | NA  | ns   |

| t <sub>ZX</sub>                                                                           | 2.894          | 5.698 | 2.894          | 6.113 | 2.894          | 6.668 | NA             | NA  | ns   |

| t <sub>INSUPLL</sub>                                                                      | 1.523          |       | 1.577          |       | 1.791          |       | NA             |     | ns   |

| t <sub>INHPLL</sub>                                                                       | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns   |

| t <sub>OUTCOPLL</sub>                                                                     | 1.174          | 2.507 | 1.174          | 2.643 | 1.174          | 2.664 | NA             | NA  | ns   |

| t <sub>XZPLL</sub>                                                                        | 1.201          | 2.561 | 1.201          | 2.699 | 1.201          | 2.732 | NA             | NA  | ns   |

| t <sub>ZXPLL</sub>                                                                        | 1.201          | 2.561 | 1.201          | 2.699 | 1.201          | 2.732 | NA             | NA  | ns   |

| Table 4–90. EP1S60 External I/O Timing on Row Pins Using Global Clock Networks Note (1) |                |       |                |       |                |       |                |     |      |

|-----------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-----|------|

| Parameter                                                                               | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |     |      |

|                                                                                         | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max | Unit |

| t <sub>INSU</sub>                                                                       | 2.232          |       | 2.393          |       | 2.721          |       | NA             |     | ns   |

| t <sub>INH</sub>                                                                        | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns   |

| t <sub>outco</sub>                                                                      | 3.182          | 6.187 | 3.182          | 6.654 | 3.182          | 7.286 | NA             | NA  | ns   |

| t <sub>XZ</sub>                                                                         | 3.209          | 6.241 | 3.209          | 6.710 | 3.209          | 7.354 | NA             | NA  | ns   |

| t <sub>ZX</sub>                                                                         | 3.209          | 6.241 | 3.209          | 6.710 | 3.209          | 7.354 | NA             | NA  | ns   |

| t <sub>INSUPLL</sub>                                                                    | 1.651          |       | 1.612          |       | 1.833          |       | NA             |     | ns   |

| t <sub>INHPLL</sub>                                                                     | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns   |

| toutcopll                                                                               | 1.154          | 2.469 | 1.154          | 2.608 | 1.154          | 2.622 | NA             | NA  | ns   |

| t <sub>XZPLL</sub>                                                                      | 1.181          | 2.523 | 1.181          | 2.664 | 1.181          | 2.690 | NA             | NA  | ns   |

| t <sub>ZXPLL</sub>                                                                      | 1.181          | 2.523 | 1.181          | 2.664 | 1.181          | 2.690 | NA             | NA  | ns   |

*Note to Tables 4–85 to 4–90:*

<sup>(1)</sup> Only EP1S25, EP1S30, and EP1S40 devices have the -8 speed grade.

| Table 4–133. Fast PLL Specifications for -8 Speed Grades (Part 2 of 2) |                                      |     |     |      |  |  |

|------------------------------------------------------------------------|--------------------------------------|-----|-----|------|--|--|

| Symbol                                                                 | Parameter                            | Min | Max | Unit |  |  |

| t <sub>ARESET</sub>                                                    | Minimum pulse width on areset signal | 10  |     | ns   |  |  |

#### Notes to Tables 4–131 through 4–133:

- (1) See "Maximum Input & Output Clock Rates" on page 4–76.

- (2) PLLs 7, 8, 9, and 10 in the EP1S80 device support up to 717-MHz input and output.

- (3) Use this equation (f<sub>OUT</sub> = f<sub>IN</sub> \* ml(n × post-scale counter)) in conjunction with the specified f<sub>INPFD</sub> and f<sub>VCO</sub> ranges to determine the allowed PLL settings.

- (4) When using the SERDES, high-speed differential I/O mode supports a maximum output frequency of 210 MHz to the global or regional clocks (that is, the maximum data rate 840 Mbps divided by the smallest SERDES J factor of 4).

- (5) Refer to the section "High-Speed I/O Specification" on page 4–87 for more information.

- (6) This parameter is for high-speed differential I/O mode only.

- (7) These counters have a maximum of 32 if programmed for 50/50 duty cycle. Otherwise, they have a maximum of 16.

- (8) High-speed differential I/O mode supports W = 1 to 16 and J = 4, 7, 8, or 10.

# DLL Specifications

Table 4–134 reports the jitter for the DLL in the DQS phase shift reference circuit.

| Table 4–134. DLL Jitter for DQS Phase Shift Reference Circuit |                 |  |  |  |

|---------------------------------------------------------------|-----------------|--|--|--|

| Frequency (MHz)                                               | DLL Jitter (ps) |  |  |  |

| 197 to 200                                                    | ± 100           |  |  |  |

| 160 to 196                                                    | ± 300           |  |  |  |

| 100 to 159 ± 500                                              |                 |  |  |  |

For more information on DLL jitter, see the *DDR SRAM* section in the *Stratix Architecture* chapter of the *Stratix Device Handbook, Volume 1*.

Table 4–135 lists the Stratix DLL low frequency limit for full phase shift across all PVT conditions. The Stratix DLL can be used below these frequencies, but it will not achieve the full phase shift requested across all

# 5. Reference & Ordering Information

\$51005-2.1

## Software

Stratix® devices are supported by the Altera® Quartus® II design software, which provides a comprehensive environment for system-on-a-programmable-chip (SOPC) design. The Quartus II software includes HDL and schematic design entry, compilation and logic synthesis, full simulation and advanced timing analysis, SignalTap® II logic analyzer, and device configuration. See the *Design Software Selector Guide* for more details on the Quartus II software features.

The Quartus II software supports the Windows XP/2000/NT/98, Sun Solaris, Linux Red Hat v7.1 and HP-UX operating systems. It also supports seamless integration with industry-leading EDA tools through the NativeLink® interface.

## **Device Pin-Outs**

Stratix device pin-outs can be found on the Altera web site (www.altera.com).

# Ordering Information

Figure 5–1 describes the ordering codes for Stratix devices. For more information on a specific package, see the *Package Information for Stratix Devices* chapter.

| Fast Regional Clock External I/O Timing            | I                                                           |

|----------------------------------------------------|-------------------------------------------------------------|

| Parameters 4–49                                    | I/O                                                         |

| Global Clock External I/O Timing                   | Standards                                                   |

| Parameters 4–50 Regional Clock External I/O Timing | 1.5-V 4-14, 4-15                                            |

| Parameters 4–50                                    | I/O Specifications 4–4                                      |

| EP1S60 Devices                                     | 1.8-V                                                       |

| Column Pin                                         | I/O Specifications 4–4                                      |

| Fast Regional Clock External I/O Timing            | 2.5-V                                                       |

| Parameters 4–51                                    | I/O Specifications 4–3                                      |

| Global Clock External I/O Timing                   | 3.3-V 4–13                                                  |

| Parameters 4–52                                    | LVDS I/O Specifications 4–6                                 |

| Regional Clock External I/O Timing                 | PCI Specifications 4–9                                      |

| Parameters 4–51                                    | PCML Specifications 4–8                                     |

| M-RAM                                              | Advanced I/O Standard Support 2–122                         |

| Interface Locations 2–38                           | Column I/O Block Connection to the                          |

| Row Pin                                            | Interconnect 2–107                                          |

| Fast Regional Clock External I/O Timing            | Column Pin                                                  |

| Parameters 4–52                                    | Input Delay Adders 4–66                                     |

| Global Clock External I/O Timing                   | Control Signal Selection per IOE 2–109                      |

| Parameters 4–53                                    | CTT I/O Specifications 4–16                                 |

| Regional Clock External I/O Timing                 | Differential LVDS Input On-Chip                             |

| Parameters 4–53                                    | Termination 2–128                                           |

| EP1S80 Devices                                     | External I/O Delay Parameters 4–66                          |

| Column Pin                                         | GTL+ I/O Specifications 4–10<br>High-Speed Differential I/O |

| Fast Regional Clock External I/O Timing            | Support 2–130                                               |

| Parameters 4–54                                    | HyperTransport Technology                                   |

| Global Clock External I/O Timing                   | Specifications 4–9                                          |

| Parameters 4–55                                    | I/O Banks 2–125                                             |

| Regional Clock External I/O Timing                 | I/O Structure 2–104                                         |

| Parameters 4–54                                    | I/O Support by Bank 2–126                                   |

| Global Clock External I/O Timing                   | IOE Structure 2–105                                         |

| Parameters 4–56                                    | LVCMOS Specifications 4–3                                   |

| Row Pin                                            | LVDS Performance on Fast PLL                                |

| Fast Regional Clock External I/O Timing            | Input 2–103                                                 |

| Parameters 4–55                                    | LVPECL Specifications 4–8                                   |

| Regional Clock External I/O Timing                 | LVTTL Specifications 4–3                                    |

| Parameters 4–56                                    | MultiVolt I/O Interface 2–129                               |

|                                                    | MultiVolt I/O Support 2–130                                 |

| H                                                  | Output Delay Adders for Fast Slew Rate                      |

| HSTL                                               | on Column Pins 4–68                                         |

| Class I Specifications 4–14, 4–15                  | Output Delay Adders for Fast Slew Rate                      |

| Class II Specifications 4–14, 4–15                 | on Row Pins 4–69                                            |

| Ciass II Specifications 4-14, 4-15                 | Output Delay Adders for Slow Slew Rate                      |

|                                                    | on Column Pins 4–70                                         |

|                                                    | Package Options & I/O Pin Counts 1–4                        |

|                                                    | Receiver Input Waveforms for Differential                   |

Index-4 Altera Corporation