Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 1846                                                     |

| Number of Logic Elements/Cells | 18460                                                    |

| Total RAM Bits                 | 1669248                                                  |

| Number of I/O                  | 426                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 672-BBGA                                                 |

| Supplier Device Package        | 672-FBGA (27x27)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s20f672c7n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Features**

The Stratix family offers the following features:

- 10,570 to 79,040 LEs; see Table 1–1

- Up to 7,427,520 RAM bits (928,440 bytes) available without reducing logic resources

- TriMatrix<sup>™</sup> memory consisting of three RAM block sizes to implement true dual-port memory and first-in first-out (FIFO) buffers

- High-speed DSP blocks provide dedicated implementation of multipliers (faster than 300 MHz), multiply-accumulate functions, and finite impulse response (FIR) filters

- Up to 16 global clocks with 22 clocking resources per device region

- Up to 12 PLLs (four enhanced PLLs and eight fast PLLs) per device provide spread spectrum, programmable bandwidth, clock switchover, real-time PLL reconfiguration, and advanced multiplication and phase shifting

- Support for numerous single-ended and differential I/O standards

- High-speed differential I/O support on up to 116 channels with up to 80 channels optimized for 840 megabits per second (Mbps)

- Support for high-speed networking and communications bus standards including RapidIO, UTOPIA IV, CSIX, HyperTransport™ technology, 10G Ethernet XSBI, SPI-4 Phase 2 (POS-PHY Level 4), and SFI-4

- Differential on-chip termination support for LVDS

- Support for high-speed external memory, including zero bus turnaround (ZBT) SRAM, quad data rate (QDR and QDRII) SRAM, double data rate (DDR) SDRAM, DDR fast cycle RAM (FCRAM), and single data rate (SDR) SDRAM

- Support for 66-MHz PCI (64 and 32 bit) in -6 and faster speed-grade devices, support for 33-MHz PCI (64 and 32 bit) in -8 and faster speed-grade devices

- Support for 133-MHz PCI-X 1.0 in -5 speed-grade devices

- Support for 100-MHz PCI-X 1.0 in -6 and faster speed-grade devices

- Support for 66-MHz PCI-X 1.0 in -7 speed-grade devices

- Support for multiple intellectual property megafunctions from Altera MegaCore<sup>®</sup> functions and Altera Megafunction Partners Program (AMPP<sup>SM</sup>) megafunctions

- Support for remote configuration updates

The number of M512 RAM, M4K RAM, and DSP blocks varies by device along with row and column numbers and M-RAM blocks. Table 2–1 lists the resources available in Stratix devices.

| Table 2-1. | Table 2–1. Stratix Device Resources |                           |                 |                             |                |          |  |  |  |  |  |  |  |

|------------|-------------------------------------|---------------------------|-----------------|-----------------------------|----------------|----------|--|--|--|--|--|--|--|

| Device     | M512 RAM<br>Columns/Blocks          | M4K RAM<br>Columns/Blocks | M-RAM<br>Blocks | DSP Block<br>Columns/Blocks | LAB<br>Columns | LAB Rows |  |  |  |  |  |  |  |

| EP1S10     | 4 / 94                              | 2/60                      | 1               | 2/6                         | 40             | 30       |  |  |  |  |  |  |  |

| EP1S20     | 6 / 194                             | 2 / 82                    | 2               | 2/10                        | 52             | 41       |  |  |  |  |  |  |  |

| EP1S25     | 6 / 224                             | 3 / 138                   | 2               | 2/10                        | 62             | 46       |  |  |  |  |  |  |  |

| EP1S30     | 7 / 295                             | 3 / 171                   | 4               | 2/12                        | 67             | 57       |  |  |  |  |  |  |  |

| EP1S40     | 8 / 384                             | 3 / 183                   | 4               | 2 / 14                      | 77             | 61       |  |  |  |  |  |  |  |

| EP1S60     | 10 / 574                            | 4 / 292                   | 6               | 2 / 18                      | 90             | 73       |  |  |  |  |  |  |  |

| EP1S80     | 11 / 767                            | 4 / 364                   | 9               | 2 / 22                      | 101            | 91       |  |  |  |  |  |  |  |

## Logic Array Blocks

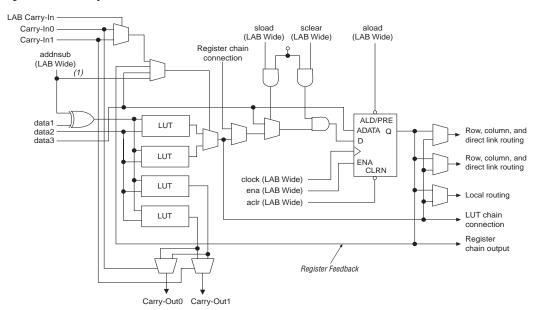

Each LAB consists of 10 LEs, LE carry chains, LAB control signals, local interconnect, LUT chain, and register chain connection lines. The local interconnect transfers signals between LEs in the same LAB. LUT chain connections transfer the output of one LE's LUT to the adjacent LE for fast sequential LUT connections within the same LAB. Register chain connections transfer the output of one LE's register to the adjacent LE's register within an LAB. The Quartus® II Compiler places associated logic within an LAB or adjacent LABs, allowing the use of local, LUT chain, and register chain connections for performance and area efficiency. Figure 2–2 shows the Stratix LAB.

## Dynamic Arithmetic Mode

The dynamic arithmetic mode is ideal for implementing adders, counters, accumulators, wide parity functions, and comparators. An LE in dynamic arithmetic mode uses four 2-input LUTs configurable as a dynamic adder/subtractor. The first two 2-input LUTs compute two summations based on a possible carry-in of 1 or 0; the other two LUTs generate carry outputs for the two chains of the carry select circuitry. As shown in Figure 2–7, the LAB carry-in signal selects either the carry-in0 or carry-in1 chain. The selected chain's logic level in turn determines which parallel sum is generated as a combinatorial or registered output. For example, when implementing an adder, the sum output is the selection of two possible calculated sums: data1 + data2 + carry-in0 or data1 + data2 + carry-in1. The other two LUTs use the data1 and data2 signals to generate two possible carry-out signals—one for a carry of 1 and the other for a carry of 0. The carry-in0 signal acts as the carry select for the carry-out 0 output and carry-in1 acts as the carry select for the carry-out1 output. LEs in arithmetic mode can drive out registered and unregistered versions of the LUT output.

The dynamic arithmetic mode also offers clock enable, counter enable, synchronous up/down control, synchronous clear, synchronous load, and dynamic adder/subtractor options. The LAB local interconnect data inputs generate the counter enable and synchronous up/down control signals. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. The Quartus II software automatically places any registers that are not used by the counter into other LABs. The addnsub LAB-wide signal controls whether the LE acts as an adder or subtractor.

Figure 2-7. LE in Dynamic Arithmetic Mode

*Note to Figure 2–7:*

(1) The addnsub signal is tied to the carry input for the first LE of a carry chain only.

## Carry-Select Chain

The carry-select chain provides a very fast carry-select function between LEs in arithmetic mode. The carry-select chain uses the redundant carry calculation to increase the speed of carry functions. The LE is configured to calculate outputs for a possible carry-in of 1 and carry-in of 0 in parallel. The carry-in0 and carry-in1 signals from a lower-order bit feed forward into the higher-order bit via the parallel carry chain and feed into both the LUT and the next portion of the carry chain. Carry-select chains can begin in any LE within an LAB.

The speed advantage of the carry-select chain is in the parallel precomputation of carry chains. Since the LAB carry-in selects the precomputed carry chain, not every LE is in the critical path. Only the propagation delay between LAB carry-in generation (LE 5 and LE 10) are now part of the critical path. This feature allows the Stratix architecture to implement high-speed counters, adders, multipliers, parity functions, and comparators of arbitrary width.

M4K RAM blocks support byte writes when the write port has a data width of 16, 18, 32, or 36 bits. The byte enables allow the input data to be masked so the device can write to specific bytes. The unwritten bytes retain the previous written value. Table 2–7 summarizes the byte selection.

| Table 2–7. Byte Enable for M4K Blocks Notes (1), (2) |            |            |  |  |  |  |  |  |  |

|------------------------------------------------------|------------|------------|--|--|--|--|--|--|--|

| byteena[30]                                          | datain ×18 | datain ×36 |  |  |  |  |  |  |  |

| [0] = 1                                              | [80]       | [80]       |  |  |  |  |  |  |  |

| [1] = 1                                              | [179]      | [179]      |  |  |  |  |  |  |  |

| [2] = 1                                              | _          | [2618]     |  |  |  |  |  |  |  |

| [3] = 1                                              | _          | [3527]     |  |  |  |  |  |  |  |

*Notes to Table 2–7:*

- (1) Any combination of byte enables is possible.

- (2) Byte enables can be used in the same manner with 8-bit words, i.e., in  $\times$  16 and  $\times$  32 modes.

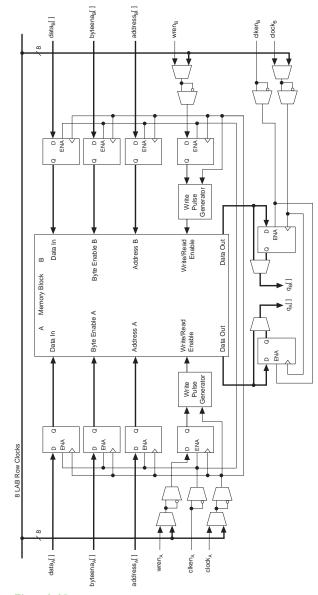

The M4K RAM blocks allow for different clocks on their inputs and outputs. Either of the two clocks feeding the block can clock M4K RAM block registers (renwe, address, byte enable, datain, and output registers). Only the output register can be bypassed. The eight labclk signals or local interconnects can drive the control signals for the A and B ports of the M4K RAM block. LEs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals, as shown in Figure 2–17.

The R4, R8, C4, C8, and direct link interconnects from adjacent LABs drive the M4K RAM block local interconnect. The M4K RAM blocks can communicate with LABs on either the left or right side through these row resources or with LAB columns on either the right or left with the column resources. Up to 10 direct link input connections to the M4K RAM Block are possible from the left adjacent LABs and another 10 possible from the right adjacent LAB. M4K RAM block outputs can also connect to left and right LABs through 10 direct link interconnects each. Figure 2–18 shows the M4K RAM block to logic array interface.

Figure 2–25. Input/Output Clock Mode in True Dual-Port Mode Notes (1), (2)

Notes to Figure 2-25:

- (1) All registers shown have asynchronous clear ports.

- (2) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

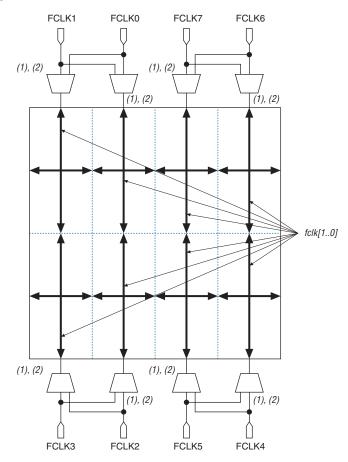

Figure 2–45. EP1S30 Device Fast Regional Clock Pin Connections to Fast Regional Clocks

Notes to Figure 2-45:

- (1) This is a set of two multiplexers.

- (2) In addition to the FCLK pin inputs, there is also an input from the I/O interconnect.

### Combined Resources

Within each region, there are 22 distinct dedicated clocking resources consisting of 16 global clock lines, four regional clock lines, and two fast regional clock lines. Multiplexers are used with these clocks to form eight bit busses to drive LAB row clocks, column IOE clocks, or row IOE clocks. Another multiplexer is used at the LAB level to select two of the eight row clocks to feed the LE registers within the LAB. See Figure 2–46.

☐ FPLL9CLK

Figure 2–50. Global & Regional Clock Connections from Side Pins & Fast PLL Outputs Note (1), (2) RCLK1 RCLK9 G1 G3 G8 G10 G2 🛕 RCLK0 ▲ G0 🛕 G9 ▲ G11 ▲ RCLK8 ▲ FPLL7CLK \_ ☐ FPLL10CLK 10 10 PLL 7 /1 /1 PLL 10 *g*0 *g*0 ☐ CLK10 CLK0 [ 10 10 CLK1 □ ☐ CLK11 PLL 1 /1 /1 PLL 4 *g*0 *g*0 □ CLK8 CLK2 CLK3 10 10 /1 PLL 3 PI 1 2 /1 g0 g0

Figure 2–50 shows the global and regional clocking from the PLL outputs and the CLK pins.

*Notes to Figure 2–50:*

FPLL8CLK \_\_

PLL 8 /1

g0

(1) PLLs 1 to 4 and 7 to 10 are fast PLLs. PLLs 5, 6, 11, and 12 are enhanced PLLs.

RCLK4

RCLK5

Regional

Clocks

(2) The global or regional clocks in a fast PLL's quadrant can drive the fast PLL input. A pin or other PLL must drive the global or regional source. The source cannot be driven by internally generated logic before driving the fast PLL.

Global

Clocks

Figure 2–51 shows the global and regional clocking from enhanced PLL outputs and top CLK pins.

RCLK14

RCLK15

Regional

Clocks

/1 PLL 9

During switchover, the PLL VCO continues to run and will either slow down or speed up, generating frequency drift on the PLL outputs. The clock switchover transitions without any glitches. After the switch, there is a finite resynchronization period to lock onto new clock as the VCO ramps up. The exact amount of time it takes for the PLL to relock relates to the PLL configuration and may be adjusted by using the programmable bandwidth feature of the PLL. The specification for the maximum time to relock is  $100~\mu s$ .

For more information on clock switchover, see *AN 313, Implementing Clock Switchover in Stratix & Stratix GX Devices*.

## PLL Reconfiguration

The PLL reconfiguration feature enables system logic to change Stratix device enhanced PLL counters and delay elements without reloading a Programmer Object File (.pof). This provides considerable flexibility for frequency synthesis, allowing real-time PLL frequency and output clock delay variation. You can sweep the PLL output frequencies and clock delay in prototype environments. The PLL reconfiguration feature can also dynamically or intelligently control system clock speeds or  $t_{\rm CO}$  delays in end systems.

Clock delay elements at each PLL output port implement variable delay. Figure 2–54 shows a diagram of the overall dynamic PLL control feature for the counters and the clock delay elements. The configuration time is less than 20 µs for the enhanced PLL using a input shift clock rate of 22 MHz. The charge pump, loop filter components, and phase shifting using VCO phase taps cannot be dynamically adjusted.

Table 2–37 shows the number of channels that each fast PLL can clock in EP1S10, EP1S20, and EP1S25 devices. Tables 2–38 through Table 2–41 show this information for EP1S30, EP1S40, EP1S60, and EP1S80 devices.

| Table 2- | 37. EP1\$10, EP1\$20 & I | EP1S25 Device l | Differential | Channels (      | Part 1 of | <b>2)</b> Note ( | 1)       |       |

|----------|--------------------------|-----------------|--------------|-----------------|-----------|------------------|----------|-------|

|          |                          | Transmitter/    | Total        | Maximum         |           | Center F         | ast PLLs |       |

| Device   | Package                  | Receiver        | Channels     | Speed<br>(Mbps) | PLL 1     | PLL 2            | PLL 3    | PLL 4 |

| EP1S10   | 484-pin FineLine BGA     | Transmitter (2) | 20           | 840 (4)         | 5         | 5                | 5        | 5     |

|          |                          |                 |              | 840 (3)         | 10        | 10               | 10       | 10    |

|          |                          | Receiver        | 20           | 840 (4)         | 5         | 5                | 5        | 5     |

|          |                          |                 |              | 840 (3)         | 10        | 10               | 10       | 10    |

|          | 672-pin FineLine BGA     | Transmitter (2) | 36           | 624 (4)         | 9         | 9                | 9        | 9     |

|          | 672-pin BGA              |                 |              | 624 (3)         | 18        | 18               | 18       | 18    |

|          |                          | Receiver        | 36           | 624 (4)         | 9         | 9                | 9        | 9     |

|          |                          |                 |              | 624 (3)         | 18        | 18               | 18       | 18    |

|          | 780-pin FineLine BGA     | Transmitter (2) | 44           | 840 (4)         | 11        | 11               | 11       | 11    |

|          |                          |                 |              | 840 (3)         | 22        | 22               | 22       | 22    |

|          |                          | Receiver        | 44           | 840 (4)         | 11        | 11               | 11       | 11    |

|          |                          |                 |              | 840 (3)         | 22        | 22               | 22       | 22    |

| EP1S20   | 484-pin FineLine BGA     | Transmitter (2) | 24           | 840 (4)         | 6         | 6                | 6        | 6     |

|          |                          |                 |              | 840 (3)         | 12        | 12               | 12       | 12    |

|          |                          | Receiver        | 20           | 840 (4)         | 5         | 5                | 5        | 5     |

|          |                          |                 |              | 840 (3)         | 10        | 10               | 10       | 10    |

|          | 672-pin FineLine BGA     | Transmitter (2) | 48           | 624 (4)         | 12        | 12               | 12       | 12    |

|          | 672-pin BGA              |                 |              | 624 (3)         | 24        | 24               | 24       | 24    |

|          |                          | Receiver        | 50           | 624 (4)         | 13        | 12               | 12       | 13    |

|          |                          |                 |              | 624 (3)         | 25        | 25               | 25       | 25    |

|          | 780-pin FineLine BGA     | Transmitter (2) | 66           | 840 (4)         | 17        | 16               | 16       | 17    |

|          |                          |                 |              | 840 (3)         | 33        | 33               | 33       | 33    |

|          |                          | Receiver        | 66           | 840 (4)         | 17        | 16               | 16       | 17    |

|          |                          |                 |              | 840 (3)         | 33        | 33               | 33       | 33    |

| Table 2-40.           | Table 2–40. EP1S60 Differential Channels (Part 2 of 2) Note (1) |                       |                 |                  |            |            |            |                           |            |            |        |  |  |

|-----------------------|-----------------------------------------------------------------|-----------------------|-----------------|------------------|------------|------------|------------|---------------------------|------------|------------|--------|--|--|

|                       | Transmitter/<br>Receiver                                        | Total<br>Channels     | Maximum         | Center Fast PLLs |            |            |            | Corner Fast PLLs (2), (3) |            |            |        |  |  |

| Package               |                                                                 |                       | Speed<br>(Mbps) | PLL1             | PLL2       | PLL3       | PLL4       | PLL7                      | PLL8       | PLL9       | PLL10  |  |  |

| 1,020-pin<br>FineLine | Transmitter (4)                                                 | 80 (12)<br><i>(7)</i> | 840             | 12<br>(2)        | 10<br>(4)  | 10<br>(4)  | 12<br>(2)  | 20                        | 20         | 20         | 20     |  |  |

| BGA                   |                                                                 |                       | 840 (5), (8)    | 22<br>(6)        | 22<br>(6)  | 22<br>(6)  | 22<br>(6)  | 20                        | 20         | 20         | 20     |  |  |

|                       | Receiver                                                        | 80 (10)<br><i>(7)</i> | 840             | 20               | 20         | 20         | 20         | 12<br>(8)                 | 10<br>(10) | 10<br>(10) | 12 (8) |  |  |

|                       |                                                                 |                       | 840 (5), (8)    | 40               | 40         | 40         | 40         | 12<br>(8)                 | 10<br>(10) | 10<br>(10) | 12 (8) |  |  |

| 1,508-pin<br>FineLine | Transmitter (4)                                                 | 80 (36)<br><i>(7)</i> | 840             | 12<br>(8)        | 10<br>(10) | 10<br>(10) | 12<br>(8)  | 20                        | 20         | 20         | 20     |  |  |

| BGA                   |                                                                 |                       | 840 (5),(8)     | 22<br>(18)       | 22<br>(18) | 22<br>(18) | 22<br>(18) | 20                        | 20         | 20         | 20     |  |  |

|                       | Receiver                                                        | 80 (36)<br>(7)        | 840             | 20               | 20         | 20         | 20         | 12<br>(8)                 | 10<br>(10) | 10<br>(10) | 12 (8) |  |  |

|                       |                                                                 |                       | 840 (5),(8)     | 40               | 40         | 40         | 40         | 12<br>(8)                 | 10<br>(10) | 10<br>(10) | 12 (8) |  |  |

| Table 2-41.           | Table 2–41. EP1S80 Differential Channels (Part 1 of 2) Note (1) |                |                 |           |           |           |           |           |           |           |         |  |  |  |

|-----------------------|-----------------------------------------------------------------|----------------|-----------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|---------|--|--|--|

|                       | Transmitter/                                                    | Total          | Maximum         | C         | enter F   | ast PLI   | -S        | Corr      | ner Fas   | t PLLs (2 | 2), (3) |  |  |  |

| Package               | Receiver                                                        | Channels       | Speed<br>(Mbps) | PLL1      | PLL2      | PLL3      | PLL4      | PLL7      | PLL8      | PLL9      | PLL10   |  |  |  |

| 956-pin Transmitter   | 80 (40)                                                         | 840            | 10              | 10        | 10        | 10        | 20        | 20        | 20        | 20        |         |  |  |  |

| BGA                   | (4)                                                             | (7)            | 840 (5),(8)     | 20        | 20        | 20        | 20        | 20        | 20        | 20        | 20      |  |  |  |

|                       | Receiver                                                        | 80             | 840             | 20        | 20        | 20        | 20        | 10        | 10        | 10        | 10      |  |  |  |

|                       |                                                                 |                | 840 (5),(8)     | 40        | 40        | 40        | 40        | 10        | 10        | 10        | 10      |  |  |  |

| 1,020-pin<br>FineLine | Transmitter (4)                                                 | 92 (12)<br>(7) | 840             | 10<br>(2) | 10<br>(4) | 10<br>(4) | 10<br>(2) | 20        | 20        | 20        | 20      |  |  |  |

| BGA                   |                                                                 |                | 840 (5),(8)     | 20<br>(6) | 20<br>(6) | 20<br>(6) | 20<br>(6) | 20        | 20        | 20        | 20      |  |  |  |

|                       | Receiver                                                        | 90 (10)<br>(7) | 840             | 20        | 20        | 20        | 20        | 10<br>(2) | 10<br>(3) | 10 (3)    | 10 (2)  |  |  |  |

|                       |                                                                 |                | 840 (5),(8)     | 40        | 40        | 40        | 40        | 10<br>(2) | 10<br>(3) | 10 (3)    | 10 (2)  |  |  |  |

| Table 2–41. EP1S80 Differential Channels (Part 2 of 2) Note (1) |                 |                       |                 |            |            |            |            |                           |            |            |            |  |  |

|-----------------------------------------------------------------|-----------------|-----------------------|-----------------|------------|------------|------------|------------|---------------------------|------------|------------|------------|--|--|

| Package                                                         | Transmitter/    | Total                 | Maximum         | C          | enter F    | ast PLI    | .s         | Corner Fast PLLs (2), (3) |            |            |            |  |  |

|                                                                 | Receiver        | Channels              | Speed<br>(Mbps) | PLL1       | PLL2       | PLL3       | PLL4       | PLL7                      | PLL8       | PLL9       | PLL10      |  |  |

| 1,508-pin<br>FineLine                                           | Transmitter (4) | 80 (72)<br><i>(7)</i> | 840             | 10<br>(10) | 10<br>(10) | 10<br>(10) | 10<br>(10) | 20<br>(8)                 | 20<br>(8)  | 20 (8)     | 20 (8)     |  |  |

| BGA                                                             |                 |                       | 840 (5),(8)     | 20<br>(20) | 20<br>(20) | 20<br>(20) | 20<br>(20) | 20<br>(8)                 | 20<br>(8)  | 20 (8)     | 20 (8)     |  |  |

|                                                                 | Receiver        | 80 (56)<br>(7)        | 840             | 20         | 20         | 20         | 20         | 10<br>(14)                | 10<br>(14) | 10<br>(14) | 10<br>(14) |  |  |

|                                                                 |                 |                       | 840 (5),(8)     | 40         | 40         | 40         | 40         | 10<br>(14)                | 10<br>(14) | 10<br>(14) | 10<br>(14) |  |  |

## Notes to Tables 2-38 through 2-41:

- (1) The first row for each transmitter or receiver reports the number of channels driven directly by the PLL. The second row below it shows the maximum channels a PLL can drive if cross bank channels are used from the adjacent center PLL. For example, in the 780-pin FineLine BGA EP1S30 device, PLL 1 can drive a maximum of 18 transmitter channels at 840 Mbps or a maximum of 35 transmitter channels at 840 Mbps. The Quartus II software may also merge transmitter and receiver PLLs when a receiver is driving a transmitter. In this case, one fast PLL can drive both the maximum numbers of receiver and transmitter channels.

- (2) Some of the channels accessible by the center fast PLL and the channels accessible by the corner fast PLL overlap. Therefore, the total number of channels is not the addition of the number of channels accessible by PLLs 1, 2, 3, and 4 with the number of channels accessible by PLLs 7, 8, 9, and 10. For more information on which channels overlap, see the Stratix device pin-outs at www.altera.com.

- (3) The corner fast PLLs in this device support a data rate of 840 Mbps for channels labeled "high" speed in the device pin-outs at www.altera.com.

- (4) The numbers of channels listed include the transmitter clock output (tx\_outclock) channel. An extra data channel can be used if a DDR clock is needed.

- (5) These channels span across two I/O banks per side of the device. When a center PLL clocks channels in the opposite bank on the same side of the device it is called cross-bank PLL support. Both center PLLs can clock cross-bank channels simultaneously if say PLL\_1 is clocking all receiver channels and PLL\_2 is clocking all transmitter channels. You cannot have two adjacent PLLs simultaneously clocking cross-bank receiver channels or two adjacent PLLs simultaneously clocking transmitter channels. Cross-bank allows for all receiver channels on one side of the device to be clocked on one clock while all transmitter channels on the device are clocked on the other center PLL. Crossbank PLLs are supported at full-speed, 840 Mbps. For wire-bond devices, the full-speed is 624 Mbps.

- (6) PLLs 7, 8, 9, and 10 are not available in this device.

- (7) The number in parentheses is the number of slow-speed channels, guaranteed to operate at up to 462 Mbps. These channels are independent of the high-speed differential channels. For the location of these channels, see the device pin-outs at www.altera.com.

- (8) See the Stratix device pin-outs at www.altera.com. Channels marked "high" speed are 840 MBps and "low" speed channels are 462 MBps.

The high-speed differential I/O circuitry supports the following high speed I/O interconnect standards and applications:

- UTOPIA IV

- SPI-4 Phase 2 (POS-PHY Level 4)

- SFI-4

- 10G Ethernet XSBI

While in the factory configuration, the factory-configuration logic performs the following operations:

- Loads a remote update-control register to determine the page address of the new application configuration

- Determines whether to enable a user watchdog timer for the application configuration

- Determines what the watchdog timer setting should be if it is enabled

The user watchdog timer is a counter that must be continually reset within a specific amount of time in the user mode of an application configuration to ensure that valid configuration occurred during a remote update. Only valid application configurations designed for remote update can reset the user watchdog timer in user mode. If a valid application configuration does not reset the user watchdog timer in a specific amount of time, the timer updates a status register and loads the factory configuration. The user watchdog timer is automatically disabled for factory configurations.

If an error occurs in loading the application configuration, the configuration logic writes a status register to specify the cause of the error. Once this occurs, the Stratix device automatically loads the factory configuration, which reads the status register and determines the reason for reconfiguration. Based on the reason, the factory configuration will take appropriate steps and will write the remote update control register to specify the next application configuration page to be loaded.

When the Stratix device successfully loads the application configuration, it enters into user mode. The Stratix device then executes the main application of the user. Intellectual property (IP), such as a Nios® (16-bit ISA) and Nios® II (32-bit ISA) embedded processors, can help the Stratix device determine when remote update is coming. The Nios embedded processor or user logic receives incoming data, writes it to the configuration device, and loads the factory configuration. The factory configuration will read the remote update status register and determine the valid application configuration to load. Figure 3–2 shows the Stratix remote update. Figure 3–3 shows the transition diagram for remote update mode.

Figure 4–2. Transmitter Output Waveforms for Differential I/O Standards

# Single-Ended Waveform Positive Channel (p) = $V_{OH}$ $V_{CM}$ Negative Channel (n) = $V_{OL}$ Ground

## Differential Waveform $V_{OD} = 0 \text{ V}$ $V_{OD} = 0 \text{ V}$

Tables 4–10 through 4–33 recommend operating conditions, DC operating conditions, and capacitance for 1.5-V Stratix devices.

| Table 4–10. 3.3-V LVDS I/O Specifications (Part 1 of 2) |                                                 |                                                                                 |         |         |         |      |  |  |  |  |  |

|---------------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------|---------|---------|---------|------|--|--|--|--|--|

| Symbol                                                  | Parameter                                       | Conditions                                                                      | Minimum | Typical | Maximum | Unit |  |  |  |  |  |

| V <sub>CCIO</sub>                                       | I/O supply voltage                              |                                                                                 | 3.135   | 3.3     | 3.465   | V    |  |  |  |  |  |

| V <sub>ID</sub> (6)                                     | Input differential voltage swing (single-ended) | $0.1 \text{ V} \leq \text{V}_{\text{CM}} < 1.1 \text{ V}$<br>W = 1  through  10 | 300     |         | 1,000   | mV   |  |  |  |  |  |

|                                                         |                                                 | 1.1 V $\leq$ V <sub>CM</sub> $\leq$ 1.6 V $W = 1$                               | 200     |         | 1,000   | mV   |  |  |  |  |  |

|                                                         |                                                 | 1.1 V $\leq$ V <sub>CM</sub> $\leq$ 1.6 V<br>W = 2 through 10                   | 100     |         | 1,000   | mV   |  |  |  |  |  |

|                                                         |                                                 | 1.6 V < $V_{CM} \le 1.8 \text{ V}$<br>W = 1  through  10                        | 300     |         | 1,000   | mV   |  |  |  |  |  |

| Symbol                  | Parameter                                                                   | Conditions                                                                                 | Typical | Maximum | Unit  |    |

|-------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------|---------|-------|----|

| V <sub>ICM</sub>        | Input common mode voltage (6)                                               | LVDS<br>$0.3 \text{ V} \leq \text{V}_{\text{ID}} \leq 1.0 \text{ V}$<br>W = 1  through  10 | 100     |         | 1,100 | mV |

|                         |                                                                             | LVDS<br>$0.3 \text{ V} \leq V_{\text{ID}} \leq 1.0 \text{ V}$<br>W = 1  through  10        | 1,600   |         | 1,800 | mV |

|                         |                                                                             | LVDS<br>0.2 V ≤V <sub>ID</sub> ≤1.0 V<br>W = 1                                             | 1,100   |         | 1,600 | mV |

|                         |                                                                             | LVDS<br>$0.1 \text{ V} \leq V_{\text{ID}} \leq 1.0 \text{ V}$<br>W = 2  through  10        | 1,100   |         | 1,600 | mV |

| V <sub>OD</sub> (1)     | Output differential voltage (single-ended)                                  | R <sub>L</sub> = 100 Ω                                                                     | 250     | 375     | 550   | mV |

| Δ V <sub>OD</sub>       | Change in V <sub>OD</sub> between high and low                              | R <sub>L</sub> = 100 Ω                                                                     |         |         | 50    | mV |

| V <sub>OCM</sub>        | Output common mode voltage                                                  | $R_L = 100 \Omega$                                                                         | 1,125   | 1,200   | 1,375 | mV |

| $\Delta V_{\text{OCM}}$ | Change in V <sub>OCM</sub> between high and low                             | $R_L = 100 \Omega$                                                                         |         |         | 50    | mV |

| R <sub>L</sub>          | Receiver differential input discrete resistor (external to Stratix devices) |                                                                                            | 90      | 100     | 110   | Ω  |

|                          | Table 4–42. M-RAM Block Internal Timing Microparameter Descriptions (Part 2 of 2)                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Symbol                   | Parameter                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| $t_{MRAMDATABH}$         | B port hold time after clock                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| t <sub>MRAMADDRBSU</sub> | B port address setup time before clock                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| t <sub>MRAMADDRBH</sub>  | B port address hold time after clock                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| t <sub>MRAMDATACO1</sub> | Clock-to-output delay when using output registers                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| t <sub>MRAMDATACO2</sub> | Clock-to-output delay without output registers                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| † <sub>MRAMCLKHL</sub>   | Register minimum clock high or low time. This is a limit on the min time for the clock on the registers in these blocks. The actual performance is dependent upon the internal point-to-point delays in the blocks and may give slower performance as shown in Table 4–36 on page 4–20 and as reported by the timing analyzer in the Quartus II software. |  |  |  |  |  |  |  |  |

| t <sub>MRAMCLR</sub>     | Minimum clear pulse width.                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| Table 4-65. I         | EP1S20 Ext | ernal I/O T | iming on F | Row Pins U     | sing Regio | nal Clock I | letworks / | Vote (1) |      |

|-----------------------|------------|-------------|------------|----------------|------------|-------------|------------|----------|------|

| D                     | -5 Spee    | d Grade     | -6 Spee    | -6 Speed Grade |            | d Grade     | -8 Spee    | Unit     |      |

| Parameter             | Min        | Max         | Min        | Max            | Min        | Max         | Min        | Max      | Unit |

| t <sub>INSU</sub>     | 1.815      |             | 1.967      |                | 2.258      |             | NA         |          | ns   |

| t <sub>INH</sub>      | 0.000      |             | 0.000      |                | 0.000      |             | NA         |          | ns   |

| t <sub>OUTCO</sub>    | 2.633      | 5.235       | 2.663      | 5.595          | 2.663      | 6.070       | NA         | NA       | ns   |

| t <sub>XZ</sub>       | 2.660      | 5.289       | 2.660      | 5.651          | 2.660      | 6.138       | NA         | NA       | ns   |

| t <sub>ZX</sub>       | 2.660      | 5.289       | 2.660      | 5.651          | 2.660      | 6.138       | NA         | NA       | ns   |

| t <sub>INSUPLL</sub>  | 1.060      |             | 1.112      |                | 1.277      |             | NA         |          | ns   |

| t <sub>INHPLL</sub>   | 0.000      |             | 0.000      |                | 0.000      |             | NA         |          | ns   |

| t <sub>OUTCOPLL</sub> | 1.325      | 2.770       | 1.325      | 2.908          | 1.325      | 2.978       | NA         | NA       | ns   |

| t <sub>XZPLL</sub>    | 1.352      | 2.824       | 1.352      | 2.964          | 1.352      | 3.046       | NA         | NA       | ns   |

| t <sub>ZXPLL</sub>    | 1.352      | 2.824       | 1.352      | 2.964          | 1.352      | 3.046       | NA         | NA       | ns   |

| Table 4–66. I         | Table 4–66. EP1S20 External I/O Timing on Row Pins Using Global Clock Networks Note (1) |         |         |                |       |         |         |      |       |  |  |  |  |

|-----------------------|-----------------------------------------------------------------------------------------|---------|---------|----------------|-------|---------|---------|------|-------|--|--|--|--|

| Doromotor             | -5 Spee                                                                                 | d Grade | -6 Spee | -6 Speed Grade |       | d Grade | -8 Spee | Unit |       |  |  |  |  |

| Parameter             | Min                                                                                     | Max     | Min     | Max            | Min   | Max     | Min     | Max  | UIIIL |  |  |  |  |

| t <sub>INSU</sub>     | 1.742                                                                                   |         | 1.887   |                | 2.170 |         | NA      |      | ns    |  |  |  |  |

| t <sub>INH</sub>      | 0.000                                                                                   |         | 0.000   |                | 0.000 |         | NA      |      | ns    |  |  |  |  |

| t <sub>OUTCO</sub>    | 2.674                                                                                   | 5.308   | 2.674   | 5.675          | 2.674 | 6.158   | NA      | NA   | ns    |  |  |  |  |

| t <sub>XZ</sub>       | 2.701                                                                                   | 5.362   | 2.701   | 5.731          | 2.701 | 6.226   | NA      | NA   | ns    |  |  |  |  |

| t <sub>ZX</sub>       | 2.701                                                                                   | 5.362   | 2.701   | 5.731          | 2.701 | 6.226   | NA      | NA   | ns    |  |  |  |  |

| t <sub>INSUPLL</sub>  | 1.353                                                                                   |         | 1.418   |                | 1.613 |         | NA      |      | ns    |  |  |  |  |

| t <sub>INHPLL</sub>   | 0.000                                                                                   |         | 0.000   |                | 0.000 |         | NA      |      | ns    |  |  |  |  |

| t <sub>OUTCOPLL</sub> | 1.158                                                                                   | 2.447   | 1.158   | 2.602          | 1.158 | 2.642   | NA      | NA   | ns    |  |  |  |  |

| t <sub>XZPLL</sub>    | 1.185                                                                                   | 2.531   | 1.158   | 2.602          | 1.185 | 2.710   | NA      | NA   | ns    |  |  |  |  |

| t <sub>ZXPLL</sub>    | 1.185                                                                                   | 2.531   | 1.158   | 2.602          | 1.185 | 2.710   | NA      | NA   | ns    |  |  |  |  |

*Note to Tables 4–61 to 4–66:*

<sup>(1)</sup> Only EP1S25, EP1S30, and EP1S40 have a speed grade of -8.

| Table 4–83. EP1S40 External I/O Timing on Row Pins Using Regional Clock Networks |                |       |                |       |                |       |                |       |      |

|----------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-------|------|

| Parameter                                                                        | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | 11   |

|                                                                                  | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max   | Unit |

| t <sub>INSU</sub>                                                                | 2.349          |       | 2.526          |       | 2.898          |       | 2.952          |       | ns   |

| t <sub>INH</sub>                                                                 | 0.000          |       | 0.000          |       | 0.000          |       | 0.000          |       | ns   |

| t <sub>OUTCO</sub>                                                               | 2.725          | 5.381 | 2.725          | 5.784 | 2.725          | 6.290 | 2.725          | 7.426 | ns   |

| t <sub>XZ</sub>                                                                  | 2.752          | 5.435 | 2.752          | 5.840 | 2.752          | 6.358 | 2.936          | 7.508 | ns   |

| t <sub>ZX</sub>                                                                  | 2.752          | 5.435 | 2.752          | 5.840 | 2.752          | 6.358 | 2.936          | 7.508 | ns   |

| t <sub>INSUPLL</sub>                                                             | 1.328          |       | 1.322          |       | 1.605          |       | 1.883          |       | ns   |

| t <sub>INHPLL</sub>                                                              | 0.000          |       | 0.000          |       | 0.000          |       | 0.000          |       | ns   |

| t <sub>OUTCOPLL</sub>                                                            | 1.169          | 2.502 | 1.169          | 2.698 | 1.169          | 2.650 | 1.169          | 2.691 | ns   |

| t <sub>XZPLL</sub>                                                               | 1.196          | 2.556 | 1.196          | 2.754 | 1.196          | 2.718 | 1.196          | 2.773 | ns   |

| t <sub>ZXPLL</sub>                                                               | 1.196          | 2.556 | 1.196          | 2.754 | 1.196          | 2.718 | 1.196          | 2.773 | ns   |

| Table 4–84. EP1S40 External I/O Timing on Row Pins Using Global Clock Networks |                |       |                |       |                |       |                |       |      |

|--------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-------|------|

| Parameter                                                                      | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | 11:4 |

|                                                                                | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max   | Unit |

| t <sub>INSU</sub>                                                              | 2.020          |       | 2.171          |       | 2.491          |       | 2.898          |       | ns   |

| t <sub>INH</sub>                                                               | 0.000          |       | 0.000          |       | 0.000          |       | 0.000          |       | ns   |

| t <sub>OUTCO</sub>                                                             | 2.912          | 5.710 | 2.912          | 6.139 | 2.912          | 6.697 | 2.931          | 7.480 | ns   |

| t <sub>XZ</sub>                                                                | 2.939          | 5.764 | 2.939          | 6.195 | 2.939          | 6.765 | 2.958          | 7.562 | ns   |

| t <sub>ZX</sub>                                                                | 2.939          | 5.764 | 2.939          | 6.195 | 2.939          | 6.765 | 2.958          | 7.562 | ns   |

| t <sub>INSUPLL</sub>                                                           | 1.370          |       | 1.368          |       | 1.654          |       | 1.881          |       | ns   |

| t <sub>INHPLL</sub>                                                            | 0.000          |       | 0.000          |       | 0.000          |       | 0.000          |       | ns   |

| t <sub>OUTCOPLL</sub>                                                          | 1.144          | 2.460 | 1.144          | 2.652 | 1.144          | 2.601 | 1.170          | 2.693 | ns   |

| t <sub>XZPLL</sub>                                                             | 1.171          | 2.514 | 1.171          | 2.708 | 1.171          | 2.669 | 1.197          | 2.775 | ns   |

| t <sub>ZXPLL</sub>                                                             | 1.171          | 2.514 | 1.171          | 2.708 | 1.171          | 2.669 | 1.197          | 2.775 | ns   |

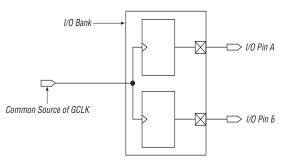

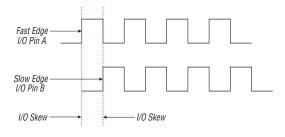

## Definition of I/O Skew

I/O skew is defined as the absolute value of the worst-case difference in clock-to-out times ( $t_{\rm CO}$ ) between any two output registers fed by a common clock source.

I/O bank skew is made up of the following components:

- Clock network skews: This is the difference between the arrival times of the clock at the clock input port of the two IOE registers.

- Package skews: This is the package trace length differences between (I/O pad A to I/O pin A) and (I/O pad B to I/O pin B).

Figure 4–5 shows an example of two IOE registers located in the same bank, being fed by a common clock source. The clock can come from an input pin or from a PLL output.

Figure 4-5. I/O Skew within an I/O Bank

| Table 4–97. Output Pin Timing Skew Definitions (Part 2 of 2) |                                                                       |  |  |  |  |  |

|--------------------------------------------------------------|-----------------------------------------------------------------------|--|--|--|--|--|

| Symbol                                                       | Definition                                                            |  |  |  |  |  |

| t <sub>LR_HIO</sub>                                          | Across all HIO banks (1, 2, 5, 6); across four similar type I/O banks |  |  |  |  |  |

| t <sub>TB_VIO</sub>                                          | Across all VIO banks (3, 4, 7, 8); across four similar type I/O banks |  |  |  |  |  |

| t <sub>OVERALL</sub>                                         | Output timing skew for all I/O pins on the device.                    |  |  |  |  |  |

### Notes to Table 4-97:

- (1) See Figure 4–5 on page 4–57.

- (2) See Figure 4–6 on page 4–58.

Table 4–98 shows the I/O skews when using the same global or regional clock to feed IOE registers in I/O banks around each device. These values can be used for calculating the timing budget on the output (write) side of a memory interface. These values already factor in the package skew.

| Table 4–98. Output Skew for Stratix by Device Density |                  |        |                 |  |  |  |  |

|-------------------------------------------------------|------------------|--------|-----------------|--|--|--|--|

| Cumbal                                                | Skew (ps) (1)    |        |                 |  |  |  |  |

| Symbol                                                | EP1S10 to EP1S30 | EP1S40 | EP1S60 & EP1S80 |  |  |  |  |

| t <sub>SB_HIO</sub>                                   | 90               | 290    | 500             |  |  |  |  |

| t <sub>SB_VIO</sub>                                   | 160              | 290    | 500             |  |  |  |  |

| t <sub>SS_HIO</sub>                                   | 90               | 460    | 600             |  |  |  |  |

| t <sub>SS_VIO</sub>                                   | 180              | 520    | 630             |  |  |  |  |

| t <sub>LR_HIO</sub>                                   | 150              | 490    | 600             |  |  |  |  |

| t <sub>TB_VIO</sub>                                   | 190              | 580    | 670             |  |  |  |  |

| t <sub>OVERALL</sub>                                  | 430              | 630    | 880             |  |  |  |  |

Note to Table 4-98:

(1) The skew numbers in Table 4–98 account for worst case package skews.