Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 1846                                                     |

| Number of Logic Elements/Cells | 18460                                                    |

| Total RAM Bits                 | 1669248                                                  |

| Number of I/O                  | 426                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                       |

| Package / Case                 | 672-BBGA                                                 |

| Supplier Device Package        | 672-FBGA (27x27)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s20f672i7n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 1–1. Stratix Device Features — EP1S10, EP1S20, EP1S25, EP1S30 |         |           |           |           |  |  |  |  |  |

|---------------------------------------------------------------------|---------|-----------|-----------|-----------|--|--|--|--|--|

| Feature                                                             | EP1S10  | EP1S20    | EP1S25    | EP1S30    |  |  |  |  |  |

| LEs                                                                 | 10,570  | 18,460    | 25,660    | 32,470    |  |  |  |  |  |

| M512 RAM blocks (32 × 18 bits)                                      | 94      | 194       | 224       | 295       |  |  |  |  |  |

| M4K RAM blocks (128 × 36 bits)                                      | 60      | 82        | 138       | 171       |  |  |  |  |  |

| M-RAM blocks (4K × 144 bits)                                        | 1       | 2         | 2         | 4         |  |  |  |  |  |

| Total RAM bits                                                      | 920,448 | 1,669,248 | 1,944,576 | 3,317,184 |  |  |  |  |  |

| DSP blocks                                                          | 6       | 10        | 10        | 12        |  |  |  |  |  |

| Embedded multipliers (1)                                            | 48      | 80        | 80        | 96        |  |  |  |  |  |

| PLLs                                                                | 6       | 6         | 6         | 10        |  |  |  |  |  |

| Maximum user I/O pins                                               | 426     | 586       | 706       | 726       |  |  |  |  |  |

| Table 1–2. Stratix Device Features — EP1S40, EP1S60, EP1S80 |           |           |           |  |  |  |  |  |

|-------------------------------------------------------------|-----------|-----------|-----------|--|--|--|--|--|

| Feature                                                     | EP1S40    | EP1S60    | EP1S80    |  |  |  |  |  |

| LEs                                                         | 41,250    | 57,120    | 79,040    |  |  |  |  |  |

| M512 RAM blocks (32 × 18 bits)                              | 384       | 574       | 767       |  |  |  |  |  |

| M4K RAM blocks (128 × 36 bits)                              | 183       | 292       | 364       |  |  |  |  |  |

| M-RAM blocks (4K × 144 bits)                                | 4         | 6         | 9         |  |  |  |  |  |

| Total RAM bits                                              | 3,423,744 | 5,215,104 | 7,427,520 |  |  |  |  |  |

| DSP blocks                                                  | 14        | 18        | 22        |  |  |  |  |  |

| Embedded multipliers (1)                                    | 112       | 144       | 176       |  |  |  |  |  |

| PLLs                                                        | 12        | 12        | 12        |  |  |  |  |  |

| Maximum user I/O pins                                       | 822       | 1,022     | 1,238     |  |  |  |  |  |

### Note to Tables 1–1 and 1–2:

<sup>(1)</sup> This parameter lists the total number of  $9 \times 9$ -bit multipliers for each device. For the total number of  $18 \times 18$ -bit multipliers per device, divide the total number of  $9 \times 9$ -bit multipliers by 2. For the total number of  $36 \times 36$ -bit multipliers per device, divide the total number of  $9 \times 9$ -bit multipliers by 8.

| Table 2–11. M-RAM Combined Byte Selection for ×144 Mode Notes (1), (2) |             |  |  |  |  |  |

|------------------------------------------------------------------------|-------------|--|--|--|--|--|

| byteena[150]                                                           | datain ×144 |  |  |  |  |  |

| [0] = 1                                                                | [80]        |  |  |  |  |  |

| [1] = 1                                                                | [179]       |  |  |  |  |  |

| [2] = 1                                                                | [2618]      |  |  |  |  |  |

| [3] = 1                                                                | [3527]      |  |  |  |  |  |

| [4] = 1                                                                | [4436]      |  |  |  |  |  |

| [5] = 1                                                                | [5345]      |  |  |  |  |  |

| [6] = 1                                                                | [6254]      |  |  |  |  |  |

| [7] = 1                                                                | [7163]      |  |  |  |  |  |

| [8] = 1                                                                | [8072]      |  |  |  |  |  |

| [9] = 1                                                                | [8981]      |  |  |  |  |  |

| [10] = 1                                                               | [9890]      |  |  |  |  |  |

| [11] = 1                                                               | [10799]     |  |  |  |  |  |

| [12] = 1                                                               | [116108]    |  |  |  |  |  |

| [13] = 1                                                               | [125117]    |  |  |  |  |  |

| [14] = 1                                                               | [134126]    |  |  |  |  |  |

| [15] = 1                                                               | [143135]    |  |  |  |  |  |

Notes to Tables 2-10 and 2-11:

- (1) Any combination of byte enables is possible.

- (2) Byte enables can be used in the same manner with 8-bit words, i.e., in  $\times$ 16,  $\times$ 32,  $\times$ 64, and  $\times$ 128 modes.

Similar to all RAM blocks, M-RAM blocks can have different clocks on their inputs and outputs. All input registers—renwe, datain, address, and byte enable registers—are clocked together from either of the two clocks feeding the block. The output register can be bypassed. The eight labclk signals or local interconnect can drive the control signals for the A and B ports of the M-RAM block. LEs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals as shown in Figure 2–19.

Table 2–12 shows the input and output data signal connections for the column units (B1 to B6 and A1 to A6). It also shows the address and control signal input connections to the row units (R1 to R11).

| Unit Interface Block | Input Signals                                | Output Signals  |

|----------------------|----------------------------------------------|-----------------|

| R1                   | addressa[70]                                 |                 |

| R2                   | addressa[158]                                |                 |

| R3                   | byte_enable_a[70]<br>renwe_a                 |                 |

| R4                   | -                                            |                 |

| R5                   | -                                            |                 |

| R6                   | clock_a<br>clocken_a<br>clock_b<br>clocken_b |                 |

| R7                   | -                                            |                 |

| R8                   | -                                            |                 |

| R9                   | byte_enable_b[70]<br>renwe_b                 |                 |

| R10                  | addressb[158]                                |                 |

| R11                  | addressb[70]                                 |                 |

| B1                   | datain_b[7160]                               | dataout_b[7160] |

| B2                   | datain_b[5948]                               | dataout_b[5948] |

| B3                   | datain_b[4736]                               | dataout_b[4736] |

| B4                   | datain_b[3524]                               | dataout_b[3524] |

| B5                   | datain_b[2312]                               | dataout_b[2312] |

| B6                   | datain_b[110]                                | dataout_b[110]  |

| A1                   | datain_a[7160]                               | dataout_a[7160] |

| A2                   | datain_a[5948]                               | dataout_a[5948] |

| A3                   | datain_a[4736]                               | dataout_a[4736] |

| A4                   | datain_a[3524]                               | dataout_a[3524] |

| A5                   | datain_a[2312]                               | dataout_a[2312] |

| A6                   | datain_a[110]                                | dataout_a[110]  |

## Read/Write Clock Mode

The memory blocks implement read/write clock mode for simple dual-port memory. You can use up to two clocks in this mode. The write clock controls the block's data inputs, wraddress, and wren. The read clock controls the data output, rdaddress, and rden. The memory blocks support independent clock enables for each clock and asynchronous clear signals for the read- and write-side registers. Figure 2–27 shows a memory block in read/write clock mode.

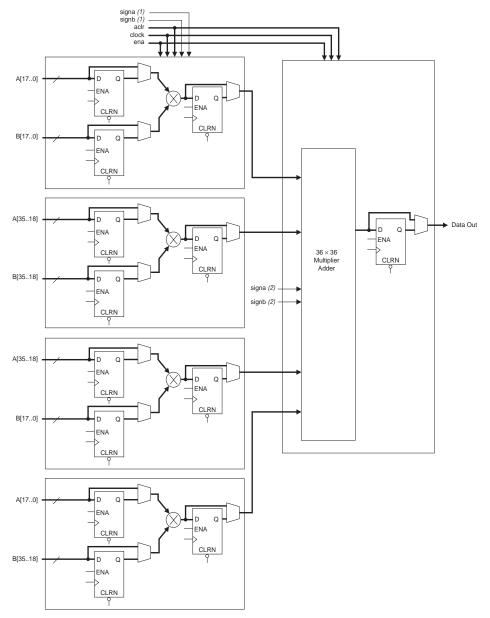

Figure 2–36. 36  $\times$  36 Multiply Mode

#### *Notes to Figure 2–36:*

- (1) These signals are not registered or registered once to match the pipeline.

- (2) These signals are not registered, registered once, or registered twice for latency to match the pipeline.

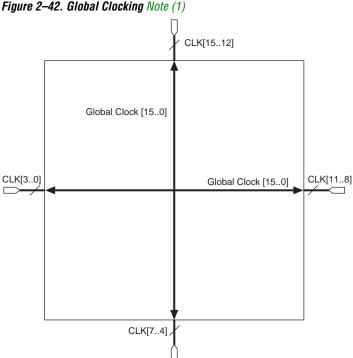

*Note to Figure 2–42:*

(1) The corner fast PLLs can also be driven through the global or regional clock networks. The global or regional clock input to the fast PLL can be driven by an output from another PLL, a pin-driven global or regional clock, or internallygenerated global signals.

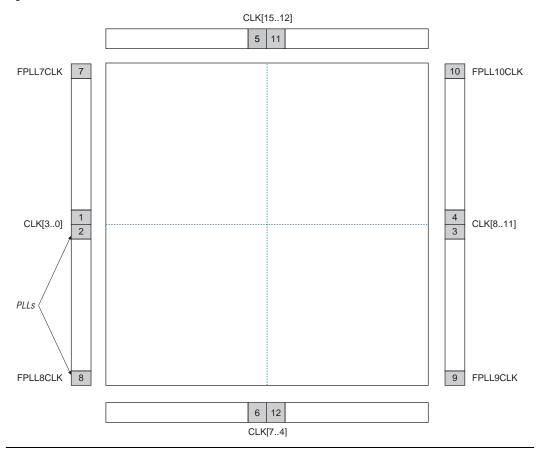

## Regional Clock Network

There are four regional clock networks within each quadrant of the Stratix device that are driven by the same dedicated CLK[15..0] input pins or from PLL outputs. From a top view of the silicon, RCLK [0..3] are in the top left quadrant, RCLK[8..11] are in the top-right quadrant, RCLK[4..7] are in the bottom-left quadrant, and RCLK[12..15] are in the bottom-right quadrant. The regional clock networks only pertain to the quadrant they drive into. The regional clock networks provide the lowest clock delay and skew for logic contained within a single quadrant. RCLK cannot be driven by internal logic. The CLK clock pins symmetrically drive the RCLK networks within a particular quadrant, as shown in Figure 2–43. See Figures 2–50 and 2–51 for RCLK connections from PLLs and CLK pins.

Figure 2–49 shows a top-level diagram of the Stratix device and PLL floorplan.

### **Enhanced PLLs**

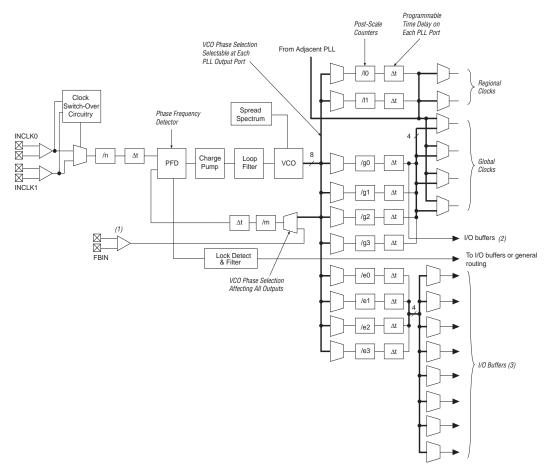

Stratix devices contain up to four enhanced PLLs with advanced clock management features. Figure 2–52 shows a diagram of the enhanced PLL.

Figure 2-52. Stratix Enhanced PLL

#### Notes to Figure 2-52:

- (1) External feedback is available in PLLs 5 and 6.

- (2) This single-ended external output is available from the g0 counter for PLLs 11 and 12.

- (3) These four counters and external outputs are available in PLLs 5 and 6.

- (4) This connection is only available on EP1S40 and larger Stratix devices. For example, PLLs 5 and 11 are adjacent and PLLs 6 and 12 are adjacent. The EP1S40 device in the 780-pin FineLine BGA package does not support PLLs 11 and 12.

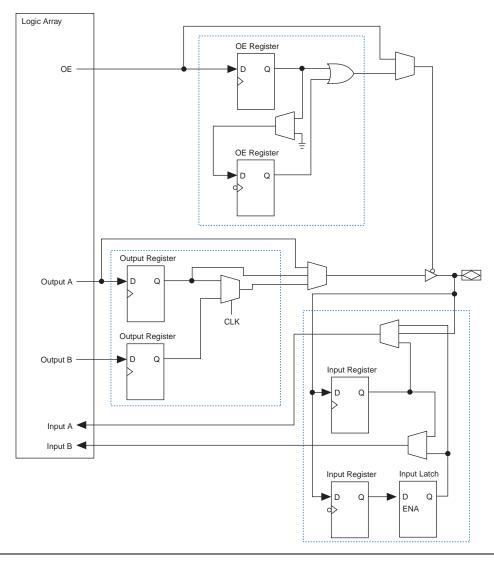

Figure 2-59. Stratix IOE Structure

The IOEs are located in I/O blocks around the periphery of the Stratix device. There are up to four IOEs per row I/O block and six IOEs per column I/O block. The row I/O blocks drive row, column, or direct link interconnects. The column I/O blocks drive column interconnects. Figure 2–60 shows how a row I/O block connects to the logic array. Figure 2–61 shows how a column I/O block connects to the logic array.

Each IOE contains its own control signal selection for the following control signals: oe, ce\_in, ce\_out, aclr/preset, sclr/preset, clk\_in, and clk\_out. Figure 2–63 illustrates the control signal selection.

io bclk[3..0] io\_bce[3..0] io\_bclr[3..0] io\_boe[3..0] Dedicated I/O Clock [7..0] I/O Interconnect [15..0] io\_coe Local Interconnect io\_cclr Local Interconnect io\_cce\_out Local Interconnect io cce in Local Interconnect io\_cclk clk\_out ce\_out sclr/preset Local Interconnect

ce\_in

clk in

Figure 2-63. Control Signal Selection per IOE

In normal bidirectional operation, the input register can be used for input data requiring fast setup times. The input register can have its own clock input and clock enable separate from the OE and output registers. The output register can be used for data requiring fast clock-to-output performance. The OE register can be used for fast clock-to-output enable timing. The OE and output register share the same clock source and the same clock enable source from local interconnect in the associated LAB, dedicated I/O clocks, and the column and row interconnects. Figure 2–64 shows the IOE in bidirectional configuration.

aclr/preset

oe

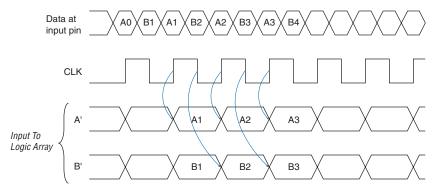

Figure 2-66. Input Timing Diagram in DDR Mode

When using the IOE for DDR outputs, the two output registers are configured to clock two data paths from LEs on rising clock edges. These output registers are multiplexed by the clock to drive the output pin at a  $\times 2$  rate. One output register clocks the first bit out on the clock high time, while the other output register clocks the second bit out on the clock low time. Figure 2–67 shows the IOE configured for DDR output. Figure 2–68 shows the DDR output timing diagram.

Tables 2–25 and 2–26 show the performance specification for DDR SDRAM, RLDRAM II, QDR SRAM, QDRII SRAM, and ZBT SRAM interfaces in EP1S10 through EP1S40 devices and in EP1S60 and EP1S80 devices. The DDR SDRAM and QDR SRAM numbers in Table 2–25 have been verified with hardware characterization with third-party DDR SDRAM and QDR SRAM devices over temperature and voltage extremes.

| Table 2–25. External RAM Support in EP1S10 through EP1S40 Devices |                 |                          |                |               |                |               |                |               |  |  |

|-------------------------------------------------------------------|-----------------|--------------------------|----------------|---------------|----------------|---------------|----------------|---------------|--|--|

|                                                                   |                 | Maximum Clock Rate (MHz) |                |               |                |               |                |               |  |  |

| DDR Memory Type                                                   | I/O<br>Standard | -5 Speed<br>Grade        | -6 Speed Grade |               | -7 Speed Grade |               | -8 Speed Grade |               |  |  |

|                                                                   |                 | Flip-Chip                | Flip-Chip      | Wire-<br>Bond | Flip-<br>Chip  | Wire-<br>Bond | Flip-<br>Chip  | Wire-<br>Bond |  |  |

| DDR SDRAM (1), (2)                                                | SSTL-2          | 200                      | 167            | 133           | 133            | 100           | 100            | 100           |  |  |

| DDR SDRAM - side banks (2), (3), (4)                              | SSTL-2          | 150                      | 133            | 110           | 133            | 100           | 100            | 100           |  |  |

| RLDRAM II (4)                                                     | 1.8-V HSTL      | 200                      | (5)            | (5)           | (5)            | (5)           | (5)            | (5)           |  |  |

| QDR SRAM (6)                                                      | 1.5-V HSTL      | 167                      | 167            | 133           | 133            | 100           | 100            | 100           |  |  |

| QDRII SRAM (6)                                                    | 1.5-V HSTL      | 200                      | 167            | 133           | 133            | 100           | 100            | 100           |  |  |

| ZBT SRAM (7)                                                      | LVTTL           | 200                      | 200            | 200           | 167            | 167           | 133            | 133           |  |  |

#### Notes to Table 2-25:

- (1) These maximum clock rates apply if the Stratix device uses DQS phase-shift circuitry to interface with DDR SDRAM. DQS phase-shift circuitry is only available in the top and bottom I/O banks (I/O banks 3, 4, 7, and 8).

- (2) For more information on DDR SDRAM, see AN 342: Interfacing DDR SDRAM with Stratix & Stratix GX Devices.

- (3) DDR SDRAM is supported on the Stratix device side I/O banks (I/O banks 1, 2, 5, and 6) without dedicated DQS phase-shift circuitry. The read DQS signal is ignored in this mode.

- (4) These performance specifications are preliminary.

- (5) This device does not support RLDRAM II.

- (6) For more information on QDR or QDRII SRAM, see AN 349: QDR SRAM Controller Reference Design for Stratix & Stratix GX Devices.

- (7) For more information on ZBT SRAM, see AN 329: ZBT SRAM Controller Reference Design for Stratix & Stratix GX Devices.

The output levels are compatible with systems of the same voltage as the power supply (i.e., when VCCIO pins are connected to a 1.5-V power supply, the output levels are compatible with 1.5-V systems). When VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3 V and is compatible with 3.3-V or 5.0-V systems.

Table 2–36 summarizes Stratix MultiVolt I/O support.

| Table 2–36. Stratix MultiVolt I/O Support Note (1) |              |                                    |              |              |                   |              |              |              |          |          |

|----------------------------------------------------|--------------|------------------------------------|--------------|--------------|-------------------|--------------|--------------|--------------|----------|----------|

| V (V)                                              |              | Input Signal (5) Output Signal (6) |              |              | Output Signal (6) |              |              |              |          |          |

| V <sub>CCIO</sub> (V)                              | 1.5 V        | 1.8 V                              | 2.5 V        | 3.3 V        | 5.0 V             | 1.5 V        | 1.8 V        | 2.5 V        | 3.3 V    | 5.0 V    |

| 1.5                                                | <b>✓</b>     | <b>✓</b>                           | <b>√</b> (2) | <b>√</b> (2) |                   | <b>✓</b>     |              |              |          |          |

| 1.8                                                | <b>√</b> (2) | <b>✓</b>                           | <b>√</b> (2) | <b>√</b> (2) |                   | <b>✓</b> (3) | <b>✓</b>     |              |          |          |

| 2.5                                                |              |                                    | <b>✓</b>     | <b>✓</b>     |                   | <b>√</b> (3) | <b>√</b> (3) | <b>✓</b>     |          |          |

| 3.3                                                |              |                                    | <b>√</b> (2) | <b>✓</b>     | <b>✓</b> (4)      | <b>✓</b> (3) | <b>√</b> (3) | <b>√</b> (3) | <b>✓</b> | <b>✓</b> |

#### Notes to Table 2-36:

- (1) To drive inputs higher than  $V_{CCIO}$  but less than 4.1 V, disable the PCI clamping diode. However, to drive 5.0-V inputs to the device, enable the PCI clamping diode to prevent  $V_{\rm I}$  from rising above 4.0 V.

- (2) The input pin current may be slightly higher than the typical value.

- (3) Although  $V_{CCIO}$  specifies the voltage necessary for the Stratix device to drive out, a receiving device powered at a different level can still interface with the Stratix device if it has inputs that tolerate the  $V_{CCIO}$  value.

- (4) Stratix devices can be 5.0-V tolerant with the use of an external resistor and the internal PCI clamp diode.

- (5) This is the external signal that is driving the Stratix device.

- (6) This represents the system voltage that Stratix supports when a VCCIO pin is connected to a specific voltage level. For example, when VCCIO is 3.3 V and if the I/O standard is LVTTL/LVCMOS, the output high of the signal coming out from Stratix is 3.3 V and is compatible with 3.3-V or 5.0-V systems.

## High-Speed Differential I/O Support

Stratix devices contain dedicated circuitry for supporting differential standards at speeds up to 840 Mbps. The following differential I/O standards are supported in the Stratix device: LVDS, LVPECL, HyperTransport, and 3.3-V PCML.

There are four dedicated high-speed PLLs in the EP1S10 to EP1S25 devices and eight dedicated high-speed PLLs in the EP1S30 to EP1S80 devices to multiply reference clocks and drive high-speed differential SERDES channels.

See the Stratix device pin-outs at **www.altera.com** for additional high speed DIFFIO pin information for Stratix devices.

The transmitter external clock output is transmitted on a data channel. The txclk pin for each bank is located in between data transmitter pins. For  $\times 1$  clocks (e.g., 622 Mbps, 622 MHz), the high-speed PLL clock bypasses the SERDES to drive the output pins. For half-rate clocks (e.g., 622 Mbps, 311 MHz) or any other even-numbered factor such as 1/4, 1/7, 1/8, or 1/10, the SERDES automatically generates the clock in the Ouartus II software.

For systems that require more than four or eight high-speed differential I/O clock domains, a SERDES bypass implementation is possible using IOEs.

## **Byte Alignment**

For high-speed source synchronous interfaces such as POS-PHY 4, XSBI, RapidIO, and HyperTransport technology, the source synchronous clock rate is not a byte- or SERDES-rate multiple of the data rate. Byte alignment is necessary for these protocols since the source synchronous clock does not provide a byte or word boundary since the clock is one half the data rate, not one eighth. The Stratix device's high-speed differential I/O circuitry provides dedicated data realignment circuitry for user-controlled byte boundary shifting. This simplifies designs while saving LE resources. An input signal to each fast PLL can stall deserializer parallel data outputs by one bit period. You can use an LE-based state machine to signal the shift of receiver byte boundaries until a specified pattern is detected to indicate byte alignment.

## Power Sequencing & Hot Socketing

Because Stratix devices can be used in a mixed-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. Therefore, the VCCIO and VCCINT power supplies may be powered in any order.

Although you can power up or down the VCCIO and VCCINT power supplies in any sequence, you should not power down any I/O banks that contain configuration pins while leaving other I/O banks powered on. For power up and power down, all supplies (VCCINT and all VCCIO power planes) must be powered up and down within 100 ms of each other. This prevents I/O pins from driving out.

Signals can be driven into Stratix devices before and during power up without damaging the device. In addition, Stratix devices do not drive out during power up. Once operating conditions are reached and the device is configured, Stratix devices operate as specified by the user. For more information, see *Hot Socketing* in the *Selectable I/O Standards in Stratix & Stratix GX Devices* chapter in the *Stratix Device Handbook*, *Volume 2*.

For Stratix, the CRC is computed by the Quartus II software and downloaded into the device as a part of the configuration bit stream. The CRC\_ERROR pin reports a soft error when configuration SRAM data is corrupted, triggering device reconfiguration.

## **Custom-Built Circuitry**

Dedicated circuitry is built in the Stratix devices to perform error detection automatically. You can use the built-in dedicated circuitry for error detection using CRC feature in Stratix devices, eliminating the need for external logic. This circuitry will perform error detection automatically when enabled. This error detection circuitry in Stratix devices constantly checks for errors in the configuration SRAM cells while the device is in user mode. You can monitor one external pin for the error and use it to trigger a re-configuration cycle. Select the desired time between checks by adjusting a built-in clock divider.

#### **Software Interface**

In the Quartus II software version 4.1 and later, you can turn on the automated error detection CRC feature in the **Device & Pin Options** dialog box. This dialog box allows you to enable the feature and set the internal frequency of the CRC between 400 kHz to 100 MHz. This controls the rate that the CRC circuitry verifies the internal configuration SRAM bits in the FPGA device.

For more information on CRC, see AN 357: Error Detection Using CRC in Altera FPGA Devices.

## Temperature Sensing Diode

Stratix devices include a diode-connected transistor for use as a temperature sensor in power management. This diode is used with an external digital thermometer device such as a MAX1617A or MAX1619 from MAXIM Integrated Products. These devices steer bias current through the Stratix diode, measuring forward voltage and converting this reading to temperature in the form of an 8-bit signed number (7 bits plus sign). The external device's output represents the junction temperature of the Stratix device and can be used for intelligent power management.

The diode requires two pins (tempdiodep and tempdioden) on the Stratix device to connect to the external temperature-sensing device, as shown in Figure 3–5. The temperature sensing diode is a passive element and therefore can be used before the Stratix device is powered.

| Table 4-36          | S. Stratix Performance (             | Part 2 | of 2) Notes                   | 5 (1), (2)    |                      |                      |                      |                      |       |

|---------------------|--------------------------------------|--------|-------------------------------|---------------|----------------------|----------------------|----------------------|----------------------|-------|

|                     |                                      | F      | Resources L                   | Jsed          | Performance          |                      |                      |                      |       |

| Applications        |                                      | LEs    | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -5<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade | Units |

| TriMatrix<br>memory | True dual-port<br>RAM 16K × 36 bit   | 0      | 1                             | 0             | 269.83               | 237.69               | 206.82               | 175.74               | MHz   |

| M-RAM<br>block      | Single port<br>RAM 32K × 18 bit      | 0      | 1                             | 0             | 275.86               | 244.55               | 212.76               | 180.83               | MHz   |

|                     | Simple dual-port<br>RAM 32K × 18 bit | 0      | 1                             | 0             | 275.86               | 244.55               | 212.76               | 180.83               | MHz   |

|                     | True dual-port<br>RAM 32K × 18 bit   | 0      | 1                             | 0             | 275.86               | 244.55               | 212.76               | 180.83               | MHz   |

|                     | Single port<br>RAM 64K × 9 bit       | 0      | 1                             | 0             | 287.85               | 253.29               | 220.36               | 187.26               | MHz   |

|                     | Simple dual-port<br>RAM 64K × 9 bit  | 0      | 1                             | 0             | 287.85               | 253.29               | 220.36               | 187.26               | MHz   |

|                     | True dual-port<br>RAM 64K × 9 bit    | 0      | 1                             | 0             | 287.85               | 253.29               | 220.36               | 187.26               | MHz   |

| DSP block           | 9 × 9-bit multiplier (3)             | 0      | 0                             | 1             | 335.0                | 293.94               | 255.68               | 217.24               | MHz   |

|                     | 18 × 18-bit multiplier (4)           | 0      | 0                             | 1             | 278.78               | 237.41               | 206.52               | 175.50               | MHz   |

|                     | $36 \times 36$ -bit multiplier (4)   | 0      | 0                             | 1             | 148.25               | 134.71               | 117.16               | 99.59                | MHz   |

|                     | 36 × 36-bit multiplier (5)           | 0      | 0                             | 1             | 278.78               | 237.41               | 206.52               | 175.5                | MHz   |

|                     | 18-bit, 4-tap FIR filter             | 0      | 0                             | 1             | 278.78               | 237.41               | 206.52               | 175.50               | MHz   |

| Larger<br>Designs   | 8-bit, 16-tap parallel<br>FIR filter | 58     | 0                             | 4             | 141.26               | 133.49               | 114.88               | 100.28               | MHz   |

|                     | 8-bit, 1,024-point FFT function      | 870    | 5                             | 1             | 261.09               | 235.51               | 205.21               | 175.22               | MHz   |

### Notes to Table 4–36:

- (1) These design performance numbers were obtained using the Quartus II software.

- (2) Numbers not listed will be included in a future version of the data sheet.

- (3) This application uses registered inputs and outputs.

- (4) This application uses registered multiplier input and output stages within the DSP block.

- (5) This application uses registered multiplier input, pipeline, and output stages within the DSP block.

## **Internal Timing Parameters**

Internal timing parameters are specified on a speed grade basis independent of device density. Tables 4–37 through 4–42 describe the Stratix device internal timing microparameters for LEs, IOEs, TriMatrix memory structures, DSP blocks, and MultiTrack interconnects.

| Table 4–37. LE Internal Timing Microparameter Descriptions |                                                                                                                           |  |  |  |  |  |  |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Symbol                                                     | Parameter                                                                                                                 |  |  |  |  |  |  |

| t <sub>SU</sub>                                            | LE register setup time before clock                                                                                       |  |  |  |  |  |  |

| t <sub>H</sub>                                             | LE register hold time after clock                                                                                         |  |  |  |  |  |  |

| t <sub>CO</sub>                                            | LE register clock-to-output delay                                                                                         |  |  |  |  |  |  |

| t <sub>LUT</sub>                                           | LE combinatorial LUT delay for data-in to data-out                                                                        |  |  |  |  |  |  |

| t <sub>CLR</sub>                                           | Minimum clear pulse width                                                                                                 |  |  |  |  |  |  |

| t <sub>PRE</sub>                                           | Minimum preset pulse width                                                                                                |  |  |  |  |  |  |

| t <sub>CLKHL</sub>                                         | Register minimum clock high or low time. The maximum core clock frequency can be calculated by $1/(2 \times t_{CLKHL})$ . |  |  |  |  |  |  |

| Table 4–38. IOE Internal Timing Microparameter Descriptions |                                                                                                                                                                                                                            |  |  |  |  |  |  |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Symbol                                                      | Parameter                                                                                                                                                                                                                  |  |  |  |  |  |  |

| t <sub>SU_R</sub>                                           | Row IOE input register setup time                                                                                                                                                                                          |  |  |  |  |  |  |

| t <sub>SU_C</sub>                                           | Column IOE input register setup time                                                                                                                                                                                       |  |  |  |  |  |  |

| t <sub>H</sub>                                              | IOE input and output register hold time after clock                                                                                                                                                                        |  |  |  |  |  |  |

| t <sub>CO_R</sub>                                           | Row IOE input and output register clock-to-output delay                                                                                                                                                                    |  |  |  |  |  |  |

| t <sub>CO_C</sub>                                           | Column IOE input and output register clock-to-output delay                                                                                                                                                                 |  |  |  |  |  |  |

| t <sub>PIN2COMBOUT_R</sub>                                  | Row input pin to IOE combinatorial output                                                                                                                                                                                  |  |  |  |  |  |  |

| t <sub>PIN2COMBOUT_C</sub>                                  | Column input pin to IOE combinatorial output                                                                                                                                                                               |  |  |  |  |  |  |

| t <sub>COMBIN2PIN_R</sub>                                   | Row IOE data input to combinatorial output pin                                                                                                                                                                             |  |  |  |  |  |  |

| t <sub>COMBIN2PIN_C</sub>                                   | Column IOE data input to combinatorial output pin                                                                                                                                                                          |  |  |  |  |  |  |

| t <sub>CLR</sub>                                            | Minimum clear pulse width                                                                                                                                                                                                  |  |  |  |  |  |  |

| t <sub>PRE</sub>                                            | Minimum preset pulse width                                                                                                                                                                                                 |  |  |  |  |  |  |

| t <sub>CLKHL</sub>                                          | Register minimum clock high or low time. The maximum I/O clock frequency can be calculated by $1/(2 \times t_{\text{CLKHL}})$ . Performance may also be affected by I/O timing, use of PLL, and I/O programmable settings. |  |  |  |  |  |  |

Table 4–114. Stratix Maximum Input Clock Rate for CLK[7..4] & CLK[15..12] Pins in Flip-Chip Packages (Part 2 of 2)

| I/O Standard                  | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------|-------------------|-------------------|-------------------|-------------------|------|

| LVDS (1)                      | 645               | 645               | 622               | 622               | MHz  |

| HyperTransport technology (1) | 500               | 500               | 450               | 450               | MHz  |

Table 4–115. Stratix Maximum Input Clock Rate for CLK[0, 2, 9, 11] Pins & FPLL[10..7]CLK Pins in Flip-Chip Packages

| I/O Standard                  | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------|-------------------|-------------------|-------------------|-------------------|------|

| LVTTL                         | 422               | 422               | 390               | 390               | MHz  |

| 2.5 V                         | 422               | 422               | 390               | 390               | MHz  |

| 1.8 V                         | 422               | 422               | 390               | 390               | MHz  |

| 1.5 V                         | 422               | 422               | 390               | 390               | MHz  |

| LVCMOS                        | 422               | 422               | 390               | 390               | MHz  |

| GTL+                          | 300               | 250               | 200               | 200               | MHz  |

| SSTL-3 Class I                | 400               | 350               | 300               | 300               | MHz  |

| SSTL-3 Class II               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-2 Class I                | 400               | 350               | 300               | 300               | MHz  |

| SSTL-2 Class II               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-18 Class I               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-18 Class II              | 400               | 350               | 300               | 300               | MHz  |

| 1.5-V HSTL Class I            | 400               | 350               | 300               | 300               | MHz  |

| 1.8-V HSTL Class I            | 400               | 350               | 300               | 300               | MHz  |

| СТТ                           | 300               | 250               | 200               | 200               | MHz  |

| Differential 1.5-V HSTL<br>C1 | 400               | 350               | 300               | 300               | MHz  |

| LVPECL (1)                    | 717               | 717               | 640               | 640               | MHz  |

| PCML (1)                      | 400               | 375               | 350               | 350               | MHz  |

| LVDS (1)                      | 717               | 717               | 640               | 640               | MHz  |

| HyperTransport technology (1) | 717               | 717               | 640               | 640               | MHz  |

| Symbol                                                                                             | Conditions                   | -5 Speed Grade |     |     | -6 Speed Grade |     |     | -7 Speed Grade |     |       | -8 Speed Grade |     |       | 1114 |

|----------------------------------------------------------------------------------------------------|------------------------------|----------------|-----|-----|----------------|-----|-----|----------------|-----|-------|----------------|-----|-------|------|

|                                                                                                    |                              | Min            | Тур | Max | Min            | Тур | Max | Min            | Тур | Max   | Min            | Тур | Max   | Unit |

| f <sub>HSCLK</sub> (Clock<br>frequency)<br>(PCML)<br>f <sub>HSCLK</sub> = f <sub>HSDR</sub> /<br>W | W = 4 to 30<br>(Serdes used) | 10             |     | 100 | 10             |     | 100 | 10             |     | 77.75 | 10             |     | 77.75 | MHz  |

|                                                                                                    | W = 2 (Serdes bypass)        | 50             |     | 200 | 50             |     | 200 | 50             |     | 150   | 50             |     | 150   | MHz  |

|                                                                                                    | W = 2 (Serdes used)          | 150            |     | 200 | 150            |     | 200 | 150            |     | 155.5 | 150            |     | 155.5 | MHz  |

|                                                                                                    | W = 1 (Serdes bypass)        | 100            |     | 250 | 100            |     | 250 | 100            |     | 200   | 100            |     | 200   | MHz  |

|                                                                                                    | W = 1 (Serdes used)          | 300            |     | 400 | 300            |     | 400 | 300            |     | 311   | 300            |     | 311   | MHz  |

| f <sub>HSDR</sub> Device<br>operation<br>(PCML)                                                    | J = 10                       | 300            |     | 400 | 300            |     | 400 | 300            |     | 311   | 300            |     | 311   | Mbps |

|                                                                                                    | J = 8                        | 300            |     | 400 | 300            |     | 400 | 300            |     | 311   | 300            |     | 311   | Mbps |

|                                                                                                    | J = 7                        | 300            |     | 400 | 300            |     | 400 | 300            |     | 311   | 300            |     | 311   | Mbps |

|                                                                                                    | J = 4                        | 300            |     | 400 | 300            |     | 400 | 300            |     | 311   | 300            |     | 311   | Mbps |

|                                                                                                    | J = 2                        | 100            |     | 400 | 100            |     | 400 | 100            |     | 300   | 100            |     | 300   | Mbps |

|                                                                                                    | J = 1                        | 100            |     | 250 | 100            |     | 250 | 100            |     | 200   | 100            |     | 200   | Mbps |

| TCCS                                                                                               | All                          |                |     | 200 |                |     | 200 |                |     | 300   |                |     | 300   | ps   |

| Differential HSTL Specifications 4–15<br>DSP        | Parameters 4–39<br>Row Pin                         |  |  |  |  |  |  |

|-----------------------------------------------------|----------------------------------------------------|--|--|--|--|--|--|

| Block Diagram                                       | Fast Regional Clock External I/O Timing            |  |  |  |  |  |  |

| Configuration                                       | Parameters 4–40                                    |  |  |  |  |  |  |

| for 18 x 18-Bit 2–55                                | Global Clock External I/O Timing                   |  |  |  |  |  |  |

| for 9 x 9-Bit 2–56                                  | Parameters 4–41                                    |  |  |  |  |  |  |

| Block Interconnect Interface 2–71                   | Regional Clock External I/O Timing                 |  |  |  |  |  |  |

| Block Interface 2–70                                | Parameters 4–41                                    |  |  |  |  |  |  |

| Block Signal Sources & Destinations 2–73            | EP1S25 Devices                                     |  |  |  |  |  |  |

| Blocks                                              | Column Pin                                         |  |  |  |  |  |  |

| Arranged in Columns 2–53                            | Fast Regional Clock External I/O Timing            |  |  |  |  |  |  |

| in Stratix Devices 2–54                             | Parameters 4–42                                    |  |  |  |  |  |  |

| Input Register Modes 2-60                           | Global Clock External I/O Timing                   |  |  |  |  |  |  |

| Input Registers 2–58                                | Parameters 4–43                                    |  |  |  |  |  |  |

| Multiplier                                          | Regional Clock External I/O Timing                 |  |  |  |  |  |  |

| 2–60                                                | Parameters 4–42                                    |  |  |  |  |  |  |

| Block 2–57                                          | Row Pin                                            |  |  |  |  |  |  |

| Signed Representation 2-60                          | Fast Regional Clock External I/O Timing            |  |  |  |  |  |  |

| Sub-Block 2–57                                      | Parameters 4–43                                    |  |  |  |  |  |  |

| Sub-Blocks Using Input Shift Register               | Global Clock External I/O Timing                   |  |  |  |  |  |  |

| Connections 2–59                                    | Parameters 4–44                                    |  |  |  |  |  |  |

| Pipeline/Post Multiply Register 2–61                | Regional Clock External I/O Timing                 |  |  |  |  |  |  |

|                                                     | Parameters 4–44                                    |  |  |  |  |  |  |

| E                                                   | EP1S30 Devices                                     |  |  |  |  |  |  |

| <b>L</b>                                            | Column Pin                                         |  |  |  |  |  |  |

| EP1S10 Devices                                      | Fast Regional Clock External I/O Timing            |  |  |  |  |  |  |

| Column Pin                                          | Parameters 4–45                                    |  |  |  |  |  |  |

| Fast Regional Clock External I/O Timing             | Global Clock External I/O Timing                   |  |  |  |  |  |  |

| Parameters 4–36                                     | Parameters 4–45                                    |  |  |  |  |  |  |

| Global Clock External I/O Timing<br>Parameters 4–37 | Regional Clock External I/O Timing Parameters 4–45 |  |  |  |  |  |  |

| Regional Clock External I/O Timing                  | Row Pin                                            |  |  |  |  |  |  |

| Parameters 4–36                                     | Fast Regional Clock External I/O Timing            |  |  |  |  |  |  |

| Row Pin                                             | Parameters 4–46                                    |  |  |  |  |  |  |

| Fast Regional Clock External I/O Timing             | Global Clock External I/O Timing                   |  |  |  |  |  |  |

| Parameters 4–37                                     | Parameters 4–47                                    |  |  |  |  |  |  |

| Global Clock External I/O Timing                    | Regional Clock External I/O Timing                 |  |  |  |  |  |  |

| Parameters 4–38                                     | Parameters 4–47                                    |  |  |  |  |  |  |

| Regional Clock External I/O Timing                  | EP1S40 Devices                                     |  |  |  |  |  |  |

| Parameters 4–38                                     | Column Pin                                         |  |  |  |  |  |  |

| EP1S20 Devices                                      | Fast Regional Clock External I/O Timing            |  |  |  |  |  |  |

| Column Pin                                          | Parameters 4–48                                    |  |  |  |  |  |  |

| Fast Regional Clock External I/O Timing             | Global Clock External I/O Timing                   |  |  |  |  |  |  |

| Parameters 4–39                                     | Parameters 4–49                                    |  |  |  |  |  |  |

| Global Clock External I/O Timing                    | Regional Clock External I/O Timing                 |  |  |  |  |  |  |

| Parameters 4–40                                     | Parameters 4–48                                    |  |  |  |  |  |  |

| Regional Clock External I/O Timing                  | Row Pin                                            |  |  |  |  |  |  |

Altera Corporation Index-3