Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 1846                                                     |

| Number of Logic Elements/Cells | 18460                                                    |

| Total RAM Bits                 | 1669248                                                  |

| Number of I/O                  | 586                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 780-BBGA, FCBGA                                          |

| Supplier Device Package        | 780-FBGA (29x29)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s20f780c5n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Chapter | Date/Version         | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4       | October 2003, v2.1   | <ul> <li>Added -8 speed grade information.</li> <li>Updated performance information in Table 4–36.</li> <li>Updated timing information in Tables 4–55 through 4–96.</li> <li>Updated delay information in Tables 4–103 through 4–108.</li> <li>Updated programmable delay information in Tables 4–100 and 4–103.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | July 2003, v2.0      | <ul> <li>Updated clock rates in Tables 4–114 through 4–123.</li> <li>Updated speed grade information in the introduction on page 4-1.</li> <li>Corrected figures 4-1 &amp; 4-2 and Table 4-9 to reflect how VID and VOD are specified.</li> <li>Added note 6 to Table 4-32.</li> <li>Updated Stratix Performance Table 4-35.</li> <li>Updated EP1S60 and EP1S80 timing parameters in Tables 4-82 to 4-93. The Stratix timing models are final for all devices.</li> <li>Updated Stratix IOE programmable delay chains in Tables 4-100 to 4-101.</li> <li>Added single-ended I/O standard output pin delay adders for loading in Table 4-102.</li> <li>Added spec for FPLL[107]CLK pins in Tables 4-104 and 4-107.</li> <li>Updated high-speed I/O specification for J=2 in Tables 4-114 and 4-115.</li> <li>Updated EPLL specification and fast PLL specification in Tables 4-116 to 4-120.</li> </ul> |

| 5       | September 2004, v2.1 | <ul> <li>Updated reference to device pin-outs on page 5-1 to indicate that<br/>device pin-outs are no longer included in this manual and are now<br/>available on the Altera web site.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | April 2003, v1.0     | No new changes in Stratix Device Handbook v2.0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Altera Corporation Section I–7

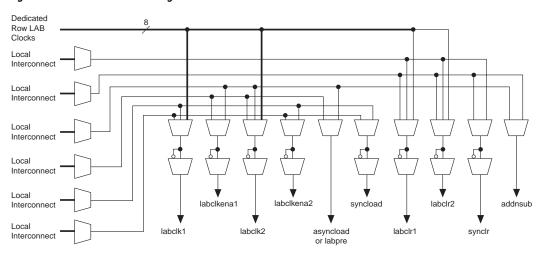

With the LAB-wide addnsub control signal, a single LE can implement a one-bit adder and subtractor. This saves LE resources and improves performance for logic functions such as DSP correlators and signed multipliers that alternate between addition and subtraction depending on data.

The LAB row clocks [7..0] and LAB local interconnect generate the LAB-wide control signals. The MultiTrack $^{\text{IM}}$  interconnect's inherent low skew allows clock and control signal distribution in addition to data. Figure 2–4 shows the LAB control signal generation circuit.

Figure 2-4. LAB-Wide Control Signals

### **Logic Elements**

The smallest unit of logic in the Stratix architecture, the LE, is compact and provides advanced features with efficient logic utilization. Each LE contains a four-input LUT, which is a function generator that can implement any function of four variables. In addition, each LE contains a programmable register and carry chain with carry select capability. A single LE also supports dynamic single bit addition or subtraction mode selectable by an LAB-wide control signal. Each LE drives all types of interconnects: local, row, column, LUT chain, register chain, and direct link interconnects. See Figure 2–5.

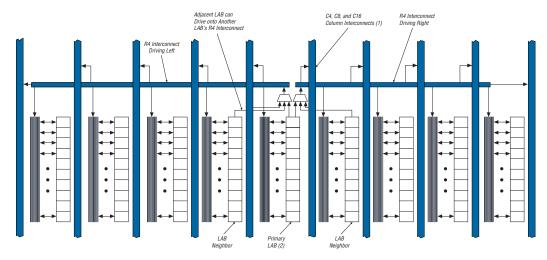

row connections in a four-LAB region. Every LAB has its own set of R4 interconnects to drive either left or right. Figure 2–9 shows R4 interconnect connections from an LAB. R4 interconnects can drive and be driven by DSP blocks and RAM blocks and horizontal IOEs. For LAB interfacing, a primary LAB or LAB neighbor can drive a given R4 interconnect. For R4 interconnects that drive to the right, the primary LAB and right neighbor can drive on to the interconnect. For R4 interconnects that drive to the left, the primary LAB and its left neighbor can drive on to the interconnects can drive other R4 interconnects to extend the range of LABs they can drive. R4 interconnects can also drive C4 and C16 interconnects for connections from one row to another. Additionally, R4 interconnects can drive R24 interconnects.

Figure 2-9. R4 Interconnect Connections

#### *Notes to Figure 2–9:*

- (1) C4 interconnects can drive R4 interconnects.

- (2) This pattern is repeated for every LAB in the LAB row.

The R8 interconnects span eight LABs, M512 or M4K RAM blocks, or DSP blocks to the right or left from a source LAB. These resources are used for fast row connections in an eight-LAB region. Every LAB has its own set of R8 interconnects to drive either left or right. R8 interconnect connections between LABs in a row are similar to the R4 connections shown in Figure 2–9, with the exception that they connect to eight LABs to the right or left, not four. Like R4 interconnects, R8 interconnects can drive and be driven by all types of architecture blocks. R8 interconnects

M4K RAM blocks support byte writes when the write port has a data width of 16, 18, 32, or 36 bits. The byte enables allow the input data to be masked so the device can write to specific bytes. The unwritten bytes retain the previous written value. Table 2–7 summarizes the byte selection.

| Table 2–7. Byte Enable for M4K Blocks Notes (1), (2) |            |            |  |  |  |  |  |

|------------------------------------------------------|------------|------------|--|--|--|--|--|

| byteena[30]                                          | datain ×18 | datain ×36 |  |  |  |  |  |

| [0] = 1                                              | [80]       | [80]       |  |  |  |  |  |

| [1] = 1                                              | [179]      | [179]      |  |  |  |  |  |

| [2] = 1                                              | _          | [2618]     |  |  |  |  |  |

| [3] = 1                                              | _          | [3527]     |  |  |  |  |  |

*Notes to Table 2–7:*

- (1) Any combination of byte enables is possible.

- (2) Byte enables can be used in the same manner with 8-bit words, i.e., in  $\times$  16 and  $\times$  32 modes.

The M4K RAM blocks allow for different clocks on their inputs and outputs. Either of the two clocks feeding the block can clock M4K RAM block registers (renwe, address, byte enable, datain, and output registers). Only the output register can be bypassed. The eight labclk signals or local interconnects can drive the control signals for the A and B ports of the M4K RAM block. LEs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals, as shown in Figure 2–17.

The R4, R8, C4, C8, and direct link interconnects from adjacent LABs drive the M4K RAM block local interconnect. The M4K RAM blocks can communicate with LABs on either the left or right side through these row resources or with LAB columns on either the right or left with the column resources. Up to 10 direct link input connections to the M4K RAM Block are possible from the left adjacent LABs and another 10 possible from the right adjacent LAB. M4K RAM block outputs can also connect to left and right LABs through 10 direct link interconnects each. Figure 2–18 shows the M4K RAM block to logic array interface.

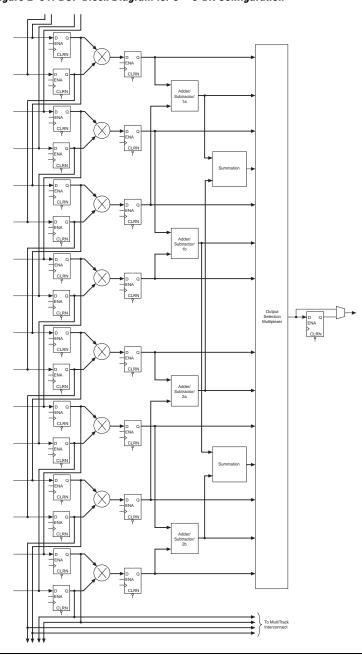

Figure 2–31. DSP Block Diagram for  $9 \times 9$ -Bit Configuration

#### Adder/Subtractor/Accumulator

The adder/subtractor/accumulator is the first level of the adder/output block and can be used as an accumulator or as an adder/subtractor.

#### Adder/Subtractor

Each adder/subtractor/accumulator block can perform addition or subtraction using the addnsub independent control signal for each first-level adder in  $18 \times 18$ -bit mode. There are two addnsub [1..0] signals available in a DSP block for any configuration. For  $9 \times 9$ -bit mode, one addnsub [1..0] signal controls the top two one-level adders and another addnsub [1..0] signal controls the bottom two one-level adders. A high addnsub signal indicates addition, and a low signal indicates subtraction. The addnsub control signal can be unregistered or registered once or twice when feeding the adder blocks to match data path pipelines.

The signa and signb signals serve the same function as the multiplier block signa and signb signals. The only difference is that these signals can be registered up to two times. These signals are tied to the same signa and signb signals from the multiplier and must be connected to the same clocks and control signals.

#### Accumulator

When configured for accumulation, the adder/output block output feeds back to the accumulator as shown in Figure 2–34. The accum\_sload[1..0] signal synchronously loads the multiplier result to the accumulator output. This signal can be unregistered or registered once or twice. Additionally, the overflow signal indicates the accumulator has overflowed or underflowed in accumulation mode. This signal is always registered and must be externally latched in LEs if the design requires a latched overflow signal.

#### Summation

The output of the adder/subtractor/accumulator block feeds to an optional summation block. This block sums the outputs of the DSP block multipliers. In 9  $\times$  9-bit mode, there are two summation blocks providing the sums of two sets of four 9  $\times$  9-bit multipliers. In 18  $\times$  18-bit mode, there is one summation providing the sum of one set of four 18  $\times$  18-bit multipliers.

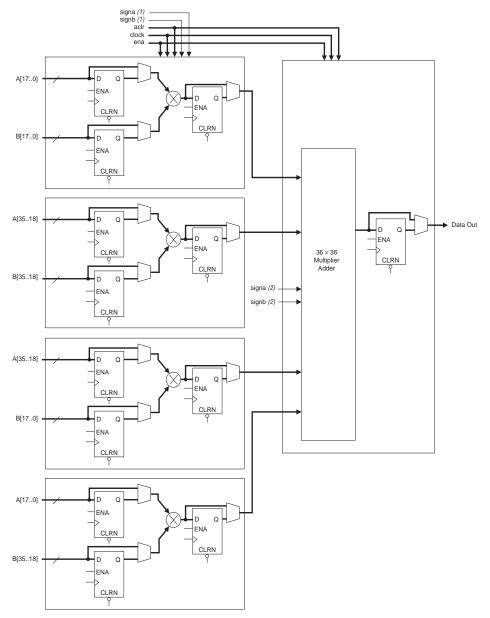

Figure 2–36. 36  $\times$  36 Multiply Mode

#### *Notes to Figure 2–36:*

- (1) These signals are not registered or registered once to match the pipeline.

- (2) These signals are not registered, registered once, or registered twice for latency to match the pipeline.

#### Clock Feedback

The following four feedback modes in Stratix device enhanced PLLs allow multiplication and/or phase and delay shifting:

- Zero delay buffer: The external clock output pin is phase-aligned with the clock input pin for zero delay. Altera recommends using the same I/O standard on the input clock and the output clocks for optimum performance.

- External feedback: The external feedback input pin, FBIN, is phase-aligned with the clock input, CLK, pin. Aligning these clocks allows you to remove clock delay and skew between devices. This mode is only possible for PLLs 5 and 6. PLLs 5 and 6 each support feedback for one of the dedicated external outputs, either one single-ended or one differential pair. In this mode, one *e* counter feeds back to the PLL FBIN input, becoming part of the feedback loop. Altera recommends using the same I/O standard on the input clock, the FBIN pin, and the output clocks for optimum performance.

- Normal mode: If an internal clock is used in this mode, it is phasealigned to the input clock pin. The external clock output pin will have a phase delay relative to the clock input pin if connected in this mode. You define which internal clock output from the PLL should be phase-aligned to the internal clock pin.

- No compensation: In this mode, the PLL will not compensate for any clock networks or external clock outputs.

#### Phase & Delay Shifting

Stratix device enhanced PLLs provide advanced programmable phase and clock delay shifting. These parameters are set in the Quartus II software.

#### Phase Delay

The Quartus II software automatically sets the phase taps and counter settings according to the phase shift entry. You enter a desired phase shift and the Quartus II software automatically sets the closest setting achievable. This type of phase shift is not reconfigurable during system operation. For phase shifting, enter a phase shift (in degrees or time units) for each PLL clock output port or for all outputs together in one shift. You can select phase-shifting values in time units with a resolution of 156.25 to 416.66 ps. This resolution is a function of frequency input and the multiplication and division factors (that is, it is a function of the VCO period), with the finest step being equal to an eighth (×0.125) of the VCO period. Each clock output counter can choose a different phase of the

#### External Clock Inputs

Each fast PLL supports single-ended or differential inputs for source synchronous transmitters or for general-purpose use. Source-synchronous receivers support differential clock inputs. The fast PLL inputs are fed by CLK [0..3], CLK [8..11], and FPLL [7..10] CLK pins, as shown in Figure 2–50 on page 2–85.

Table 2–22 shows the I/O standards supported by fast PLL input pins.

| LVCMOS                    |          |           |  |  |  |  |  |

|---------------------------|----------|-----------|--|--|--|--|--|

| I/O Ctondovd              | li li    | nput      |  |  |  |  |  |

| i/O Stailuaru             | INCLK    | PLLENABLE |  |  |  |  |  |

| LVTTL                     | ✓        | ✓         |  |  |  |  |  |

| LVCMOS                    | ✓        | ✓         |  |  |  |  |  |

| 2.5 V                     | ✓        |           |  |  |  |  |  |

| 1.8 V                     | ✓        |           |  |  |  |  |  |

| 1.5 V                     | ✓        |           |  |  |  |  |  |

| 3.3-V PCI                 |          |           |  |  |  |  |  |

| 3.3-V PCI-X 1.0           |          |           |  |  |  |  |  |

| LVPECL                    | <b>✓</b> |           |  |  |  |  |  |

| 3.3-V PCML                | <b>✓</b> |           |  |  |  |  |  |

| LVDS                      | ✓        |           |  |  |  |  |  |

| HyperTransport technology | ✓        |           |  |  |  |  |  |

| Differential HSTL         | ✓        |           |  |  |  |  |  |

| Differential SSTL         |          |           |  |  |  |  |  |

| 3.3-V GTL                 |          |           |  |  |  |  |  |

| 3.3-V GTL+                | ✓        |           |  |  |  |  |  |

| 1.5-V HSTL Class I        | ✓        |           |  |  |  |  |  |

| 1.5-V HSTL Class II       |          |           |  |  |  |  |  |

| 1.8-V HSTL Class I        | ✓        |           |  |  |  |  |  |

| 1.8-V HSTL Class II       |          |           |  |  |  |  |  |

| SSTL-18 Class I           | <b>✓</b> |           |  |  |  |  |  |

| SSTL-18 Class II          |          |           |  |  |  |  |  |

| SSTL-2 Class I            | ✓        |           |  |  |  |  |  |

## 3. Configuration & Testing

\$51003-1.3

## IEEE Std. 1149.1 (JTAG) Boundary-Scan Support

All Stratix® devices provide JTAG BST circuitry that complies with the IEEE Std. 1149.1a-1990 specification. JTAG boundary-scan testing can be performed either before or after, but not during configuration. Stratix devices can also use the JTAG port for configuration together with either the Quartus® II software or hardware using either Jam Files (.jam) or Jam Byte-Code Files (.jbc).

Stratix devices support IOE I/O standard setting reconfiguration through the JTAG BST chain. The JTAG chain can update the I/O standard for all input and output pins any time before or during user mode through the CONFIG\_IO instruction. You can use this ability for JTAG testing before configuration when some of the Stratix pins drive or receive from other devices on the board using voltage-referenced standards. Since the Stratix device may not be configured before JTAG testing, the I/O pins may not be configured for appropriate electrical standards for chip-to-chip communication. Programming those I/O standards via JTAG allows you to fully test the I/O connection to other devices.

The enhanced PLL reconfiguration bits are part of the JTAG chain before configuration and after power-up. After device configuration, the PLL reconfiguration bits are not part of the JTAG chain.

The JTAG pins support 1.5-V/1.8-V or 2.5-V/3.3-V I/O standards. The TDO pin voltage is determined by the  $V_{\rm CCIO}$  of the bank where it resides. The VCCSEL pin selects whether the JTAG inputs are 1.5-V, 1.8-V, 2.5-V, or 3.3-V compatible.

Stratix devices also use the JTAG port to monitor the logic operation of the device with the SignalTap<sup>®</sup> II embedded logic analyzer. Stratix devices support the JTAG instructions shown in Table 3–1.

The Quartus II software has an Auto Usercode feature where you can choose to use the checksum value of a programming file as the JTAG user code. If selected, the checksum is automatically loaded to the USERCODE register. In the Settings dialog box in the Assignments menu, click **Device & Pin Options**, then **General**, and then turn on the **Auto Usercode** option.

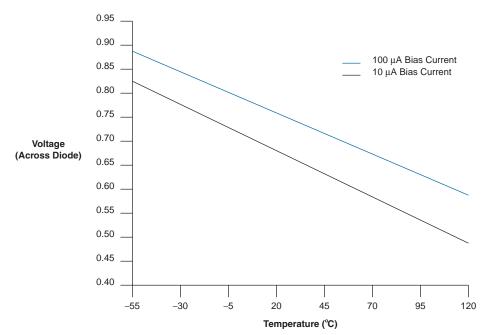

The temperature-sensing diode works for the entire operating range shown in Figure 3–6.

Figure 3-6. Temperature vs. Temperature-Sensing Diode Voltage

| Table 4–9. Overshoot Input Voltage with Respect to Duty Cycle (Part 2 of 2) |                        |  |  |  |  |

|-----------------------------------------------------------------------------|------------------------|--|--|--|--|

| Vin (V)                                                                     | Maximum Duty Cycle (%) |  |  |  |  |

| 4.3                                                                         | 30                     |  |  |  |  |

| 4.4                                                                         | 17                     |  |  |  |  |

| 4.5                                                                         | 10                     |  |  |  |  |

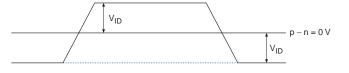

Figures 4–1 and 4–2 show receiver input and transmitter output waveforms, respectively, for all differential I/O standards (LVDS, 3.3-V PCML, LVPECL, and HyperTransport technology).

Figure 4-1. Receiver Input Waveforms for Differential I/O Standards

# Single-Ended Waveform Positive Channel (p) = $V_{IH}$ Negative Channel (n) = $V_{IL}$

#### **Differential Waveform**

| Table 4–41. M4<br>2 of 2) | Table 4–41. M4K Block Internal Timing Microparameter Descriptions (Part 2 of 2)                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Symbol                    | Parameter                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| t <sub>M4KDATAAH</sub>    | A port data hold time after clock                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| t <sub>M4KADDRASU</sub>   | A port address setup time before clock                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| t <sub>M4KADDRAH</sub>    | A port address hold time after clock                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| t <sub>M4KDATABSU</sub>   | B port data setup time before clock                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| t <sub>M4KDATABH</sub>    | B port data hold time after clock                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| t <sub>M4KADDRBSU</sub>   | B port address setup time before clock                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| t <sub>M4KADDRBH</sub>    | B port address hold time after clock                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| t <sub>M4KDATACO1</sub>   | Clock-to-output delay when using output registers                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| t <sub>M4KDATACO2</sub>   | Clock-to-output delay without output registers                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| t <sub>M4KCLKHL</sub>     | Register minimum clock high or low time. This is a limit on the min time for the clock on the registers in these blocks. The actual performance is dependent upon the internal point-to-point delays in the blocks and may give slower performance as shown inTable 4–36 on page 4–20 and as reported by the timing analyzer in the Quartus II software. |  |  |  |  |  |

Minimum clear pulse width

$t_{\mathsf{M4KCLR}}$

|                          | Table 4–42. M-RAM Block Internal Timing Microparameter Descriptions (Part 1 of 2) |  |  |  |  |  |

|--------------------------|-----------------------------------------------------------------------------------|--|--|--|--|--|

| Symbol                   | Parameter                                                                         |  |  |  |  |  |

| t <sub>MRAMRC</sub>      | Synchronous read cycle time                                                       |  |  |  |  |  |

| t <sub>MRAMWC</sub>      | Synchronous write cycle time                                                      |  |  |  |  |  |

| t <sub>MRAMWERESU</sub>  | Write or read enable setup time before clock                                      |  |  |  |  |  |

| t <sub>MRAMWEREH</sub>   | Write or read enable hold time after clock                                        |  |  |  |  |  |

| t <sub>MRAMCLKENSU</sub> | Clock enable setup time before clock                                              |  |  |  |  |  |

| t <sub>MRAMCLKENH</sub>  | Clock enable hold time after clock                                                |  |  |  |  |  |

| t <sub>MRAMBESU</sub>    | Byte enable setup time before clock                                               |  |  |  |  |  |

| t <sub>MRAMBEH</sub>     | Byte enable hold time after clock                                                 |  |  |  |  |  |

| t <sub>MRAMDATAASU</sub> | A port data setup time before clock                                               |  |  |  |  |  |

| t <sub>MRAMDATAAH</sub>  | A port data hold time after clock                                                 |  |  |  |  |  |

| t <sub>MRAMADDRASU</sub> | A port address setup time before clock                                            |  |  |  |  |  |

| t <sub>MRAMADDRAH</sub>  | A port address hold time after clock                                              |  |  |  |  |  |

| t <sub>MRAMDATABSU</sub> | B port setup time before clock                                                    |  |  |  |  |  |

|                          | Table 4–42. M-RAM Block Internal Timing Microparameter Descriptions (Part 2 of 2)                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Symbol                   | Parameter                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| $t_{MRAMDATABH}$         | B port hold time after clock                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| t <sub>MRAMADDRBSU</sub> | B port address setup time before clock                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| t <sub>MRAMADDRBH</sub>  | B port address hold time after clock                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| t <sub>MRAMDATACO1</sub> | Clock-to-output delay when using output registers                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| t <sub>MRAMDATACO2</sub> | Clock-to-output delay without output registers                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| t <sub>MRAMCLKHL</sub>   | Register minimum clock high or low time. This is a limit on the min time for the clock on the registers in these blocks. The actual performance is dependent upon the internal point-to-point delays in the blocks and may give slower performance as shown in Table 4–36 on page 4–20 and as reported by the timing analyzer in the Quartus II software. |  |  |  |  |  |

| t <sub>MRAMCLR</sub>     | Minimum clear pulse width.                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Device | Symbol            | -   | -5  |     | -6  |     | -7  |     | -8  |    |

|--------|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|----|

|        | Symbol            | Min | Max | Min | Max | Min | Max | Min | Max |    |

| EP1S40 | t <sub>SU_R</sub> | 76  |     | 80  |     | 80  |     | 80  |     | ps |

|        | t <sub>SU_C</sub> | 376 |     | 380 |     | 380 |     | 380 |     | ps |

| EP1S60 | t <sub>SU_R</sub> | 276 |     | 280 |     | 280 |     | 280 |     | ps |

|        | t <sub>SU_C</sub> | 276 |     | 280 |     | 280 |     | 280 |     | ps |

| EP1S80 | t <sub>SU_R</sub> | 426 |     | 430 |     | 430 |     | 430 |     | ps |

|        | t <sub>SU_C</sub> | 76  |     | 80  |     | 80  |     | 80  |     | ps |

| Table 4–46. IOE Internal Timing Microparameters |       |       |       |       |       |       |       |       |      |

|-------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Symbol                                          | -     | -5    |       | -6    |       | -7    |       | -8    |      |

|                                                 | Min   | Max   | Min   | Max   | Min   | Max   | Min   | Max   | Unit |

| t <sub>H</sub>                                  | 68    |       | 71    |       | 82    |       | 96    |       | ps   |

| t <sub>CO_R</sub>                               |       | 171   |       | 179   |       | 206   |       | 242   | ps   |

| t <sub>CO_C</sub>                               |       | 171   |       | 179   |       | 206   |       | 242   | ps   |

| t <sub>PIN2COMBOUT_R</sub>                      |       | 1,234 |       | 1,295 |       | 1,490 |       | 1,753 | ps   |

| t <sub>PIN2COMBOUT_C</sub>                      |       | 1,087 |       | 1,141 |       | 1,312 |       | 1,544 | ps   |

| t <sub>COMBIN2PIN_R</sub>                       |       | 3,894 |       | 4,089 |       | 4,089 |       | 4,089 | ps   |

| t <sub>COMBIN2PIN_C</sub>                       |       | 4,299 |       | 4,494 |       | 4,494 |       | 4,494 | ps   |

| t <sub>CLR</sub>                                | 276   |       | 289   |       | 333   |       | 392   |       | ps   |

| t <sub>PRE</sub>                                | 260   |       | 273   |       | 313   |       | 369   |       | ps   |

| t <sub>CLKHL</sub>                              | 1,000 |       | 1,111 |       | 1,190 |       | 1,400 |       | ps   |

| Table 4–47. DSP Block Internal Timing Microparameters (Part 1 of 2) |     |       |     |       |     |       |     |       |      |  |

|---------------------------------------------------------------------|-----|-------|-----|-------|-----|-------|-----|-------|------|--|

| Symbol                                                              | -5  |       | -6  |       | -7  |       | -8  |       | 1124 |  |

|                                                                     | Min | Max   | Min | Max   | Min | Max   | Min | Max   | Unit |  |

| t <sub>SU</sub>                                                     | 0   |       | 0   |       | 0   |       | 0   |       | ps   |  |

| t <sub>H</sub>                                                      | 67  |       | 75  |       | 86  |       | 101 |       | ps   |  |

| t <sub>CO</sub>                                                     |     | 142   |     | 158   |     | 181   |     | 214   | ps   |  |

| t <sub>INREG2PIPE9</sub>                                            |     | 2,613 |     | 2,982 |     | 3,429 |     | 4,035 | ps   |  |

| t <sub>INREG2PIPE18</sub>                                           |     | 3,390 |     | 3,993 |     | 4,591 |     | 5,402 | ps   |  |

| Table 4-77. L         | Table 4–77. EP1S30 External I/O Timing on Row Pins Using Regional Clock Networks |       |                |       |         |         |         |       |      |  |  |

|-----------------------|----------------------------------------------------------------------------------|-------|----------------|-------|---------|---------|---------|-------|------|--|--|

| Parameter             | -5 Speed Grade                                                                   |       | -6 Speed Grade |       | -7 Spee | d Grade | -8 Spee | 11    |      |  |  |

|                       | Min                                                                              | Max   | Min            | Max   | Min     | Max     | Min     | Max   | Unit |  |  |

| t <sub>INSU</sub>     | 2.322                                                                            |       | 2.467          |       | 2.828   |         | 3.342   |       | ns   |  |  |

| t <sub>INH</sub>      | 0.000                                                                            |       | 0.000          |       | 0.000   |         | 0.000   |       | ns   |  |  |

| t <sub>OUTCO</sub>    | 2.731                                                                            | 5.408 | 2.731          | 5.843 | 2.731   | 6.360   | 2.731   | 7.036 | ns   |  |  |

| t <sub>XZ</sub>       | 2.758                                                                            | 5.462 | 2.758          | 5.899 | 2.758   | 6.428   | 2.758   | 7.118 | ns   |  |  |

| t <sub>ZX</sub>       | 2.758                                                                            | 5.462 | 2.758          | 5.899 | 2.758   | 6.428   | 2.758   | 7.118 | ns   |  |  |

| t <sub>INSUPLL</sub>  | 1.291                                                                            |       | 1.283          |       | 1.469   |         | 1.832   |       | ns   |  |  |

| t <sub>INHPLL</sub>   | 0.000                                                                            |       | 0.000          |       | 0.000   |         | 0.000   |       | ns   |  |  |

| t <sub>OUTCOPLL</sub> | 1.192                                                                            | 2.539 | 1.192          | 2.737 | 1.192   | 2.786   | 1.192   | 2.742 | ns   |  |  |

| t <sub>XZPLL</sub>    | 1.219                                                                            | 2.539 | 1.219          | 2.793 | 1.219   | 2.854   | 1.219   | 2.824 | ns   |  |  |

| t <sub>ZXPLL</sub>    | 1.219                                                                            | 2.539 | 1.219          | 2.793 | 1.219   | 2.854   | 1.219   | 2.824 | ns   |  |  |

| Table 4–78. EP1S30 External I/O Timing on Row Pins Using Global Clock Networks |         |         |                |       |         |         |         |       |      |  |

|--------------------------------------------------------------------------------|---------|---------|----------------|-------|---------|---------|---------|-------|------|--|

| Parameter                                                                      | -5 Spee | d Grade | -6 Speed Grade |       | -7 Spee | d Grade | -8 Spee | 11-24 |      |  |

|                                                                                | Min     | Max     | Min            | Max   | Min     | Max     | Min     | Max   | Unit |  |

| t <sub>INSU</sub>                                                              | 1.995   |         | 2.089          |       | 2.398   |         | 2.830   |       | ns   |  |

| t <sub>INH</sub>                                                               | 0.000   |         | 0.000          |       | 0.000   |         | 0.000   |       | ns   |  |

| t <sub>OUTCO</sub>                                                             | 2.917   | 5.735   | 2.917          | 6.221 | 2.917   | 6.790   | 2.917   | 7.548 | ns   |  |

| t <sub>XZ</sub>                                                                | 2.944   | 5.789   | 2.944          | 6.277 | 2.944   | 6.858   | 2.944   | 7.630 | ns   |  |

| t <sub>ZX</sub>                                                                | 2.944   | 5.789   | 2.944          | 6.277 | 2.944   | 6.858   | 2.944   | 7.630 | ns   |  |

| t <sub>INSUPLL</sub>                                                           | 1.337   |         | 1.312          |       | 1.508   |         | 1.902   |       | ns   |  |

| t <sub>INHPLL</sub>                                                            | 0.000   |         | 0.000          |       | 0.000   |         | 0.000   |       | ns   |  |

| t <sub>OUTCOPLL</sub>                                                          | 1.164   | 2.493   | 1.164          | 2.708 | 1.164   | 2.747   | 1.164   | 2.672 | ns   |  |

| t <sub>XZPLL</sub>                                                             | 1.191   | 2.547   | 1.191          | 2.764 | 1.191   | 2.815   | 1.191   | 2.754 | ns   |  |

| t <sub>ZXPLL</sub>                                                             | 1.191   | 2.547   | 1.191          | 2.764 | 1.191   | 2.815   | 1.191   | 2.754 | ns   |  |

Tables 4–79 through 4–84 show the external timing parameters on column and row pins for EP1S40 devices.

| Table 4–79. EP1S40 External I/O Timing on Column Pins Using Fast Regional Clock Networks |                |       |                |       |                |       |                |       |      |  |

|------------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-------|------|--|

| Parameter                                                                                | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | IIi4 |  |

|                                                                                          | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max   | Unit |  |

| t <sub>INSU</sub>                                                                        | 2.696          |       | 2.907          |       | 3.290          |       | 2.899          |       | ns   |  |

| t <sub>INH</sub>                                                                         | 0.000          |       | 0.000          |       | 0.000          |       | 0.000          |       | ns   |  |

| t <sub>OUTCO</sub>                                                                       | 2.506          | 5.015 | 2.506          | 5.348 | 2.506          | 5.809 | 2.698          | 7.286 | ns   |  |

| t <sub>XZ</sub>                                                                          | 2.446          | 4.889 | 2.446          | 5.216 | 2.446          | 5.685 | 2.638          | 7.171 | ns   |  |

| t <sub>ZX</sub>                                                                          | 2.446          | 4.889 | 2.446          | 5.216 | 2.446          | 5.685 | 2.638          | 7.171 | ns   |  |

| Table 4–80. EP1S40 External I/O Timing on Column Pins Using Regional Clock Networks |                |       |                |       |         |         |         |       |      |  |

|-------------------------------------------------------------------------------------|----------------|-------|----------------|-------|---------|---------|---------|-------|------|--|

| Parameter                                                                           | -5 Speed Grade |       | -6 Speed Grade |       | -7 Spee | d Grade | -8 Spee | Heit  |      |  |

|                                                                                     | Min            | Max   | Min            | Max   | Min     | Max     | Min     | Max   | Unit |  |

| t <sub>INSU</sub>                                                                   | 2.413          |       | 2.581          |       | 2.914   |         | 2.938   |       | ns   |  |

| t <sub>INH</sub>                                                                    | 0.000          |       | 0.000          |       | 0.000   |         | 0.000   |       | ns   |  |

| t <sub>outco</sub>                                                                  | 2.668          | 5.254 | 2.668          | 5.628 | 2.668   | 6.132   | 2.869   | 7.307 | ns   |  |

| t <sub>XZ</sub>                                                                     | 2.608          | 5.128 | 2.608          | 5.496 | 2.608   | 6.008   | 2.809   | 7.192 | ns   |  |

| t <sub>ZX</sub>                                                                     | 2.608          | 5.128 | 2.608          | 5.496 | 2.608   | 6.008   | 2.809   | 7.192 | ns   |  |

| t <sub>INSUPLL</sub>                                                                | 1.385          |       | 1.376          |       | 1.609   |         | 1.837   |       | ns   |  |

| t <sub>INHPLL</sub>                                                                 | 0.000          |       | 0.000          |       | 0.000   |         | 0.000   |       | ns   |  |

| toutcopll                                                                           | 1.117          | 2.382 | 1.117          | 2.552 | 1.117   | 2.504   | 1.117   | 2.542 | ns   |  |

| t <sub>XZPLL</sub>                                                                  | 1.057          | 2.256 | 1,057          | 2.420 | 1.057   | 2.380   | 1.057   | 2.427 | ns   |  |

| t <sub>ZXPLL</sub>                                                                  | 1.057          | 2.256 | 1,057          | 2.420 | 1.057   | 2.380   | 1.057   | 2.427 | ns   |  |

| Table 4–105. Stratix I/O Standard Output Delay Adders for Fast Slew Rate on Column Pins (Part 2 of 2) |         |                |     |                |     |                |     |                |      |

|-------------------------------------------------------------------------------------------------------|---------|----------------|-----|----------------|-----|----------------|-----|----------------|------|

| Parameter                                                                                             | -5 Spee | -5 Speed Grade |     | -6 Speed Grade |     | -7 Speed Grade |     | -8 Speed Grade |      |

|                                                                                                       | Min     | Max            | Min | Max            | Min | Max            | Min | Max            | Unit |

| CTT                                                                                                   |         | 973            |     | 1,021          |     | 1,021          |     | 1,021          | ps   |

| SSTL-3 Class I                                                                                        |         | 719            |     | 755            |     | 755            |     | 755            | ps   |

| SSTL-3 Class II                                                                                       |         | 146            |     | 153            |     | 153            |     | 153            | ps   |

| SSTL-2 Class I                                                                                        |         | 678            |     | 712            |     | 712            |     | 712            | ps   |

| SSTL-2 Class II                                                                                       |         | 223            |     | 234            |     | 234            |     | 234            | ps   |

| SSTL-18 Class I                                                                                       |         | 1,032          |     | 1,083          |     | 1,083          |     | 1,083          | ps   |

| SSTL-18 Class II                                                                                      |         | 447            |     | 469            |     | 469            |     | 469            | ps   |

| 1.5-V HSTL Class I                                                                                    |         | 660            |     | 693            |     | 693            |     | 693            | ps   |

| 1.5-V HSTL Class II                                                                                   |         | 537            |     | 564            |     | 564            |     | 564            | ps   |

| 1.8-V HSTL Class I                                                                                    |         | 304            |     | 319            |     | 319            |     | 319            | ps   |

| 1.8-V HSTL Class II                                                                                   |         | 231            |     | 242            |     | 242            |     | 242            | ps   |

| Table 4–106. Stratix I/O Standard Output Delay Adders for Fast Slew Rate on Row Pins (Part 1 of 2) |       |                |       |                |       |                |       |                |       |       |

|----------------------------------------------------------------------------------------------------|-------|----------------|-------|----------------|-------|----------------|-------|----------------|-------|-------|

| Рокото                                                                                             | ator. | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | Unit  |

| Parameter                                                                                          |       | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max   | UIIIL |

| LVCMOS                                                                                             | 2 mA  |                | 1,518 |                | 1,594 |                | 1,594 |                | 1,594 | ps    |

|                                                                                                    | 4 mA  |                | 746   |                | 783   |                | 783   |                | 783   | ps    |

|                                                                                                    | 8 mA  |                | 96    |                | 100   |                | 100   |                | 100   | ps    |

|                                                                                                    | 12 mA |                | 0     |                | 0     |                | 0     |                | 0     | ps    |

| 3.3-V LVTTL                                                                                        | 4 mA  |                | 1,518 |                | 1,594 |                | 1,594 |                | 1,594 | ps    |

|                                                                                                    | 8 mA  |                | 1,038 |                | 1,090 |                | 1,090 |                | 1,090 | ps    |

|                                                                                                    | 12 mA |                | 521   |                | 547   |                | 547   |                | 547   | ps    |

|                                                                                                    | 16 mA |                | 414   |                | 434   |                | 434   |                | 434   | ps    |

|                                                                                                    | 24 mA |                | 0     |                | 0     |                | 0     |                | 0     | ps    |

| 2.5-V LVTTL                                                                                        | 2 mA  |                | 2,032 |                | 2,133 |                | 2,133 |                | 2,133 | ps    |

|                                                                                                    | 8 mA  |                | 699   |                | 734   |                | 734   |                | 734   | ps    |

|                                                                                                    | 12 mA |                | 374   |                | 392   |                | 392   |                | 392   | ps    |

|                                                                                                    | 16 mA |                | 165   |                | 173   |                | 173   |                | 173   | ps    |

| 1.8-V LVTTL                                                                                        | 2 mA  |                | 3,714 |                | 3,899 |                | 3,899 |                | 3,899 | ps    |

|                                                                                                    | 8 mA  |                | 1,055 |                | 1,107 |                | 1,107 |                | 1,107 | ps    |

|                                                                                                    | 12 mA |                | 830   |                | 871   |                | 871   |                | 871   | ps    |

# Table 4–123. Stratix Maximum Output Clock Rate (Using I/O Pins) for PLL[1, 2, 3, 4] Pins in Wire-Bond Packages (Part 2 of 2)

| I/O Standard                  | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |  |

|-------------------------------|-------------------|-------------------|-------------------|------|--|

| LVDS (2)                      | 400               | 311               | 311               | MHz  |  |

| HyperTransport technology (2) | 420               | 400               | 400               | MHz  |  |

#### Notes to Tables 4-120 through 4-123:

- (1) Differential SSTL-2 outputs are only available on column clock pins.

- (2) These parameters are only available on row I/O pins.

- (3) SSTL-2 in maximum drive strength condition. See Table 4–101 on page 4–62 for more information on exact loading conditions for each I/O standard.

- (4) SSTL-2 in minimum drive strength with  $\leq$ 10pF output load condition.

- (5) SSTL-2 in minimum drive strength with > 10pF output load condition.

- (6) Differential SSTL-2 outputs are only supported on column clock pins.

| Table 4-12               | Table 4–129. Enhanced PLL Specifications for -7 Speed Grade (Part 2 of 2)                                         |     |     |                                                            |              |  |  |  |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|------------------------------------------------------------|--------------|--|--|--|--|--|

| Symbol                   | Parameter                                                                                                         | Min | Тур | Max                                                        | Unit         |  |  |  |  |  |

| t <sub>OUTDUTY</sub>     | Duty cycle for external clock output (when set to 50%)                                                            | 45  |     | 55                                                         | %            |  |  |  |  |  |

| t <sub>JITTER</sub>      | Period jitter for external clock output (6)                                                                       |     |     | ±100 ps for >200-MHz outclk<br>±20 mUI for <200-MHz outclk | ps or<br>mUI |  |  |  |  |  |

| t <sub>CONFIG5,6</sub>   | Time required to reconfigure the scan chains for PLLs 5 and 6                                                     |     |     | 289/f <sub>SCANCLK</sub>                                   |              |  |  |  |  |  |

| t <sub>CONFIG11,12</sub> | Time required to reconfigure the scan chains for PLLs 11 and 12                                                   |     |     | 193/f <sub>SCANCLK</sub>                                   |              |  |  |  |  |  |

| t <sub>SCANCLK</sub>     | scanclk frequency (5)                                                                                             |     |     | 22                                                         | MHz          |  |  |  |  |  |

| t <sub>DLOCK</sub>       | Time required to lock dynamically (after switchover or reconfiguring any non-post-scale counters/delays) (7) (11) | (9) |     | 100                                                        | μs           |  |  |  |  |  |

| t <sub>LOCK</sub>        | Time required to lock from end of device configuration (11)                                                       | 10  |     | 400                                                        | μs           |  |  |  |  |  |

| f <sub>VCO</sub>         | PLL internal VCO operating range                                                                                  | 300 |     | 600 (8)                                                    | MHz          |  |  |  |  |  |

| t <sub>LSKEW</sub>       | Clock skew between two external clock outputs driven by the same counter                                          |     | ±50 |                                                            | ps           |  |  |  |  |  |

| t <sub>SKEW</sub>        | Clock skew between two external clock outputs driven by the different counters with the same settings             |     | ±75 |                                                            | ps           |  |  |  |  |  |

| f <sub>SS</sub>          | Spread spectrum modulation frequency                                                                              | 30  |     | 150                                                        | kHz          |  |  |  |  |  |

| % spread                 | Percentage spread for spread spectrum frequency (10)                                                              | 0.5 |     | 0.6                                                        | %            |  |  |  |  |  |

| t <sub>ARESET</sub>      | Minimum pulse width on areset signal                                                                              | 10  |     |                                                            | ns           |  |  |  |  |  |

| Table 4–130. Enhanced PLL Specifications for -8 Speed Grade (Part 1 of 3) |                                          |               |     |          |      |  |  |  |  |

|---------------------------------------------------------------------------|------------------------------------------|---------------|-----|----------|------|--|--|--|--|

| Symbol                                                                    | Parameter                                | Min           | Тур | Max      | Unit |  |  |  |  |

| f <sub>IN</sub>                                                           | Input clock frequency                    | 3<br>(1), (2) |     | 480      | MHz  |  |  |  |  |

| f <sub>INPFD</sub>                                                        | Input frequency to PFD                   | 3             |     | 420      | MHz  |  |  |  |  |

| f <sub>INDUTY</sub>                                                       | Input clock duty cycle                   | 40            |     | 60       | %    |  |  |  |  |

| f <sub>EINDUTY</sub>                                                      | External feedback clock input duty cycle | 40            |     | 60       | %    |  |  |  |  |

| t <sub>INJITTER</sub>                                                     | Input clock period jitter                |               |     | ±200 (3) | ps   |  |  |  |  |