Welcome to **E-XFL.COM**

### Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 1846                                                    |

| Number of Logic Elements/Cells | 18460                                                   |

| Total RAM Bits                 | 1669248                                                 |

| Number of I/O                  | 586                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                         |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 780-BBGA, FCBGA                                         |

| Supplier Device Package        | 780-FBGA (29x29)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s20f780c6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Copyright © 2006 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published in

formation and before placing orders for products or services.

I.S. EN ISO 9001

ii Altera Corporation

#### **About This Handbook**

This handbook provides comprehensive information about the Altera® Stratix family of devices.

## How to Find Information

You can find more information in the following ways:

- The Adobe Acrobat Find feature, which searches the text of a PDF document. Click the binoculars toolbar icon to open the Find dialog box.

- Acrobat bookmarks, which serve as an additional table of contents in PDF documents.

- Thumbnail icons, which provide miniature previews of each page, provide a link to the pages.

- Numerous links, shown in green text, which allow you to jump to related information.

#### How to Contact Altera

For the most up-to-date information about Altera products, go to the Altera world-wide web site at www.altera.com. For technical support on this product, go to www.altera.com/mysupport. For additional information about Altera products, consult the sources shown below.

| Information Type               | USA & Canada                                                   | All Other Locations                                                    |

|--------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------|

| Technical support              | www.altera.com/mysupport/                                      | www.altera.com/mysupport/                                              |

|                                | (800) 800-EPLD (3753)<br>(7:00 a.m. to 5:00 p.m. Pacific Time) | +1 408-544-8767<br>7:00 a.m. to 5:00 p.m. (GMT -8:00)<br>Pacific Time  |

| Product literature             | www.altera.com                                                 | www.altera.com                                                         |

| Altera literature services     | literature@altera.com                                          | literature@altera.com                                                  |

| Non-technical customer service | (800) 767-3753                                                 | + 1 408-544-7000<br>7:00 a.m. to 5:00 p.m. (GMT -8:00)<br>Pacific Time |

| FTP site                       | ftp.altera.com                                                 | ftp.altera.com                                                         |

Altera Corporation ix

## Section I. Stratix Device Family Data Sheet

This section provides the data sheet specifications for Stratix® devices. They contain feature definitions of the internal architecture, configuration and JTAG boundary-scan testing information, DC operating conditions, AC timing parameters, a reference to power consumption, and ordering information for Stratix devices.

This section contains the following chapters:

- Chapter 1, Introduction

- Chapter 2, Stratix Architecture

- Chapter 3, Configuration & Testing

- Chapter 4, DC & Switching Characteristics

- Chapter 5, Reference & Ordering Information

#### **Revision History**

The table below shows the revision history for Chapters 1 through 5.

| Chapter | Date/Version         | Changes Made                                                                                                                                                                                                                                                                                                                     |

|---------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | July 2005, v3.2      | Minor content changes.                                                                                                                                                                                                                                                                                                           |

|         | September 2004, v3.1 | Updated Table 1–6 on page 1–5.                                                                                                                                                                                                                                                                                                   |

|         | April 2004, v3.0     | <ul> <li>Main section page numbers changed on first page.</li> <li>Changed PCI-X to PCI-X 1.0 in "Features" on page 1–2.</li> <li>Global change from SignalTap to SignalTap II.</li> <li>The DSP blocks in "Features" on page 1–2 provide dedicated implementation of multipliers that are now "faster than 300 MHz."</li> </ul> |

|         | January 2004, v2.2   | Updated -5 speed grade device information in Table 1-6.                                                                                                                                                                                                                                                                          |

|         | October 2003, v2.1   | Add -8 speed grade device information.                                                                                                                                                                                                                                                                                           |

|         | July 2003, v2.0      | Format changes throughout chapter.                                                                                                                                                                                                                                                                                               |

Altera Corporation Section I–1

#### 2. Stratix Architecture

\$51002-3.2

## Functional Description

Stratix® devices contain a two-dimensional row- and column-based architecture to implement custom logic. A series of column and row interconnects of varying length and speed provide signal interconnects between logic array blocks (LABs), memory block structures, and DSP blocks.

The logic array consists of LABs, with 10 logic elements (LEs) in each LAB. An LE is a small unit of logic providing efficient implementation of user logic functions. LABs are grouped into rows and columns across the device.

M512 RAM blocks are simple dual-port memory blocks with 512 bits plus parity (576 bits). These blocks provide dedicated simple dual-port or single-port memory up to 18-bits wide at up to 318 MHz. M512 blocks are grouped into columns across the device in between certain LABs.

M4K RAM blocks are true dual-port memory blocks with 4K bits plus parity (4,608 bits). These blocks provide dedicated true dual-port, simple dual-port, or single-port memory up to 36-bits wide at up to 291 MHz. These blocks are grouped into columns across the device in between certain LABs.

M-RAM blocks are true dual-port memory blocks with 512K bits plus parity (589,824 bits). These blocks provide dedicated true dual-port, simple dual-port, or single-port memory up to 144-bits wide at up to 269 MHz. Several M-RAM blocks are located individually or in pairs within the device's logic array.

Digital signal processing (DSP) blocks can implement up to either eight full-precision  $9\times 9$ -bit multipliers, four full-precision  $18\times 18$ -bit multipliers, or one full-precision  $36\times 36$ -bit multiplier with add or subtract features. These blocks also contain 18-bit input shift registers for digital signal processing applications, including FIR and infinite impulse response (IIR) filters. DSP blocks are grouped into two columns in each device.

Each Stratix device I/O pin is fed by an I/O element (IOE) located at the end of LAB rows and columns around the periphery of the device. I/O pins support numerous single-ended and differential I/O standards. Each IOE contains a bidirectional I/O buffer and six registers for registering input, output, and output-enable signals. When used with

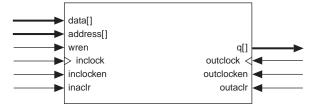

In addition to true dual-port memory, the memory blocks support simple dual-port and single-port RAM. Simple dual-port memory supports a simultaneous read and write and can either read old data before the write occurs or just read the don't care bits. Single-port memory supports non-simultaneous reads and writes, but the q[] port will output the data once it has been written to the memory (if the outputs are not registered) or after the next rising edge of the clock (if the outputs are registered). For more information, see Chapter 2, TriMatrix Embedded Memory Blocks in Stratix & Stratix GX Devices of the *Stratix Device Handbook, Volume 2*. Figure 2–13 shows these different RAM memory port configurations for TriMatrix memory.

Figure 2–13. Simple Dual-Port & Single-Port Memory Configurations

# data[] rdaddress[] wraddress[] rden wren q[] inclock outclock inclocken outclocken inaclr outaclr

#### Single-Port Memory (1)

Simple Dual-Port Memory

Note to Figure 2-13:

Two single-port memory blocks can be implemented in a single M4K block as long as each of the two independent block sizes is equal to or less than half of the M4K block size.

The memory blocks also enable mixed-width data ports for reading and writing to the RAM ports in dual-port RAM configuration. For example, the memory block can be written in  $\times 1$  mode at port A and read out in  $\times 16$  mode from port B.

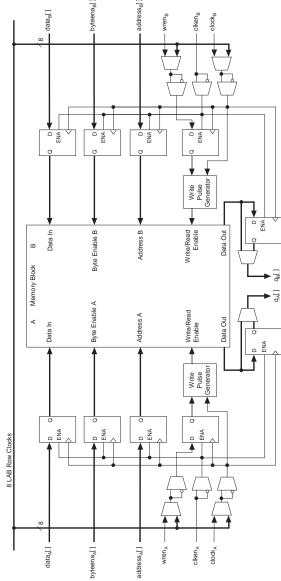

Figure 2–24. Independent Clock Mode Notes (1), (2)

Notes to Figure 2-24

- (1) All registers shown have asynchronous clear ports.

- (2) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

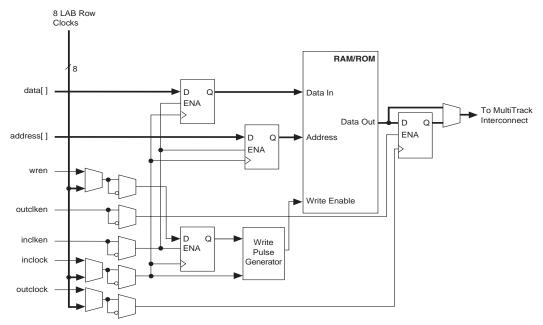

#### **Single-Port Mode**

The memory blocks also support single-port mode, used when simultaneous reads and writes are not required. See Figure 2–28. A single block in a memory block can support up to two single-port mode RAM blocks in the M4K RAM blocks if each RAM block is less than or equal to 2K bits in size.

Figure 2–28. Single-Port Mode Note (1)

Note to Figure 2-28:

(1) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

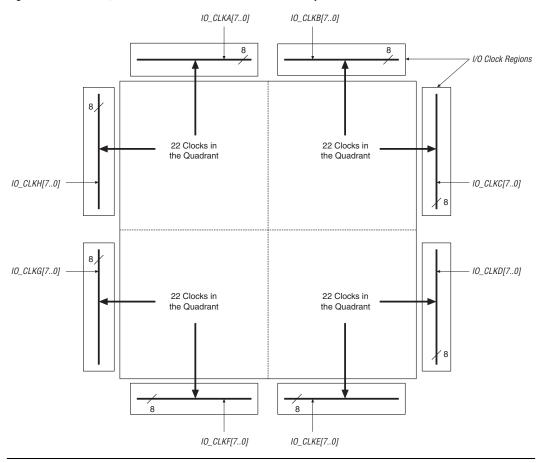

Figure 2-47. EP1S10, EP1S20 & EP1S25 Device I/O Clock Groups

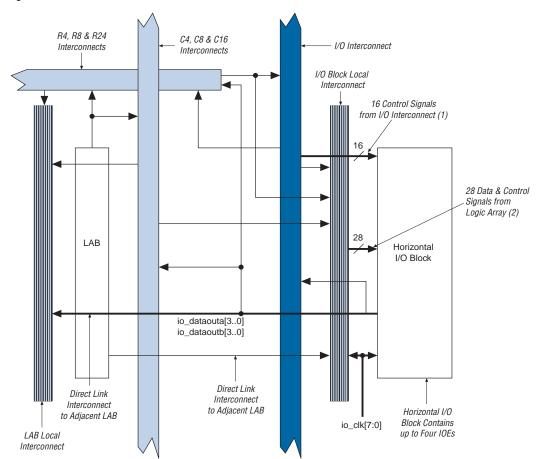

Figure 2-60. Row I/O Block Connection to the Interconnect

#### *Notes to Figure 2–60:*

- (1) The 16 control signals are composed of four output enables io\_boe[3..0], four clock enables io\_boe[3..0], four clocks io\_clk[3..0], and four clear signals io\_bclr[3..0].

- (2) The 28 data and control signals consist of eight data out lines: four lines each for DDR applications io\_dataouta[3..0] and io\_dataoutb[3..0], four output enables io\_coe[3..0], four input clock enables io\_cce\_in[3..0], four output clock enables io\_cce\_out[3..0], four clocks io\_cclk[3..0], and four clear signals io\_cclr[3..0].

Stratix devices have an I/O interconnect similar to the R4 and C4 interconnect to drive high-fanout signals to and from the I/O blocks. There are 16 signals that drive into the I/O blocks composed of four output enables <code>io\_boe[3..0]</code>, four clock enables <code>io\_bce[3..0]</code>, four clocks <code>io\_bclk[3..0]</code>, and four clear signals <code>io\_bclr[3..0]</code>. The pin's <code>datain</code> signals can drive the IO interconnect, which in turn drives the logic array or other I/O blocks. In addition, the control and data signals can be driven from the logic array, providing a slower but more flexible routing resource. The row or column IOE clocks, <code>io\_clk[7..0]</code>, provide a dedicated routing resource for low-skew, high-speed clocks. I/O clocks are generated from regional, global, or fast regional clocks (see "PLLs & Clock Networks" on page 2–73). Figure 2–62 illustrates the signal paths through the I/O block.

Row or Column io\_clk[7..0] io\_boe[3..0] To Other io\_bce[3..0] 10Es From I/O Interconnect io\_bclk[3..0] io\_bclr[3..0] io\_datain0 To Logic Array io datain1 ◀ oe ce\_in ce\_out io coe Control IOE aclr/apreset io cce in Signal Selection sclr/spreset io cce out clk in From Logic io\_cclr Array clk out io\_cclk io\_dataout0 io\_dataout1

Figure 2-62. Signal Path through the I/O Block

Table 2–28 shows the possible settings for the I/O standards with drive strength control.

| Table 2–28. Programmable Drive Strength                                                                                         |                                                                 |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|--|--|--|--|

| I/O Standard                                                                                                                    | I <sub>OH</sub> / I <sub>OL</sub> Current Strength Setting (mA) |  |  |  |  |  |  |

| 3.3-V LVTTL                                                                                                                     | 24 (1), 16, 12, 8, 4                                            |  |  |  |  |  |  |

| 3.3-V LVCMOS                                                                                                                    | 24 (2), 12 (1), 8, 4, 2                                         |  |  |  |  |  |  |

| 2.5-V LVTTL/LVCMOS                                                                                                              | 16 (1), 12, 8, 2                                                |  |  |  |  |  |  |

| 1.8-V LVTTL/LVCMOS                                                                                                              | 12 (1), 8, 2                                                    |  |  |  |  |  |  |

| 1.5-V LVCMOS                                                                                                                    | 8 (1), 4, 2                                                     |  |  |  |  |  |  |

| GTL/GTL+ 1.5-V HSTL Class I and II 1.8-V HSTL Class I and II SSTL-3 Class I and II SSTL-2 Class I and II SSTL-18 Class I and II | Support max and min strength                                    |  |  |  |  |  |  |

Notes to Table 2-28:

- (1) This is the Quartus II software default current setting.

- (2) I/O banks 1, 2, 5, and 6 do not support this setting.

Quartus II software version 4.2 and later will report current strength as "PCI Compliant" for 3.3-V PCI, 3.3-V PCI-X 1.0, and Compact PCI I/O standards.

Stratix devices support series on-chip termination (OCT) using programmable drive strength. For more information, contact your Altera Support Representative.

#### Open-Drain Output

Stratix devices provide an optional open-drain (equivalent to an open-collector) output for each I/O pin. This open-drain output enables the device to provide system-level control signals (e.g., interrupt and write-enable signals) that can be asserted by any of several devices.

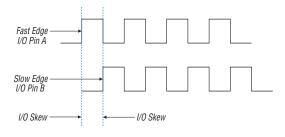

#### Slew-Rate Control

The output buffer for each Stratix device I/O pin has a programmable output slew-rate control that can be configured for low-noise or high-speed performance. A faster slew rate provides high-speed transitions for high-performance systems. However, these fast transitions may introduce noise transients into the system. A slow slew rate reduces system noise, but adds a nominal delay to rising and falling edges. Each

The output levels are compatible with systems of the same voltage as the power supply (i.e., when VCCIO pins are connected to a 1.5-V power supply, the output levels are compatible with 1.5-V systems). When VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3 V and is compatible with 3.3-V or 5.0-V systems.

Table 2–36 summarizes Stratix MultiVolt I/O support.

| Table 2–36. Stra      | Table 2–36. Stratix MultiVolt I/O Support Note (1) |                  |              |              |              |              |                   |              |          |          |  |

|-----------------------|----------------------------------------------------|------------------|--------------|--------------|--------------|--------------|-------------------|--------------|----------|----------|--|

| V <sub>CCIO</sub> (V) |                                                    | Input Signal (5) |              |              |              |              | Output Signal (6) |              |          |          |  |

|                       | 1.5 V                                              | 1.8 V            | 2.5 V        | 3.3 V        | 5.0 V        | 1.5 V        | 1.8 V             | 2.5 V        | 3.3 V    | 5.0 V    |  |

| 1.5                   | <b>✓</b>                                           | <b>✓</b>         | <b>√</b> (2) | <b>√</b> (2) |              | <b>✓</b>     |                   |              |          |          |  |

| 1.8                   | <b>√</b> (2)                                       | <b>✓</b>         | <b>√</b> (2) | <b>√</b> (2) |              | <b>✓</b> (3) | <b>✓</b>          |              |          |          |  |

| 2.5                   |                                                    |                  | <b>✓</b>     | <b>✓</b>     |              | <b>√</b> (3) | <b>√</b> (3)      | <b>✓</b>     |          |          |  |

| 3.3                   |                                                    |                  | <b>√</b> (2) | <b>✓</b>     | <b>✓</b> (4) | <b>✓</b> (3) | <b>√</b> (3)      | <b>√</b> (3) | <b>✓</b> | <b>✓</b> |  |

#### Notes to Table 2-36:

- (1) To drive inputs higher than  $V_{CCIO}$  but less than 4.1 V, disable the PCI clamping diode. However, to drive 5.0-V inputs to the device, enable the PCI clamping diode to prevent  $V_{\rm I}$  from rising above 4.0 V.

- (2) The input pin current may be slightly higher than the typical value.

- (3) Although  $V_{CCIO}$  specifies the voltage necessary for the Stratix device to drive out, a receiving device powered at a different level can still interface with the Stratix device if it has inputs that tolerate the  $V_{CCIO}$  value.

- (4) Stratix devices can be 5.0-V tolerant with the use of an external resistor and the internal PCI clamp diode.

- (5) This is the external signal that is driving the Stratix device.

- (6) This represents the system voltage that Stratix supports when a VCCIO pin is connected to a specific voltage level. For example, when VCCIO is 3.3 V and if the I/O standard is LVTTL/LVCMOS, the output high of the signal coming out from Stratix is 3.3 V and is compatible with 3.3-V or 5.0-V systems.

#### High-Speed Differential I/O Support

Stratix devices contain dedicated circuitry for supporting differential standards at speeds up to 840 Mbps. The following differential I/O standards are supported in the Stratix device: LVDS, LVPECL, HyperTransport, and 3.3-V PCML.

There are four dedicated high-speed PLLs in the EP1S10 to EP1S25 devices and eight dedicated high-speed PLLs in the EP1S30 to EP1S80 devices to multiply reference clocks and drive high-speed differential SERDES channels.

See the Stratix device pin-outs at **www.altera.com** for additional high speed DIFFIO pin information for Stratix devices.

For Stratix, the CRC is computed by the Quartus II software and downloaded into the device as a part of the configuration bit stream. The CRC\_ERROR pin reports a soft error when configuration SRAM data is corrupted, triggering device reconfiguration.

#### **Custom-Built Circuitry**

Dedicated circuitry is built in the Stratix devices to perform error detection automatically. You can use the built-in dedicated circuitry for error detection using CRC feature in Stratix devices, eliminating the need for external logic. This circuitry will perform error detection automatically when enabled. This error detection circuitry in Stratix devices constantly checks for errors in the configuration SRAM cells while the device is in user mode. You can monitor one external pin for the error and use it to trigger a re-configuration cycle. Select the desired time between checks by adjusting a built-in clock divider.

#### **Software Interface**

In the Quartus II software version 4.1 and later, you can turn on the automated error detection CRC feature in the **Device & Pin Options** dialog box. This dialog box allows you to enable the feature and set the internal frequency of the CRC between 400 kHz to 100 MHz. This controls the rate that the CRC circuitry verifies the internal configuration SRAM bits in the FPGA device.

For more information on CRC, see AN 357: Error Detection Using CRC in Altera FPGA Devices.

#### Temperature Sensing Diode

Stratix devices include a diode-connected transistor for use as a temperature sensor in power management. This diode is used with an external digital thermometer device such as a MAX1617A or MAX1619 from MAXIM Integrated Products. These devices steer bias current through the Stratix diode, measuring forward voltage and converting this reading to temperature in the form of an 8-bit signed number (7 bits plus sign). The external device's output represents the junction temperature of the Stratix device and can be used for intelligent power management.

The diode requires two pins (tempdiodep and tempdioden) on the Stratix device to connect to the external temperature-sensing device, as shown in Figure 3–5. The temperature sensing diode is a passive element and therefore can be used before the Stratix device is powered.

device. Decoupling capacitors were not used in this measurement. To factor in the current for decoupling capacitors, sum up the current for each capacitor using the following equation:

$$I = C (dV/dt)$$

If the regulator or power supply minimum output current is more than the Stratix device requires, then the device may consume more current than the maximum current listed in Table 4–34. However, the device does not require any more current to successfully power up than what is listed in Table 4–34.

| Table 4–34. Strat | Table 4–34. Stratix Power-Up Current (I <sub>CCINT</sub> ) Requirements Note (1) |                              |      |  |  |  |  |  |  |

|-------------------|----------------------------------------------------------------------------------|------------------------------|------|--|--|--|--|--|--|

| Device            | Power-Up Curre                                                                   | Power-Up Current Requirement |      |  |  |  |  |  |  |

| Device            | Typical                                                                          | Maximum                      | Unit |  |  |  |  |  |  |

| EP1S10            | 250                                                                              | 700                          | mA   |  |  |  |  |  |  |

| EP1S20            | 400                                                                              | 1,200                        | mA   |  |  |  |  |  |  |

| EP1S25            | 500                                                                              | 1,500                        | mA   |  |  |  |  |  |  |

| EP1S30            | 550                                                                              | 1,900                        | mA   |  |  |  |  |  |  |

| EP1S40            | 650                                                                              | 2,300                        | mA   |  |  |  |  |  |  |

| EP1S60            | 800                                                                              | 2,600                        | mA   |  |  |  |  |  |  |

| EP1S80            | 1,000                                                                            | 3,000                        | mA   |  |  |  |  |  |  |

Note to Table 4-34:

The exact amount of current consumed varies according to the process, temperature, and power ramp rate. Stratix devices typically require less current during power up than shown in Table 4–34. The user-mode current during device operation is generally higher than the power-up current.

The duration of the  $I_{CCINT}$  power-up requirement depends on the  $V_{CCINT}$  voltage supply rise time. The power-up current consumption drops when the  $V_{CCINT}$  supply reaches approximately 0.75 V.

<sup>(1)</sup> The maximum test conditions are for  $0^{\circ}$  C and typical test conditions are for  $40^{\circ}$  C

#### **Performance**

Table 4–36 shows Stratix performance for some common designs. All performance values were obtained with Quartus II software compilation of LPM, or MegaCore $^{\rm @}$  functions for the FIR and FFT designs.

| Table 4-36       | Table 4–36. Stratix Performance (Part 1 of 2) Notes (1), (2) |     |                               |               |                      |                      |                      |                      |       |  |

|------------------|--------------------------------------------------------------|-----|-------------------------------|---------------|----------------------|----------------------|----------------------|----------------------|-------|--|

|                  |                                                              | F   | Resources L                   | Jsed          | Performance          |                      |                      |                      |       |  |

| ļ                | Applications                                                 | LEs | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -5<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade | Units |  |

| LE               | 16-to-1 multiplexer (1)                                      | 22  | 0                             | 0             | 407.83               | 324.56               | 288.68               | 228.67               | MHz   |  |

|                  | 32-to-1 multiplexer (3)                                      | 46  | 0                             | 0             | 318.26               | 255.29               | 242.89               | 185.18               | MHz   |  |

|                  | 16-bit counter                                               | 16  | 0                             | 0             | 422.11               | 422.11               | 390.01               | 348.67               | MHz   |  |

|                  | 64-bit counter                                               | 64  | 0                             | 0             | 321.85               | 290.52               | 261.23               | 220.5                | MHz   |  |

| TriMatrix memory | Simple dual-port RAM 32 × 18 bit                             | 0   | 1                             | 0             | 317.76               | 277.62               | 241.48               | 205.21               | MHz   |  |

|                  | FIFO 32 × 18 bit                                             | 30  | 1                             | 0             | 319.18               | 278.86               | 242.54               | 206.14               | MHz   |  |

| TriMatrix memory | Simple dual-port RAM<br>128 × 36 bit                         | 0   | 1                             | 0             | 290.86               | 255.55               | 222.27               | 188.89               | MHz   |  |

| M4K block        | True dual-port RAM<br>128 × 18 bit                           | 0   | 1                             | 0             | 290.86               | 255.55               | 222.27               | 188.89               | MHz   |  |

|                  | FIFO 128 × 36 bit                                            | 34  | 1                             | 0             | 290.86               | 255.55               | 222.27               | 188.89               | MHz   |  |

| TriMatrix memory | Single port<br>RAM 4K × 144 bit                              | 1   | 1                             | 0             | 255.95               | 223.06               | 194.06               | 164.93               | MHz   |  |

| M-RAM<br>block   | Simple dual-port<br>RAM 4K × 144 bit                         | 0   | 1                             | 0             | 255.95               | 233.06               | 194.06               | 164.93               | MHz   |  |

|                  | True dual-port<br>RAM 4K × 144 bit                           | 0   | 1                             | 0             | 255.95               | 233.06               | 194.06               | 164.93               | MHz   |  |

|                  | Single port<br>RAM 8K × 72 bit                               | 0   | 1                             | 0             | 278.94               | 243.19               | 211.59               | 179.82               | MHz   |  |

|                  | Simple dual-port<br>RAM 8K × 72 bit                          | 0   | 1                             | 0             | 255.95               | 223.06               | 194.06               | 164.93               | MHz   |  |

|                  | True dual-port<br>RAM 8K × 72 bit                            | 0   | 1                             | 0             | 255.95               | 223.06               | 194.06               | 164.93               | MHz   |  |

|                  | Single port<br>RAM 16K × 36 bit                              | 0   | 1                             | 0             | 280.66               | 254.32               | 221.28               | 188.00               | MHz   |  |

|                  | Simple dual-port<br>RAM 16K × 36 bit                         | 0   | 1                             | 0             | 269.83               | 237.69               | 206.82               | 175.74               | MHz   |  |

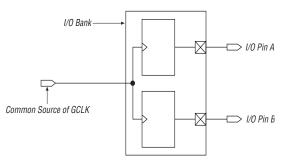

#### Definition of I/O Skew

I/O skew is defined as the absolute value of the worst-case difference in clock-to-out times ( $t_{\rm CO}$ ) between any two output registers fed by a common clock source.

I/O bank skew is made up of the following components:

- Clock network skews: This is the difference between the arrival times of the clock at the clock input port of the two IOE registers.

- Package skews: This is the package trace length differences between (I/O pad A to I/O pin A) and (I/O pad B to I/O pin B).

Figure 4–5 shows an example of two IOE registers located in the same bank, being fed by a common clock source. The clock can come from an input pin or from a PLL output.

Figure 4-5. I/O Skew within an I/O Bank

Tables 4–109 and 4–110 show the adder delays for the column and row IOE programmable delays. These delays are controlled with the Quartus II software logic options listed in the Parameter column.

| Table 4–109. Stratix              | 1       |     | d Grade |     | d Grade | . , | d Grade | -8 Snee | ed Grade |      |

|-----------------------------------|---------|-----|---------|-----|---------|-----|---------|---------|----------|------|

| Parameter                         | Setting | Min | Max     | Min | Max     | Min | Max     | Min     | Max      | Unit |

| Decrease input delay              | Off     |     | 3,970   |     | 4,367   |     | 5.022   |         | 5,908    | ps   |

| to internal cells                 | Small   |     | 3,390   |     | 3,729   |     | 4,288   |         | 5,045    | ps   |

|                                   | Medium  |     | 2,810   |     | 3,091   |     | 3,554   |         | 4,181    | ps   |

|                                   | Large   |     | 224     |     | 235     |     | 270     |         | 318      | ps   |

|                                   | On      |     | 224     |     | 235     |     | 270     |         | 318      | ps   |

| Decrease input delay              | Off     |     | 3,900   |     | 4,290   |     | 4,933   |         | 5,804    | ps   |

| o input register                  | On      |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

| Decrease input delay              | Off     |     | 1,240   |     | 1,364   |     | 1,568   |         | 1,845    | ps   |

| to output register                | On      |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

| Increase delay to                 | Off     |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

| output pin                        | On      |     | 397     |     | 417     |     | 417     |         | 417      | ps   |

| Increase delay to                 | Off     |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

| output enable pin                 | On      |     | 338     |     | 372     |     | 427     |         | 503      | ps   |

| Increase output clock             | Off     |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

| enable delay                      | Small   |     | 540     |     | 594     |     | 683     |         | 804      | ps   |

|                                   | Large   |     | 1,016   |     | 1,118   |     | 1,285   |         | 1,512    | ps   |

|                                   | On      |     | 1,016   |     | 1,118   |     | 1,285   |         | 1,512    | ps   |

| Increase input clock              | Off     |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

| enable delay                      | Small   |     | 540     |     | 594     |     | 683     |         | 804      | ps   |

|                                   | Large   |     | 1,016   |     | 1,118   |     | 1,285   |         | 1,512    | ps   |

|                                   | On      |     | 1,016   |     | 1,118   |     | 1,285   |         | 1,512    | ps   |

| Increase output                   | Off     |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

| enable clock enable delay         | Small   |     | 540     |     | 594     |     | 683     |         | 804      | ps   |

| uciay                             | Large   |     | 1,016   |     | 1,118   |     | 1,285   |         | 1,512    | ps   |

|                                   | On      |     | 1,016   |     | 1,118   |     | 1,285   |         | 1,512    | ps   |

| Increase t <sub>ZX</sub> delay to | Off     |     | 0       |     | 0       |     | 0       |         | 0        | ps   |

| output pin                        | On      |     | 2,199   |     | 2,309   |     | 2,309   |         | 2,309    | ps   |

The scaling factors for column output pin timing in Tables 4–111 to 4–113 are shown in units of time per pF unit of capacitance (ps/pF). Add this delay to the  $t_{\rm CO}$  or combinatorial timing path for output or bidirectional pins in addition to the I/O adder delays shown in Tables 4–103 through 4–108 and the IOE programmable delays in Tables 4–109 and 4–110.

| Table 4–111. Output Delay Adder for Loading on LVTTL/LVCMOS Output Buffers Note (1) |       |                                |             |             |             |        |  |  |  |

|-------------------------------------------------------------------------------------|-------|--------------------------------|-------------|-------------|-------------|--------|--|--|--|

| Conditi                                                                             | ons   | Output Pin Adder Delay (ps/pF) |             |             |             |        |  |  |  |

| Parameter                                                                           | Value | 3.3-V LVTTL                    | 2.5-V LVTTL | 1.8-V LVTTL | 1.5-V LVTTL | LVCMOS |  |  |  |

|                                                                                     | 24mA  | 15                             | -           | -           | =           | 8      |  |  |  |

|                                                                                     | 16mA  | 25                             | 18          | -           | _           | -      |  |  |  |

| Drive Strength                                                                      | 12mA  | 30                             | 25          | 25          | -           | 15     |  |  |  |

| Drive Strength                                                                      | 8mA   | 50                             | 35          | 40          | 35          | 20     |  |  |  |

|                                                                                     | 4mA   | 60                             | -           | -           | 80          | 30     |  |  |  |

|                                                                                     | 2mA   | _                              | 75          | 120         | 160         | 60     |  |  |  |

Note to Table 4-111:

(1) The timing information in this table is preliminary.

| Table 4–112. Output Delay Adder for Loading on SSTL/HSTL Output Buffers Note (1) |                                |        |          |            |  |  |  |  |

|----------------------------------------------------------------------------------|--------------------------------|--------|----------|------------|--|--|--|--|

| Conditions                                                                       | Output Pin Adder Delay (ps/pF) |        |          |            |  |  |  |  |

| Conditions                                                                       | SSTL-3                         | SSTL-2 | SSTL-1.8 | 1.5-V HSTL |  |  |  |  |

| Class I                                                                          | 25                             | 25     | 25       | 25         |  |  |  |  |

| Class II                                                                         | 25                             | 20     | 25       | 20         |  |  |  |  |

Note to Table 4–112:

(1) The timing information in this table is preliminary.

| Table 4–113. 0 | Table 4–113. Output Delay Adder for Loading on GTL+/GTL/CTT/PCI Output Buffers         Note (1) |                                |     |     |     |     |  |  |  |  |

|----------------|-------------------------------------------------------------------------------------------------|--------------------------------|-----|-----|-----|-----|--|--|--|--|

| Conditions     |                                                                                                 | Output Pin Adder Delay (ps/pF) |     |     |     |     |  |  |  |  |

| Parameter      | Value                                                                                           | GTL+                           | GTL | СТТ | PCI | AGP |  |  |  |  |

| VCCIO Voltage  | 3.3V                                                                                            | 18                             | 18  | 25  | 20  | 20  |  |  |  |  |

| Level          | 2.5V                                                                                            | 15                             | 18  | -   | -   | -   |  |  |  |  |

Note to Table 4-113:

(1) The timing information in this table is preliminary.

| Symbol                   | Parameter                                                                                                         | Min | Тур | Max                                                        | Unit         |

|--------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|------------------------------------------------------------|--------------|

| t <sub>EINJITTER</sub>   | External feedback clock period jitter                                                                             |     |     | ±200 (3)                                                   | ps           |

| t <sub>FCOMP</sub>       | External feedback clock compensation time (4)                                                                     |     |     | 6                                                          | ns           |

| f <sub>OUT</sub>         | Output frequency for internal global or regional clock                                                            | 0.3 |     | 357                                                        | MHz          |

| f <sub>OUT_EXT</sub>     | Output frequency for external clock (3)                                                                           | 0.3 |     | 369                                                        | MHz          |

| t <sub>OUTDUTY</sub>     | Duty cycle for external clock output (when set to 50%)                                                            | 45  |     | 55                                                         | %            |

| t <sub>JITTER</sub>      | Period jitter for external clock output (6)                                                                       |     |     | ±100 ps for >200-MHz outclk<br>±20 mUI for <200-MHz outclk | ps or<br>mUI |

| t <sub>CONFIG5,6</sub>   | Time required to reconfigure the scan chains for PLLs 5 and 6                                                     |     |     | 289/f <sub>SCANCLK</sub>                                   |              |

| t <sub>CONFIG11,12</sub> | Time required to reconfigure the scan chains for PLLs 11 and 12                                                   |     |     | 193/f <sub>SCANCLK</sub>                                   |              |

| t <sub>SCANCLK</sub>     | scanclk frequency (5)                                                                                             |     |     | 22                                                         | MHz          |

| t <sub>DLOCK</sub>       | Time required to lock dynamically (after switchover or reconfiguring any non-post-scale counters/delays) (7) (11) | (9) |     | 100                                                        | μs           |

| t <sub>LOCK</sub>        | Time required to lock from end of device configuration (11)                                                       | 10  |     | 400                                                        | μs           |

| f <sub>VCO</sub>         | PLL internal VCO operating range                                                                                  | 300 |     | 600 (8)                                                    | MHz          |

Tables 4–131 through 4–133 describe the Stratix device fast PLL specifications.

| Symbol                             | Parameter                                                                             | Min   | Max   | Unit    |

|------------------------------------|---------------------------------------------------------------------------------------|-------|-------|---------|

| f <sub>IN</sub>                    | CLKIN frequency (1), (2), (3)                                                         | 10    | 717   | MHz     |

| f <sub>INPFD</sub>                 | Input frequency to PFD                                                                | 10    | 500   | MHz     |

| f <sub>OUT</sub>                   | Output frequency for internal global or regional clock (3)                            | 9.375 | 420   | MHz     |

| f <sub>OUT_DIFFIO</sub>            | Output frequency for external clock driven out on a differential I/O data channel (2) | (5)   | (5)   |         |

| f <sub>VCO</sub>                   | VCO operating frequency                                                               | 300   | 1,000 | MHz     |

| t <sub>INDUTY</sub>                | CLKIN duty cycle                                                                      | 40    | 60    | %       |

| t <sub>INJITTER</sub>              | Period jitter for CLKIN pin                                                           |       | ±200  | ps      |

| t <sub>DUTY</sub>                  | Duty cycle for DFFIO 1× CLKOUT pin (6)                                                | 45    | 55    | %       |

| t <sub>JITTER</sub>                | Period jitter for DIFFIO clock out (6)                                                |       | (5)   | ps      |

| t <sub>LOCK</sub>                  | Time required for PLL to acquire lock                                                 | 10    | 100   | μs      |

| m                                  | Multiplication factors for <i>m</i> counter (6)                                       | 1     | 32    | Integer |

| <i>l</i> 0, <i>l</i> 1, <i>g</i> 0 | Multiplication factors for I0, I1, and g0 counter (7), (8)                            | 1     | 32    | Integer |

| t <sub>ARESET</sub>                | Minimum pulse width on areset signal                                                  | 10    |       | ns      |

| Table 4–132. Fast PLL Specifications for -7 Speed Grades (Part 1 of 2) |                                                                                   |       |      |      |  |  |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------|------|------|--|--|

| Symbol                                                                 | Parameter                                                                         | Min   | Max  | Unit |  |  |

| f <sub>IN</sub>                                                        | CLKIN frequency (1), (3)                                                          | 10    | 640  | MHz  |  |  |

| f <sub>INPFD</sub>                                                     | Input frequency to PFD                                                            | 10    | 500  | MHz  |  |  |

| f <sub>OUT</sub>                                                       | Output frequency for internal global or regional clock (4)                        | 9.375 | 420  | MHz  |  |  |

| fout_diffio                                                            | Output frequency for external clock driven out on a differential I/O data channel | (5)   | (5)  | MHz  |  |  |

| f <sub>VCO</sub>                                                       | VCO operating frequency                                                           | 300   | 700  | MHz  |  |  |

| t <sub>INDUTY</sub>                                                    | CLKIN duty cycle                                                                  | 40    | 60   | %    |  |  |

| t <sub>INJITTER</sub>                                                  | Period jitter for CLKIN pin                                                       |       | ±200 | ps   |  |  |

| t <sub>DUTY</sub>                                                      | Duty cycle for DFFIO 1× CLKOUT pin (6)                                            | 45    | 55   | %    |  |  |