Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 1846                                                     |

| Number of Logic Elements/Cells | 18460                                                    |

| Total RAM Bits                 | 1669248                                                  |

| Number of I/O                  | 586                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 780-BBGA, FCBGA                                          |

| Supplier Device Package        | 780-FBGA (29x29)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s20f780c7n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

viii Altera Corporation

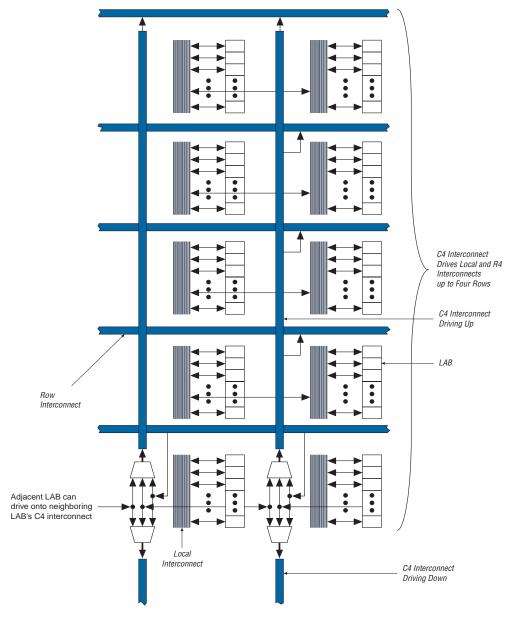

Figure 2–11. C4 Interconnect Connections Note (1)

Note to Figure 2–11:

(1) Each C4 interconnect can drive either up or down four rows.

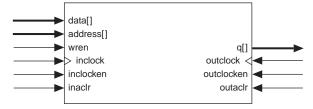

In addition to true dual-port memory, the memory blocks support simple dual-port and single-port RAM. Simple dual-port memory supports a simultaneous read and write and can either read old data before the write occurs or just read the don't care bits. Single-port memory supports non-simultaneous reads and writes, but the q[] port will output the data once it has been written to the memory (if the outputs are not registered) or after the next rising edge of the clock (if the outputs are registered). For more information, see Chapter 2, TriMatrix Embedded Memory Blocks in Stratix & Stratix GX Devices of the *Stratix Device Handbook, Volume 2*. Figure 2–13 shows these different RAM memory port configurations for TriMatrix memory.

Figure 2–13. Simple Dual-Port & Single-Port Memory Configurations

# data[] rdaddress[] wraddress[] rden wren q[] inclock outclock inclocken outclocken inaclr outaclr

#### Single-Port Memory (1)

Simple Dual-Port Memory

Note to Figure 2-13:

Two single-port memory blocks can be implemented in a single M4K block as long as each of the two independent block sizes is equal to or less than half of the M4K block size.

The memory blocks also enable mixed-width data ports for reading and writing to the RAM ports in dual-port RAM configuration. For example, the memory block can be written in  $\times 1$  mode at port A and read out in  $\times 16$  mode from port B.

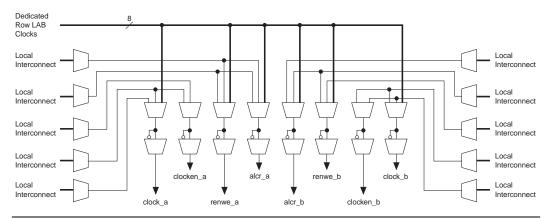

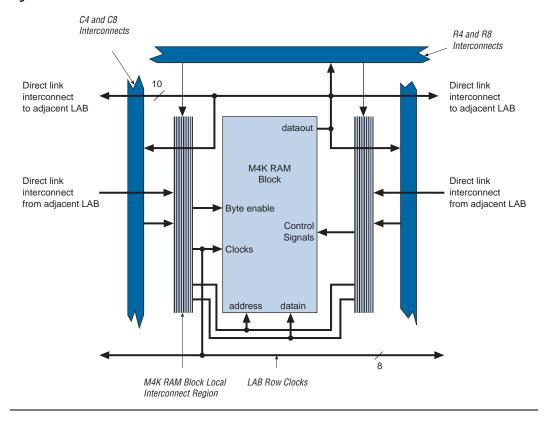

Figure 2-17. M4K RAM Block Control Signals

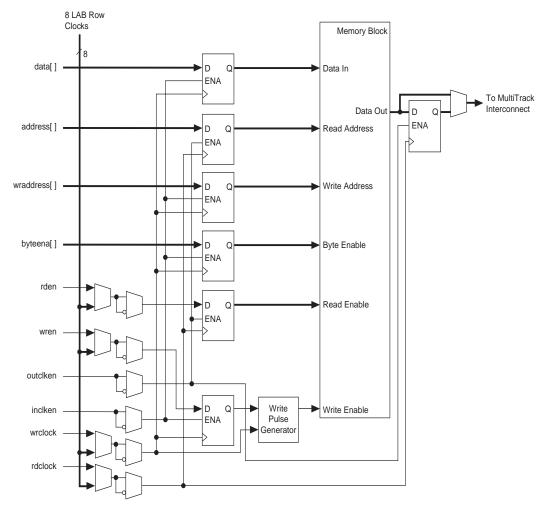

Figure 2-18. M4K RAM Block LAB Row Interface

Figure 2-27. Read/Write Clock Mode in Simple Dual-Port Mode Notes (1), (2)

### Notes to Figure 2-27:

- (1) All registers shown except the rden register have asynchronous clear ports.

- (2) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

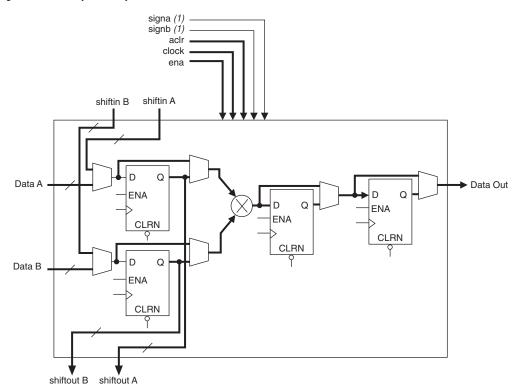

Figure 2-35. Simple Multiplier Mode

*Note to Figure 2–35:*

(1) These signals are not registered or registered once to match the data path pipeline.

DSP blocks can also implement one  $36 \times 36$ -bit multiplier in multiplier mode. DSP blocks use four  $18 \times 18$ -bit multipliers combined with dedicated adder and internal shift circuitry to achieve 36-bit multiplication. The input shift register feature is not available for the  $36 \times 36$ -bit multiplier. In  $36 \times 36$ -bit mode, the device can use the register that is normally a multiplier-result-output register as a pipeline stage for the  $36 \times 36$ -bit multiplier. Figure 2–36 shows the  $36 \times 36$ -bit multiply mode.

and/or output enable registers. A programmable delay exists to increase the  $t_{ZX}$  delay to the output pin, which is required for ZBT interfaces. Table 2–24 shows the programmable delays for Stratix devices.

| Table 2–24. Stratix Programmable Delay Chain |                                              |  |  |  |  |  |

|----------------------------------------------|----------------------------------------------|--|--|--|--|--|

| Programmable Delays                          | Quartus II Logic Option                      |  |  |  |  |  |

| Input pin to logic array delay               | Decrease input delay to internal cells       |  |  |  |  |  |

| Input pin to input register delay            | Decrease input delay to input register       |  |  |  |  |  |

| Output pin delay                             | Increase delay to output pin                 |  |  |  |  |  |

| Output enable register t <sub>CO</sub> delay | Increase delay to output enable pin          |  |  |  |  |  |

| Output t <sub>ZX</sub> delay                 | Increase t <sub>ZX</sub> delay to output pin |  |  |  |  |  |

| Output clock enable delay                    | Increase output clock enable delay           |  |  |  |  |  |

| Input clock enable delay                     | Increase input clock enable delay            |  |  |  |  |  |

| Logic array to output register delay         | Decrease input delay to output register      |  |  |  |  |  |

| Output enable clock enable delay             | Increase output enable clock enable delay    |  |  |  |  |  |

The IOE registers in Stratix devices share the same source for clear or preset. You can program preset or clear for each individual IOE. You can also program the registers to power up high or low after configuration is complete. If programmed to power up low, an asynchronous clear can control the registers. If programmed to power up high, an asynchronous preset can control the registers. This feature prevents the inadvertent activation of another device's active-low input upon power-up. If one register in an IOE uses a preset or clear signal then all registers in the IOE must use that same signal if they require preset or clear. Additionally a synchronous reset signal is available for the IOE registers.

## Double-Data Rate I/O Pins

Stratix devices have six registers in the IOE, which support DDR interfacing by clocking data on both positive and negative clock edges. The IOEs in Stratix devices support DDR inputs, DDR outputs, and bidirectional DDR modes.

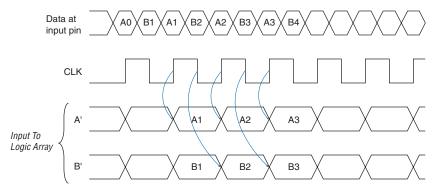

When using the IOE for DDR inputs, the two input registers clock double rate input data on alternating edges. An input latch is also used within the IOE for DDR input acquisition. The latch holds the data that is present during the clock high times. This allows both bits of data to be synchronous with the same clock edge (either rising or falling). Figure 2–65 shows an IOE configured for DDR input. Figure 2–66 shows the DDR input timing diagram.

Figure 2-66. Input Timing Diagram in DDR Mode

When using the IOE for DDR outputs, the two output registers are configured to clock two data paths from LEs on rising clock edges. These output registers are multiplexed by the clock to drive the output pin at a  $\times 2$  rate. One output register clocks the first bit out on the clock high time, while the other output register clocks the second bit out on the clock low time. Figure 2–67 shows the IOE configured for DDR output. Figure 2–68 shows the DDR output timing diagram.

Table 2–32 shows I/O standard support for each I/O bank.

| I/O Standard                      | Top & Bottom Banks<br>(3, 4, 7 & 8) | Left & Right Banks<br>(1, 2, 5 & 6) | Enhanced PLL External<br>Clock Output Banks<br>(9, 10, 11 & 12) |

|-----------------------------------|-------------------------------------|-------------------------------------|-----------------------------------------------------------------|

| LVTTL                             | <b>✓</b>                            | <b>✓</b>                            | <b>✓</b>                                                        |

| LVCMOS                            | ✓                                   | <b>✓</b>                            | <b>✓</b>                                                        |

| 2.5 V                             | ✓                                   | ✓                                   | ✓                                                               |

| 1.8 V                             | ✓                                   | ✓                                   | ✓                                                               |

| 1.5 V                             | ✓                                   | <b>✓</b>                            | <b>✓</b>                                                        |

| 3.3-V PCI                         | <b>✓</b>                            |                                     | <b>✓</b>                                                        |

| 3.3-V PCI-X 1.0                   | <b>✓</b>                            |                                     | <b>✓</b>                                                        |

| LVPECL                            |                                     | <b>✓</b>                            | <b>✓</b>                                                        |

| 3.3-V PCML                        |                                     | ✓                                   | <b>✓</b>                                                        |

| LVDS                              |                                     | <b>✓</b>                            | <b>✓</b>                                                        |

| HyperTransport technology         |                                     | <b>✓</b>                            | <b>✓</b>                                                        |

| Differential HSTL (clock inputs)  | <b>✓</b>                            | <b>✓</b>                            |                                                                 |

| Differential HSTL (clock outputs) |                                     |                                     | ✓                                                               |

| Differential SSTL (clock outputs) |                                     |                                     | ✓                                                               |

| 3.3-V GTL                         | ✓                                   |                                     | ✓                                                               |

| 3.3-V GTL+                        | ✓                                   | ✓                                   | <b>✓</b>                                                        |

| 1.5-V HSTL Class I                | ✓                                   | ✓                                   | ✓                                                               |

| 1.5-V HSTL Class II               | ✓                                   |                                     | ✓                                                               |

| 1.8-V HSTL Class I                | ✓                                   | ✓                                   | <b>✓</b>                                                        |

| 1.8-V HSTL Class II               | ✓                                   |                                     | ✓                                                               |

| SSTL-18 Class I                   | ✓                                   | ✓                                   | ✓                                                               |

| SSTL-18 Class II                  | ✓                                   |                                     | ✓                                                               |

| SSTL-2 Class I                    | ✓                                   | <b>✓</b>                            | <b>✓</b>                                                        |

| SSTL-2 Class II                   | ✓                                   | ✓                                   | <b>✓</b>                                                        |

| SSTL-3 Class I                    | <b>✓</b>                            | <b>✓</b>                            | <b>✓</b>                                                        |

The output levels are compatible with systems of the same voltage as the power supply (i.e., when VCCIO pins are connected to a 1.5-V power supply, the output levels are compatible with 1.5-V systems). When VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3 V and is compatible with 3.3-V or 5.0-V systems.

Table 2–36 summarizes Stratix MultiVolt I/O support.

| Table 2–36. Stra      | Table 2–36. Stratix MultiVolt I/O Support Note (1) |          |              |              |              |                   |              |              |          |          |

|-----------------------|----------------------------------------------------|----------|--------------|--------------|--------------|-------------------|--------------|--------------|----------|----------|

| V <sub>CCIO</sub> (V) |                                                    | Inp      | ut Signal    | (5)          |              | Output Signal (6) |              |              |          |          |

|                       | 1.5 V                                              | 1.8 V    | 2.5 V        | 3.3 V        | 5.0 V        | 1.5 V             | 1.8 V        | 2.5 V        | 3.3 V    | 5.0 V    |

| 1.5                   | <b>✓</b>                                           | <b>✓</b> | <b>√</b> (2) | <b>√</b> (2) |              | <b>✓</b>          |              |              |          |          |

| 1.8                   | <b>√</b> (2)                                       | <b>✓</b> | <b>√</b> (2) | <b>√</b> (2) |              | <b>✓</b> (3)      | <b>✓</b>     |              |          |          |

| 2.5                   |                                                    |          | <b>✓</b>     | <b>✓</b>     |              | <b>√</b> (3)      | <b>√</b> (3) | <b>✓</b>     |          |          |

| 3.3                   |                                                    |          | <b>√</b> (2) | <b>✓</b>     | <b>✓</b> (4) | <b>✓</b> (3)      | <b>√</b> (3) | <b>√</b> (3) | <b>✓</b> | <b>✓</b> |

#### Notes to Table 2-36:

- (1) To drive inputs higher than  $V_{CCIO}$  but less than 4.1 V, disable the PCI clamping diode. However, to drive 5.0-V inputs to the device, enable the PCI clamping diode to prevent  $V_{\rm I}$  from rising above 4.0 V.

- (2) The input pin current may be slightly higher than the typical value.

- (3) Although  $V_{CCIO}$  specifies the voltage necessary for the Stratix device to drive out, a receiving device powered at a different level can still interface with the Stratix device if it has inputs that tolerate the  $V_{CCIO}$  value.

- (4) Stratix devices can be 5.0-V tolerant with the use of an external resistor and the internal PCI clamp diode.

- (5) This is the external signal that is driving the Stratix device.

- (6) This represents the system voltage that Stratix supports when a VCCIO pin is connected to a specific voltage level. For example, when VCCIO is 3.3 V and if the I/O standard is LVTTL/LVCMOS, the output high of the signal coming out from Stratix is 3.3 V and is compatible with 3.3-V or 5.0-V systems.

# High-Speed Differential I/O Support

Stratix devices contain dedicated circuitry for supporting differential standards at speeds up to 840 Mbps. The following differential I/O standards are supported in the Stratix device: LVDS, LVPECL, HyperTransport, and 3.3-V PCML.

There are four dedicated high-speed PLLs in the EP1S10 to EP1S25 devices and eight dedicated high-speed PLLs in the EP1S30 to EP1S80 devices to multiply reference clocks and drive high-speed differential SERDES channels.

See the Stratix device pin-outs at **www.altera.com** for additional high speed DIFFIO pin information for Stratix devices.

| Table 2-39            | Table 2–39. EP1S40 Differential Channels (Part 2 of 2) Note (1) |                       |                 |           |                  |           |           |           |                           |           |        |  |

|-----------------------|-----------------------------------------------------------------|-----------------------|-----------------|-----------|------------------|-----------|-----------|-----------|---------------------------|-----------|--------|--|

|                       | Transmitter/                                                    | Total                 | Maximum         | C         | Center Fast PLLs |           |           |           | Corner Fast PLLs (2), (3) |           |        |  |

| Package               | Receiver                                                        | Channels              | Speed<br>(Mbps) | PLL1      | PLL2             | PLL3      | PLL4      | PLL7      | PLL8                      | PLL9      | PLL10  |  |

| 956-pin               | Transmitter                                                     | 80                    | 840             | 18        | 17               | 17        | 18        | 20        | 20                        | 20        | 20     |  |

| BGA                   | (4)                                                             |                       | 840 (5)         | 35        | 35               | 35        | 35        | 20        | 20                        | 20        | 20     |  |

|                       | Receiver                                                        | 80                    | 840             | 20        | 20               | 20        | 20        | 18        | 17                        | 17        | 18     |  |

|                       |                                                                 |                       | 840 (5)         | 40        | 40               | 40        | 40        | 18        | 17                        | 17        | 18     |  |

| 1,020-pin<br>FineLine | Transmitter (4)                                                 | 80 (10)<br><i>(7)</i> | 840             | 18<br>(2) | 17<br>(3)        | 17<br>(3) | 18<br>(2) | 20        | 20                        | 20        | 20     |  |

| BGA                   |                                                                 |                       | 840 (5), (8)    | 35<br>(5) | 35<br>(5)        | 35<br>(5) | 35<br>(5) | 20        | 20                        | 20        | 20     |  |

|                       | Receiver                                                        | 80 (10)<br><i>(7)</i> | 840             | 20        | 20               | 20        | 20        | 18<br>(2) | 17<br>(3)                 | 17<br>(3) | 18 (2) |  |

|                       |                                                                 |                       | 840 (5), (8)    | 40        | 40               | 40        | 40        | 18<br>(2) | 17<br>(3)                 | 17<br>(3) | 18 (2) |  |

| 1,508-pin<br>FineLine | Transmitter (4)                                                 | 80 (10)<br><i>(7)</i> | 840             | 18<br>(2) | 17<br>(3)        | 17<br>(3) | 18<br>(2) | 20        | 20                        | 20        | 20     |  |

| BGA                   |                                                                 |                       | 840 (5), (8)    | 35<br>(5) | 35<br>(5)        | 35<br>(5) | 35<br>(5) | 20        | 20                        | 20        | 20     |  |

|                       | Receiver                                                        | 80 (10)<br><i>(7)</i> | 840             | 20        | 20               | 20        | 20        | 18<br>(2) | 17<br>(3)                 | 17<br>(3) | 18 (2) |  |

|                       |                                                                 |                       | 840 (5), (8)    | 40        | 40               | 40        | 40        | 18<br>(2) | 17<br>(3)                 | 17<br>(3) | 18 (2) |  |

| Table 2-40. | Table 2–40. EP1S60 Differential Channels (Part 1 of 2) Note (1) |          |                     |      |         |         |      |      |         |      |          |

|-------------|-----------------------------------------------------------------|----------|---------------------|------|---------|---------|------|------|---------|------|----------|

|             | Transmitter/                                                    | Total    | Maximum             | C    | enter F | ast PLI | .s   | Corn | er Fast | PLLs | (2), (3) |

| Package     |                                                                 | Channels | Speed<br>(Mbps)     | PLL1 | PLL2    | PLL3    | PLL4 | PLL7 | PLL8    | PLL9 | PLL10    |

| 956-pin     | Transmitter                                                     | 80       | 840                 | 12   | 10      | 10      | 12   | 20   | 20      | 20   | 20       |

| BGA         | (4)                                                             |          | 840 (5), (8)        | 22   | 22      | 22      | 22   | 20   | 20      | 20   | 20       |

|             | Receiver                                                        | 80       | 840                 | 20   | 20      | 20      | 20   | 12   | 10      | 10   | 12       |

|             |                                                                 |          | 840 <i>(5), (8)</i> | 40   | 40      | 40      | 40   | 12   | 10      | 10   | 12       |

The transmitter external clock output is transmitted on a data channel. The txclk pin for each bank is located in between data transmitter pins. For  $\times 1$  clocks (e.g., 622 Mbps, 622 MHz), the high-speed PLL clock bypasses the SERDES to drive the output pins. For half-rate clocks (e.g., 622 Mbps, 311 MHz) or any other even-numbered factor such as 1/4, 1/7, 1/8, or 1/10, the SERDES automatically generates the clock in the Ouartus II software.

For systems that require more than four or eight high-speed differential I/O clock domains, a SERDES bypass implementation is possible using IOEs.

## **Byte Alignment**

For high-speed source synchronous interfaces such as POS-PHY 4, XSBI, RapidIO, and HyperTransport technology, the source synchronous clock rate is not a byte- or SERDES-rate multiple of the data rate. Byte alignment is necessary for these protocols since the source synchronous clock does not provide a byte or word boundary since the clock is one half the data rate, not one eighth. The Stratix device's high-speed differential I/O circuitry provides dedicated data realignment circuitry for user-controlled byte boundary shifting. This simplifies designs while saving LE resources. An input signal to each fast PLL can stall deserializer parallel data outputs by one bit period. You can use an LE-based state machine to signal the shift of receiver byte boundaries until a specified pattern is detected to indicate byte alignment.

# Power Sequencing & Hot Socketing

Because Stratix devices can be used in a mixed-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. Therefore, the VCCIO and VCCINT power supplies may be powered in any order.

Although you can power up or down the VCCIO and VCCINT power supplies in any sequence, you should not power down any I/O banks that contain configuration pins while leaving other I/O banks powered on. For power up and power down, all supplies (VCCINT and all VCCIO power planes) must be powered up and down within 100 ms of each other. This prevents I/O pins from driving out.

Signals can be driven into Stratix devices before and during power up without damaging the device. In addition, Stratix devices do not drive out during power up. Once operating conditions are reached and the device is configured, Stratix devices operate as specified by the user. For more information, see *Hot Socketing* in the *Selectable I/O Standards in Stratix & Stratix GX Devices* chapter in the *Stratix Device Handbook*, *Volume 2*.

configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power-up, and before and during configuration. Together, the configuration and initialization processes are called command mode. Normal device operation is called user mode.

SRAM configuration elements allow Stratix devices to be reconfigured incircuit by loading new configuration data into the device. With real-time reconfiguration, the device is forced into command mode with a device pin. The configuration process loads different configuration data, reinitializes the device, and resumes user-mode operation. You can perform in-field upgrades by distributing new configuration files either within the system or remotely.

PORSEL is a dedicated input pin used to select POR delay times of 2 ms or 100 ms during power-up. When the PORSEL pin is connected to ground, the POR time is 100 ms; when the PORSEL pin is connected to  $V_{\rm CC}$ , the POR time is 2 ms.

The nio\_pullup pin enables a built-in weak pull-up resistor to pull all user I/O pins to  $V_{CCIO}$  before and during device configuration. If nio\_pullup is connected to  $V_{CC}$  during configuration, the weak pull-ups on all user I/O pins are disabled. If connected to ground, the pull-ups are enabled during configuration. The nio\_pullup pin can be pulled to 1.5, 1.8, 2.5, or 3.3 V for a logic level high.

VCCSEL is a dedicated input that is used to choose whether all dedicated configuration and JTAG input pins can accept 1.5 V/1.8 V or 2.5 V/3.3 V during configuration. A logic low sets 3.3 V/2.5 V, and a logic high sets 1.8 V/1.5 V. VCCSEL affects the following pins: TDI, TMS, TCK, TRST, MSEL0, MSEL1, MSEL2, nCONFIG, nCE, DCLK, PLL\_ENA, CONF\_DONE, nSTATUS. The VCCSEL pin can be pulled to 1.5, 1.8, 2.5, or 3.3 V for a logic level high.

The VCCSEL signal does not control the dual-purpose configuration pins such as the DATA [7..0] and PPA pins (nws, nrs, cs, nrcs, and RDYnbsy). During configuration, these dual-purpose pins will drive out voltage levels corresponding to the  $V_{\rm CCIO}$  supply voltage that powers the I/O bank containing the pin. After configuration, the dual-purpose pins use I/O standards specified in the user design.

TDO and nCEO drive out at the same voltages as the  $V_{CCIO}$  supply that powers the I/O bank containing the pin. Users must select the  $V_{CCIO}$  supply for bank containing TDO accordingly. For example, when using the ByteBlaster MV cable, the  $V_{CCIO}$  for the bank containing TDO must be powered up at 3.3 V.

| Symbol                  | Parameter                                                                   | Conditions                                                                                 | Minimum | Typical | Maximum | Unit |

|-------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------|---------|---------|------|

| V <sub>ICM</sub>        | Input common mode voltage (6)                                               | LVDS<br>$0.3 \text{ V} \leq \text{V}_{\text{ID}} \leq 1.0 \text{ V}$<br>W = 1  through  10 | 100     |         | 1,100   | mV   |

|                         |                                                                             | LVDS<br>$0.3 \text{ V} \leq V_{\text{ID}} \leq 1.0 \text{ V}$<br>W = 1  through  10        | 1,600   |         | 1,800   | mV   |

|                         |                                                                             | LVDS<br>0.2 V ≤V <sub>ID</sub> ≤1.0 V<br>W = 1                                             | 1,100   |         | 1,600   | mV   |

|                         |                                                                             | LVDS<br>$0.1 \text{ V} \leq V_{\text{ID}} \leq 1.0 \text{ V}$<br>W = 2  through  10        | 1,100   |         | 1,600   | mV   |

| V <sub>OD</sub> (1)     | Output differential voltage (single-ended)                                  | R <sub>L</sub> = 100 Ω                                                                     | 250     | 375     | 550     | mV   |

| Δ V <sub>OD</sub>       | Change in V <sub>OD</sub> between high and low                              | R <sub>L</sub> = 100 Ω                                                                     |         |         | 50      | mV   |

| V <sub>OCM</sub>        | Output common mode voltage                                                  | $R_L = 100 \Omega$                                                                         | 1,125   | 1,200   | 1,375   | mV   |

| $\Delta V_{\text{OCM}}$ | Change in V <sub>OCM</sub> between high and low                             | $R_L = 100 \Omega$                                                                         |         |         | 50      | mV   |

| R <sub>L</sub>          | Receiver differential input discrete resistor (external to Stratix devices) |                                                                                            | 90      | 100     | 110     | Ω    |

| Table 4-47. DSP BI           | Table 4–47. DSP Block Internal Timing Microparameters (Part 2 of 2) |       |       |       |       |       |       |        |      |

|------------------------------|---------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--------|------|

| Chal                         | -                                                                   | 5     | -     | -6    |       | -7    |       | -8     |      |

| Symbol                       | Min                                                                 | Max   | Min   | Max   | Min   | Max   | Min   | Max    | Unit |

| t <sub>PIPE2OUTREG2ADD</sub> |                                                                     | 2,002 |       | 2,203 |       | 2,533 |       | 2,980  | ps   |

| t <sub>PIPE2OUTREG4ADD</sub> |                                                                     | 2,899 |       | 3,189 |       | 3,667 |       | 4,314  | ps   |

| t <sub>PD9</sub>             |                                                                     | 3,709 |       | 4,081 |       | 4,692 |       | 5,520  | ps   |

| t <sub>PD18</sub>            |                                                                     | 4,795 |       | 5,275 |       | 6,065 |       | 7,135  | ps   |

| t <sub>PD36</sub>            |                                                                     | 7,495 |       | 8,245 |       | 9,481 |       | 11,154 | ps   |

| t <sub>CLR</sub>             | 450                                                                 |       | 500   |       | 575   |       | 676   |        | ps   |

| t <sub>CLKHL</sub>           | 1,350                                                               |       | 1,500 |       | 1,724 |       | 2,029 |        | ps   |

| Table 4–48. M512         | Table 4–48. M512 Block Internal Timing Microparameters |       |       |       |       |       |       |       |      |

|--------------------------|--------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|------|

| Ourseh e l               | -                                                      | -5    |       | 6     | -     | 7     | -8    |       | Heit |

| Symbol                   | Min                                                    | Max   | Min   | Max   | Min   | Max   | Min   | Max   | Unit |

| t <sub>M512RC</sub>      |                                                        | 3,340 |       | 3,816 |       | 4,387 |       | 5,162 | ps   |

| t <sub>M512WC</sub>      |                                                        | 3,138 |       | 3,590 |       | 4,128 |       | 4,860 | ps   |

| t <sub>M512WERESU</sub>  | 110                                                    |       | 123   |       | 141   |       | 166   |       | ps   |

| t <sub>M512WEREH</sub>   | 34                                                     |       | 38    |       | 43    |       | 51    |       | ps   |

| t <sub>M512CLKENSU</sub> | 215                                                    |       | 215   |       | 247   |       | 290   |       | ps   |

| t <sub>M512CLKENH</sub>  | -70                                                    |       | -70   |       | -81   |       | -95   |       | ps   |

| t <sub>M512DATASU</sub>  | 110                                                    |       | 123   |       | 141   |       | 166   |       | ps   |

| t <sub>M512DATAH</sub>   | 34                                                     |       | 38    |       | 43    |       | 51    |       | ps   |

| t <sub>M512WADDRSU</sub> | 110                                                    |       | 123   |       | 141   |       | 166   |       | ps   |

| t <sub>M512WADDRH</sub>  | 34                                                     |       | 38    |       | 43    |       | 51    |       | ps   |

| t <sub>M512RADDRSU</sub> | 110                                                    |       | 123   |       | 141   |       | 166   |       | ps   |

| t <sub>M512RADDRH</sub>  | 34                                                     |       | 38    |       | 43    |       | 51    |       | ps   |

| t <sub>M512DATACO1</sub> |                                                        | 424   |       | 472   |       | 541   |       | 637   | ps   |

| t <sub>M512DATACO2</sub> |                                                        | 3,366 |       | 3,846 |       | 4,421 |       | 5,203 | ps   |

| t <sub>M512CLKHL</sub>   | 1,000                                                  |       | 1,111 |       | 1,190 |       | 1,400 |       | ps   |

| t <sub>M512CLR</sub>     | 170                                                    |       | 189   |       | 217   |       | 255   |       | ps   |

| Table 4–53. Stratix Regional Clock External I/O Ti | iming Parameters (Part 2 |

|----------------------------------------------------|--------------------------|

| <b>of 2)</b> Notes (1), (2)                        |                          |

|                                                    |                          |

| Symbol             | Parameter                                                                                                                              |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>XZPLL</sub> | Synchronous IOE output enable register to output pin disable delay using regional clock fed by Enhanced PLL with default phase setting |

| t <sub>ZXPLL</sub> | Synchronous IOE output enable register to output pin enable delay using regional clock fed by Enhanced PLL with default phase setting  |

#### *Notes to Table 4–53:*

- (1) These timing parameters are sample-tested only.

- (2) These timing parameters are for column and row IOE pins. You should use the Quartus II software to verify the external timing for any pin.

Table 4–54 shows the external I/O timing parameters when using global clock networks.

| <b>Table 4–3</b> (2)  | <b>Table 4–54. Stratix Global Clock External I/O Timing Parameters</b> Notes (1), (2)                                                 |  |  |  |  |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Symbol                | Parameter                                                                                                                             |  |  |  |  |  |  |

| t <sub>INSU</sub>     | Setup time for input or bidirectional pin using IOE input register with global clock fed by ${\tt CLK}$ pin                           |  |  |  |  |  |  |

| t <sub>INH</sub>      | Hold time for input or bidirectional pin using IOE input register with global clock fed by CLK pin                                    |  |  |  |  |  |  |

| t <sub>OUTCO</sub>    | Clock-to-output delay output or bidirectional pin using IOE output register with global clock fed by CLK pin                          |  |  |  |  |  |  |

| t <sub>INSUPLL</sub>  | Setup time for input or bidirectional pin using IOE input register with global clock fed by Enhanced PLL with default phase setting   |  |  |  |  |  |  |

| t <sub>INHPLL</sub>   | Hold time for input or bidirectional pin using IOE input register with global clock fed by Enhanced PLL with default phase setting    |  |  |  |  |  |  |

| t <sub>OUTCOPLL</sub> | Clock-to-output delay output or bidirectional pin using IOE output register with global clock Enhanced PLL with default phase setting |  |  |  |  |  |  |

| t <sub>XZPLL</sub>    | Synchronous IOE output enable register to output pin disable delay using global clock fed by Enhanced PLL with default phase setting  |  |  |  |  |  |  |

| t <sub>ZXPLL</sub>    | Synchronous IOE output enable register to output pin enable delay using global clock fed by Enhanced PLL with default phase setting   |  |  |  |  |  |  |

#### Notes to Table 4-54:

- (1) These timing parameters are sample-tested only.

- (2) These timing parameters are for column and row IOE pins. You should use the Quartus II software to verify the external timing for any pin.

| Table 4–105. Stratix I/O Standard Output Delay Adders for Fast Slew Rate on Column Pins (Part 2 of 2) |         |                |     |                |     |                |     |                |      |

|-------------------------------------------------------------------------------------------------------|---------|----------------|-----|----------------|-----|----------------|-----|----------------|------|

| _                                                                                                     | -5 Spee | -5 Speed Grade |     | -6 Speed Grade |     | -7 Speed Grade |     | -8 Speed Grade |      |

| Parameter                                                                                             | Min     | Max            | Min | Max            | Min | Max            | Min | Max            | Unit |

| CTT                                                                                                   |         | 973            |     | 1,021          |     | 1,021          |     | 1,021          | ps   |

| SSTL-3 Class I                                                                                        |         | 719            |     | 755            |     | 755            |     | 755            | ps   |

| SSTL-3 Class II                                                                                       |         | 146            |     | 153            |     | 153            |     | 153            | ps   |

| SSTL-2 Class I                                                                                        |         | 678            |     | 712            |     | 712            |     | 712            | ps   |

| SSTL-2 Class II                                                                                       |         | 223            |     | 234            |     | 234            |     | 234            | ps   |

| SSTL-18 Class I                                                                                       |         | 1,032          |     | 1,083          |     | 1,083          |     | 1,083          | ps   |

| SSTL-18 Class II                                                                                      |         | 447            |     | 469            |     | 469            |     | 469            | ps   |

| 1.5-V HSTL Class I                                                                                    |         | 660            |     | 693            |     | 693            |     | 693            | ps   |

| 1.5-V HSTL Class II                                                                                   |         | 537            |     | 564            |     | 564            |     | 564            | ps   |

| 1.8-V HSTL Class I                                                                                    |         | 304            |     | 319            |     | 319            |     | 319            | ps   |

| 1.8-V HSTL Class II                                                                                   |         | 231            |     | 242            |     | 242            |     | 242            | ps   |

| Table 4–106. Stratix I/O Standard Output Delay Adders for Fast Slew Rate on Row Pins (Part 1 of 2) |           |                |       |                |       |                |       |                |       |       |

|----------------------------------------------------------------------------------------------------|-----------|----------------|-------|----------------|-------|----------------|-------|----------------|-------|-------|

| Davamatav                                                                                          |           | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | Unit  |

| ratallie                                                                                           | Parameter |                | Max   | Min            | Max   | Min            | Max   | Min            | Max   | UIIIL |

| LVCMOS                                                                                             | 2 mA      |                | 1,518 |                | 1,594 |                | 1,594 |                | 1,594 | ps    |

|                                                                                                    | 4 mA      |                | 746   |                | 783   |                | 783   |                | 783   | ps    |

|                                                                                                    | 8 mA      |                | 96    |                | 100   |                | 100   |                | 100   | ps    |

|                                                                                                    | 12 mA     |                | 0     |                | 0     |                | 0     |                | 0     | ps    |

| 3.3-V LVTTL                                                                                        | 4 mA      |                | 1,518 |                | 1,594 |                | 1,594 |                | 1,594 | ps    |

|                                                                                                    | 8 mA      |                | 1,038 |                | 1,090 |                | 1,090 |                | 1,090 | ps    |

|                                                                                                    | 12 mA     |                | 521   |                | 547   |                | 547   |                | 547   | ps    |

|                                                                                                    | 16 mA     |                | 414   |                | 434   |                | 434   |                | 434   | ps    |

|                                                                                                    | 24 mA     |                | 0     |                | 0     |                | 0     |                | 0     | ps    |

| 2.5-V LVTTL                                                                                        | 2 mA      |                | 2,032 |                | 2,133 |                | 2,133 |                | 2,133 | ps    |

|                                                                                                    | 8 mA      |                | 699   |                | 734   |                | 734   |                | 734   | ps    |

|                                                                                                    | 12 mA     |                | 374   |                | 392   |                | 392   |                | 392   | ps    |

|                                                                                                    | 16 mA     |                | 165   |                | 173   |                | 173   |                | 173   | ps    |

| 1.8-V LVTTL                                                                                        | 2 mA      |                | 3,714 |                | 3,899 |                | 3,899 |                | 3,899 | ps    |

|                                                                                                    | 8 mA      |                | 1,055 |                | 1,107 |                | 1,107 |                | 1,107 | ps    |

|                                                                                                    | 12 mA     |                | 830   |                | 871   |                | 871   |                | 871   | ps    |

The scaling factors for column output pin timing in Tables 4–111 to 4–113 are shown in units of time per pF unit of capacitance (ps/pF). Add this delay to the  $t_{\rm CO}$  or combinatorial timing path for output or bidirectional pins in addition to the I/O adder delays shown in Tables 4–103 through 4–108 and the IOE programmable delays in Tables 4–109 and 4–110.

| Table 4–111. Output Delay Adder for Loading on LVTTL/LVCMOS Output Buffers Note (1) |                                           |             |             |             |             |        |

|-------------------------------------------------------------------------------------|-------------------------------------------|-------------|-------------|-------------|-------------|--------|

| Conditi                                                                             | Conditions Output Pin Adder Delay (ps/pF) |             |             |             |             |        |

| Parameter                                                                           | Value                                     | 3.3-V LVTTL | 2.5-V LVTTL | 1.8-V LVTTL | 1.5-V LVTTL | LVCMOS |

|                                                                                     | 24mA                                      | 15          | -           | -           | =           | 8      |

|                                                                                     | 16mA                                      | 25          | 18          | -           | _           | -      |

| Drive Strength                                                                      | 12mA                                      | 30          | 25          | 25          | -           | 15     |

| Drive Strength                                                                      | 8mA                                       | 50          | 35          | 40          | 35          | 20     |

|                                                                                     | 4mA                                       | 60          | -           | -           | 80          | 30     |

|                                                                                     | 2mA                                       | _           | 75          | 120         | 160         | 60     |

Note to Table 4-111:

(1) The timing information in this table is preliminary.

| Table 4–112. Output Delay Adder for Loading on SSTL/HSTL Output Buffers Note (1) |                                |        |          |            |  |  |  |

|----------------------------------------------------------------------------------|--------------------------------|--------|----------|------------|--|--|--|

| Conditions                                                                       | Output Pin Adder Delay (ps/pF) |        |          |            |  |  |  |

| Conditions                                                                       | SSTL-3                         | SSTL-2 | SSTL-1.8 | 1.5-V HSTL |  |  |  |

| Class I                                                                          | 25                             | 25     | 25       | 25         |  |  |  |

| Class II                                                                         | 25                             | 20     | 25       | 20         |  |  |  |

Note to Table 4–112:

(1) The timing information in this table is preliminary.

| Table 4–113. Output Delay Adder for Loading on GTL+/GTL/CTT/PCI Output Buffers Note (1) |       |                                |     |     |     |     |

|-----------------------------------------------------------------------------------------|-------|--------------------------------|-----|-----|-----|-----|

| Condi                                                                                   | tions | Output Pin Adder Delay (ps/pF) |     |     |     |     |

| Parameter                                                                               | Value | GTL+                           | GTL | СТТ | PCI | AGP |

| VCCIO Voltage                                                                           | 3.3V  | 18                             | 18  | 25  | 20  | 20  |

| Level                                                                                   | 2.5V  | 15                             | 18  | -   | -   | -   |

Note to Table 4-113:

(1) The timing information in this table is preliminary.

# PLL Specifications

Tables 4–127 through 4–129 describe the Stratix device enhanced PLL specifications.

| Table 4–127. Enhanced PLL Specifications for -5 Speed Grades (Part 1 of 2) |                                                                                                              |               |     |                                                            |              |  |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------|-----|------------------------------------------------------------|--------------|--|

| Symbol                                                                     | Parameter                                                                                                    | Min           | Тур | Max                                                        | Unit         |  |

| f <sub>IN</sub>                                                            | Input clock frequency                                                                                        | 3<br>(1), (2) |     | 684                                                        | MHz          |  |

| f <sub>INPFD</sub>                                                         | Input frequency to PFD                                                                                       | 3             |     | 420                                                        | MHz          |  |

| f <sub>INDUTY</sub>                                                        | Input clock duty cycle                                                                                       | 40            |     | 60                                                         | %            |  |

| f <sub>EINDUTY</sub>                                                       | External feedback clock input duty cycle                                                                     | 40            |     | 60                                                         | %            |  |

| t <sub>INJITTER</sub>                                                      | Input clock period jitter                                                                                    |               |     | ±200 (3)                                                   | ps           |  |

| t <sub>EINJITTER</sub>                                                     | External feedback clock period jitter                                                                        |               |     | ±200 (3)                                                   | ps           |  |

| t <sub>FCOMP</sub>                                                         | External feedback clock compensation time (4)                                                                |               |     | 6                                                          | ns           |  |

| f <sub>OUT</sub>                                                           | Output frequency for internal global or regional clock                                                       | 0.3           |     | 500                                                        | MHz          |  |

| f <sub>OUT_EXT</sub>                                                       | Output frequency for external clock (3)                                                                      | 0.3           |     | 526                                                        | MHz          |  |

| t <sub>OUTDUTY</sub>                                                       | Duty cycle for external clock output (when set to 50%)                                                       | 45            |     | 55                                                         | %            |  |

| t <sub>JITTER</sub>                                                        | Period jitter for external clock output (6)                                                                  |               |     | ±100 ps for >200-MHz outclk<br>±20 mUI for <200-MHz outclk | ps or<br>mUI |  |

| t <sub>CONFIG5,6</sub>                                                     | Time required to reconfigure the scan chains for PLLs 5 and 6                                                |               |     | 289/f <sub>SCANCLK</sub>                                   |              |  |

| t <sub>CONFIG11,12</sub>                                                   | Time required to reconfigure the scan chains for PLLs 11 and 12                                              |               |     | 193/f <sub>SCANCLK</sub>                                   |              |  |

| t <sub>SCANCLK</sub>                                                       | scanclk frequency (5)                                                                                        |               |     | 22                                                         | MHz          |  |

| t <sub>DLOCK</sub>                                                         | Time required to lock dynamically (after switchover or reconfiguring any non-post-scale counters/delays) (7) |               |     | 100                                                        | μs           |  |

| t <sub>LOCK</sub>                                                          | Time required to lock from end of device configuration                                                       | 10            |     | 400                                                        | μs           |  |

| f <sub>VCO</sub>                                                           | PLL internal VCO operating range                                                                             | 300           |     | 800 (8)                                                    | MHz          |  |

| t <sub>LSKEW</sub>                                                         | Clock skew between two external clock outputs driven by the same counter                                     |               | ±50 |                                                            | ps           |  |

| Differential HSTL Specifications 4–15<br>DSP        | Parameters 4–39<br>Row Pin                         |

|-----------------------------------------------------|----------------------------------------------------|

| Block Diagram                                       | Fast Regional Clock External I/O Timing            |

| Configuration                                       | Parameters 4–40                                    |

| for 18 x 18-Bit 2–55                                | Global Clock External I/O Timing                   |

| for 9 x 9-Bit 2–56                                  | Parameters 4–41                                    |

| Block Interconnect Interface 2–71                   | Regional Clock External I/O Timing                 |

| Block Interface 2–70                                | Parameters 4–41                                    |

| Block Signal Sources & Destinations 2–73            | EP1S25 Devices                                     |

| Blocks                                              | Column Pin                                         |

| Arranged in Columns 2–53                            | Fast Regional Clock External I/O Timing            |

| in Stratix Devices 2–54                             | Parameters 4–42                                    |

| Input Register Modes 2-60                           | Global Clock External I/O Timing                   |

| Input Registers 2–58                                | Parameters 4–43                                    |

| Multiplier                                          | Regional Clock External I/O Timing                 |

| 2–60                                                | Parameters 4–42                                    |

| Block 2–57                                          | Row Pin                                            |

| Signed Representation 2-60                          | Fast Regional Clock External I/O Timing            |

| Sub-Block 2–57                                      | Parameters 4–43                                    |

| Sub-Blocks Using Input Shift Register               | Global Clock External I/O Timing                   |

| Connections 2–59                                    | Parameters 4–44                                    |

| Pipeline/Post Multiply Register 2–61                | Regional Clock External I/O Timing                 |

|                                                     | Parameters 4–44                                    |

| E                                                   | EP1S30 Devices                                     |

| <b>L</b>                                            | Column Pin                                         |

| EP1S10 Devices                                      | Fast Regional Clock External I/O Timing            |

| Column Pin                                          | Parameters 4–45                                    |

| Fast Regional Clock External I/O Timing             | Global Clock External I/O Timing                   |

| Parameters 4–36                                     | Parameters 4–45                                    |

| Global Clock External I/O Timing<br>Parameters 4–37 | Regional Clock External I/O Timing Parameters 4–45 |

| Regional Clock External I/O Timing                  | Row Pin                                            |

| Parameters 4–36                                     | Fast Regional Clock External I/O Timing            |

| Row Pin                                             | Parameters 4–46                                    |

| Fast Regional Clock External I/O Timing             | Global Clock External I/O Timing                   |

| Parameters 4–37                                     | Parameters 4–47                                    |

| Global Clock External I/O Timing                    | Regional Clock External I/O Timing                 |

| Parameters 4–38                                     | Parameters 4–47                                    |

| Regional Clock External I/O Timing                  | EP1S40 Devices                                     |

| Parameters 4–38                                     | Column Pin                                         |

| EP1S20 Devices                                      | Fast Regional Clock External I/O Timing            |

| Column Pin                                          | Parameters 4–48                                    |

| Fast Regional Clock External I/O Timing             | Global Clock External I/O Timing                   |

| Parameters 4–39                                     | Parameters 4–49                                    |

| Global Clock External I/O Timing                    | Regional Clock External I/O Timing                 |

| Parameters 4–40                                     | Parameters 4–48                                    |

| Regional Clock External I/O Timing                  | Row Pin                                            |

Altera Corporation Index-3