Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Obsolete                                                  |

| Number of LABs/CLBs            | 2566                                                      |

| Number of Logic Elements/Cells | 25660                                                     |

| Total RAM Bits                 | 1944576                                                   |

| Number of I/O                  | 706                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.425V ~ 1.575V                                           |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 1020-BBGA                                                 |

| Supplier Device Package        | 1020-FBGA (33x33)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s25f1020c5n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

vi Altera Corporation

| Table 1–1. Stratix Device Features — EP1S10, EP1S20, EP1S25, EP1S30 |         |           |           |           |  |  |  |  |  |  |

|---------------------------------------------------------------------|---------|-----------|-----------|-----------|--|--|--|--|--|--|

| Feature                                                             | EP1S10  | EP1S20    | EP1S25    | EP1S30    |  |  |  |  |  |  |

| LEs                                                                 | 10,570  | 18,460    | 25,660    | 32,470    |  |  |  |  |  |  |

| M512 RAM blocks (32 × 18 bits)                                      | 94      | 194       | 224       | 295       |  |  |  |  |  |  |

| M4K RAM blocks (128 × 36 bits)                                      | 60      | 82        | 138       | 171       |  |  |  |  |  |  |

| M-RAM blocks (4K × 144 bits)                                        | 1       | 2         | 2         | 4         |  |  |  |  |  |  |

| Total RAM bits                                                      | 920,448 | 1,669,248 | 1,944,576 | 3,317,184 |  |  |  |  |  |  |

| DSP blocks                                                          | 6       | 10        | 10        | 12        |  |  |  |  |  |  |

| Embedded multipliers (1)                                            | 48      | 80        | 80        | 96        |  |  |  |  |  |  |

| PLLs                                                                | 6       | 6         | 6         | 10        |  |  |  |  |  |  |

| Maximum user I/O pins                                               | 426     | 586       | 706       | 726       |  |  |  |  |  |  |

| Table 1–2. Stratix Device Features — EP1S40, EP1S60, EP1S80 |           |           |           |  |  |  |  |  |  |  |

|-------------------------------------------------------------|-----------|-----------|-----------|--|--|--|--|--|--|--|

| Feature                                                     | EP1S40    | EP1S60    | EP1S80    |  |  |  |  |  |  |  |

| LEs                                                         | 41,250    | 57,120    | 79,040    |  |  |  |  |  |  |  |

| M512 RAM blocks (32 × 18 bits)                              | 384       | 574       | 767       |  |  |  |  |  |  |  |

| M4K RAM blocks (128 × 36 bits)                              | 183       | 292       | 364       |  |  |  |  |  |  |  |

| M-RAM blocks (4K × 144 bits)                                | 4         | 6         | 9         |  |  |  |  |  |  |  |

| Total RAM bits                                              | 3,423,744 | 5,215,104 | 7,427,520 |  |  |  |  |  |  |  |

| DSP blocks                                                  | 14        | 18        | 22        |  |  |  |  |  |  |  |

| Embedded multipliers (1)                                    | 112       | 144       | 176       |  |  |  |  |  |  |  |

| PLLs                                                        | 12        | 12        | 12        |  |  |  |  |  |  |  |

| Maximum user I/O pins                                       | 822       | 1,022     | 1,238     |  |  |  |  |  |  |  |

#### Note to Tables 1–1 and 1–2:

<sup>(1)</sup> This parameter lists the total number of  $9 \times 9$ -bit multipliers for each device. For the total number of  $18 \times 18$ -bit multipliers per device, divide the total number of  $9 \times 9$ -bit multipliers by 2. For the total number of  $36 \times 36$ -bit multipliers per device, divide the total number of  $9 \times 9$ -bit multipliers by 8.

With the LAB-wide addnsub control signal, a single LE can implement a one-bit adder and subtractor. This saves LE resources and improves performance for logic functions such as DSP correlators and signed multipliers that alternate between addition and subtraction depending on data.

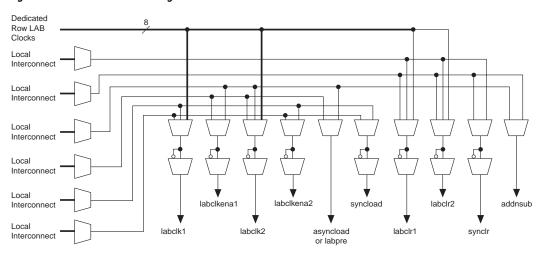

The LAB row clocks [7..0] and LAB local interconnect generate the LAB-wide control signals. The MultiTrack $^{\text{IM}}$  interconnect's inherent low skew allows clock and control signal distribution in addition to data. Figure 2–4 shows the LAB control signal generation circuit.

Figure 2-4. LAB-Wide Control Signals

# **Logic Elements**

The smallest unit of logic in the Stratix architecture, the LE, is compact and provides advanced features with efficient logic utilization. Each LE contains a four-input LUT, which is a function generator that can implement any function of four variables. In addition, each LE contains a programmable register and carry chain with carry select capability. A single LE also supports dynamic single bit addition or subtraction mode selectable by an LAB-wide control signal. Each LE drives all types of interconnects: local, row, column, LUT chain, register chain, and direct link interconnects. See Figure 2–5.

LAB Carry-In LAB Carry-In Sum1 A1 B1 LE1 Carry-In0 Carry-In1 Sum2 LE2 LUT B2 data1 Sum data2 Sum3 LUT LE3 A4 B4 Sum4 LUT LE4 LUT A5 B5 Sum5 LE5 Carry-Out0 Carry-Out1 Sum6 A6 B6 LE6 A7 B7 Sum7 LE7 \_<u>A8</u> \_B8 Sum8 LE8 <u>A9</u> B9 Sum9 LE9 Sum10 A10 B10 LE10 LAB Carry-Out

Figure 2-8. Carry Select Chain

# **Clear & Preset Logic Control**

LAB-wide signals control the logic for the register's clear and preset signals. The LE directly supports an asynchronous clear and preset function. The register preset is achieved through the asynchronous load of a logic high. The direct asynchronous preset does not require a NOT-gate push-back technique. Stratix devices support simultaneous preset/

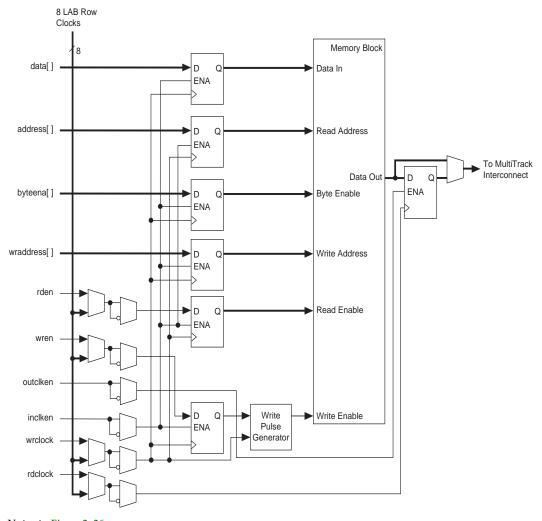

Figure 2–26. Input/Output Clock Mode in Simple Dual-Port Mode Notes (1), (2)

#### Notes to Figure 2–26:

- (1) All registers shown except the rden register have asynchronous clear ports.

- (2) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

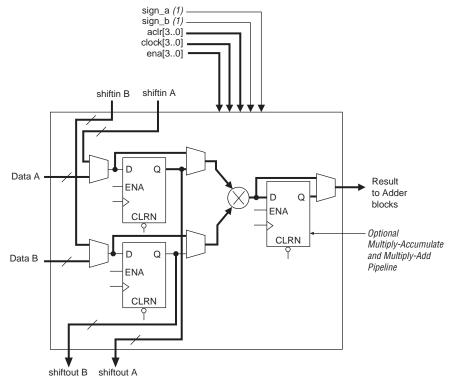

The DSP block consists of the following elements:

- Multiplier block

- Adder/output block

## **Multiplier Block**

The DSP block multiplier block consists of the input registers, a multiplier, and pipeline register for pipelining multiply-accumulate and multiply-add/subtract functions as shown in Figure 2–32.

Figure 2-32. Multiplier Sub-Block within Stratix DSP Block

Note to Figure 2-32:

(1) These signals can be unregistered or registered once to match data path pipelines if required.

For FIR filters, the DSP block combines the four-multipliers adder mode with the shift register inputs. One set of shift inputs contains the filter data, while the other holds the coefficients loaded in serial or parallel. The input shift register eliminates the need for shift registers external to the DSP block (i.e., implemented in LEs). This architecture simplifies filter design since the DSP block implements all of the filter circuitry.

One DSP block can implement an entire 18-bit FIR filter with up to four taps. For FIR filters larger than four taps, DSP blocks can be cascaded with additional adder stages implemented in LEs.

Table 2–16 shows the different number of multipliers possible in each DSP block mode according to size. These modes allow the DSP blocks to implement numerous applications for DSP including FFTs, complex FIR, FIR, and 2D FIR filters, equalizers, IIR, correlators, matrix multiplication and many other functions.

| Table 2–16. Multiplier Size & Configurations per DSP block |                                              |                                            |                                        |  |  |  |  |  |  |  |

|------------------------------------------------------------|----------------------------------------------|--------------------------------------------|----------------------------------------|--|--|--|--|--|--|--|

| DSP Block Mode                                             | 9 × 9                                        | 18 × 18                                    | <b>36</b> × <b>36</b> (1)              |  |  |  |  |  |  |  |

| Multiplier                                                 | Eight multipliers with eight product outputs | Four multipliers with four product outputs | One multiplier with one product output |  |  |  |  |  |  |  |

| Multiply-accumulator                                       | Two multiply and accumulate (52 bits)        | Two multiply and accumulate (52 bits)      | _                                      |  |  |  |  |  |  |  |

| Two-multipliers adder                                      | Four sums of two multiplier products each    | Two sums of two multiplier products each   | -                                      |  |  |  |  |  |  |  |

| Four-multipliers adder                                     | Two sums of four multiplier products each    | One sum of four multiplier products each   | -                                      |  |  |  |  |  |  |  |

Note to Table 2–16:

The number of supported multiply functions shown is based on signed/signed or unsigned/unsigned implementations.

#### **DSP Block Interface**

Stratix device DSP block outputs can cascade down within the same DSP block column. Dedicated connections between DSP blocks provide fast connections between the shift register inputs to cascade the shift register chains. You can cascade DSP blocks for  $9 \times 9$ - or  $18 \times 18$ -bit FIR filters larger than four taps, with additional adder stages implemented in LEs. If the DSP block is configured as  $36 \times 36$  bits, the adder, subtractor, or accumulator stages are implemented in LEs. Each DSP block can route the shift register chain out of the block to cascade two full columns of DSP blocks.

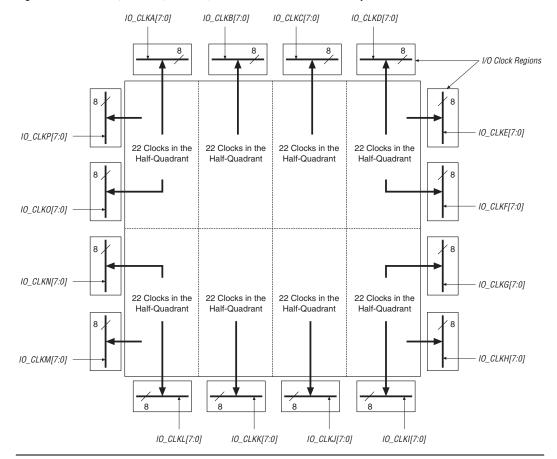

Figure 2-48. EP1S30, EP1S40, EP1S60, EP1S80 Device I/O Clock Groups

You can use the Quartus II software to control whether a clock input pin is either global, regional, or fast regional. The Quartus II software automatically selects the clocking resources if not specified.

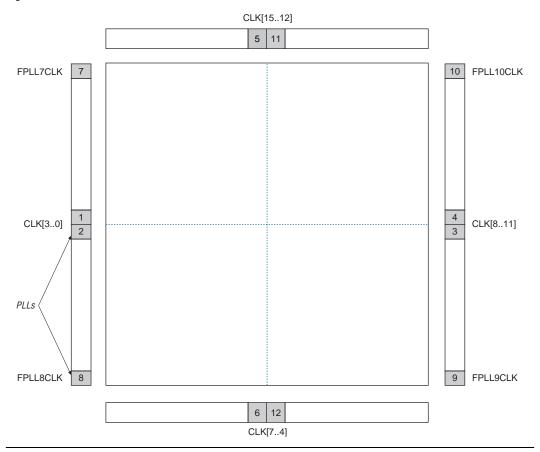

#### **Enhanced & Fast PLLs**

Stratix devices provide robust clock management and synthesis using up to four enhanced PLLs and eight fast PLLs. These PLLs increase performance and provide advanced clock interfacing and clock-frequency synthesis. With features such as clock switchover, spread spectrum clocking, programmable bandwidth, phase and delay control, and PLL reconfiguration, the Stratix device's enhanced PLLs provide you with complete control of your clocks and system timing. The fast PLLs

Figure 2–49 shows a top-level diagram of the Stratix device and PLL floorplan.

Tables 2–25 and 2–26 show the performance specification for DDR SDRAM, RLDRAM II, QDR SRAM, QDRII SRAM, and ZBT SRAM interfaces in EP1S10 through EP1S40 devices and in EP1S60 and EP1S80 devices. The DDR SDRAM and QDR SRAM numbers in Table 2–25 have been verified with hardware characterization with third-party DDR SDRAM and QDR SRAM devices over temperature and voltage extremes.

| Table 2–25. External                 | Table 2–25. External RAM Support in EP1S10 through EP1S40 Devices |                          |           |               |               |               |                |               |  |  |  |  |

|--------------------------------------|-------------------------------------------------------------------|--------------------------|-----------|---------------|---------------|---------------|----------------|---------------|--|--|--|--|

|                                      |                                                                   | Maximum Clock Rate (MHz) |           |               |               |               |                |               |  |  |  |  |

| DDR Memory Type                      | I/O<br>Standard                                                   | -5 Speed<br>Grade        | -6 Spee   | d Grade       | -7 Spec       | ed Grade      | -8 Speed Grade |               |  |  |  |  |

|                                      |                                                                   | Flip-Chip                | Flip-Chip | Wire-<br>Bond | Flip-<br>Chip | Wire-<br>Bond | Flip-<br>Chip  | Wire-<br>Bond |  |  |  |  |

| DDR SDRAM (1), (2)                   | SSTL-2                                                            | 200                      | 167       | 133           | 133           | 100           | 100            | 100           |  |  |  |  |

| DDR SDRAM - side banks (2), (3), (4) | SSTL-2                                                            | 150                      | 133       | 110           | 133           | 100           | 100            | 100           |  |  |  |  |

| RLDRAM II (4)                        | 1.8-V HSTL                                                        | 200                      | (5)       | (5)           | (5)           | (5)           | (5)            | (5)           |  |  |  |  |

| QDR SRAM (6)                         | 1.5-V HSTL                                                        | 167                      | 167       | 133           | 133           | 100           | 100            | 100           |  |  |  |  |

| QDRII SRAM (6)                       | 1.5-V HSTL                                                        | 200                      | 167       | 133           | 133           | 100           | 100            | 100           |  |  |  |  |

| ZBT SRAM (7)                         | LVTTL                                                             | 200                      | 200       | 200           | 167           | 167           | 133            | 133           |  |  |  |  |

#### Notes to Table 2-25:

- (1) These maximum clock rates apply if the Stratix device uses DQS phase-shift circuitry to interface with DDR SDRAM. DQS phase-shift circuitry is only available in the top and bottom I/O banks (I/O banks 3, 4, 7, and 8).

- (2) For more information on DDR SDRAM, see AN 342: Interfacing DDR SDRAM with Stratix & Stratix GX Devices.

- (3) DDR SDRAM is supported on the Stratix device side I/O banks (I/O banks 1, 2, 5, and 6) without dedicated DQS phase-shift circuitry. The read DQS signal is ignored in this mode.

- (4) These performance specifications are preliminary.

- (5) This device does not support RLDRAM II.

- (6) For more information on QDR or QDRII SRAM, see AN 349: QDR SRAM Controller Reference Design for Stratix & Stratix GX Devices.

- (7) For more information on ZBT SRAM, see AN 329: ZBT SRAM Controller Reference Design for Stratix & Stratix GX Devices.

- RapidIO

- HyperTransport

#### **Dedicated Circuitry**

Stratix devices support source-synchronous interfacing with LVDS, LVPECL, 3.3-V PCML, or HyperTransport signaling at up to 840 Mbps. Stratix devices can transmit or receive serial channels along with a low-speed or high-speed clock. The receiving device PLL multiplies the clock by a integer factor W (W = 1 through 32). For example, a HyperTransport application where the data rate is 800 Mbps and the clock rate is 400 MHz would require that W be set to 2. The SERDES factor J determines the parallel data width to deserialize from receivers or to serialize for transmitters. The SERDES factor J can be set to 4, 7, 8, or 10 and does not have to equal the PLL clock-multiplication W value. For a J factor of 1, the Stratix device bypasses the SERDES block. For a J factor of 2, the Stratix device bypasses the SERDES block, and the DDR input and output registers are used in the IOE. See Figure 2–73.

R4, R8, and R24 Interconnect 840 Mbps 840 Mbps 8 Data Dedicated Dedicated Local Receiver Transmitter Interconnect Interface Interface rx load en 8× 8× 105 MHz Fast tx\_load\_en PLL Regional or global clock

Figure 2–73. High-Speed Differential I/O Receiver / Transmitter Interface Example

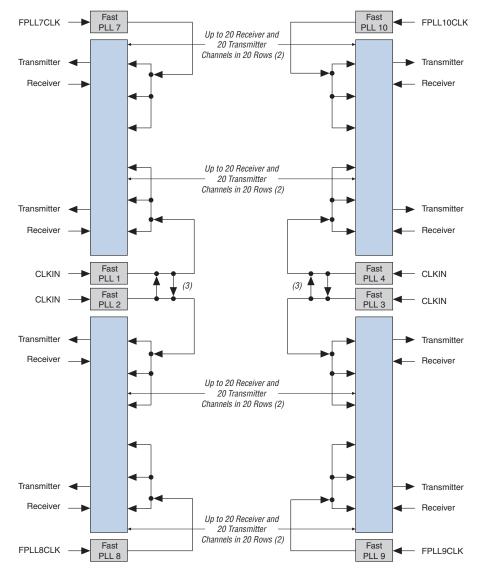

An external pin or global or regional clock can drive the fast PLLs, which can output up to three clocks: two multiplied high-speed differential I/O clocks to drive the SERDES block and/or external pin, and a low-speed clock to drive the logic array.

Figure 2-75. Fast PLL & Channel Layout in the EP1S30 to EP1S80 Devices Note (1)

#### Notes to Figure 2-75:

- (1) Wire-bond packages support up to 624 Mbps.

- (2) See Table 2–38 through 2–41 for the number of channels each device supports.

- (3) There is a multiplexer here to select the PLL clock source. If a PLL uses this multiplexer to clock channels outside of its bank quadrant, those clocked channels support up to 840 Mbps for "high" speed channels and 462 Mbps for "low" speed channels as labeled in the device pin-outs at www.altera.com.

Figure 4–2. Transmitter Output Waveforms for Differential I/O Standards

# Single-Ended Waveform Positive Channel (p) = $V_{OH}$ $V_{CM}$ Negative Channel (n) = $V_{OL}$ Ground

# Differential Waveform $V_{OD} = 0 \text{ V}$ $V_{OD} = 0 \text{ V}$

Tables 4–10 through 4–33 recommend operating conditions, DC operating conditions, and capacitance for 1.5-V Stratix devices.

| Table 4–10. 3.3-V LVDS I/O Specifications (Part 1 of 2) |                                                 |                                                                                 |         |         |         |      |  |  |  |  |  |

|---------------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------|---------|---------|---------|------|--|--|--|--|--|

| Symbol                                                  | Parameter                                       | Conditions                                                                      | Minimum | Typical | Maximum | Unit |  |  |  |  |  |

| V <sub>CCIO</sub>                                       | I/O supply voltage                              |                                                                                 | 3.135   | 3.3     | 3.465   | V    |  |  |  |  |  |

| V <sub>ID</sub> (6)                                     | Input differential voltage swing (single-ended) | $0.1 \text{ V} \leq \text{V}_{\text{CM}} < 1.1 \text{ V}$<br>W = 1  through  10 | 300     |         | 1,000   | mV   |  |  |  |  |  |

|                                                         |                                                 | 1.1 V $\leq$ V <sub>CM</sub> $\leq$ 1.6 V $W = 1$                               | 200     |         | 1,000   | mV   |  |  |  |  |  |

|                                                         |                                                 | 1.1 V $\leq$ V <sub>CM</sub> $\leq$ 1.6 V<br>W = 2 through 10                   | 100     |         | 1,000   | mV   |  |  |  |  |  |

|                                                         |                                                 | 1.6 V < $V_{CM} \le 1.8 \text{ V}$<br>W = 1  through  10                        | 300     |         | 1,000   | mV   |  |  |  |  |  |

# **Timing Model**

The DirectDrive<sup>TM</sup> technology and MultiTrack<sup>TM</sup> interconnect ensure predictable performance, accurate simulation, and accurate timing analysis across all Stratix device densities and speed grades. This section describes and specifies the performance, internal, external, and PLL timing specifications.

All specifications are representative of worst-case supply voltage and junction temperature conditions.

### **Preliminary & Final Timing**

Timing models can have either preliminary or final status. The Quartus II software issues an informational message during the design compilation if the timing models are preliminary. Table 4–35 shows the status of the Stratix device timing models.

Preliminary status means the timing model is subject to change. Initially, timing numbers are created using simulation results, process data, and other known parameters. These tests are used to make the preliminary numbers as close to the actual timing parameters as possible.

Final timing numbers are based on actual device operation and testing. These numbers reflect the actual performance of the device under worst-case voltage and junction temperature conditions.

| e 4–35. Stratix Dev |             |          |  |  |  |  |  |

|---------------------|-------------|----------|--|--|--|--|--|

| Device              | Preliminary | Final    |  |  |  |  |  |

| EP1S10              |             | ✓        |  |  |  |  |  |

| EP1S20              |             | ✓        |  |  |  |  |  |

| EP1S25              |             | ✓        |  |  |  |  |  |

| EP1S30              |             | ✓        |  |  |  |  |  |

| EP1S40              |             | ✓        |  |  |  |  |  |

| EP1S60              |             | ✓        |  |  |  |  |  |

| EP1S80              |             | <b>✓</b> |  |  |  |  |  |

| Device | Symbol            | -   | -5  |     | 6   | -   | -7  |     | -8  |    |

|--------|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|----|

|        | Symbol            | Min | Max | Min | Max | Min | Max | Min | Max |    |

| EP1S40 | t <sub>SU_R</sub> | 76  |     | 80  |     | 80  |     | 80  |     | ps |

|        | t <sub>SU_C</sub> | 376 |     | 380 |     | 380 |     | 380 |     | ps |

| EP1S60 | t <sub>SU_R</sub> | 276 |     | 280 |     | 280 |     | 280 |     | ps |

|        | t <sub>SU_C</sub> | 276 |     | 280 |     | 280 |     | 280 |     | ps |

| EP1S80 | t <sub>SU_R</sub> | 426 |     | 430 |     | 430 |     | 430 |     | ps |

|        | t <sub>SU_C</sub> | 76  |     | 80  |     | 80  |     | 80  |     | ps |

| Table 4–46. IOE Internal Timing Microparameters |       |       |       |       |       |       |       |       |      |  |

|-------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|------|--|

| 0h - l                                          | -     | -5    |       | -6    |       | -7    |       | -8    |      |  |

| Symbol                                          | Min   | Max   | Min   | Max   | Min   | Max   | Min   | Max   | Unit |  |

| t <sub>H</sub>                                  | 68    |       | 71    |       | 82    |       | 96    |       | ps   |  |

| t <sub>CO_R</sub>                               |       | 171   |       | 179   |       | 206   |       | 242   | ps   |  |

| t <sub>CO_C</sub>                               |       | 171   |       | 179   |       | 206   |       | 242   | ps   |  |

| t <sub>PIN2COMBOUT_R</sub>                      |       | 1,234 |       | 1,295 |       | 1,490 |       | 1,753 | ps   |  |

| t <sub>PIN2COMBOUT_C</sub>                      |       | 1,087 |       | 1,141 |       | 1,312 |       | 1,544 | ps   |  |

| t <sub>COMBIN2PIN_R</sub>                       |       | 3,894 |       | 4,089 |       | 4,089 |       | 4,089 | ps   |  |

| t <sub>COMBIN2PIN_C</sub>                       |       | 4,299 |       | 4,494 |       | 4,494 |       | 4,494 | ps   |  |

| t <sub>CLR</sub>                                | 276   |       | 289   |       | 333   |       | 392   |       | ps   |  |

| t <sub>PRE</sub>                                | 260   |       | 273   |       | 313   |       | 369   |       | ps   |  |

| t <sub>CLKHL</sub>                              | 1,000 |       | 1,111 |       | 1,190 |       | 1,400 |       | ps   |  |

| Table 4–47. DSP Block Internal Timing Microparameters (Part 1 of 2) |     |       |     |       |     |       |     |       |      |  |

|---------------------------------------------------------------------|-----|-------|-----|-------|-----|-------|-----|-------|------|--|

| Symbol                                                              | -5  |       | -   | -6    |     | -7    |     | -8    |      |  |

|                                                                     | Min | Max   | Min | Max   | Min | Max   | Min | Max   | Unit |  |

| t <sub>SU</sub>                                                     | 0   |       | 0   |       | 0   |       | 0   |       | ps   |  |

| t <sub>H</sub>                                                      | 67  |       | 75  |       | 86  |       | 101 |       | ps   |  |

| t <sub>CO</sub>                                                     |     | 142   |     | 158   |     | 181   |     | 214   | ps   |  |

| t <sub>INREG2PIPE9</sub>                                            |     | 2,613 |     | 2,982 |     | 3,429 |     | 4,035 | ps   |  |

| t <sub>INREG2PIPE18</sub>                                           |     | 3,390 |     | 3,993 |     | 4,591 |     | 5,402 | ps   |  |

Tables 4–79 through 4–84 show the external timing parameters on column and row pins for EP1S40 devices.

| Table 4-79. I      | Table 4–79. EP1S40 External I/O Timing on Column Pins Using Fast Regional Clock Networks |       |                |       |                |       |                |       |      |  |  |  |

|--------------------|------------------------------------------------------------------------------------------|-------|----------------|-------|----------------|-------|----------------|-------|------|--|--|--|

| Parameter          | -5 Speed Grade                                                                           |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       |      |  |  |  |

|                    | Min                                                                                      | Max   | Min            | Max   | Min            | Max   | Min            | Max   | Unit |  |  |  |

| t <sub>INSU</sub>  | 2.696                                                                                    |       | 2.907          |       | 3.290          |       | 2.899          |       | ns   |  |  |  |

| t <sub>INH</sub>   | 0.000                                                                                    |       | 0.000          |       | 0.000          |       | 0.000          |       | ns   |  |  |  |

| t <sub>OUTCO</sub> | 2.506                                                                                    | 5.015 | 2.506          | 5.348 | 2.506          | 5.809 | 2.698          | 7.286 | ns   |  |  |  |

| t <sub>XZ</sub>    | 2.446                                                                                    | 4.889 | 2.446          | 5.216 | 2.446          | 5.685 | 2.638          | 7.171 | ns   |  |  |  |

| t <sub>ZX</sub>    | 2.446                                                                                    | 4.889 | 2.446          | 5.216 | 2.446          | 5.685 | 2.638          | 7.171 | ns   |  |  |  |

| Table 4-80. I        | Table 4–80. EP1S40 External I/O Timing on Column Pins Using Regional Clock Networks |                |       |                |       |         |         |       |      |  |  |  |

|----------------------|-------------------------------------------------------------------------------------|----------------|-------|----------------|-------|---------|---------|-------|------|--|--|--|

| Parameter            | -5 Spee                                                                             | -5 Speed Grade |       | -6 Speed Grade |       | d Grade | -8 Spee | Heit  |      |  |  |  |

| rarameter            | Min                                                                                 | Max            | Min   | Max            | Min   | Max     | Min     | Max   | Unit |  |  |  |

| t <sub>INSU</sub>    | 2.413                                                                               |                | 2.581 |                | 2.914 |         | 2.938   |       | ns   |  |  |  |

| t <sub>INH</sub>     | 0.000                                                                               |                | 0.000 |                | 0.000 |         | 0.000   |       | ns   |  |  |  |

| t <sub>outco</sub>   | 2.668                                                                               | 5.254          | 2.668 | 5.628          | 2.668 | 6.132   | 2.869   | 7.307 | ns   |  |  |  |

| t <sub>XZ</sub>      | 2.608                                                                               | 5.128          | 2.608 | 5.496          | 2.608 | 6.008   | 2.809   | 7.192 | ns   |  |  |  |

| t <sub>ZX</sub>      | 2.608                                                                               | 5.128          | 2.608 | 5.496          | 2.608 | 6.008   | 2.809   | 7.192 | ns   |  |  |  |

| t <sub>INSUPLL</sub> | 1.385                                                                               |                | 1.376 |                | 1.609 |         | 1.837   |       | ns   |  |  |  |

| t <sub>INHPLL</sub>  | 0.000                                                                               |                | 0.000 |                | 0.000 |         | 0.000   |       | ns   |  |  |  |

| toutcopll            | 1.117                                                                               | 2.382          | 1.117 | 2.552          | 1.117 | 2.504   | 1.117   | 2.542 | ns   |  |  |  |

| t <sub>XZPLL</sub>   | 1.057                                                                               | 2.256          | 1,057 | 2.420          | 1.057 | 2.380   | 1.057   | 2.427 | ns   |  |  |  |

| t <sub>ZXPLL</sub>   | 1.057                                                                               | 2.256          | 1,057 | 2.420          | 1.057 | 2.380   | 1.057   | 2.427 | ns   |  |  |  |

The scaling factors for column output pin timing in Tables 4–111 to 4–113 are shown in units of time per pF unit of capacitance (ps/pF). Add this delay to the  $t_{\rm CO}$  or combinatorial timing path for output or bidirectional pins in addition to the I/O adder delays shown in Tables 4–103 through 4–108 and the IOE programmable delays in Tables 4–109 and 4–110.

| Table 4–111. Output Delay Adder for Loading on LVTTL/LVCMOS Output Buffers Note (1) |                                           |                                                                |    |     |     |    |  |

|-------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------|----|-----|-----|----|--|

| Conditi                                                                             | Conditions Output Pin Adder Delay (ps/pF) |                                                                |    |     |     |    |  |

| Parameter                                                                           | Value                                     | 3.3-V LVTTL   2.5-V LVTTL   1.8-V LVTTL   1.5-V LVTTL   LVCMOS |    |     |     |    |  |

|                                                                                     | 24mA                                      | 15                                                             | -  | -   | =   | 8  |  |

|                                                                                     | 16mA                                      | 25                                                             | 18 | -   | _   | -  |  |

| Drive Strength                                                                      | 12mA                                      | 30                                                             | 25 | 25  | -   | 15 |  |

| Drive Strength                                                                      | 8mA                                       | 50                                                             | 35 | 40  | 35  | 20 |  |

|                                                                                     | 4mA                                       | 60                                                             | -  | -   | 80  | 30 |  |

|                                                                                     | 2mA                                       | _                                                              | 75 | 120 | 160 | 60 |  |

Note to Table 4-111:

(1) The timing information in this table is preliminary.

| Table 4–112. Output Delay Adder for Loading on SSTL/HSTL Output Buffers Note (1) |                                |        |          |            |  |  |

|----------------------------------------------------------------------------------|--------------------------------|--------|----------|------------|--|--|

| Conditions                                                                       | Output Pin Adder Delay (ps/pF) |        |          |            |  |  |

| Conditions                                                                       | SSTL-3                         | SSTL-2 | SSTL-1.8 | 1.5-V HSTL |  |  |

| Class I                                                                          | 25                             | 25     | 25       | 25         |  |  |

| Class II                                                                         | 25                             | 20     | 25       | 20         |  |  |

Note to Table 4–112:

(1) The timing information in this table is preliminary.

| Table 4–113. Output Delay Adder for Loading on GTL+/GTL/CTT/PCI Output Buffers Note (1) |                                           |      |     |     |     |     |

|-----------------------------------------------------------------------------------------|-------------------------------------------|------|-----|-----|-----|-----|

| Condi                                                                                   | Conditions Output Pin Adder Delay (ps/pF) |      |     |     |     |     |

| Parameter                                                                               | Value                                     | GTL+ | GTL | СТТ | PCI | AGP |

| VCCIO Voltage                                                                           | 3.3V                                      | 18   | 18  | 25  | 20  | 20  |

| Level                                                                                   | 2.5V                                      | 15   | 18  | -   | -   | -   |

Note to Table 4-113:

(1) The timing information in this table is preliminary.

| Table 4–129. Enhanced PLL Specifications for -7 Speed Grade (Part 2 of 2) |                                                                                                                   |     |     |                                                            |              |  |  |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|------------------------------------------------------------|--------------|--|--|

| Symbol                                                                    | Parameter                                                                                                         | Min | Тур | Max                                                        | Unit         |  |  |

| t <sub>OUTDUTY</sub>                                                      | Duty cycle for external clock output (when set to 50%)                                                            | 45  |     | 55                                                         | %            |  |  |

| t <sub>JITTER</sub>                                                       | Period jitter for external clock output (6)                                                                       |     |     | ±100 ps for >200-MHz outclk<br>±20 mUI for <200-MHz outclk | ps or<br>mUI |  |  |

| t <sub>CONFIG5,6</sub>                                                    | Time required to reconfigure the scan chains for PLLs 5 and 6                                                     |     |     | 289/f <sub>SCANCLK</sub>                                   |              |  |  |

| t <sub>CONFIG11,12</sub>                                                  | Time required to reconfigure the scan chains for PLLs 11 and 12                                                   |     |     | 193/f <sub>SCANCLK</sub>                                   |              |  |  |

| t <sub>SCANCLK</sub>                                                      | scanclk frequency (5)                                                                                             |     |     | 22                                                         | MHz          |  |  |

| t <sub>DLOCK</sub>                                                        | Time required to lock dynamically (after switchover or reconfiguring any non-post-scale counters/delays) (7) (11) | (9) |     | 100                                                        | μs           |  |  |

| t <sub>LOCK</sub>                                                         | Time required to lock from end of device configuration (11)                                                       | 10  |     | 400                                                        | μs           |  |  |

| f <sub>VCO</sub>                                                          | PLL internal VCO operating range                                                                                  | 300 |     | 600 (8)                                                    | MHz          |  |  |

| t <sub>LSKEW</sub>                                                        | Clock skew between two external clock outputs driven by the same counter                                          |     | ±50 |                                                            | ps           |  |  |

| t <sub>SKEW</sub>                                                         | Clock skew between two external clock outputs driven by the different counters with the same settings             |     | ±75 |                                                            | ps           |  |  |

| f <sub>SS</sub>                                                           | Spread spectrum modulation frequency                                                                              | 30  |     | 150                                                        | kHz          |  |  |

| % spread                                                                  | Percentage spread for spread spectrum frequency (10)                                                              | 0.5 |     | 0.6                                                        | %            |  |  |

| t <sub>ARESET</sub>                                                       | Minimum pulse width on areset signal                                                                              | 10  |     |                                                            | ns           |  |  |

| Table 4–130. Enhanced PLL Specifications for -8 Speed Grade (Part 1 of 3) |                                          |               |     |          |      |  |

|---------------------------------------------------------------------------|------------------------------------------|---------------|-----|----------|------|--|

| Symbol                                                                    | Parameter                                | Min           | Тур | Max      | Unit |  |

| f <sub>IN</sub>                                                           | Input clock frequency                    | 3<br>(1), (2) |     | 480      | MHz  |  |

| f <sub>INPFD</sub>                                                        | Input frequency to PFD                   | 3             |     | 420      | MHz  |  |

| f <sub>INDUTY</sub>                                                       | Input clock duty cycle                   | 40            |     | 60       | %    |  |

| f <sub>EINDUTY</sub>                                                      | External feedback clock input duty cycle | 40            |     | 60       | %    |  |

| t <sub>INJITTER</sub>                                                     | Input clock period jitter                |               |     | ±200 (3) | ps   |  |

| Symbol                   | Parameter                                                                                                         | Min | Тур | Max                                                        | Unit         |

|--------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|------------------------------------------------------------|--------------|

| t <sub>EINJITTER</sub>   | External feedback clock period jitter                                                                             |     |     | ±200 (3)                                                   | ps           |

| t <sub>FCOMP</sub>       | External feedback clock compensation time (4)                                                                     |     |     | 6                                                          | ns           |

| f <sub>OUT</sub>         | Output frequency for internal global or regional clock                                                            | 0.3 |     | 357                                                        | MHz          |

| f <sub>OUT_EXT</sub>     | Output frequency for external clock (3)                                                                           | 0.3 |     | 369                                                        | MHz          |

| t <sub>OUTDUTY</sub>     | Duty cycle for external clock output (when set to 50%)                                                            | 45  |     | 55                                                         | %            |

| t <sub>JITTER</sub>      | Period jitter for external clock output (6)                                                                       |     |     | ±100 ps for >200-MHz outclk<br>±20 mUI for <200-MHz outclk | ps or<br>mUI |

| t <sub>CONFIG5,6</sub>   | Time required to reconfigure the scan chains for PLLs 5 and 6                                                     |     |     | 289/f <sub>SCANCLK</sub>                                   |              |

| t <sub>CONFIG11,12</sub> | Time required to reconfigure the scan chains for PLLs 11 and 12                                                   |     |     | 193/f <sub>SCANCLK</sub>                                   |              |

| t <sub>SCANCLK</sub>     | scanclk frequency (5)                                                                                             |     |     | 22                                                         | MHz          |

| t <sub>DLOCK</sub>       | Time required to lock dynamically (after switchover or reconfiguring any non-post-scale counters/delays) (7) (11) | (9) |     | 100                                                        | μs           |

| t <sub>LOCK</sub>        | Time required to lock from end of device configuration (11)                                                       | 10  |     | 400                                                        | μs           |

| f <sub>VCO</sub>         | PLL internal VCO operating range                                                                                  | 300 |     | 600 (8)                                                    | MHz          |

| Table 4–132. Fast PLL Specifications for -7 Speed Grades (Part 2 of 2) |                                                            |     |     |         |  |  |

|------------------------------------------------------------------------|------------------------------------------------------------|-----|-----|---------|--|--|

| Symbol                                                                 | Parameter                                                  | Min | Max | Unit    |  |  |

| t <sub>JITTER</sub>                                                    | Period jitter for DIFFIO clock out (6)                     |     | (5) | ps      |  |  |

| t <sub>LOCK</sub>                                                      | Time required for PLL to acquire lock                      | 10  | 100 | μs      |  |  |

| m                                                                      | Multiplication factors for <i>m</i> counter (7)            | 1   | 32  | Integer |  |  |

| 10, 11, g0                                                             | Multiplication factors for IO, I1, and gO counter (7), (8) | 1   | 32  | Integer |  |  |

| t <sub>ARESET</sub>                                                    | Minimum pulse width on areset signal                       | 10  |     | ns      |  |  |

| Table 4–133. Fast PLL Specifications for -8 Speed Grades (Part 1 of 2) |                                                                                   |       |      |         |  |  |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------|------|---------|--|--|

| Symbol                                                                 | Parameter                                                                         | Min   | Max  | Unit    |  |  |

| f <sub>IN</sub>                                                        | CLKIN frequency (1), (3)                                                          | 10    | 460  | MHz     |  |  |

| f <sub>INPFD</sub>                                                     | Input frequency to PFD                                                            | 10    | 500  | MHz     |  |  |

| f <sub>OUT</sub>                                                       | Output frequency for internal global or regional clock (4)                        | 9.375 | 420  | MHz     |  |  |

| f <sub>OUT_DIFFIO</sub>                                                | Output frequency for external clock driven out on a differential I/O data channel | (5)   | (5)  | MHz     |  |  |

| f <sub>VCO</sub>                                                       | VCO operating frequency                                                           | 300   | 700  | MHz     |  |  |

| t <sub>INDUTY</sub>                                                    | CLKIN duty cycle                                                                  | 40    | 60   | %       |  |  |

| t <sub>INJITTER</sub>                                                  | Period jitter for CLKIN pin                                                       |       | ±200 | ps      |  |  |

| t <sub>DUTY</sub>                                                      | Duty cycle for DFFIO 1× CLKOUT pin (6)                                            | 45    | 55   | %       |  |  |

| t <sub>JITTER</sub>                                                    | Period jitter for DIFFIO clock out (6)                                            |       | (5)  | ps      |  |  |

| t <sub>LOCK</sub>                                                      | Time required for PLL to acquire lock                                             | 10    | 100  | μs      |  |  |

| m                                                                      | Multiplication factors for <i>m</i> counter (7)                                   | 1     | 32   | Integer |  |  |

| 10, 11, g0                                                             | Multiplication factors for I0, I1, and g0 counter (7), (8)                        | 1     | 32   | Integer |  |  |