Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Obsolete                                                  |

| Number of LABs/CLBs            | 2566                                                      |

| Number of Logic Elements/Cells | 25660                                                     |

| Total RAM Bits                 | 1944576                                                   |

| Number of I/O                  | 706                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.425V ~ 1.575V                                           |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 1020-BBGA                                                 |

| Supplier Device Package        | 1020-FBGA (33x33)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s25f1020c6n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| DSP Block Interface                                                                                                                                                                                                                                                                                                                                              | 2–70                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| PLLs & Clock Networks                                                                                                                                                                                                                                                                                                                                            |                     |

| Global & Hierarchical Clocking                                                                                                                                                                                                                                                                                                                                   | 2–73                |

| Enhanced & Fast PLLs                                                                                                                                                                                                                                                                                                                                             |                     |

| Enhanced PLLs                                                                                                                                                                                                                                                                                                                                                    |                     |

| Fast PLLs                                                                                                                                                                                                                                                                                                                                                        | 2–100               |

| I/O Structure                                                                                                                                                                                                                                                                                                                                                    | 2–104               |

| Double-Data Rate I/O Pins                                                                                                                                                                                                                                                                                                                                        |                     |

| External RAM Interfacing                                                                                                                                                                                                                                                                                                                                         |                     |

| Programmable Drive Strength                                                                                                                                                                                                                                                                                                                                      |                     |

| Open-Drain Output                                                                                                                                                                                                                                                                                                                                                | 2–120               |

| Slew-Rate Control                                                                                                                                                                                                                                                                                                                                                | 2–120               |

| Bus Hold                                                                                                                                                                                                                                                                                                                                                         |                     |

| Programmable Pull-Up Resistor                                                                                                                                                                                                                                                                                                                                    |                     |

| Advanced I/O Standard Support                                                                                                                                                                                                                                                                                                                                    |                     |

| Differential On-Chip Termination                                                                                                                                                                                                                                                                                                                                 |                     |

| MultiVolt I/O Interface                                                                                                                                                                                                                                                                                                                                          |                     |

| High-Speed Differential I/O Support                                                                                                                                                                                                                                                                                                                              |                     |

| Dedicated Circuitry                                                                                                                                                                                                                                                                                                                                              |                     |

| Byte Alignment                                                                                                                                                                                                                                                                                                                                                   |                     |

| Power Sequencing & Hot Socketing                                                                                                                                                                                                                                                                                                                                 |                     |

| IEEE Std. 1149.1 (JTAG) Boundary-Scan Support SignalTap II Embedded Logic Analyzer Configuration Operating Modes Configuring Stratix FPGAs with JRunner Configuration Schemes Partial Reconfiguration Remote Update Configuration Modes Stratix Automated Single Event Upset (SEU) Detection Custom-Built Circuitry Software Interface Temperature Sensing Diode |                     |

| Chapter 4. DC & Switching Characteristics Operating Conditions Power Consumption Timing Model                                                                                                                                                                                                                                                                    | 4–1<br>4–17<br>4–19 |

| Preliminary & Final Timing                                                                                                                                                                                                                                                                                                                                       |                     |

| Performance                                                                                                                                                                                                                                                                                                                                                      |                     |

| Internal Timing Parameters                                                                                                                                                                                                                                                                                                                                       |                     |

| External Timing Parameters                                                                                                                                                                                                                                                                                                                                       |                     |

| Stratix External I/O Timing                                                                                                                                                                                                                                                                                                                                      |                     |

| I/O Timing Measurement Methodology                                                                                                                                                                                                                                                                                                                               |                     |

| External I/O Delay Parameters                                                                                                                                                                                                                                                                                                                                    | 4–66                |

# Section I. Stratix Device Family Data Sheet

This section provides the data sheet specifications for Stratix® devices. They contain feature definitions of the internal architecture, configuration and JTAG boundary-scan testing information, DC operating conditions, AC timing parameters, a reference to power consumption, and ordering information for Stratix devices.

This section contains the following chapters:

- Chapter 1, Introduction

- Chapter 2, Stratix Architecture

- Chapter 3, Configuration & Testing

- Chapter 4, DC & Switching Characteristics

- Chapter 5, Reference & Ordering Information

#### **Revision History**

The table below shows the revision history for Chapters 1 through 5.

| Chapter | Date/Version         | Changes Made                                                                                                                                                                                                                                                                                                                     |

|---------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | July 2005, v3.2      | Minor content changes.                                                                                                                                                                                                                                                                                                           |

|         | September 2004, v3.1 | Updated Table 1–6 on page 1–5.                                                                                                                                                                                                                                                                                                   |

|         | April 2004, v3.0     | <ul> <li>Main section page numbers changed on first page.</li> <li>Changed PCI-X to PCI-X 1.0 in "Features" on page 1–2.</li> <li>Global change from SignalTap to SignalTap II.</li> <li>The DSP blocks in "Features" on page 1–2 provide dedicated implementation of multipliers that are now "faster than 300 MHz."</li> </ul> |

|         | January 2004, v2.2   | Updated -5 speed grade device information in Table 1-6.                                                                                                                                                                                                                                                                          |

|         | October 2003, v2.1   | Add -8 speed grade device information.                                                                                                                                                                                                                                                                                           |

|         | July 2003, v2.0      | Format changes throughout chapter.                                                                                                                                                                                                                                                                                               |

Altera Corporation Section I–1

| Chapter | Date/Version        | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4       |                     | <ul> <li>Updated Table 4–123 on page 4–85 through Table 4–126 on page 4–92.</li> <li>Updated Note 3 in Table 4–123 on page 4–85.</li> <li>Table 4–125 on page 4–88: moved to correct order in chapter, and updated table.</li> <li>Updated Table 4–126 on page 4–92.</li> <li>Updated Table 4–127 on page 4–94.</li> <li>Updated Table 4–128 on page 4–95.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | April 2004, v3.0    | <ul> <li>Table 4–129 on page 4–96: updated table and added Note 10.</li> <li>Updated Table 4–131 and Table 4–132 on page 4–100.</li> <li>Updated Table 4–110 on page 4–74.</li> <li>Updated Table 4–123 on page 4–85.</li> <li>Updated Table 4–124 on page 4–87. through Table 4–126 on page 4–92.</li> <li>Added Note 10 to Table 4–129 on page 4–96.</li> <li>Moved Table 4–127 on page 4–94 to correct order in the chapter.</li> <li>Updated Table 4–131 on page 4–100 through Table 4–132 on page 4–100.</li> <li>Deleted t<sub>XZ</sub> and t<sub>ZX</sub> from Figure 4–4.</li> <li>Waveform was added to Figure 4–6.</li> <li>The minimum and maximum duty cycle values in Note 3 of Table 4–8 were moved to a new Table 4–9.</li> <li>Changes were made to values in SSTL-3 Class I and II rows in Table 4–17.</li> <li>Note 1 was added to Table 4–34.</li> <li>Added t<sub>SU_R</sub> and t<sub>SU_C</sub> rows in Table 4–38.</li> <li>Changed Table 4–55 title from "EP1S10 Column Pin Fast Regional Clock External I/O Timing Parameters" to "EP1S10 External I/O Timing on Column Pins Using Fast Regional Clock Networks."</li> <li>Changed values in Tables 4–46, 4–48 to 4–51, 4–128, and 4–131.</li> <li>Added t<sub>ARESET</sub> row in Tables 4–127 to 4–132.</li> <li>Deleted -5 Speed Grade column in Tables 4–117 to 4–119 and 4–122 to 4–123.</li> <li>Fixed differential waveform in Figure 4–1.</li> <li>Added "Definition of I/O Skew" section.</li> <li>Added t<sub>SU</sub> and t<sub>CO_C</sub> rows and made changes to values in t<sub>PRE</sub> and t<sub>CLKHL</sub> rows in Table 4–46.</li> <li>Values changed in the t<sub>MAKCLKHL</sub> row in Table 4–47.</li> <li>Values changed in the t<sub>MMAKCLKHL</sub> row in Table 4–55 through 4–96.</li> <li>Added Table 4–51 to "Internal Timing Parameters" section.</li> <li>The timing information is preliminary in Tables 4–55 through 4–96.</li> <li>Table 4–111 was separated into 3 tables: Tables 4–111 to 4–113.</li> </ul> |

|         | November 2003, v2.2 | Updated Tables 4–127 through 4–129.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Section I–6 Altera Corporation

### TriMatrix Memory

TriMatrix memory consists of three types of RAM blocks: M512, M4K, and M-RAM blocks. Although these memory blocks are different, they can all implement various types of memory with or without parity, including true dual-port, simple dual-port, and single-port RAM, ROM, and FIFO buffers. Table 2–3 shows the size and features of the different RAM blocks.

| Table 2–3. TriMatrix Memory Features (Part 1 of 2) |                                  |                                  |                                |  |  |  |  |

|----------------------------------------------------|----------------------------------|----------------------------------|--------------------------------|--|--|--|--|

| Memory Feature                                     | M512 RAM Block<br>(32 × 18 Bits) | M4K RAM Block<br>(128 × 36 Bits) | M-RAM Block<br>(4K × 144 Bits) |  |  |  |  |

| Maximum performance                                | (1)                              | (1)                              | (1)                            |  |  |  |  |

| True dual-port memory                              |                                  | <b>✓</b>                         | <b>✓</b>                       |  |  |  |  |

| Simple dual-port memory                            | ✓                                | ~                                | <b>✓</b>                       |  |  |  |  |

| Single-port memory                                 | ✓                                | ✓                                | ✓                              |  |  |  |  |

| Shift register                                     | <b>✓</b>                         | ✓                                |                                |  |  |  |  |

| ROM                                                | ✓                                | ✓                                | (2)                            |  |  |  |  |

| FIFO buffer                                        | ✓                                | ✓                                | ✓                              |  |  |  |  |

| Byte enable                                        |                                  | ✓                                | ✓                              |  |  |  |  |

| Parity bits                                        | ✓                                | ✓                                | ✓                              |  |  |  |  |

| Mixed clock mode                                   | ✓                                | ✓                                | ✓                              |  |  |  |  |

| Memory initialization                              | ✓                                | ✓                                |                                |  |  |  |  |

| Simple dual-port<br>memory mixed width<br>support  | <b>✓</b>                         | ~                                | ~                              |  |  |  |  |

| True dual-port memory mixed width support          |                                  | ~                                | ~                              |  |  |  |  |

| Power-up conditions                                | Outputs cleared                  | Outputs cleared                  | Outputs<br>unknown             |  |  |  |  |

| Register clears                                    | Input and output registers       | Input and output registers       | Output registers               |  |  |  |  |

| Mixed-port read-<br>during-write                   | Unknown<br>output/old data       | Unknown<br>output/old data       | Unknown output                 |  |  |  |  |

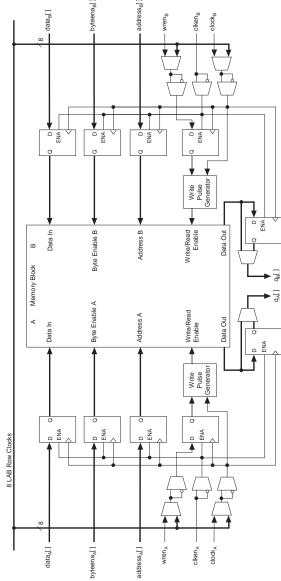

Figure 2–24. Independent Clock Mode Notes (1), (2)

Notes to Figure 2-24

- (1) All registers shown have asynchronous clear ports.

- (2) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

Table 2–13 shows the number of DSP blocks in each Stratix device.

| Table 2–13. DSP Blocks in Stratix Devices Notes (1), (2) |            |                            |                              |                              |  |  |  |  |

|----------------------------------------------------------|------------|----------------------------|------------------------------|------------------------------|--|--|--|--|

| Device                                                   | DSP Blocks | Total 9 × 9<br>Multipliers | Total 18 × 18<br>Multipliers | Total 36 × 36<br>Multipliers |  |  |  |  |

| EP1S10                                                   | 6          | 48                         | 24                           | 6                            |  |  |  |  |

| EP1S20                                                   | 10         | 80                         | 40                           | 10                           |  |  |  |  |

| EP1S25                                                   | 10         | 80                         | 40                           | 10                           |  |  |  |  |

| EP1S30                                                   | 12         | 96                         | 48                           | 12                           |  |  |  |  |

| EP1S40                                                   | 14         | 112                        | 56                           | 14                           |  |  |  |  |

| EP1S60                                                   | 18         | 144                        | 72                           | 18                           |  |  |  |  |

| EP1S80                                                   | 22         | 176                        | 88                           | 22                           |  |  |  |  |

#### *Notes to Table 2–13:*

- (1) Each device has either the number of  $9 \times 9$ -,  $18 \times 18$ -, or  $36 \times 36$ -bit multipliers shown. The total number of multipliers for each device is not the sum of all the multipliers.

- (2) The number of supported multiply functions shown is based on signed/signed or unsigned/unsigned implementations.

DSP block multipliers can optionally feed an adder/subtractor or accumulator within the block depending on the configuration. This makes routing to LEs easier, saves LE routing resources, and increases performance, because all connections and blocks are within the DSP block. Additionally, the DSP block input registers can efficiently implement shift registers for FIR filter applications.

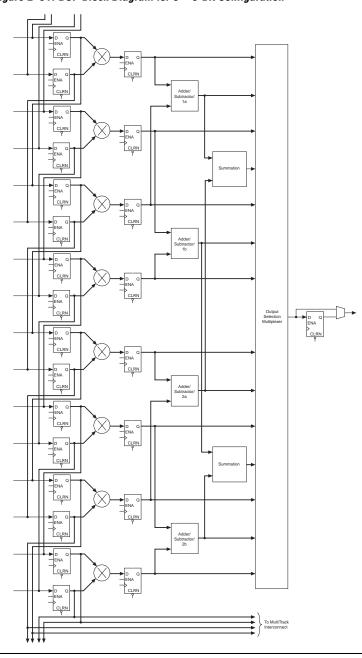

Figure 2–30 shows the top-level diagram of the DSP block configured for  $18 \times 18$ -bit multiplier mode. Figure 2–31 shows the  $9 \times 9$ -bit multiplier configuration of the DSP block.

Figure 2–31. DSP Block Diagram for  $9 \times 9$ -Bit Configuration

#### Output Selection Multiplexer

The outputs from the various elements of the adder/output block are routed through an output selection multiplexer. Based on the DSP block operational mode and user settings, the multiplexer selects whether the output from the multiplier, the adder/subtractor/accumulator, or summation block feeds to the output.

#### Output Registers

Optional output registers for the DSP block outputs are controlled by four sets of control signals: clock [3..0], aclr [3..0], and ena [3..0]. Output registers can be used in any mode.

#### **Modes of Operation**

The adder, subtractor, and accumulate functions of a DSP block have four modes of operation:

- Simple multiplier

- Multiply-accumulator

- Two-multipliers adder

- Four-multipliers adder

Each DSP block can only support one mode. Mixed modes in the same DSP block is not supported.

#### Simple Multiplier Mode

In simple multiplier mode, the DSP block drives the multiplier sub-block result directly to the output with or without an output register. Up to four  $18 \times 18$ -bit multipliers or eight  $9 \times 9$ -bit multipliers can drive their results directly out of one DSP block. See Figure 2–35.

*Note to Figure 2–42:*

(1) The corner fast PLLs can also be driven through the global or regional clock networks. The global or regional clock input to the fast PLL can be driven by an output from another PLL, a pin-driven global or regional clock, or internallygenerated global signals.

#### Regional Clock Network

There are four regional clock networks within each quadrant of the Stratix device that are driven by the same dedicated CLK[15..0] input pins or from PLL outputs. From a top view of the silicon, RCLK [0..3] are in the top left quadrant, RCLK[8..11] are in the top-right quadrant, RCLK[4..7] are in the bottom-left quadrant, and RCLK[12..15] are in the bottom-right quadrant. The regional clock networks only pertain to the quadrant they drive into. The regional clock networks provide the lowest clock delay and skew for logic contained within a single quadrant. RCLK cannot be driven by internal logic. The CLK clock pins symmetrically drive the RCLK networks within a particular quadrant, as shown in Figure 2–43. See Figures 2–50 and 2–51 for RCLK connections from PLLs and CLK pins.

| Table 2–22. Fast PLL Port I/O Standards (Part 2 of 2) |          |           |  |  |  |  |

|-------------------------------------------------------|----------|-----------|--|--|--|--|

| I/O Standard                                          | Input    |           |  |  |  |  |

| I/O Standard                                          | INCLK    | PLLENABLE |  |  |  |  |

| SSTL-2 Class II                                       | <b>✓</b> |           |  |  |  |  |

| SSTL-3 Class I                                        | ✓        |           |  |  |  |  |

| SSTL-3 Class II                                       | <b>✓</b> |           |  |  |  |  |

| AGP (1× and 2×)                                       |          |           |  |  |  |  |

| СТТ                                                   | <b>✓</b> |           |  |  |  |  |

Table 2–23 shows the performance on each of the fast PLL clock inputs when using LVDS, LVPECL, 3.3-V PCML, or HyperTransport technology.

| Table 2–23. LVDS Performance on Fast PLL Input                         |                 |  |  |  |  |

|------------------------------------------------------------------------|-----------------|--|--|--|--|

| Fast PLL Clock Input Maximum Input Frequency (MHz)                     |                 |  |  |  |  |

| CLK0, CLK2, CLK9, CLK11,<br>FPLL7CLK, FPLL8CLK, FPLL9CLK,<br>FPLL10CLK | 717 <i>(</i> 1) |  |  |  |  |

| CLK1, CLK3, CLK8, CLK10                                                | 645             |  |  |  |  |

*Note to Table 2–23:*

#### External Clock Outputs

Each fast PLL supports differential or single-ended outputs for source-synchronous transmitters or for general-purpose external clocks. There are no dedicated external clock output pins. Any I/O pin can be driven by the fast PLL global or regional outputs as an external output pin. The I/O standards supported by any particular bank determines what standards are possible for an external clock output driven by the fast PLL in that bank.

#### Phase Shifting

Stratix device fast PLLs have advanced clock shift capability that enables programmable phase shifts. You can enter a phase shift (in degrees or time units) for each PLL clock output port or for all outputs together in one shift. You can perform phase shifting in time units with a resolution range of 125 to 416.66 ps. This resolution is a function of the VCO period, with the finest step being equal to an eighth (×0.125) of the VCO period.

<sup>(1)</sup> See the chapter DC & Switching Characteristics of the Stratix Device Handbook, Volume 1 for more information.

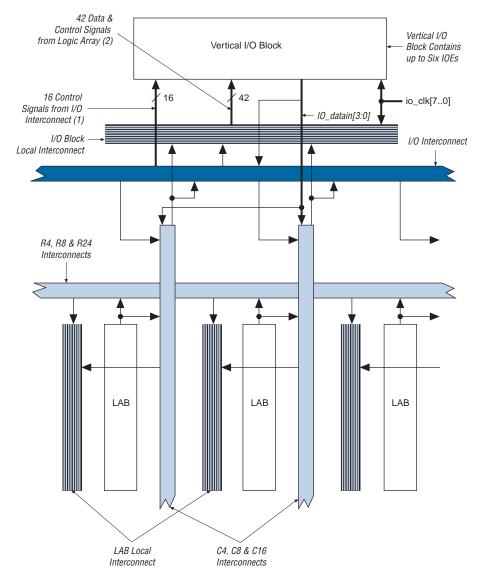

Figure 2-61. Column I/O Block Connection to the Interconnect

#### *Notes to Figure 2–61:*

- (1) The 16 control signals are composed of four output enables io\_boe[3..0], four clock enables io\_boe[3..0], four clocks io\_bclk[3..0], and four clear signals io\_bclr[3..0].

- (2) The 42 data and control signals consist of 12 data out lines; six lines each for DDR applications io\_dataouta[5..0] and io\_dataoutb[5..0], six output enables io\_coe[5..0], six input clock enables io\_cce\_in[5..0], six output clock enables io\_cce\_out[5..0], six clocks io\_cclk[5..0], and six clear signals io cclr[5..0].

I/O pin has an individual slew-rate control, allowing you to specify the slew rate on a pin-by-pin basis. The slew-rate control affects both the rising and falling edges.

#### **Bus Hold**

Each Stratix device I/O pin provides an optional bus-hold feature. The bus-hold circuitry can weakly hold the signal on an I/O pin at its last-driven state. Since the bus-hold feature holds the last-driven state of the pin until the next input signal is present, an external pull-up or pull-down resistor is not needed to hold a signal level when the bus is tri-stated.

Table 2–29 shows bus hold support for different pin types.

| Table 2–29. Bus Hold Support |          |  |  |  |

|------------------------------|----------|--|--|--|

| Pin Type                     | Bus Hold |  |  |  |

| I/O pins                     | ✓        |  |  |  |

| CLK[150]                     |          |  |  |  |

| CLK[0,1,2,3,8,9,10,11]       |          |  |  |  |

| FCLK                         | ~        |  |  |  |

| FPLL[710]CLK                 |          |  |  |  |

The bus-hold circuitry also pulls undriven pins away from the input threshold voltage where noise can cause unintended high-frequency switching. You can select this feature individually for each I/O pin. The bus-hold output drives no higher than  $V_{\rm CCIO}$  to prevent overdriving signals. If the bus-hold feature is enabled, the programmable pull-up option cannot be used. Disable the bus-hold feature when using opendrain outputs with the GTL+ I/O standard or when the I/O pin has been configured for differential signals.

The bus-hold circuitry uses a resistor with a nominal resistance ( $R_{BH}$ ) of approximately 7 k $\Omega$ to weakly pull the signal level to the last-driven state. See the DC & Switching Characteristics chapter of the Stratix Device Handbook, Volume 1 for the specific sustaining current driven through this resistor and overdrive current used to identify the next-driven input level. This information is provided for each  $V_{CCIO}$  voltage level.

The bus-hold circuitry is active only after configuration. When going into user mode, the bus-hold circuit captures the value on the pin present at the end of configuration.

| Table 2- | Table 2–37. EP1S10, EP1S20 & EP1S25 Device Differential Channels (Part 2 of 2) Note (1) |                 |          |                            |                  |       |       |       |  |

|----------|-----------------------------------------------------------------------------------------|-----------------|----------|----------------------------|------------------|-------|-------|-------|--|

|          |                                                                                         | Transmitter/    | Total    | Maximum<br>Speed<br>(Mbps) | Center Fast PLLs |       |       |       |  |

| Device   | ce Package Receiver                                                                     |                 | Channels |                            | PLL 1            | PLL 2 | PLL 3 | PLL 4 |  |

| EP1S25   | 672-pin FineLine BGA                                                                    | Transmitter (2) | 56       | 624 (4)                    | 14               | 14    | 14    | 14    |  |

|          | 672-pin BGA                                                                             |                 |          | 624 (3)                    | 28               | 28    | 28    | 28    |  |

|          |                                                                                         | Receiver        | 58       | 624 (4)                    | 14               | 15    | 15    | 14    |  |

|          |                                                                                         |                 |          | 624 (3)                    | 29               | 29    | 29    | 29    |  |

|          | 780-pin FineLine BGA                                                                    | Transmitter (2) | 70       | 840 (4)                    | 18               | 17    | 17    | 18    |  |

|          |                                                                                         |                 |          | 840 (3)                    | 35               | 35    | 35    | 35    |  |

|          |                                                                                         | Receiver        | 66       | 840 (4)                    | 17               | 16    | 16    | 17    |  |

|          |                                                                                         |                 |          | 840 (3)                    | 33               | 33    | 33    | 33    |  |

|          | 1,020-pin FineLine<br>BGA                                                               | Transmitter (2) | 78       | 840 (4)                    | 19               | 20    | 20    | 19    |  |

|          |                                                                                         |                 |          | 840 (3)                    | 39               | 39    | 39    | 39    |  |

|          |                                                                                         | Receiver        | 78       | 840 (4)                    | 19               | 20    | 20    | 19    |  |

|          |                                                                                         |                 |          | 840 (3)                    | 39               | 39    | 39    | 39    |  |

#### Notes to Table 2–37:

- (1) The first row for each transmitter or receiver reports the number of channels driven directly by the PLL. The second row below it shows the maximum channels a PLL can drive if cross bank channels are used from the adjacent center PLL. For example, in the 484-pin FineLine BGA EP1S10 device, PLL 1 can drive a maximum of five channels at 840 Mbps or a maximum of 10 channels at 840 Mbps. The Quartus II software may also merge receiver and transmitter PLLs when a receiver is driving a transmitter. In this case, one fast PLL can drive both the maximum numbers of receiver and transmitter channels.

- (2) The number of channels listed includes the transmitter clock output (tx\_outclock) channel. If the design requires a DDR clock, it can use an extra data channel.

- (3) These channels span across two I/O banks per side of the device. When a center PLL clocks channels in the opposite bank on the same side of the device it is called cross-bank PLL support. Both center PLLs can clock cross-bank channels simultaneously if, for example, PLL\_1 is clocking all receiver channels and PLL\_2 is clocking all transmitter channels. You cannot have two adjacent PLLs simultaneously clocking cross-bank receiver channels or two adjacent PLLs simultaneously clocking transmitter channels. Cross-bank allows for all receiver channels on one side of the device to be clocked on one clock while all transmitter channels on the device are clocked on the other center PLL. Crossbank PLLs are supported at full-speed, 840 Mbps. For wire-bond devices, the full-speed is 624 Mbps.

- (4) These values show the channels available for each PLL without crossing another bank.

When you span two I/O banks using cross-bank support, you can route only two load enable signals total between the PLLs. When you enable rx\_data\_align, you use both rxloadena and txloadena of a PLL. That leaves no loadena for the second PLL.

| Table 2-41.           | Table 2–41. EP1S80 Differential Channels (Part 2 of 2) Note (1) |                       |                 |                  |            |            |            |                           |            |            |            |

|-----------------------|-----------------------------------------------------------------|-----------------------|-----------------|------------------|------------|------------|------------|---------------------------|------------|------------|------------|

| Dankana               | Transmitter/                                                    | Total                 | Maximum         | Center Fast PLLs |            |            |            | Corner Fast PLLs (2), (3) |            |            |            |

| Package               | Receiver                                                        | Channels              | Speed<br>(Mbps) | PLL1             | PLL2       | PLL3       | PLL4       | PLL7                      | PLL8       | PLL9       | PLL10      |

| 1,508-pin<br>FineLine | Transmitter (4)                                                 | 80 (72)<br><i>(7)</i> | 840             | 10<br>(10)       | 10<br>(10) | 10<br>(10) | 10<br>(10) | 20<br>(8)                 | 20<br>(8)  | 20 (8)     | 20 (8)     |

| BGA                   |                                                                 |                       | 840 (5),(8)     | 20<br>(20)       | 20<br>(20) | 20<br>(20) | 20<br>(20) | 20<br>(8)                 | 20<br>(8)  | 20 (8)     | 20 (8)     |

|                       | Receiver                                                        | 80 (56)<br>(7)        | 840             | 20               | 20         | 20         | 20         | 10<br>(14)                | 10<br>(14) | 10<br>(14) | 10<br>(14) |

|                       |                                                                 |                       | 840 (5),(8)     | 40               | 40         | 40         | 40         | 10<br>(14)                | 10<br>(14) | 10<br>(14) | 10<br>(14) |

#### Notes to Tables 2–38 through 2–41:

- (1) The first row for each transmitter or receiver reports the number of channels driven directly by the PLL. The second row below it shows the maximum channels a PLL can drive if cross bank channels are used from the adjacent center PLL. For example, in the 780-pin FineLine BGA EP1S30 device, PLL 1 can drive a maximum of 18 transmitter channels at 840 Mbps or a maximum of 35 transmitter channels at 840 Mbps. The Quartus II software may also merge transmitter and receiver PLLs when a receiver is driving a transmitter. In this case, one fast PLL can drive both the maximum numbers of receiver and transmitter channels.

- (2) Some of the channels accessible by the center fast PLL and the channels accessible by the corner fast PLL overlap. Therefore, the total number of channels is not the addition of the number of channels accessible by PLLs 1, 2, 3, and 4 with the number of channels accessible by PLLs 7, 8, 9, and 10. For more information on which channels overlap, see the Stratix device pin-outs at www.altera.com.

- (3) The corner fast PLLs in this device support a data rate of 840 Mbps for channels labeled "high" speed in the device pin-outs at www.altera.com.

- (4) The numbers of channels listed include the transmitter clock output (tx\_outclock) channel. An extra data channel can be used if a DDR clock is needed.

- (5) These channels span across two I/O banks per side of the device. When a center PLL clocks channels in the opposite bank on the same side of the device it is called cross-bank PLL support. Both center PLLs can clock cross-bank channels simultaneously if say PLL\_1 is clocking all receiver channels and PLL\_2 is clocking all transmitter channels. You cannot have two adjacent PLLs simultaneously clocking cross-bank receiver channels or two adjacent PLLs simultaneously clocking transmitter channels. Cross-bank allows for all receiver channels on one side of the device to be clocked on one clock while all transmitter channels on the device are clocked on the other center PLL. Crossbank PLLs are supported at full-speed, 840 Mbps. For wire-bond devices, the full-speed is 624 Mbps.

- (6) PLLs 7, 8, 9, and 10 are not available in this device.

- (7) The number in parentheses is the number of slow-speed channels, guaranteed to operate at up to 462 Mbps. These channels are independent of the high-speed differential channels. For the location of these channels, see the device pin-outs at www.altera.com.

- (8) See the Stratix device pin-outs at www.altera.com. Channels marked "high" speed are 840 MBps and "low" speed channels are 462 MBps.

The high-speed differential I/O circuitry supports the following high speed I/O interconnect standards and applications:

- UTOPIA IV

- SPI-4 Phase 2 (POS-PHY Level 4)

- SFI-4

- 10G Ethernet XSBI

The Stratix device instruction register length is 10 bits and the USERCODE register length is 32 bits. Tables 3–2 and 3–3 show the boundary-scan register length and device IDCODE information for Stratix devices.

| Table 3–2. Stratix Boundary-Scan Register Length |       |  |  |  |  |

|--------------------------------------------------|-------|--|--|--|--|

| Device Boundary-Scan Register Lenç               |       |  |  |  |  |

| EP1S10                                           | 1,317 |  |  |  |  |

| EP1S20                                           | 1,797 |  |  |  |  |

| EP1S25                                           | 2,157 |  |  |  |  |

| EP1S30                                           | 2,253 |  |  |  |  |

| EP1S40                                           | 2,529 |  |  |  |  |

| EP1S60                                           | 3,129 |  |  |  |  |

| EP1S80                                           | 3,777 |  |  |  |  |

| Table 3–3. 32-Bit Stratix Device IDCODE |                      |                       |                                    |                 |  |  |  |  |

|-----------------------------------------|----------------------|-----------------------|------------------------------------|-----------------|--|--|--|--|

|                                         | IDCODE (32 Bits) (1) |                       |                                    |                 |  |  |  |  |

| Device                                  | Version (4 Bits)     | Part Number (16 Bits) | Manufacturer Identity<br>(11 Bits) | LSB (1 Bit) (2) |  |  |  |  |

| EP1S10                                  | 0000                 | 0010 0000 0000 0001   | 000 0110 1110                      | 1               |  |  |  |  |

| EP1S20                                  | 0000                 | 0010 0000 0000 0010   | 000 0110 1110                      | 1               |  |  |  |  |

| EP1S25                                  | 0000                 | 0010 0000 0000 0011   | 000 0110 1110                      | 1               |  |  |  |  |

| EP1S30                                  | 0000                 | 0010 0000 0000 0100   | 000 0110 1110                      | 1               |  |  |  |  |

| EP1S40                                  | 0000                 | 0010 0000 0000 0101   | 000 0110 1110                      | 1               |  |  |  |  |

| EP1S60                                  | 0000                 | 0010 0000 0000 0110   | 000 0110 1110                      | 1               |  |  |  |  |

| EP1S80                                  | 0000                 | 0010 0000 0000 0111   | 000 0110 1110                      | 1               |  |  |  |  |

Notes to Tables 3-2 and 3-3:

- (1) The most significant bit (MSB) is on the left.

- (2) The IDCODE's least significant bit (LSB) is always 1.

#### **External Timing Parameters**

External timing parameters are specified by device density and speed grade. Figure 4–4 shows the pin-to-pin timing model for bidirectional IOE pin timing. All registers are within the IOE.

OE Register PRN D t<sub>INSU</sub> Dedicated  $t_{INH}$ Clock t<sub>OUTCO</sub> CLRN  $t_{XZ}$  $t_{ZX}$ Output Register PRN Bidirectional Pin CLRN Input Register PRN CLRN

Figure 4-4. External Timing in Stratix Devices

All external timing parameters reported in this section are defined with respect to the dedicated clock pin as the starting point. All external I/O timing parameters shown are for 3.3-V LVTTL I/O standard with the 24-mA current strength and fast slew rate. For external I/O timing using standards other than LVTTL or for different current strengths, use the I/O standard input and output delay adders in Tables 4–103 through 4–108.

| Table 4–71. EP1S25 External I/O Timing on Row Pins Using Regional Clock Networks |                |       |                |       |         |         |         |       |      |

|----------------------------------------------------------------------------------|----------------|-------|----------------|-------|---------|---------|---------|-------|------|

|                                                                                  | -5 Speed Grade |       | -6 Speed Grade |       | -7 Spee | d Grade | -8 Spee | Ī     |      |

| Parameter                                                                        | Min            | Max   | Min            | Max   | Min     | Max     | Min     | Max   | Unit |

| t <sub>INSU</sub>                                                                | 1.793          |       | 1.927          |       | 2.182   |         | 2.542   |       | ns   |

| t <sub>INH</sub>                                                                 | 0.000          |       | 0.000          |       | 0.000   |         | 0.000   |       | ns   |

| t <sub>OUTCO</sub>                                                               | 2.759          | 5.457 | 2.759          | 5.835 | 2.759   | 6.346   | 2.759   | 7.024 | ns   |

| t <sub>XZ</sub>                                                                  | 2.786          | 5.511 | 2.786          | 5.891 | 2.786   | 6.414   | 2.786   | 7.106 | ns   |

| t <sub>ZX</sub>                                                                  | 2.786          | 5.511 | 2.786          | 5.891 | 2.786   | 6.414   | 2.786   | 7.106 | ns   |

| t <sub>INSUPLL</sub>                                                             | 1.169          |       | 1.221          |       | 1.373   |         | 1.600   |       | ns   |

| t <sub>INHPLL</sub>                                                              | 0.000          |       | 0.000          |       | 0.000   |         | 0.000   |       | ns   |

| t <sub>OUTCOPLL</sub>                                                            | 1.375          | 2.861 | 1.375          | 2.999 | 1.375   | 3.082   | 1.375   | 3.174 | ns   |

| t <sub>XZPLL</sub>                                                               | 1.402          | 2.915 | 1.402          | 3.055 | 1.402   | 3.150   | 1.402   | 3.256 | ns   |

| t <sub>ZXPLL</sub>                                                               | 1.402          | 2.915 | 1.402          | 3.055 | 1.402   | 3.150   | 1.402   | 3.256 | ns   |

| Table 4–72. EP1S25 External I/O Timing on Row Pins Using Global Clock Networks |         |         |                |       |         |         |         |       |      |

|--------------------------------------------------------------------------------|---------|---------|----------------|-------|---------|---------|---------|-------|------|

| Davamatav                                                                      | -5 Spee | d Grade | -6 Speed Grade |       | -7 Spee | d Grade | -8 Spee | 11!4  |      |

| Parameter                                                                      | Min     | Max     | Min            | Max   | Min     | Max     | Min     | Max   | Unit |

| t <sub>INSU</sub>                                                              | 1.665   |         | 1.779          |       | 2.012   |         | 2.372   |       | ns   |

| t <sub>INH</sub>                                                               | 0.000   |         | 0.000          |       | 0.000   |         | 0.000   |       | ns   |

| t <sub>OUTCO</sub>                                                             | 2.834   | 5.585   | 2.834          | 5.983 | 2.834   | 6.516   | 2.834   | 7.194 | ns   |

| t <sub>XZ</sub>                                                                | 2.861   | 5.639   | 2.861          | 6.039 | 2.861   | 6.584   | 2.861   | 7.276 | ns   |

| t <sub>ZX</sub>                                                                | 2.861   | 5.639   | 2.861          | 6.039 | 2.861   | 6.584   | 2.861   | 7.276 | ns   |

| t <sub>INSUPLL</sub>                                                           | 1.538   |         | 1.606          |       | 1.816   |         | 2.121   |       | ns   |

| t <sub>INHPLL</sub>                                                            | 0.000   |         | 0.000          |       | 0.000   |         | 0.000   |       | ns   |

| t <sub>OUTCOPLL</sub>                                                          | 1.164   | 2.492   | 1.164          | 2.614 | 1.164   | 2.639   | 1.164   | 2.653 | ns   |

| t <sub>XZPLL</sub>                                                             | 1.191   | 2.546   | 1.191          | 2.670 | 1.191   | 2.707   | 1.191   | 2.735 | ns   |

| t <sub>ZXPLL</sub>                                                             | 1.191   | 2.546   | 1.191          | 2.670 | 1.191   | 2.707   | 1.191   | 2.735 | ns   |

Tables 4–85 through 4–90 show the external timing parameters on column and row pins for EP1S60 devices.

| Table 4–85. EP1S60 External I/O Timing on Column Pins Using Fast Regional Clock Networks Note (1) |         |         |                |       |                |       |                |     |      |  |

|---------------------------------------------------------------------------------------------------|---------|---------|----------------|-------|----------------|-------|----------------|-----|------|--|

|                                                                                                   | -5 Spee | d Grade | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |     |      |  |

| Parameter                                                                                         | Min     | Max     | Min            | Max   | Min            | Max   | Min            | Max | Unit |  |

| t <sub>INSU</sub>                                                                                 | 3.029   |         | 3.277          |       | 3.733          |       | NA             |     | ns   |  |

| t <sub>INH</sub>                                                                                  | 0.000   |         | 0.000          |       | 0.000          |       | NA             |     | ns   |  |

| t <sub>OUTCO</sub>                                                                                | 2.446   | 4.871   | 2.446          | 5.215 | 2.446          | 5.685 | NA             | NA  | ns   |  |

| t <sub>XZ</sub>                                                                                   | 2.386   | 4.745   | 2.386          | 5.083 | 2.386          | 5.561 | NA             | NA  | ns   |  |

| t <sub>ZX</sub>                                                                                   | 2.386   | 4.745   | 2.386          | 5.083 | 2.386          | 5.561 | NA             | NA  | ns   |  |

| Table 4–86. EP1S60 External I/O Timing on Column Pins Using Regional Clock Networks Note (1) |         |         |         |                |       |         |         |     |      |

|----------------------------------------------------------------------------------------------|---------|---------|---------|----------------|-------|---------|---------|-----|------|

| Davamatav                                                                                    | -5 Spee | d Grade | -6 Spee | -6 Speed Grade |       | d Grade | -8 Spee |     |      |

| Parameter                                                                                    | Min     | Max     | Min     | Max            | Min   | Max     | Min     | Max | Unit |

| t <sub>INSU</sub>                                                                            | 2.491   |         | 2.691   |                | 3.060 |         | NA      |     | ns   |

| t <sub>INH</sub>                                                                             | 0.000   |         | 0.000   |                | 0.000 |         | NA      |     | ns   |

| t <sub>OUTCO</sub>                                                                           | 2.767   | 5.409   | 2.767   | 5.801          | 2.767 | 6.358   | NA      | NA  | ns   |

| t <sub>XZ</sub>                                                                              | 2.707   | 5.283   | 2.707   | 5.669          | 2.707 | 6.234   | NA      | NA  | ns   |

| t <sub>ZX</sub>                                                                              | 2.707   | 5.283   | 2.707   | 5.669          | 2.707 | 6.234   | NA      | NA  | ns   |

| t <sub>INSUPLL</sub>                                                                         | 1.233   |         | 1.270   |                | 1.438 |         | NA      |     | ns   |

| t <sub>INHPLL</sub>                                                                          | 0.000   |         | 0.000   |                | 0.000 |         | NA      |     | ns   |

| t <sub>OUTCOPLL</sub>                                                                        | 1.078   | 2.278   | 1.078   | 2.395          | 1.078 | 2.428   | NA      | NA  | ns   |

| t <sub>XZPLL</sub>                                                                           | 1.018   | 2.152   | 1.018   | 2.263          | 1.018 | 2.304   | NA      | NA  | ns   |

| t <sub>ZXPLL</sub>                                                                           | 1.018   | 2.152   | 1.018   | 2.263          | 1.018 | 2.304   | NA      | NA  | ns   |

| Symbol                                             |                              | -5 Speed Grade |     | -6 Speed Grade |     | -7 Speed Grade |     |     | -8 Speed Grade |       |     | l   |       |      |

|----------------------------------------------------|------------------------------|----------------|-----|----------------|-----|----------------|-----|-----|----------------|-------|-----|-----|-------|------|

|                                                    | Conditions                   | Min            | Тур | Max            | Min | Тур            | Max | Min | Тур            | Max   | Min | Тур | Max   | Unit |

| f <sub>HSCLK</sub> (Clock<br>frequency)            | W = 4 to 30<br>(Serdes used) | 10             |     | 100            | 10  |                | 100 | 10  |                | 77.75 | 10  |     | 77.75 | MHz  |

| (PCML)<br>f <sub>HSCLK</sub> = f <sub>HSDR</sub> / | W = 2 (Serdes bypass)        | 50             |     | 200            | 50  |                | 200 | 50  |                | 150   | 50  |     | 150   | MHz  |

| W                                                  | W = 2 (Serdes used)          | 150            |     | 200            | 150 |                | 200 | 150 |                | 155.5 | 150 |     | 155.5 | MHz  |

|                                                    | W = 1 (Serdes bypass)        | 100            |     | 250            | 100 |                | 250 | 100 |                | 200   | 100 |     | 200   | MHz  |

|                                                    | W = 1 (Serdes used)          | 300            |     | 400            | 300 |                | 400 | 300 |                | 311   | 300 |     | 311   | MHz  |

| f <sub>HSDR</sub> Device                           | J= 10                        | 300            |     | 400            | 300 |                | 400 | 300 |                | 311   | 300 |     | 311   | Mbps |

| operation                                          | J = 8                        | 300            |     | 400            | 300 |                | 400 | 300 |                | 311   | 300 |     | 311   | Mbps |

| (PCML)                                             | J = 7                        | 300            |     | 400            | 300 |                | 400 | 300 |                | 311   | 300 |     | 311   | Mbps |

|                                                    | J = 4                        | 300            |     | 400            | 300 |                | 400 | 300 |                | 311   | 300 |     | 311   | Mbps |

|                                                    | J = 2                        | 100            |     | 400            | 100 |                | 400 | 100 |                | 300   | 100 |     | 300   | Mbps |

|                                                    | J = 1                        | 100            |     | 250            | 100 |                | 250 | 100 |                | 200   | 100 |     | 200   | Mbps |

| TCCS                                               | All                          |                |     | 200            |     |                | 200 |     |                | 300   |     |     | 300   | ps   |

| Fast Regional Clock External I/O Timing            | I                                                           |

|----------------------------------------------------|-------------------------------------------------------------|

| Parameters 4–49                                    | I/O                                                         |

| Global Clock External I/O Timing                   | Standards                                                   |

| Parameters 4–50 Regional Clock External I/O Timing | 1.5-V 4-14, 4-15                                            |

| Parameters 4–50                                    | I/O Specifications 4–4                                      |

| EP1S60 Devices                                     | 1.8-V                                                       |

| Column Pin                                         | I/O Specifications 4–4                                      |

| Fast Regional Clock External I/O Timing            | 2.5-V                                                       |

| Parameters 4–51                                    | I/O Specifications 4–3                                      |

| Global Clock External I/O Timing                   | 3.3-V 4–13                                                  |

| Parameters 4–52                                    | LVDS I/O Specifications 4–6                                 |

| Regional Clock External I/O Timing                 | PCI Specifications 4–9                                      |

| Parameters 4–51                                    | PCML Specifications 4–8                                     |

| M-RAM                                              | Advanced I/O Standard Support 2–122                         |

| Interface Locations 2–38                           | Column I/O Block Connection to the                          |

| Row Pin                                            | Interconnect 2–107                                          |

| Fast Regional Clock External I/O Timing            | Column Pin                                                  |

| Parameters 4–52                                    | Input Delay Adders 4–66                                     |

| Global Clock External I/O Timing                   | Control Signal Selection per IOE 2–109                      |

| Parameters 4–53                                    | CTT I/O Specifications 4–16                                 |

| Regional Clock External I/O Timing                 | Differential LVDS Input On-Chip                             |

| Parameters 4–53                                    | Termination 2–128                                           |

| EP1S80 Devices                                     | External I/O Delay Parameters 4–66                          |

| Column Pin                                         | GTL+ I/O Specifications 4–10<br>High-Speed Differential I/O |

| Fast Regional Clock External I/O Timing            | Support 2–130                                               |

| Parameters 4–54                                    | HyperTransport Technology                                   |

| Global Clock External I/O Timing                   | Specifications 4–9                                          |

| Parameters 4–55                                    | I/O Banks 2–125                                             |

| Regional Clock External I/O Timing                 | I/O Structure 2–104                                         |

| Parameters 4–54                                    | I/O Support by Bank 2–126                                   |

| Global Clock External I/O Timing                   | IOE Structure 2–105                                         |

| Parameters 4–56                                    | LVCMOS Specifications 4–3                                   |

| Row Pin                                            | LVDS Performance on Fast PLL                                |

| Fast Regional Clock External I/O Timing            | Input 2–103                                                 |

| Parameters 4–55                                    | LVPECL Specifications 4–8                                   |

| Regional Clock External I/O Timing                 | LVTTL Specifications 4–3                                    |

| Parameters 4–56                                    | MultiVolt I/O Interface 2–129                               |

|                                                    | MultiVolt I/O Support 2–130                                 |

| H                                                  | Output Delay Adders for Fast Slew Rate                      |

| HSTL                                               | on Column Pins 4–68                                         |

| Class I Specifications 4–14, 4–15                  | Output Delay Adders for Fast Slew Rate                      |

| Class II Specifications 4–14, 4–15                 | on Row Pins 4–69                                            |

| Ciass II Specifications 4-14, 4-15                 | Output Delay Adders for Slow Slew Rate                      |

|                                                    | on Column Pins 4–70                                         |

|                                                    | Package Options & I/O Pin Counts 1–4                        |

|                                                    | Receiver Input Waveforms for Differential                   |

Index-4 Altera Corporation