Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Obsolete                                                  |

| Number of LABs/CLBs            | 2566                                                      |

| Number of Logic Elements/Cells | 25660                                                     |

| Total RAM Bits                 | 1944576                                                   |

| Number of I/O                  | 706                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.425V ~ 1.575V                                           |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 1020-BBGA                                                 |

| Supplier Device Package        | 1020-FBGA (33x33)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s25f1020c7n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Features**

The Stratix family offers the following features:

- 10,570 to 79,040 LEs; see Table 1–1

- Up to 7,427,520 RAM bits (928,440 bytes) available without reducing logic resources

- TriMatrix<sup>™</sup> memory consisting of three RAM block sizes to implement true dual-port memory and first-in first-out (FIFO) buffers

- High-speed DSP blocks provide dedicated implementation of multipliers (faster than 300 MHz), multiply-accumulate functions, and finite impulse response (FIR) filters

- Up to 16 global clocks with 22 clocking resources per device region

- Up to 12 PLLs (four enhanced PLLs and eight fast PLLs) per device provide spread spectrum, programmable bandwidth, clock switchover, real-time PLL reconfiguration, and advanced multiplication and phase shifting

- Support for numerous single-ended and differential I/O standards

- High-speed differential I/O support on up to 116 channels with up to 80 channels optimized for 840 megabits per second (Mbps)

- Support for high-speed networking and communications bus standards including RapidIO, UTOPIA IV, CSIX, HyperTransport™ technology, 10G Ethernet XSBI, SPI-4 Phase 2 (POS-PHY Level 4), and SFI-4

- Differential on-chip termination support for LVDS

- Support for high-speed external memory, including zero bus turnaround (ZBT) SRAM, quad data rate (QDR and QDRII) SRAM, double data rate (DDR) SDRAM, DDR fast cycle RAM (FCRAM), and single data rate (SDR) SDRAM

- Support for 66-MHz PCI (64 and 32 bit) in -6 and faster speed-grade devices, support for 33-MHz PCI (64 and 32 bit) in -8 and faster speed-grade devices

- Support for 133-MHz PCI-X 1.0 in -5 speed-grade devices

- Support for 100-MHz PCI-X 1.0 in -6 and faster speed-grade devices

- Support for 66-MHz PCI-X 1.0 in -7 speed-grade devices

- Support for multiple intellectual property megafunctions from Altera MegaCore<sup>®</sup> functions and Altera Megafunction Partners Program (AMPP<sup>SM</sup>) megafunctions

- Support for remote configuration updates

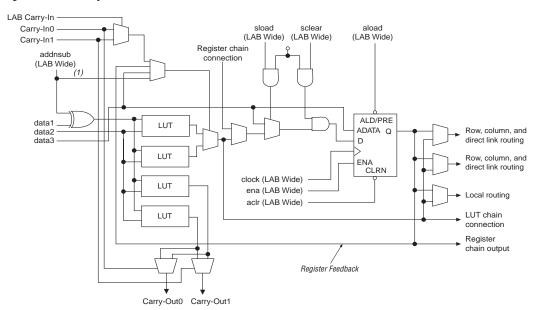

Figure 2-7. LE in Dynamic Arithmetic Mode

*Note to Figure 2–7:*

(1) The addnsub signal is tied to the carry input for the first LE of a carry chain only.

#### Carry-Select Chain

The carry-select chain provides a very fast carry-select function between LEs in arithmetic mode. The carry-select chain uses the redundant carry calculation to increase the speed of carry functions. The LE is configured to calculate outputs for a possible carry-in of 1 and carry-in of 0 in parallel. The carry-in0 and carry-in1 signals from a lower-order bit feed forward into the higher-order bit via the parallel carry chain and feed into both the LUT and the next portion of the carry chain. Carry-select chains can begin in any LE within an LAB.

The speed advantage of the carry-select chain is in the parallel precomputation of carry chains. Since the LAB carry-in selects the precomputed carry chain, not every LE is in the critical path. Only the propagation delay between LAB carry-in generation (LE 5 and LE 10) are now part of the critical path. This feature allows the Stratix architecture to implement high-speed counters, adders, multipliers, parity functions, and comparators of arbitrary width.

Figure 2–8 shows the carry-select circuitry in an LAB for a 10-bit full adder. One portion of the LUT generates the sum of two bits using the input signals and the appropriate carry-in bit; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used for accumulator functions. Another portion of the LUT generates carry-out bits. An LAB-wide carry in bit selects which chain is used for the addition of given inputs. The carry-in signal for each chain, carry-in0 or carry-in1, selects the carry-out to carry forward to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it is fed to local, row, or column interconnects.

The Quartus II Compiler automatically creates carry chain logic during design processing, or you can create it manually during design entry. Parameterized functions such as LPM functions automatically take advantage of carry chains for the appropriate functions.

The Quartus II Compiler creates carry chains longer than 10 LEs by linking LABs together automatically. For enhanced fitting, a long carry chain runs vertically allowing fast horizontal connections to  $TriMatrix^{TM}$  memory and DSP blocks. A carry chain can continue as far as a full column.

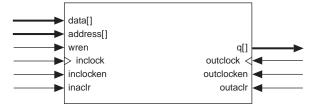

In addition to true dual-port memory, the memory blocks support simple dual-port and single-port RAM. Simple dual-port memory supports a simultaneous read and write and can either read old data before the write occurs or just read the don't care bits. Single-port memory supports non-simultaneous reads and writes, but the q[] port will output the data once it has been written to the memory (if the outputs are not registered) or after the next rising edge of the clock (if the outputs are registered). For more information, see Chapter 2, TriMatrix Embedded Memory Blocks in Stratix & Stratix GX Devices of the *Stratix Device Handbook, Volume 2*. Figure 2–13 shows these different RAM memory port configurations for TriMatrix memory.

Figure 2–13. Simple Dual-Port & Single-Port Memory Configurations

# data[] rdaddress[] wraddress[] rden wren q[] inclock outclock inclocken outclocken inaclr outaclr

#### Single-Port Memory (1)

Simple Dual-Port Memory

Note to Figure 2-13:

Two single-port memory blocks can be implemented in a single M4K block as long as each of the two independent block sizes is equal to or less than half of the M4K block size.

The memory blocks also enable mixed-width data ports for reading and writing to the RAM ports in dual-port RAM configuration. For example, the memory block can be written in  $\times 1$  mode at port A and read out in  $\times 16$  mode from port B.

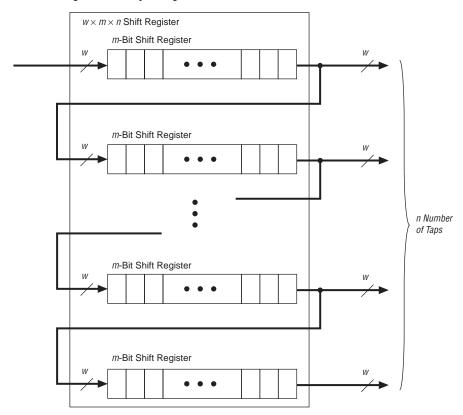

Figure 2-14. Shift Register Memory Configuration

## **Memory Block Size**

TriMatrix memory provides three different memory sizes for efficient application support. The large number of M512 blocks are ideal for designs with many shallow first-in first-out (FIFO) buffers. M4K blocks provide additional resources for channelized functions that do not require large amounts of storage. The M-RAM blocks provide a large single block of RAM ideal for data packet storage. The different-sized blocks allow Stratix devices to efficiently support variable-sized memory in designs.

The Quartus II software automatically partitions the user-defined memory into the embedded memory blocks using the most efficient size combinations. You can also manually assign the memory to a specific block size or a mixture of block sizes.

| Table 2–9. M-RAM Block Configurations (True Dual-Port) |          |          |          |          |  |  |

|--------------------------------------------------------|----------|----------|----------|----------|--|--|

| Dovt A                                                 |          | Po       | rt B     |          |  |  |

| Port A                                                 | 64K × 9  | 32K × 18 | 16K × 36 | 8K × 72  |  |  |

| 64K × 9                                                | <b>✓</b> | ✓        | ✓        | <b>✓</b> |  |  |

| 32K × 18                                               | ✓        | ✓        | ✓        | <b>✓</b> |  |  |

| 16K × 36                                               | <b>✓</b> | ✓        | ✓        | ✓        |  |  |

| 8K × 72                                                | ✓        | ✓        | ✓        | <b>✓</b> |  |  |

The read and write operation of the memory is controlled by the WREN signal, which sets the ports into either read or write modes. There is no separate read enable (RE) signal.

Writing into RAM is controlled by both the WREN and byte enable (byteena) signals for each port. The default value for the byteena signal is high, in which case writing is controlled only by the WREN signal. The byte enables are available for the ×18, ×36, and ×72 modes. In the ×144 simple dual-port mode, the two sets of byteena signals (byteena\_a and byteena\_b) are combined to form the necessary 16 byte enables. Tables 2–10 and 2–11 summarize the byte selection.

| Table 2–10. Byte Enable for M-RAM Blocks Notes (1), (2) |            |            |            |  |  |  |  |

|---------------------------------------------------------|------------|------------|------------|--|--|--|--|

| byteena[30]                                             | datain ×18 | datain ×36 | datain ×72 |  |  |  |  |

| [0] = 1                                                 | [80]       | [80]       | [80]       |  |  |  |  |

| [1] = 1                                                 | [179]      | [179]      | [179]      |  |  |  |  |

| [2] = 1                                                 | _          | [2618]     | [2618]     |  |  |  |  |

| [3] = 1                                                 | -          | [3527]     | [3527]     |  |  |  |  |

| [4] = 1                                                 | _          | _          | [4436]     |  |  |  |  |

| [5] = 1                                                 | _          | _          | [5345]     |  |  |  |  |

| [6] = 1                                                 | _          | _          | [6254]     |  |  |  |  |

| [7] = 1                                                 | _          | _          | [7163]     |  |  |  |  |

### **Input/Output Clock Mode**

Input/output clock mode can be implemented for both the true and simple dual-port memory modes. On each of the two ports, A or B, one clock controls all registers for inputs into the memory block: data input, wren, and address. The other clock controls the block's data output registers. Each memory block port, A or B, also supports independent clock enables and asynchronous clear signals for input and output registers. Figures 2–25 and 2–26 show the memory block in input/output clock mode.

#### Pipeline/Post Multiply Register

The output of  $9 \times 9$ - or  $18 \times 18$ -bit multipliers can optionally feed a register to pipeline multiply-accumulate and multiply-add/subtract functions. For  $36 \times 36$ -bit multipliers, this register will pipeline the multiplier function.

#### **Adder/Output Blocks**

The result of the multiplier sub-blocks are sent to the adder/output block which consist of an adder/subtractor/accumulator unit, summation unit, output select multiplexer, and output registers. The results are used to configure the adder/output block as a pure output, accumulator, a simple two-multiplier adder, four-multiplier adder, or final stage of the 36-bit multiplier. You can configure the adder/output block to use output registers in any mode, and must use output registers for the accumulator. The system cannot use adder/output blocks independently of the multiplier. Figure 2–34 shows the adder and output stages.

The DSP block is divided into eight block units that interface with eight LAB rows on the left and right. Each block unit can be considered half of an 18 × 18-bit multiplier sub-block with 18 inputs and 18 outputs. A local interconnect region is associated with each DSP block. Like an LAB, this interconnect region can be fed with 10 direct link interconnects from the LAB to the left or right of the DSP block in the same row. All row and column routing resources can access the DSP block's local interconnect region. The outputs also work similarly to LAB outputs as well. Nine outputs from the DSP block can drive to the left LAB through direct link interconnects and nine can drive to the right LAB though direct link interconnects. All 18 outputs can drive to all types of row and column routing. Outputs can drive right- or left-column routing. Figures 2–40 and 2–41 show the DSP block interfaces to LAB rows.

DSP Block OA[17..0] MultiTrack MultiTrack Interconnect \ Interconnect A1[17..0] OB[17..0] B1[17..0] OC[17..0] A2[17..0] OD[17..0] B2[17..0] OE[17..0] A3[17..0] OF[17..0] B3[17..0] OG[17..0] A4[17..0] OH[17..0] ►B4[17..0]

Figure 2-40. DSP Block Interconnect Interface

| Table 2–20. I/O Standards Supported for Enhanced PLL Pins (Part 2 of 2) |          |          |           |          |  |  |

|-------------------------------------------------------------------------|----------|----------|-----------|----------|--|--|

| I/O Standard                                                            |          | Input    |           | Output   |  |  |

| I/O Standard                                                            | INCLK    | FBIN     | PLLENABLE | EXTCLK   |  |  |

| 1.5-V HSTL Class II                                                     | <b>✓</b> | <b>✓</b> |           | ✓        |  |  |

| 1.8-V HSTL Class I                                                      | <b>✓</b> | <b>✓</b> |           | ✓        |  |  |

| 1.8-V HSTL Class II                                                     | <b>✓</b> | <b>✓</b> |           | ✓        |  |  |

| SSTL-18 Class I                                                         | <b>✓</b> | <b>✓</b> |           | ✓        |  |  |

| SSTL-18 Class II                                                        | <b>✓</b> | <b>✓</b> |           | ✓        |  |  |

| SSTL-2 Class I                                                          | <b>✓</b> | <b>✓</b> |           | ✓        |  |  |

| SSTL-2 Class II                                                         | <b>✓</b> | <b>✓</b> |           | ✓        |  |  |

| SSTL-3 Class I                                                          | <b>✓</b> | <b>✓</b> |           | ✓        |  |  |

| SSTL-3 Class II                                                         | <b>✓</b> | ✓        |           | ✓        |  |  |

| AGP (1× and 2×)                                                         | <b>✓</b> | ✓        |           | <b>✓</b> |  |  |

| СТТ                                                                     | <b>✓</b> | ✓        |           | ✓        |  |  |

Enhanced PLLs 11 and 12 support one single-ended output each (see Figure 2–56). These outputs do not have their own VCC and GND signals. Therefore, to minimize jitter, do not place switching I/O pins next to this output pin.

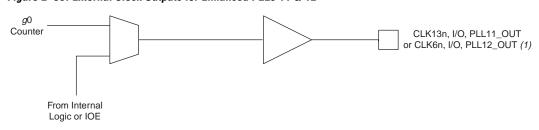

Figure 2-56. External Clock Outputs for Enhanced PLLs 11 & 12

Note to Figure 2-56:

(1) For PLL 11, this pin is CLK13n; for PLL 12 this pin is CLK7n.

Stratix devices can drive any enhanced PLL driven through the global clock or regional clock network to any general I/O pin as an external output clock. The jitter on the output clock is not guaranteed for these cases.

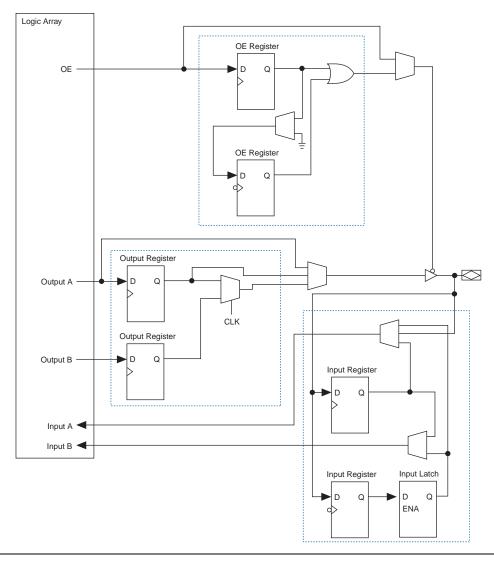

Figure 2-59. Stratix IOE Structure

The IOEs are located in I/O blocks around the periphery of the Stratix device. There are up to four IOEs per row I/O block and six IOEs per column I/O block. The row I/O blocks drive row, column, or direct link interconnects. The column I/O blocks drive column interconnects. Figure 2–60 shows how a row I/O block connects to the logic array. Figure 2–61 shows how a column I/O block connects to the logic array.

and/or output enable registers. A programmable delay exists to increase the  $t_{ZX}$  delay to the output pin, which is required for ZBT interfaces. Table 2–24 shows the programmable delays for Stratix devices.

| Table 2–24. Stratix Programmable Delay Chain |                                              |  |  |  |  |  |

|----------------------------------------------|----------------------------------------------|--|--|--|--|--|

| Programmable Delays                          | Quartus II Logic Option                      |  |  |  |  |  |

| Input pin to logic array delay               | Decrease input delay to internal cells       |  |  |  |  |  |

| Input pin to input register delay            | Decrease input delay to input register       |  |  |  |  |  |

| Output pin delay                             | Increase delay to output pin                 |  |  |  |  |  |

| Output enable register t <sub>CO</sub> delay | Increase delay to output enable pin          |  |  |  |  |  |

| Output t <sub>ZX</sub> delay                 | Increase t <sub>ZX</sub> delay to output pin |  |  |  |  |  |

| Output clock enable delay                    | Increase output clock enable delay           |  |  |  |  |  |

| Input clock enable delay                     | Increase input clock enable delay            |  |  |  |  |  |

| Logic array to output register delay         | Decrease input delay to output register      |  |  |  |  |  |

| Output enable clock enable delay             | Increase output enable clock enable delay    |  |  |  |  |  |

The IOE registers in Stratix devices share the same source for clear or preset. You can program preset or clear for each individual IOE. You can also program the registers to power up high or low after configuration is complete. If programmed to power up low, an asynchronous clear can control the registers. If programmed to power up high, an asynchronous preset can control the registers. This feature prevents the inadvertent activation of another device's active-low input upon power-up. If one register in an IOE uses a preset or clear signal then all registers in the IOE must use that same signal if they require preset or clear. Additionally a synchronous reset signal is available for the IOE registers.

#### Double-Data Rate I/O Pins

Stratix devices have six registers in the IOE, which support DDR interfacing by clocking data on both positive and negative clock edges. The IOEs in Stratix devices support DDR inputs, DDR outputs, and bidirectional DDR modes.

When using the IOE for DDR inputs, the two input registers clock double rate input data on alternating edges. An input latch is also used within the IOE for DDR input acquisition. The latch holds the data that is present during the clock high times. This allows both bits of data to be synchronous with the same clock edge (either rising or falling). Figure 2–65 shows an IOE configured for DDR input. Figure 2–66 shows the DDR input timing diagram.

Tables 2–25 and 2–26 show the performance specification for DDR SDRAM, RLDRAM II, QDR SRAM, QDRII SRAM, and ZBT SRAM interfaces in EP1S10 through EP1S40 devices and in EP1S60 and EP1S80 devices. The DDR SDRAM and QDR SRAM numbers in Table 2–25 have been verified with hardware characterization with third-party DDR SDRAM and QDR SRAM devices over temperature and voltage extremes.

| Table 2–25. External RAM Support in EP1\$10 through EP1\$40 Devices |                 |                          |           |               |               |               |               |               |

|---------------------------------------------------------------------|-----------------|--------------------------|-----------|---------------|---------------|---------------|---------------|---------------|

|                                                                     |                 | Maximum Clock Rate (MHz) |           |               |               |               |               |               |

| DDR Memory Type                                                     | I/O<br>Standard | -5 Speed<br>Grade        | -6 Spee   | d Grade       | -7 Spec       | ed Grade      | -8 Spee       | d Grade       |

|                                                                     |                 | Flip-Chip                | Flip-Chip | Wire-<br>Bond | Flip-<br>Chip | Wire-<br>Bond | Flip-<br>Chip | Wire-<br>Bond |

| DDR SDRAM (1), (2)                                                  | SSTL-2          | 200                      | 167       | 133           | 133           | 100           | 100           | 100           |

| DDR SDRAM - side banks (2), (3), (4)                                | SSTL-2          | 150                      | 133       | 110           | 133           | 100           | 100           | 100           |

| RLDRAM II (4)                                                       | 1.8-V HSTL      | 200                      | (5)       | (5)           | (5)           | (5)           | (5)           | (5)           |

| QDR SRAM (6)                                                        | 1.5-V HSTL      | 167                      | 167       | 133           | 133           | 100           | 100           | 100           |

| QDRII SRAM (6)                                                      | 1.5-V HSTL      | 200                      | 167       | 133           | 133           | 100           | 100           | 100           |

| ZBT SRAM (7)                                                        | LVTTL           | 200                      | 200       | 200           | 167           | 167           | 133           | 133           |

#### Notes to Table 2-25:

- (1) These maximum clock rates apply if the Stratix device uses DQS phase-shift circuitry to interface with DDR SDRAM. DQS phase-shift circuitry is only available in the top and bottom I/O banks (I/O banks 3, 4, 7, and 8).

- (2) For more information on DDR SDRAM, see AN 342: Interfacing DDR SDRAM with Stratix & Stratix GX Devices.

- (3) DDR SDRAM is supported on the Stratix device side I/O banks (I/O banks 1, 2, 5, and 6) without dedicated DQS phase-shift circuitry. The read DQS signal is ignored in this mode.

- (4) These performance specifications are preliminary.

- (5) This device does not support RLDRAM II.

- (6) For more information on QDR or QDRII SRAM, see AN 349: QDR SRAM Controller Reference Design for Stratix & Stratix GX Devices.

- (7) For more information on ZBT SRAM, see AN 329: ZBT SRAM Controller Reference Design for Stratix & Stratix GX Devices.

The only way you can use the rx\_data\_align is if one of the following is true:

- The receiver PLL is only clocking receive channels (no resources for the transmitter)

- If all channels can fit in one I/O bank

| Table 2-38            | Table 2–38. EP1S30 Differential Channels Note (1) |                 |                 |           |           |           |           |        |         |        |         |    |

|-----------------------|---------------------------------------------------|-----------------|-----------------|-----------|-----------|-----------|-----------|--------|---------|--------|---------|----|

|                       | Transmitter                                       | Total           | Maximum         | C         | enter F   | ast PLI   | _S        | Corn   | er Fast | PLLs ( | 2), (3) |    |

| Package               | /Receiver                                         | Channels        | Speed<br>(Mbps) | PLL1      | PLL2      | PLL3      | PLL4      | PLL7   | PLL8    | PLL9   | PLL10   |    |

| 780-pin               | Transmitter                                       | 70              | 840             | 18        | 17        | 17        | 18        | (6)    | (6)     | (6)    | (6)     |    |

| FineLine<br>BGA       | (4)                                               |                 | 840 (5)         | 35        | 35        | 35        | 35        | (6)    | (6)     | (6)    | (6)     |    |

|                       | Receiver                                          | 66              | 840             | 17        | 16        | 16        | 17        | (6)    | (6)     | (6)    | (6)     |    |

|                       |                                                   |                 | 840 (5)         | 33        | 33        | 33        | 33        | (6)    | (6)     | (6)    | (6)     |    |

| 956-pin               | Transmitter                                       | oin Transmitter | 80              | 840       | 19        | 20        | 20        | 19     | 20      | 20     | 20      | 20 |

| BGA                   | (4)                                               |                 | 840 (5)         | 39        | 39        | 39        | 39        | 20     | 20      | 20     | 20      |    |

|                       | Receiver                                          | 80              | 840             | 20        | 20        | 20        | 20        | 19     | 20      | 20     | 19      |    |

|                       |                                                   |                 | 840 (5)         | 40        | 40        | 40        | 40        | 19     | 20      | 20     | 19      |    |

| 1,020-pin<br>FineLine | Transmitter (4)                                   | 80 (2) (7)      | 840             | 19<br>(1) | 20        | 20        | 19<br>(1) | 20     | 20      | 20     | 20      |    |

| BGA                   |                                                   |                 | 840 (5),(8)     | 39<br>(1) | 39<br>(1) | 39<br>(1) | 39<br>(1) | 20     | 20      | 20     | 20      |    |

|                       | Receiver                                          | 80 (2) (7)      | 840             | 20        | 20        | 20        | 20        | 19 (1) | 20      | 20     | 19 (1)  |    |

|                       |                                                   |                 | 840 (5),(8)     | 40        | 40        | 40        | 40        | 19 (1) | 20      | 20     | 19 (1)  |    |

| Table 2-39      | Table 2–39. EP1S40 Differential Channels (Part 1 of 2) Note (1) |       |                 |      |         |         |      |      |         |      |          |

|-----------------|-----------------------------------------------------------------|-------|-----------------|------|---------|---------|------|------|---------|------|----------|

|                 | Transmitter/                                                    | Total | Maximum         | C    | enter F | ast PLI | -S   | Corn | er Fast | PLLs | (2), (3) |

| Package         | ackage Receiver Cha                                             |       | Speed<br>(Mbps) | PLL1 | PLL2    | PLL3    | PLL4 | PLL7 | PLL8    | PLL9 | PLL10    |

| 780-pin         | Transmitter                                                     | 68    | 840             | 18   | 16      | 16      | 18   | (6)  | (6)     | (6)  | (6)      |

| FineLine<br>BGA | (4)                                                             |       | 840 (5)         | 34   | 34      | 34      | 34   | (6)  | (6)     | (6)  | (6)      |

|                 | Receiver                                                        | 66    | 840             | 17   | 16      | 16      | 17   | (6)  | (6)     | (6)  | (6)      |

|                 |                                                                 |       | 840 (5)         | 33   | 33      | 33      | 33   | (6)  | (6)     | (6)  | (6)      |

| Symbol            | Parameter                 | Conditions                  | Minimum                    | Typical | Maximum                     | Unit |

|-------------------|---------------------------|-----------------------------|----------------------------|---------|-----------------------------|------|

| V <sub>CCIO</sub> | Output supply voltage     |                             | 3.0                        |         | 3.6                         | V    |

| V <sub>IH</sub>   | High-level input voltage  |                             | 0.5 ×<br>V <sub>CCIO</sub> |         | V <sub>CCIO</sub> + 0.5     | V    |

| V <sub>IL</sub>   | Low-level input voltage   |                             | -0.5                       |         | 0.35 ×<br>V <sub>CCIO</sub> | V    |

| V <sub>IPU</sub>  | Input pull-up voltage     |                             | 0.7 ×<br>V <sub>CCIO</sub> |         |                             | V    |

| V <sub>OH</sub>   | High-level output voltage | $I_{OUT} = -500 \mu A$      | 0.9 ×<br>V <sub>CCIO</sub> |         |                             | V    |

| V <sub>OL</sub>   | Low-level output voltage  | I <sub>OUT</sub> = 1,500 μA |                            |         | 0.1 ×<br>V <sub>CCIO</sub>  | V    |

| Table 4–16.      | Table 4–16. GTL+ I/O Specifications |                             |                        |         |                        |      |  |  |  |

|------------------|-------------------------------------|-----------------------------|------------------------|---------|------------------------|------|--|--|--|

| Symbol           | Parameter                           | Conditions                  | Minimum                | Typical | Maximum                | Unit |  |  |  |

| $V_{TT}$         | Termination voltage                 |                             | 1.35                   | 1.5     | 1.65                   | V    |  |  |  |

| V <sub>REF</sub> | Reference voltage                   |                             | 0.88                   | 1.0     | 1.12                   | V    |  |  |  |

| V <sub>IH</sub>  | High-level input voltage            |                             | V <sub>REF</sub> + 0.1 |         |                        | V    |  |  |  |

| V <sub>IL</sub>  | Low-level input voltage             |                             |                        |         | V <sub>REF</sub> - 0.1 | V    |  |  |  |

| V <sub>OL</sub>  | Low-level output voltage            | I <sub>OL</sub> = 34 mA (3) |                        |         | 0.65                   | V    |  |  |  |

| Table 4–17. GTL I/O Specifications |                          |                             |                         |         |                         |      |  |

|------------------------------------|--------------------------|-----------------------------|-------------------------|---------|-------------------------|------|--|

| Symbol                             | Parameter                | Conditions                  | Minimum                 | Typical | Maximum                 | Unit |  |

| $V_{TT}$                           | Termination voltage      |                             | 1.14                    | 1.2     | 1.26                    | V    |  |

| $V_{REF}$                          | Reference voltage        |                             | 0.74                    | 0.8     | 0.86                    | V    |  |

| V <sub>IH</sub>                    | High-level input voltage |                             | V <sub>REF</sub> + 0.05 |         |                         | V    |  |

| V <sub>IL</sub>                    | Low-level input voltage  |                             |                         |         | V <sub>REF</sub> – 0.05 | V    |  |

| V <sub>OL</sub>                    | Low-level output voltage | I <sub>OL</sub> = 40 mA (3) |                         |         | 0.4                     | V    |  |

| Table 4–41. M4<br>2 of 2) | Table 4–41. M4K Block Internal Timing Microparameter Descriptions (Part 2 of 2)                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Symbol                    | Parameter                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| t <sub>M4KDATAAH</sub>    | A port data hold time after clock                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| t <sub>M4KADDRASU</sub>   | A port address setup time before clock                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| t <sub>M4KADDRAH</sub>    | A port address hold time after clock                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| t <sub>M4KDATABSU</sub>   | B port data setup time before clock                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| t <sub>M4KDATABH</sub>    | B port data hold time after clock                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| t <sub>M4KADDRBSU</sub>   | B port address setup time before clock                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| t <sub>M4KADDRBH</sub>    | B port address hold time after clock                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| t <sub>M4KDATACO1</sub>   | Clock-to-output delay when using output registers                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| t <sub>M4KDATACO2</sub>   | Clock-to-output delay without output registers                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| t <sub>M4KCLKHL</sub>     | Register minimum clock high or low time. This is a limit on the min time for the clock on the registers in these blocks. The actual performance is dependent upon the internal point-to-point delays in the blocks and may give slower performance as shown inTable 4–36 on page 4–20 and as reported by the timing analyzer in the Quartus II software. |  |  |  |  |  |

Minimum clear pulse width

$t_{\mathsf{M4KCLR}}$

| Table 4–42. M-RAM Block Internal Timing Microparameter Descriptions (Part 1 of 2) |                                              |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------|----------------------------------------------|--|--|--|--|--|--|--|

| Symbol                                                                            | Parameter                                    |  |  |  |  |  |  |  |

| t <sub>MRAMRC</sub>                                                               | Synchronous read cycle time                  |  |  |  |  |  |  |  |

| t <sub>MRAMWC</sub>                                                               | Synchronous write cycle time                 |  |  |  |  |  |  |  |

| t <sub>MRAMWERESU</sub>                                                           | Write or read enable setup time before clock |  |  |  |  |  |  |  |

| t <sub>MRAMWEREH</sub>                                                            | Write or read enable hold time after clock   |  |  |  |  |  |  |  |

| t <sub>MRAMCLKENSU</sub>                                                          | Clock enable setup time before clock         |  |  |  |  |  |  |  |

| t <sub>MRAMCLKENH</sub>                                                           | Clock enable hold time after clock           |  |  |  |  |  |  |  |

| t <sub>MRAMBESU</sub>                                                             | Byte enable setup time before clock          |  |  |  |  |  |  |  |

| t <sub>MRAMBEH</sub>                                                              | Byte enable hold time after clock            |  |  |  |  |  |  |  |

| t <sub>MRAMDATAASU</sub>                                                          | A port data setup time before clock          |  |  |  |  |  |  |  |

| t <sub>MRAMDATAAH</sub>                                                           | A port data hold time after clock            |  |  |  |  |  |  |  |

| t <sub>MRAMADDRASU</sub>                                                          | A port address setup time before clock       |  |  |  |  |  |  |  |

| t <sub>MRAMADDRAH</sub>                                                           | A port address hold time after clock         |  |  |  |  |  |  |  |

| t <sub>MRAMDATABSU</sub>                                                          | B port setup time before clock               |  |  |  |  |  |  |  |

| Table 4–47. DSP Block Internal Timing Microparameters (Part 2 of 2) |       |       |       |       |       |       |       |        |      |  |

|---------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--------|------|--|

| Symbol                                                              | -5    |       | -6    |       | -     | 7     | -     | 11:4   |      |  |

|                                                                     | Min   | Max   | Min   | Max   | Min   | Max   | Min   | Max    | Unit |  |

| t <sub>PIPE2OUTREG2ADD</sub>                                        |       | 2,002 |       | 2,203 |       | 2,533 |       | 2,980  | ps   |  |

| t <sub>PIPE2OUTREG4ADD</sub>                                        |       | 2,899 |       | 3,189 |       | 3,667 |       | 4,314  | ps   |  |

| t <sub>PD9</sub>                                                    |       | 3,709 |       | 4,081 |       | 4,692 |       | 5,520  | ps   |  |

| t <sub>PD18</sub>                                                   |       | 4,795 |       | 5,275 |       | 6,065 |       | 7,135  | ps   |  |

| t <sub>PD36</sub>                                                   |       | 7,495 |       | 8,245 |       | 9,481 |       | 11,154 | ps   |  |

| t <sub>CLR</sub>                                                    | 450   |       | 500   |       | 575   |       | 676   |        | ps   |  |

| t <sub>CLKHL</sub>                                                  | 1,350 |       | 1,500 |       | 1,724 |       | 2,029 |        | ps   |  |

| Table 4–48. M512 Block Internal Timing Microparameters |       |       |       |       |       |       |       |       |      |

|--------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Symbol                                                 | -     | -5    |       | -6    |       | 7     | -     |       |      |

|                                                        | Min   | Max   | Min   | Max   | Min   | Max   | Min   | Max   | Unit |

| t <sub>M512RC</sub>                                    |       | 3,340 |       | 3,816 |       | 4,387 |       | 5,162 | ps   |

| t <sub>M512WC</sub>                                    |       | 3,138 |       | 3,590 |       | 4,128 |       | 4,860 | ps   |

| t <sub>M512WERESU</sub>                                | 110   |       | 123   |       | 141   |       | 166   |       | ps   |

| t <sub>M512WEREH</sub>                                 | 34    |       | 38    |       | 43    |       | 51    |       | ps   |

| t <sub>M512CLKENSU</sub>                               | 215   |       | 215   |       | 247   |       | 290   |       | ps   |

| t <sub>M512CLKENH</sub>                                | -70   |       | -70   |       | -81   |       | -95   |       | ps   |

| t <sub>M512DATASU</sub>                                | 110   |       | 123   |       | 141   |       | 166   |       | ps   |

| t <sub>M512DATAH</sub>                                 | 34    |       | 38    |       | 43    |       | 51    |       | ps   |

| t <sub>M512WADDRSU</sub>                               | 110   |       | 123   |       | 141   |       | 166   |       | ps   |

| t <sub>M512WADDRH</sub>                                | 34    |       | 38    |       | 43    |       | 51    |       | ps   |

| t <sub>M512RADDRSU</sub>                               | 110   |       | 123   |       | 141   |       | 166   |       | ps   |

| t <sub>M512RADDRH</sub>                                | 34    |       | 38    |       | 43    |       | 51    |       | ps   |

| t <sub>M512DATACO1</sub>                               |       | 424   |       | 472   |       | 541   |       | 637   | ps   |

| t <sub>M512DATACO2</sub>                               |       | 3,366 |       | 3,846 |       | 4,421 |       | 5,203 | ps   |

| t <sub>M512CLKHL</sub>                                 | 1,000 |       | 1,111 |       | 1,190 |       | 1,400 |       | ps   |

| t <sub>M512CLR</sub>                                   | 170   |       | 189   |       | 217   |       | 255   |       | ps   |

#### **External Timing Parameters**

External timing parameters are specified by device density and speed grade. Figure 4–4 shows the pin-to-pin timing model for bidirectional IOE pin timing. All registers are within the IOE.

OE Register PRN D t<sub>INSU</sub> Dedicated  $t_{INH}$ Clock t<sub>OUTCO</sub> CLRN  $t_{XZ}$  $t_{ZX}$ Output Register PRN Bidirectional Pin CLRN Input Register PRN CLRN

Figure 4-4. External Timing in Stratix Devices

All external timing parameters reported in this section are defined with respect to the dedicated clock pin as the starting point. All external I/O timing parameters shown are for 3.3-V LVTTL I/O standard with the 24-mA current strength and fast slew rate. For external I/O timing using standards other than LVTTL or for different current strengths, use the I/O standard input and output delay adders in Tables 4–103 through 4–108.

Table 4–122. Stratix Maximum Output Clock Rate for PLL[5, 6, 11, 12] Pins in Wire-Bond Packages (Part 1 of 2)

| I/O Standard                        | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |  |  |

|-------------------------------------|-------------------|-------------------|-------------------|------|--|--|

| LVTTL                               | 175               | 150               | 150               | MHz  |  |  |

| 2.5 V                               | 175               | 150               | 150               | MHz  |  |  |

| 1.8 V                               | 175               | 150               | 150               | MHz  |  |  |

| 1.5 V                               | 175               | 150               | 150               | MHz  |  |  |

| LVCMOS                              | 175               | 150               | 150               | MHz  |  |  |

| GTL                                 | 125               | 100               | 100               | MHz  |  |  |

| GTL+                                | 125               | 100               | 100               | MHz  |  |  |

| SSTL-3 Class I                      | 110               | 90                | 90                | MHz  |  |  |

| SSTL-3 Class II                     | 133               | 125               | 125               | MHz  |  |  |

| SSTL-2 Class I                      | 166               | 133               | 133               | MHz  |  |  |

| SSTL-2 Class II                     | 133               | 100               | 100               | MHz  |  |  |

| SSTL-18 Class I                     | 110               | 100               | 100               | MHz  |  |  |

| SSTL-18 Class II                    | 110               | 100               | 100               | MHz  |  |  |

| 1.5-V HSTL Class I                  | 167               | 167               | 167               | MHz  |  |  |

| 1.5-V HSTL Class II                 | 167               | 133               | 133               | MHz  |  |  |

| 1.8-V HSTL Class I                  | 167               | 167               | 167               | MHz  |  |  |

| 1.8-V HSTL Class II                 | 167               | 133               | 133               | MHz  |  |  |

| 3.3-V PCI                           | 167               | 167               | 167               | MHz  |  |  |

| 3.3-V PCI-X 1.0                     | 167               | 133               | 133               | MHz  |  |  |

| Compact PCI                         | 175               | 150               | 150               | MHz  |  |  |

| AGP 1×                              | 175               | 150               | 150               | MHz  |  |  |

| AGP 2×                              | 175               | 150               | 150               | MHz  |  |  |

| СТТ                                 | 125               | 100               | 100               | MHz  |  |  |

| Differential 1.5-V HSTL<br>C1       | 167               | 133               | 133               | MHz  |  |  |

| Differential 1.8-V HSTL<br>Class I  | 167               | 167               | 167               | MHz  |  |  |

| Differential 1.8-V HSTL<br>Class II | 167               | 133               | 133               | MHz  |  |  |

| Differential SSTL-2 (1)             | 110               | 100               | 100               | MHz  |  |  |

| LVPECL (2)                          | 311               | 275               | 275               | MHz  |  |  |

| PCML (2)                            | 250               | 200               | 200               | MHz  |  |  |

| Symbol                                      | 0                            | -6 Speed Grade |     |       | -7 Speed Grade |     |       | -8 Speed Grade |     |       |      |

|---------------------------------------------|------------------------------|----------------|-----|-------|----------------|-----|-------|----------------|-----|-------|------|

|                                             | Conditions                   | Min            | Тур | Max   | Min            | Тур | Max   | Min            | Тур | Max   | Unit |

| f <sub>HSCLK</sub> (Clock                   | W = 4 to 30 (Serdes used)    | 10             |     | 156   | 10             |     | 115.5 | 10             |     | 115.5 | MHz  |

| frequency)<br>(LVDS,LVPECL,                 | W = 2 (Serdes bypass)        | 50             |     | 231   | 50             |     | 231   | 50             |     | 231   | MHz  |

| HyperTransport                              | W = 2 (Serdes used)          | 150            |     | 312   | 150            |     | 231   | 150            |     | 231   | MHz  |

| technology)                                 | W = 1 (Serdes bypass)        | 100            |     | 311   | 100            |     | 270   | 100            |     | 270   | MHz  |

| $f_{HSCLK} = f_{HSDR} / W$                  | W = 1 (Serdes used)          | 300            |     | 624   | 300            |     | 462   | 300            |     | 462   | MHz  |

| f <sub>HSDR</sub> Device operation,         | J = 10                       | 300            |     | 624   | 300            |     | 462   | 300            |     | 462   | Mbps |

| (LVDS,LVPECL,<br>HyperTransport             | J = 8                        | 300            |     | 624   | 300            |     | 462   | 300            |     | 462   | Mbps |

| technology)                                 | J = 7                        | 300            |     | 624   | 300            |     | 462   | 300            |     | 462   | Mbps |

| <i>G77</i>                                  | J = 4                        | 300            |     | 624   | 300            |     | 462   | 300            |     | 462   | Mbps |

|                                             | J = 2                        | 100            |     | 462   | 100            |     | 462   | 100            |     | 462   | Mbps |

|                                             | J = 1 (LVDS and LVPECL only) | 100            |     | 311   | 100            |     | 270   | 100            |     | 270   | Mbps |

| f <sub>HSCLK</sub> (Clock                   | W = 4 to 30 (Serdes used)    | 10             |     | 77.75 |                |     |       |                |     |       | MHz  |

| frequency)<br>(PCML)                        | W = 2 (Serdes bypass)        | 50             |     | 150   | 50             |     | 77.5  | 50             |     | 77.5  | MHz  |

| f <sub>HSCLK</sub> = f <sub>HSDR</sub> / W  | W = 2 (Serdes used)          | 150            |     | 155.5 |                |     |       |                |     |       | MHz  |

|                                             | W = 1 (Serdes bypass)        | 100            |     | 200   | 100            |     | 155   | 100            |     | 155   | MHz  |

|                                             | W = 1 (Serdes used)          | 300            |     | 311   |                |     |       |                |     |       | MHz  |

| Device operation,  f <sub>HSDR</sub> (PCML) | J = 10                       | 300            |     | 311   |                |     |       |                |     |       | Mbps |

|                                             | J = 8                        | 300            |     | 311   |                |     |       |                |     |       | Mbps |

|                                             | J = 7                        | 300            |     | 311   |                |     |       |                |     |       | Mbps |

|                                             | J = 4                        | 300            |     | 311   |                |     |       |                |     |       | Mbps |

|                                             | J = 2                        | 100            |     | 300   | 100            |     | 155   | 100            |     | 155   | Mbps |

|                                             | J = 1                        | 100            |     | 200   | 100            |     | 155   | 100            |     | 155   | Mbps |

| TCCS                                        | All                          |                |     | 400   |                |     | 400   |                |     | 400   | ps   |

High-Speed I/O Specification