Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 2566                                                    |

| Number of Logic Elements/Cells | 25660                                                   |

| Total RAM Bits                 | 1944576                                                 |

| Number of I/O                  | 473                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                         |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 672-BBGA                                                |

| Supplier Device Package        | 672-FBGA (27x27)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s25f672c6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Typographic Conventions

This document uses the typographic conventions shown below.

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial<br>Capital Letters   | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                                                                                              |

| bold type                                   | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: f <sub>MAX</sub> , \qdesigns directory, d: drive, chiptrip.gdf file.                                                                         |

| Italic Type with Initial Capital<br>Letters | Document titles are shown in italic type with initial capital letters. Example: AN 75: High-Speed Board Designs.                                                                                                                                                                                                        |

| Italic type                                 | Internal timing parameters and variables are shown in italic type. Examples: $t_{PlA}$ , $n+1$ .                                                                                                                                                                                                                        |

|                                             | Variable names are enclosed in angle brackets (< >) and shown in italic type. Example: <file name="">, <pre><pre><pre></pre></pre></pre></file>                                                                                                                                                                         |

| Initial Capital Letters                     | Keyboard keys and menu names are shown with initial capital letters. Examples: Delete key, the Options menu.                                                                                                                                                                                                            |

| "Subheading Title"                          | References to sections within a document and titles of on-line help topics are shown in quotation marks. Example: "Typographic Conventions."                                                                                                                                                                            |

| Courier type                                | Signal and port names are shown in lowercase Courier type. Examples: $\mathtt{data1}$ , $\mathtt{tdi}$ , $\mathtt{input}$ . Active-low signals are denoted by suffix $\mathtt{n}$ , $\mathtt{e.g.}$ , $\mathtt{resetn}$ .                                                                                               |

|                                             | Anything that must be typed exactly as it appears is shown in Courier type. For example: c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an actual file, such as a Report File, references to parts of files (e.g., the AHDL keyword SUBDESIGN), as well as logic function names (e.g., TRI) are shown in Courier. |

| 1., 2., 3., and<br>a., b., c., etc.         | Numbered steps are used in a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                                                                                                                                                        |

| • •                                         | Bullets are used in a list of items when the sequence of the items is not important.                                                                                                                                                                                                                                    |

| ✓                                           | The checkmark indicates a procedure that consists of one step only.                                                                                                                                                                                                                                                     |

|                                             | The hand points to information that requires special attention.                                                                                                                                                                                                                                                         |

| 4                                           | The angled arrow indicates you should press the Enter key.                                                                                                                                                                                                                                                              |

|                                             | The feet direct you to more information on a particular topic.                                                                                                                                                                                                                                                          |

x Altera Corporation

Stratix devices are available in space-saving FineLine BGA® and ball-grid array (BGA) packages (see Tables 1–3 through 1–5). All Stratix devices support vertical migration within the same package (for example, you can migrate between the EP1S10, EP1S20, and EP1S25 devices in the 672-pin BGA package). Vertical migration means that you can migrate to devices whose dedicated pins, configuration pins, and power pins are the same for a given package across device densities. For I/O pin migration across densities, you must cross-reference the available I/O pins using the device pin-outs for all planned densities of a given package type to identify which I/O pins are migrational. The Quartus® II software can automatically cross reference and place all pins except differential pins for migration when given a device migration list. You must use the pin-outs for each device to verify the differential placement migration. A future version of the Quartus II software will support differential pin migration.

| Table 1-3. | Table 1–3. Stratix Package Options & I/O Pin Counts |                |                            |                            |                            |                              |                              |  |  |  |  |  |

|------------|-----------------------------------------------------|----------------|----------------------------|----------------------------|----------------------------|------------------------------|------------------------------|--|--|--|--|--|

| Device     | 672-Pin<br>BGA                                      | 956-Pin<br>BGA | 484-Pin<br>FineLine<br>BGA | 672-Pin<br>FineLine<br>BGA | 780-Pin<br>FineLine<br>BGA | 1,020-Pin<br>FineLine<br>BGA | 1,508-Pin<br>FineLine<br>BGA |  |  |  |  |  |

| EP1S10     | 345                                                 |                | 335                        | 345                        | 426                        |                              |                              |  |  |  |  |  |

| EP1S20     | 426                                                 |                | 361                        | 426                        | 586                        |                              |                              |  |  |  |  |  |

| EP1S25     | 473                                                 |                |                            | 473                        | 597                        | 706                          |                              |  |  |  |  |  |

| EP1S30     |                                                     | 683            |                            |                            | 597                        | 726                          |                              |  |  |  |  |  |

| EP1S40     |                                                     | 683            |                            |                            | 615                        | 773                          | 822                          |  |  |  |  |  |

| EP1S60     |                                                     | 683            |                            |                            |                            | 773                          | 1,022                        |  |  |  |  |  |

| EP1S80     |                                                     | 683            |                            |                            |                            | 773                          | 1,203                        |  |  |  |  |  |

#### Note to Table 1-3:

<sup>(1)</sup> All I/O pin counts include 20 dedicated clock input pins (clk [15..0] p, clk0n, clk2n, clk9n, and clk11n) that can be used for data inputs.

| Table 1–4. Stratix BGA Package Sizes |         |         |  |  |  |  |  |

|--------------------------------------|---------|---------|--|--|--|--|--|

| Dimension                            | 672 Pin | 956 Pin |  |  |  |  |  |

| Pitch (mm)                           | 1.27    | 1.27    |  |  |  |  |  |

| Area (mm²)                           | 1,225   | 1,600   |  |  |  |  |  |

| Length × width (mm × mm)             | 35 × 35 | 40 × 40 |  |  |  |  |  |

With the LAB-wide addnsub control signal, a single LE can implement a one-bit adder and subtractor. This saves LE resources and improves performance for logic functions such as DSP correlators and signed multipliers that alternate between addition and subtraction depending on data.

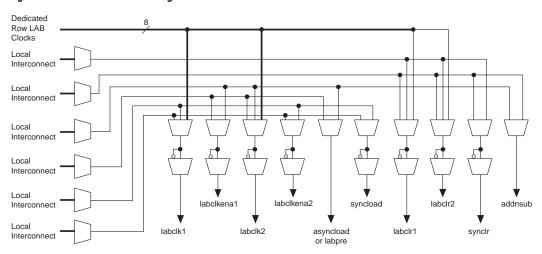

The LAB row clocks [7..0] and LAB local interconnect generate the LAB-wide control signals. The MultiTrack $^{\text{IM}}$  interconnect's inherent low skew allows clock and control signal distribution in addition to data. Figure 2–4 shows the LAB control signal generation circuit.

Figure 2-4. LAB-Wide Control Signals

### **Logic Elements**

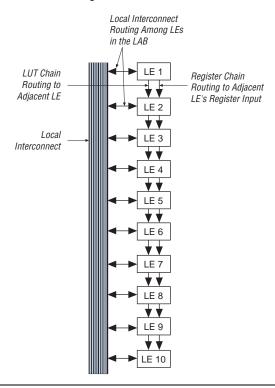

The smallest unit of logic in the Stratix architecture, the LE, is compact and provides advanced features with efficient logic utilization. Each LE contains a four-input LUT, which is a function generator that can implement any function of four variables. In addition, each LE contains a programmable register and carry chain with carry select capability. A single LE also supports dynamic single bit addition or subtraction mode selectable by an LAB-wide control signal. Each LE drives all types of interconnects: local, row, column, LUT chain, register chain, and direct link interconnects. See Figure 2–5.

Figure 2-10. LUT Chain & Register Chain Interconnects

The C4 interconnects span four LABs, M512, or M4K blocks up or down from a source LAB. Every LAB has its own set of C4 interconnects to drive either up or down. Figure 2–11 shows the C4 interconnect connections from an LAB in a column. The C4 interconnects can drive and be driven by all types of architecture blocks, including DSP blocks, TriMatrix memory blocks, and vertical IOEs. For LAB interconnection, a primary LAB or its LAB neighbor can drive a given C4 interconnect. C4 interconnects can drive each other to extend their range as well as drive row interconnects for column-to-column connections.

Table 2–2 shows the Stratix device's routing scheme.

| Table 2–2. Strat            | ix De       | vice F         | Routin             | ng Scl                   | heme            |                 |                  |                 |                 |                  |          |                |               |             |            |            |          |

|-----------------------------|-------------|----------------|--------------------|--------------------------|-----------------|-----------------|------------------|-----------------|-----------------|------------------|----------|----------------|---------------|-------------|------------|------------|----------|

|                             | Destination |                |                    |                          |                 |                 |                  |                 |                 |                  |          |                |               |             |            |            |          |

| Source                      | LUT Chain   | Register Chain | Local Interconnect | Direct Link Interconnect | R4 Interconnect | R8 Interconnect | R24 Interconnect | C4 Interconnect | C8 Interconnect | C16 Interconnect | ILE .    | M512 RAM Block | M4K RAM Block | M-RAM Block | DSP Blocks | Column 10E | Row IOE  |

| LUT Chain                   |             |                |                    |                          |                 |                 |                  |                 |                 |                  | >        |                |               |             |            |            |          |

| Register Chain              |             |                |                    |                          |                 |                 |                  |                 |                 |                  | <b>\</b> |                |               |             |            |            |          |

| Local<br>Interconnect       |             |                |                    |                          |                 |                 |                  |                 |                 |                  | <b>✓</b> | <b>✓</b>       | <b>✓</b>      | <b>✓</b>    | <b>✓</b>   | <b>✓</b>   | <b>\</b> |

| Direct Link<br>Interconnect |             |                | <b>✓</b>           |                          |                 |                 |                  |                 |                 |                  |          |                |               |             |            |            |          |

| R4 Interconnect             |             |                | <b>✓</b>           |                          | <b>✓</b>        |                 | <b>✓</b>         | <b>✓</b>        |                 | <b>✓</b>         |          |                |               |             |            |            |          |

| R8 Interconnect             |             |                | <b>✓</b>           |                          |                 | <b>✓</b>        |                  |                 | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| R24<br>Interconnect         |             |                |                    |                          | <b>✓</b>        |                 | <b>~</b>         | <b>✓</b>        |                 | <b>✓</b>         |          |                |               |             |            |            |          |

| C4 Interconnect             |             |                | <b>✓</b>           |                          | <b>✓</b>        |                 |                  | <b>✓</b>        |                 |                  |          |                |               |             |            |            |          |

| C8 Interconnect             |             |                | <b>✓</b>           |                          |                 | <b>✓</b>        |                  |                 | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| C16<br>Interconnect         |             |                |                    |                          | <b>✓</b>        |                 | <b>\</b>         | <b>\</b>        |                 | <b>✓</b>         |          |                |               |             |            |            |          |

| LE                          | <b>✓</b>    | <b>✓</b>       | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        | <b>✓</b>        |                  | <b>✓</b>        | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| M512 RAM<br>Block           |             |                | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        | <b>✓</b>        |                  | <b>\</b>        | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| M4K RAM Block               |             |                | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        | <b>✓</b>        |                  | <b>✓</b>        | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| M-RAM Block                 |             |                |                    |                          |                 |                 |                  | <b>✓</b>        | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| DSP Blocks                  |             |                | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        | <b>✓</b>        |                  | <b>✓</b>        | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| Column IOE                  |             |                |                    | <b>✓</b>                 |                 |                 |                  | <b>✓</b>        | <b>✓</b>        | <b>✓</b>         |          |                |               |             |            |            |          |

| Row IOE                     |             |                |                    | <b>✓</b>                 |                 | <b>✓</b>        | <b>✓</b>         | <b>✓</b>        | <b>✓</b>        | <b>✓</b>         |          |                |               |             |            |            |          |

The memory address depths and output widths can be configured as  $4,096 \times 1, 2,048 \times 2, 1,024 \times 4,512 \times 8$  (or  $512 \times 9$  bits),  $256 \times 16$  (or  $256 \times 18$  bits), and  $128 \times 32$  (or  $128 \times 36$  bits). The  $128 \times 32$ - or 36-bit configuration is not available in the true dual-port mode. Mixed-width configurations are also possible, allowing different read and write widths. Tables 2–5 and 2–6 summarize the possible M4K RAM block configurations.

| Table 2-5. M4 | Table 2–5. M4K RAM Block Configurations (Simple Dual-Port) |            |          |          |          |          |          |             |          |  |  |  |  |

|---------------|------------------------------------------------------------|------------|----------|----------|----------|----------|----------|-------------|----------|--|--|--|--|

| Dood Dood     |                                                            | Write Port |          |          |          |          |          |             |          |  |  |  |  |

| Read Port     | 4K × 1                                                     | 2K × 2     | 1K × 4   | 512 × 8  | 256 × 16 | 128 × 32 | 512 × 9  | 256 × 18    | 128 × 36 |  |  |  |  |

| 4K × 1        | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |  |  |  |  |

| 2K × 2        | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | ~        | <b>✓</b> | <b>✓</b> |          |             |          |  |  |  |  |

| 1K × 4        | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | ~        | <b>✓</b> | <b>✓</b> |          |             |          |  |  |  |  |

| 512 × 8       | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | ~        | <b>✓</b> | <b>✓</b> |          |             |          |  |  |  |  |

| 256 × 16      | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | ~        | <b>✓</b> | <b>✓</b> |          |             |          |  |  |  |  |

| 128 × 32      | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | ✓        |          |             |          |  |  |  |  |

| 512 × 9       |                                                            |            |          |          |          |          | <b>✓</b> | <b>✓</b>    | <b>✓</b> |  |  |  |  |

| 256 × 18      |                                                            |            |          |          |          |          | <b>✓</b> | <b>✓</b>    | <b>✓</b> |  |  |  |  |

| 128 × 36      |                                                            |            |          |          |          |          | <b>✓</b> | <b>&gt;</b> | <b>✓</b> |  |  |  |  |

| Table 2–6. M4K RAM | Table 2–6. M4K RAM Block Configurations (True Dual-Port) |          |          |          |          |          |          |  |  |  |  |  |

|--------------------|----------------------------------------------------------|----------|----------|----------|----------|----------|----------|--|--|--|--|--|

| Dovt A             |                                                          | Port B   |          |          |          |          |          |  |  |  |  |  |

| Port A             | 4K × 1                                                   | 2K × 2   | 1K × 4   | 512 × 8  | 256 × 16 | 512 × 9  | 256 × 18 |  |  |  |  |  |

| 4K × 1             | <b>✓</b>                                                 | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |  |  |  |  |  |

| 2K × 2             | ✓                                                        | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |  |  |  |  |

| 1K × 4             | ✓                                                        | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |  |  |  |  |

| 512 × 8            | ✓                                                        | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |  |  |  |  |

| 256 × 16           | <b>✓</b>                                                 | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |  |  |  |  |

| 512 × 9            |                                                          |          |          |          |          | <b>✓</b> | <b>✓</b> |  |  |  |  |  |

| 256 × 18           |                                                          |          |          |          |          | <b>✓</b> | <b>✓</b> |  |  |  |  |  |

When the M4K RAM block is configured as a shift register block, you can create a shift register up to 4,608 bits ( $w \times m \times n$ ).

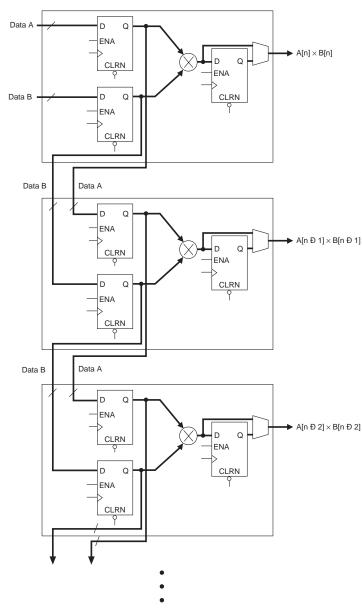

Figure 2–33. Multiplier Sub-Blocks Using Input Shift Register Connections Note (1)

Note to Figure 2–33:

(1) Either Data A or Data B input can be set to a parallel input for constant coefficient multiplication.

Accumulator Feedback accum\_sload0 (2) Result A ■ overflow0 Adder/ Subtractor/ addnsub1 (2) Accumulator1 Output Selection Multiplexer Result B signa (2) Summation Output signb (2) Register Block Result C Adder/ addnsub3 (2) Subtractor/ Accumulator2 overflow1 Result D accum\_sload1 (2) Accumulator Feedback

Figure 2–34. Adder/Output Blocks Note (1)

#### Notes to Figure 2–34:

- (1) Adder/output block shown in Figure 2–34 is in 18 × 18-bit mode. In 9 × 9-bit mode, there are four adder/subtractor blocks and two summation blocks.

- (2) These signals are either not registered, registered once, or registered twice to match the data path pipeline.

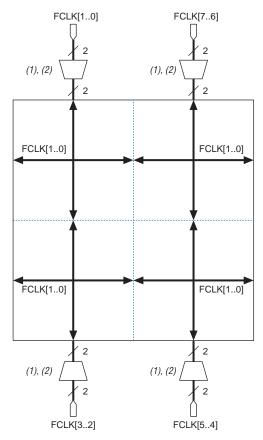

Figure 2–44. EP1S25, EP1S20 & EP1S10 Device Fast Clock Pin Connections to Fast Regional Clocks

#### Notes to Figure 2-44:

- (1) This is a set of two multiplexers.

- (2) In addition to the FCLK pin inputs, there is also an input from the I/O interconnect.

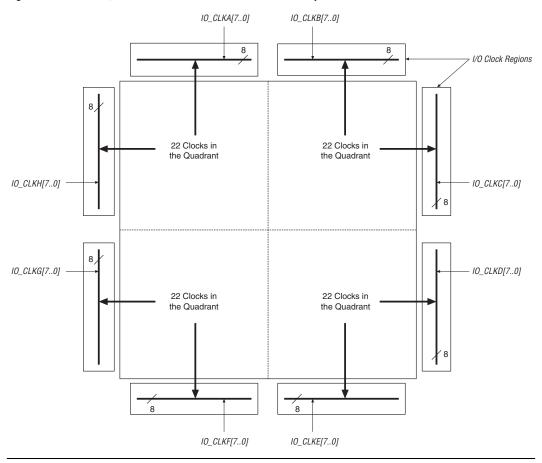

Figure 2-47. EP1S10, EP1S20 & EP1S25 Device I/O Clock Groups

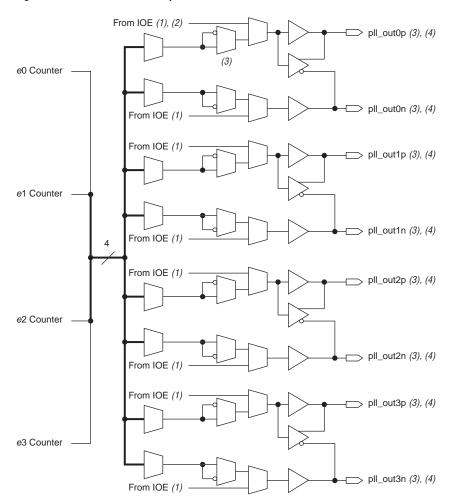

Figure 2-55. External Clock Outputs for PLLs 5 & 6

#### *Notes to Figure 2–55:*

- (1) The design can use each external clock output pin as a general-purpose output pin from the logic array. These pins are multiplexed with IOE outputs.

- (2) Two single-ended outputs are possible per output counter—either two outputs of the same frequency and phase or one shifted 180°.

- (3) EP1S10, EP1S20, and EP1S25 devices in 672-pin BGA and 484- and 672-pin FineLine BGA packages only have two pairs of external clocks (i.e., pll\_out0p, pll\_out0n, pll\_out1p, and pll\_out1n).

- (4) Differential SSTL and HSTL outputs are implemented using two single-ended output buffers, which are programmed to have opposite polarity.

Any of the four external output counters can drive the single-ended or differential clock outputs for PLLs 5 and 6. This means one counter or frequency can drive all output pins available from PLL 5 or PLL 6. Each pair of output pins (four pins total) has dedicated VCC and GND pins to reduce the output clock's overall jitter by providing improved isolation from switching I/O pins.

For PLLs 5 and 6, each pin of a single-ended output pair can either be in phase or 180° out of phase. The clock output pin pairs support the same I/O standards as standard output pins (in the top and bottom banks) as well as LVDS, LVPECL, 3.3-V PCML, HyperTransport technology, differential HSTL, and differential SSTL. Table 2–20 shows which I/O standards the enhanced PLL clock pins support. When in single-ended or differential mode, the two outputs operate off the same power supply. Both outputs use the same standards in single-ended mode to maintain performance. You can also use the external clock output pins as user output pins if external enhanced PLL clocking is not needed.

| Table 2–20. I/O Standards Supported for Enhanced PLL Pins (Part 1 of 2) |          |          |           |        |  |  |  |  |  |  |

|-------------------------------------------------------------------------|----------|----------|-----------|--------|--|--|--|--|--|--|

| L/O Ctondovd                                                            |          | Output   |           |        |  |  |  |  |  |  |

| I/O Standard                                                            | INCLK    | FBIN     | PLLENABLE | EXTCLK |  |  |  |  |  |  |

| LVTTL                                                                   | <b>✓</b> | <b>✓</b> | <b>✓</b>  | ✓      |  |  |  |  |  |  |

| LVCMOS                                                                  | <b>✓</b> | <b>✓</b> | ✓         | ✓      |  |  |  |  |  |  |

| 2.5 V                                                                   | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |  |  |

| 1.8 V                                                                   | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |  |  |

| 1.5 V                                                                   | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |  |  |

| 3.3-V PCI                                                               | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |  |  |

| 3.3-V PCI-X 1.0                                                         | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |  |  |

| LVPECL                                                                  | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |  |  |

| 3.3-V PCML                                                              | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |  |  |

| LVDS                                                                    | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |  |  |

| HyperTransport technology                                               | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |  |  |

| Differential HSTL                                                       | <b>✓</b> |          |           | ✓      |  |  |  |  |  |  |

| Differential SSTL                                                       |          |          |           | ✓      |  |  |  |  |  |  |

| 3.3-V GTL                                                               | <b>✓</b> | ✓        |           | ✓      |  |  |  |  |  |  |

| 3.3-V GTL+                                                              | <b>✓</b> | ✓        |           | ✓      |  |  |  |  |  |  |

| 1.5-V HSTL Class I                                                      | <b>✓</b> | ✓        |           | ✓      |  |  |  |  |  |  |

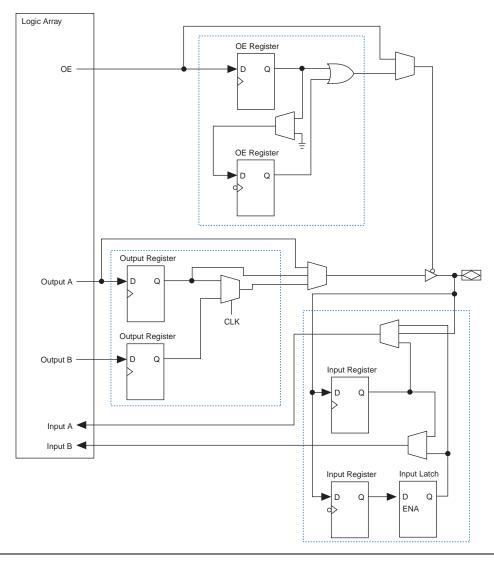

Figure 2-59. Stratix IOE Structure

The IOEs are located in I/O blocks around the periphery of the Stratix device. There are up to four IOEs per row I/O block and six IOEs per column I/O block. The row I/O blocks drive row, column, or direct link interconnects. The column I/O blocks drive column interconnects. Figure 2–60 shows how a row I/O block connects to the logic array. Figure 2–61 shows how a column I/O block connects to the logic array.

| Table 2–32. I/O Support by Bank (Part 2 of 2) |                                     |                                     |                                                                 |  |  |  |  |  |  |

|-----------------------------------------------|-------------------------------------|-------------------------------------|-----------------------------------------------------------------|--|--|--|--|--|--|

| I/O Standard                                  | Top & Bottom Banks<br>(3, 4, 7 & 8) | Left & Right Banks<br>(1, 2, 5 & 6) | Enhanced PLL External<br>Clock Output Banks<br>(9, 10, 11 & 12) |  |  |  |  |  |  |

| SSTL-3 Class II                               | ✓                                   | <b>✓</b>                            | ✓                                                               |  |  |  |  |  |  |

| AGP (1× and 2×)                               | ✓                                   |                                     | ✓                                                               |  |  |  |  |  |  |

| CTT                                           | ✓                                   | ✓                                   | ✓                                                               |  |  |  |  |  |  |

Each I/O bank has its own VCCIO pins. A single device can support 1.5-, 1.8-, 2.5-, and 3.3-V interfaces; each bank can support a different standard independently. Each bank also has dedicated VREF pins to support any one of the voltage-referenced standards (such as SSTL-3) independently.

Each I/O bank can support multiple standards with the same  $V_{\rm CCIO}$  for input and output pins. Each bank can support one voltage-referenced I/O standard. For example, when  $V_{\rm CCIO}$  is 3.3 V, a bank can support LVTTL, LVCMOS, 3.3-V PCI, and SSTL-3 for inputs and outputs.

#### **Differential On-Chip Termination**

Stratix devices provide differential on-chip termination (LVDS I/O standard) to reduce reflections and maintain signal integrity. Differential on-chip termination simplifies board design by minimizing the number of external termination resistors required. Termination can be placed inside the package, eliminating small stubs that can still lead to reflections. The internal termination is designed using transistors in the linear region of operation.

Stratix devices support internal differential termination with a nominal resistance value of 137.5  $\Omega$  for LVDS input receiver buffers. LVPECL signals require an external termination resistor. Figure 2–71 shows the device with differential termination.

# 3. Configuration & Testing

\$51003-1.3

## IEEE Std. 1149.1 (JTAG) Boundary-Scan Support

All Stratix® devices provide JTAG BST circuitry that complies with the IEEE Std. 1149.1a-1990 specification. JTAG boundary-scan testing can be performed either before or after, but not during configuration. Stratix devices can also use the JTAG port for configuration together with either the Quartus® II software or hardware using either Jam Files (.jam) or Jam Byte-Code Files (.jbc).

Stratix devices support IOE I/O standard setting reconfiguration through the JTAG BST chain. The JTAG chain can update the I/O standard for all input and output pins any time before or during user mode through the CONFIG\_IO instruction. You can use this ability for JTAG testing before configuration when some of the Stratix pins drive or receive from other devices on the board using voltage-referenced standards. Since the Stratix device may not be configured before JTAG testing, the I/O pins may not be configured for appropriate electrical standards for chip-to-chip communication. Programming those I/O standards via JTAG allows you to fully test the I/O connection to other devices.

The enhanced PLL reconfiguration bits are part of the JTAG chain before configuration and after power-up. After device configuration, the PLL reconfiguration bits are not part of the JTAG chain.

The JTAG pins support 1.5-V/1.8-V or 2.5-V/3.3-V I/O standards. The TDO pin voltage is determined by the  $V_{\rm CCIO}$  of the bank where it resides. The VCCSEL pin selects whether the JTAG inputs are 1.5-V, 1.8-V, 2.5-V, or 3.3-V compatible.

Stratix devices also use the JTAG port to monitor the logic operation of the device with the SignalTap<sup>®</sup> II embedded logic analyzer. Stratix devices support the JTAG instructions shown in Table 3–1.

The Quartus II software has an Auto Usercode feature where you can choose to use the checksum value of a programming file as the JTAG user code. If selected, the checksum is automatically loaded to the USERCODE register. In the Settings dialog box in the Assignments menu, click **Device & Pin Options**, then **General**, and then turn on the **Auto Usercode** option.

| Table 4–9. Overshoot Input Voltage with Respect to Duty Cycle (Part 2 of 2) |                        |  |  |  |  |  |  |

|-----------------------------------------------------------------------------|------------------------|--|--|--|--|--|--|

| Vin (V)                                                                     | Maximum Duty Cycle (%) |  |  |  |  |  |  |

| 4.3                                                                         | 30                     |  |  |  |  |  |  |

| 4.4                                                                         | 17                     |  |  |  |  |  |  |

| 4.5                                                                         | 10                     |  |  |  |  |  |  |

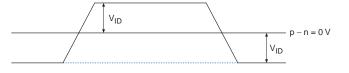

Figures 4–1 and 4–2 show receiver input and transmitter output waveforms, respectively, for all differential I/O standards (LVDS, 3.3-V PCML, LVPECL, and HyperTransport technology).

Figure 4-1. Receiver Input Waveforms for Differential I/O Standards

# Single-Ended Waveform Positive Channel (p) = $V_{IH}$ Negative Channel (n) = $V_{IL}$

#### **Differential Waveform**

| Table 4-81. I         | Table 4–81. EP1S40 External I/O Timing on Column Pins Using Global Clock Networks |         |         |                |       |         |         |       |      |  |  |

|-----------------------|-----------------------------------------------------------------------------------|---------|---------|----------------|-------|---------|---------|-------|------|--|--|

| Parameter             | -5 Spee                                                                           | d Grade | -6 Spee | -6 Speed Grade |       | d Grade | -8 Spee | 11    |      |  |  |

|                       | Min                                                                               | Max     | Min     | Max            | Min   | Max     | Min     | Max   | Unit |  |  |

| t <sub>INSU</sub>     | 2.126                                                                             |         | 2.268   |                | 2.558 |         | 2.930   |       | ns   |  |  |

| t <sub>INH</sub>      | 0.000                                                                             |         | 0.000   |                | 0.000 |         | 0.000   |       | ns   |  |  |

| t <sub>OUTCO</sub>    | 2.856                                                                             | 5.585   | 2.856   | 5.987          | 2.856 | 6.541   | 2.847   | 7.253 | ns   |  |  |

| t <sub>XZ</sub>       | 2.796                                                                             | 5.459   | 2.796   | 5.855          | 2.796 | 6.417   | 2.787   | 7.138 | ns   |  |  |

| t <sub>ZX</sub>       | 2.796                                                                             | 5.459   | 2.796   | 5.855          | 2.796 | 6.417   | 2.787   | 7.138 | ns   |  |  |

| t <sub>INSUPLL</sub>  | 1.466                                                                             |         | 1.455   |                | 1.711 |         | 1.906   |       | ns   |  |  |

| t <sub>INHPLL</sub>   | 0.000                                                                             |         | 0.000   |                | 0.000 |         | 0.000   |       | ns   |  |  |

| t <sub>OUTCOPLL</sub> | 1.092                                                                             | 2.345   | 1.092   | 2.510          | 1.092 | 2.455   | 1.089   | 2.473 | ns   |  |  |

| t <sub>XZPLL</sub>    | 1.032                                                                             | 2.219   | 1.032   | 2.378          | 1.032 | 2.331   | 1.029   | 2.358 | ns   |  |  |

| t <sub>ZXPLL</sub>    | 1.032                                                                             | 2.219   | 1.032   | 2.378          | 1.032 | 2.331   | 1.029   | 2.358 | ns   |  |  |

| Table 4-82. I      | Table 4–82. EP1S40 External I/O Timing on Row Pins Using Fast Regional Clock Networks |         |                |       |         |         |         |       |      |  |  |

|--------------------|---------------------------------------------------------------------------------------|---------|----------------|-------|---------|---------|---------|-------|------|--|--|

| Parameter          | -5 Spee                                                                               | d Grade | -6 Speed Grade |       | -7 Spee | d Grade | -8 Spee |       |      |  |  |

|                    | Min                                                                                   | Max     | Min            | Max   | Min     | Max     | Min     | Max   | Unit |  |  |

| t <sub>INSU</sub>  | 2.472                                                                                 |         | 2.685          |       | 3.083   |         | 3.056   |       | ns   |  |  |

| t <sub>INH</sub>   | 0.000                                                                                 |         | 0.000          |       | 0.000   |         | 0.000   |       | ns   |  |  |

| t <sub>OUTCO</sub> | 2.631                                                                                 | 5.258   | 2.631          | 5.625 | 2.631   | 6.105   | 2.745   | 7.324 | ns   |  |  |

| t <sub>XZ</sub>    | 2.658                                                                                 | 5.312   | 2.658          | 5.681 | 2.658   | 6.173   | 2.772   | 7.406 | ns   |  |  |

| t <sub>ZX</sub>    | 2.658                                                                                 | 5.312   | 2.658          | 5.681 | 2.658   | 6.173   | 2.772   | 7.406 | ns   |  |  |

| Table 4–102. Reporting Methodology For Minimum Timi | ng For Single-Ended Output Pins (Part 2 of 2) |

|-----------------------------------------------------|-----------------------------------------------|

| Notes (1), (2), (3)                                 |                                               |

| 1/0 0111     |                   | Measurement<br>Point |                |                  |                          |            |                        |                   |

|--------------|-------------------|----------------------|----------------|------------------|--------------------------|------------|------------------------|-------------------|

| I/O Standard | $\mathbf{R}_{UP}$ | $R_{DN}$             | R <sub>S</sub> | $\mathbf{R}_{T}$ | V <sub>CCIO</sub><br>(V) | VTT<br>(V) | C <sub>L</sub><br>(pF) | V <sub>MEAS</sub> |

| 3.3-V CTT    | _                 | =-                   | 25             | 50               | 3.600                    | 1.650      | 30                     | 1.650             |

#### Notes to Table 4–102:

- (1) Input measurement point at internal node is  $0.5 \times V_{CCINT}$ .

- (2) Output measuring point for data is V<sub>MEAS</sub>. When two values are given, the first is the measurement point on the rising edge and the other is for the falling edge.

- (3) Input stimulus edge rate is 0 to V<sub>CCINT</sub> in 0.5 ns (internal signal) from the driver preceding the I/O buffer.

- (4) The first value is for the output rising edge and the second value is for the output falling edge. The hyphen (-) indicates infinite resistance or disconnection.

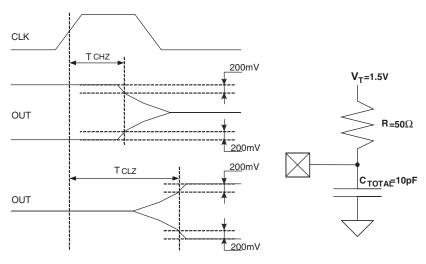

Figure 4–8 shows the measurement setup for output disable and output enable timing. The  $T_{CHZ}$  stands for clock to high Z time delay and is the same as  $T_{XZ}.$  The  $T_{CLZ}$  stands for clock to low Z (driving) time delay and is the same as  $T_{ZX}.$

Figure 4–8. Measurement Setup for  $T_{XZ}$  and  $T_{ZX}$

| Table 4–105. Stratix I/O Standard Output Delay Adders for Fast Slew Rate on Column Pins (Part 2 of 2) |                |       |                |       |                |       |                |       |      |

|-------------------------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-------|------|

| Parameter                                                                                             | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | Ī    |

|                                                                                                       | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max   | Unit |

| CTT                                                                                                   |                | 973   |                | 1,021 |                | 1,021 |                | 1,021 | ps   |

| SSTL-3 Class I                                                                                        |                | 719   |                | 755   |                | 755   |                | 755   | ps   |

| SSTL-3 Class II                                                                                       |                | 146   |                | 153   |                | 153   |                | 153   | ps   |

| SSTL-2 Class I                                                                                        |                | 678   |                | 712   |                | 712   |                | 712   | ps   |

| SSTL-2 Class II                                                                                       |                | 223   |                | 234   |                | 234   |                | 234   | ps   |

| SSTL-18 Class I                                                                                       |                | 1,032 |                | 1,083 |                | 1,083 |                | 1,083 | ps   |

| SSTL-18 Class II                                                                                      |                | 447   |                | 469   |                | 469   |                | 469   | ps   |

| 1.5-V HSTL Class I                                                                                    |                | 660   |                | 693   |                | 693   |                | 693   | ps   |

| 1.5-V HSTL Class II                                                                                   |                | 537   |                | 564   |                | 564   |                | 564   | ps   |

| 1.8-V HSTL Class I                                                                                    |                | 304   |                | 319   |                | 319   |                | 319   | ps   |

| 1.8-V HSTL Class II                                                                                   |                | 231   |                | 242   |                | 242   |                | 242   | ps   |

| Table 4–106. Stratix I/O Standard Output Delay Adders for Fast Slew Rate on Row Pins (Part 1 of 2) |       |                |       |                |       |                |       |                |       |       |

|----------------------------------------------------------------------------------------------------|-------|----------------|-------|----------------|-------|----------------|-------|----------------|-------|-------|

| Parameter                                                                                          |       | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | 11-:4 |

|                                                                                                    |       | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max   | Unit  |

| LVCMOS                                                                                             | 2 mA  |                | 1,518 |                | 1,594 |                | 1,594 |                | 1,594 | ps    |

|                                                                                                    | 4 mA  |                | 746   |                | 783   |                | 783   |                | 783   | ps    |

|                                                                                                    | 8 mA  |                | 96    |                | 100   |                | 100   |                | 100   | ps    |

|                                                                                                    | 12 mA |                | 0     |                | 0     |                | 0     |                | 0     | ps    |

| 3.3-V LVTTL                                                                                        | 4 mA  |                | 1,518 |                | 1,594 |                | 1,594 |                | 1,594 | ps    |

|                                                                                                    | 8 mA  |                | 1,038 |                | 1,090 |                | 1,090 |                | 1,090 | ps    |

|                                                                                                    | 12 mA |                | 521   |                | 547   |                | 547   |                | 547   | ps    |

|                                                                                                    | 16 mA |                | 414   |                | 434   |                | 434   |                | 434   | ps    |

|                                                                                                    | 24 mA |                | 0     |                | 0     |                | 0     |                | 0     | ps    |

| 2.5-V LVTTL                                                                                        | 2 mA  |                | 2,032 |                | 2,133 |                | 2,133 |                | 2,133 | ps    |

|                                                                                                    | 8 mA  |                | 699   |                | 734   |                | 734   |                | 734   | ps    |

|                                                                                                    | 12 mA |                | 374   |                | 392   |                | 392   |                | 392   | ps    |

|                                                                                                    | 16 mA |                | 165   |                | 173   |                | 173   |                | 173   | ps    |

| 1.8-V LVTTL                                                                                        | 2 mA  |                | 3,714 |                | 3,899 |                | 3,899 |                | 3,899 | ps    |

|                                                                                                    | 8 mA  |                | 1,055 |                | 1,107 |                | 1,107 |                | 1,107 | ps    |

|                                                                                                    | 12 mA |                | 830   |                | 871   |                | 871   |                | 871   | ps    |

| Mode 2–36                                             | Port I/O Standards 2–102                            |

|-------------------------------------------------------|-----------------------------------------------------|

| Row & Column Interface Unit                           | I/O Standards Supported for Enhanced PLL            |

| Signals 2–43                                          | Pins 2–94                                           |

| Parity Bit Support 2–24                               | Lock Detect & Programmable Gated                    |

| Shift Register                                        | Locked 2–98                                         |

| Memory Configuration 2–26                             | PLL Locations 2–84                                  |

| Support 2–25                                          | Programmable Bandwidth 2–91                         |

| Simple Dual-Port & Single-Port Memory                 | Programmable Delay Chain 2-111                      |

| Configurations 2–23                                   | Programmable Duty Cycle 2–98                        |

| Stratix IOE in DDR Input I/O                          | Reconfiguration 2–90                                |

| Configuration 2–112                                   |                                                     |

| Stratix IOE in DDR Output I/O                         | Т                                                   |

| Configuration 2–114                                   | 1                                                   |

| TriMatrix Memory 2–21                                 | Testing                                             |

| True Dual-Port Memory                                 | Temperature Sensing Diode 3–13                      |

| Configuration 2–22                                    | Electrical Characteristics 3–14                     |

|                                                       | External 3–14                                       |

| 0                                                     | Temperature vs. Temperature-Sensing Diode           |

|                                                       | Voltage 3–15                                        |

| Ordering Information 5–1                              | Timing                                              |

| Device Pin-Outs 5–1                                   | DSP                                                 |

| Packaging Ordering Information 5–2                    | Block Internal Timing                               |

| Reference & Ordering Information 5–1                  | Microparameter                                      |

| Output Registers 2–64                                 | Descriptions 4–23                                   |

| Output Selection Multiplexer 2–64                     | Microparameters 4–29                                |

|                                                       | Dual-Port RAM Timing Microparameter                 |

| P                                                     | Waveform 4–27                                       |

| P. 1                                                  | External Timing in Stratix Devices 4–33             |

| Packaging                                             | High-Speed I/O Timing 4–87                          |

| BGA Package Sizes 1–4                                 | High-Speed Timing Specifications & Terminology 4–87 |

| Device Speed Grades 1–5                               | Internal Parameters 4–22                            |

| FineLine BGA Package Sizes 1–5                        | IOE Internal Timing Microparameter                  |

| PCI-X 1.0 Specifications 4–10<br>Phase Shifting 2–103 | Descriptions 4–22                                   |

| PLL                                                   | LE Internal Timing Microparameters 4–28             |

| Advanced Clear & Enable Control 2–98                  | Logic Elements Internal Timing Microparam-          |

| Dynamically Programmable Counters & De-               | eter Descriptions 4–22                              |

| lays in Stratix Device Enhanced                       | Model 4–19                                          |

| PLLs 2–91                                             | PLL Timing 4–94                                     |

| Enhanced                                              | Preliminary & Final 4–19                            |

| Fast PLLs 2–81                                        | Stratix Device Timing Model Status 4–19             |

| Fast PLL 2–100                                        | Stratix JTAG                                        |

| Channel Layout EP1S10, EP1S20 or                      | Timing Parameters & Values 3–4                      |

| EP1S25 Devices 2–138                                  | TriMatrix Memory                                    |

| Channel Layout EP1S30 to EP1S80                       | TriMatrix Memory Features 2–21                      |

| Devices 2–139                                         | •                                                   |

Index-6 Altera Corporation