Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 2566                                                     |

| Number of Logic Elements/Cells | 25660                                                    |

| Total RAM Bits                 | 1944576                                                  |

| Number of I/O                  | 473                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 672-BBGA                                                 |

| Supplier Device Package        | 672-FBGA (27x27)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s25f672c6n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Contents Contents

| Maximum Input & Output Clock Rates                    | 4–76 |

|-------------------------------------------------------|------|

| High-Speed I/O Specification                          | 4–87 |

| PLL Specifications                                    | 4–94 |

| DLL Specifications                                    |      |

|                                                       |      |

| Chapter 5. Reference & Ordering Information           |      |

| Software                                              |      |

| Chapter 5. Reference & Ordering Information  Software | 5–1  |

# Index

Altera Corporation v

| Chapter | Date/Version         | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2       | July 2005 v3.2       | <ul> <li>Added "Clear Signals" section.</li> <li>Updated "Power Sequencing &amp; Hot Socketing" section.</li> <li>Format changes.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | September 2004, v3.1 | <ul> <li>Updated fast regional clock networks description on page 2–73.</li> <li>Deleted the word preliminary from the "specification for the maximum time to relock is 100 µs" on page 2–90.</li> <li>Added information about differential SSTL and HSTL outputs in "External Clock Outputs" on page 2–92.</li> <li>Updated notes in Figure 2–55 on page 2–93.</li> <li>Added information about <i>m</i> counter to "Clock Multiplication &amp; Division" on page 2–101.</li> <li>Updated Note 1 in Table 2–58 on page 2–101.</li> <li>Updated description of "Clock Multiplication &amp; Division" on page 2–88.</li> <li>Updated Table 2–22 on page 2–102.</li> <li>Added references to AN 349 and AN 329 to "External RAM Interfacing" on page 2–115.</li> <li>Table 2–25 on page 2–116: updated the table, updated Notes 3 and 4. Notes 4, 5, and 6, are now Notes 5, 6, and 7, respectively.</li> <li>Updated Table 2–26 on page 2–117.</li> <li>Added information about PCI Compliance to page 2–120.</li> <li>Table 2–32 on page 2–126: updated the table and deleted Note 1.</li> <li>Updated reference to device pin-outs now being available on the web on page 2–130.</li> <li>Added Notes 4 and 5 to Table 2–36 on page 2–130.</li> <li>Updated Note 3 in Table 2–37 on page 2–131.</li> <li>Updated Note 5 in Table 2–41 on page 2–135.</li> </ul> |

|         | April 2004, v3.0     | <ul> <li>Added note 3 to rows 11 and 12 in Table 2–18.</li> <li>Deleted "Stratix and Stratix GX Device PLL Availability" table.</li> <li>Added I/O standards row in Table 2–28 that support max and min strength.</li> <li>Row clk [1,3,8,10] was removed from Table 2–30.</li> <li>Added checkmarks in Enhanced column for LVPECL, 3.3-V PCML, LVDS, and HyperTransport technology rows in Table 2–32.</li> <li>Removed the Left and Right I/O Banks row in Table 2–34.</li> <li>Changed RCLK values in Figures 2–50 and 2–51.</li> <li>External RAM Interfacing section replaced.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | November 2003, v2.2  | <ul> <li>Added 672-pin BGA package information in Table 2–37.</li> <li>Removed support for series and parallel on-chip termination.</li> <li>Termination Technology renamed differential on-chip termination.</li> <li>Updated the number of channels per PLL in Tables 2-38 through 2-42.</li> <li>Updated Figures 2–65 and 2–67.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | October 2003, v2.1   | <ul> <li>Updated DDR I information.</li> <li>Updated Table 2–22.</li> <li>Added Tables 2–25, 2–29, 2–30, and 2–72.</li> <li>Updated Figures 2–59, 2–65, and 2–67.</li> <li>Updated the Lock Detect section.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Section I–2 Altera Corporation

The number of M512 RAM, M4K RAM, and DSP blocks varies by device along with row and column numbers and M-RAM blocks. Table 2–1 lists the resources available in Stratix devices.

| Table 2-1. | Table 2–1. Stratix Device Resources |                           |                 |                             |                |          |  |

|------------|-------------------------------------|---------------------------|-----------------|-----------------------------|----------------|----------|--|

| Device     | M512 RAM<br>Columns/Blocks          | M4K RAM<br>Columns/Blocks | M-RAM<br>Blocks | DSP Block<br>Columns/Blocks | LAB<br>Columns | LAB Rows |  |

| EP1S10     | 4 / 94                              | 2/60                      | 1               | 2/6                         | 40             | 30       |  |

| EP1S20     | 6 / 194                             | 2 / 82                    | 2               | 2/10                        | 52             | 41       |  |

| EP1S25     | 6 / 224                             | 3 / 138                   | 2               | 2/10                        | 62             | 46       |  |

| EP1S30     | 7 / 295                             | 3 / 171                   | 4               | 2 / 12                      | 67             | 57       |  |

| EP1S40     | 8 / 384                             | 3 / 183                   | 4               | 2 / 14                      | 77             | 61       |  |

| EP1S60     | 10 / 574                            | 4 / 292                   | 6               | 2 / 18                      | 90             | 73       |  |

| EP1S80     | 11 / 767                            | 4 / 364                   | 9               | 2 / 22                      | 101            | 91       |  |

# Logic Array Blocks

Each LAB consists of 10 LEs, LE carry chains, LAB control signals, local interconnect, LUT chain, and register chain connection lines. The local interconnect transfers signals between LEs in the same LAB. LUT chain connections transfer the output of one LE's LUT to the adjacent LE for fast sequential LUT connections within the same LAB. Register chain connections transfer the output of one LE's register to the adjacent LE's register within an LAB. The Quartus® II Compiler places associated logic within an LAB or adjacent LABs, allowing the use of local, LUT chain, and register chain connections for performance and area efficiency. Figure 2–2 shows the Stratix LAB.

C8 interconnects span eight LABs, M512, or M4K blocks up or down from a source LAB. Every LAB has its own set of C8 interconnects to drive either up or down. C8 interconnect connections between the LABs in a column are similar to the C4 connections shown in Figure 2–11 with the exception that they connect to eight LABs above and below. The C8 interconnects can drive and be driven by all types of architecture blocks similar to C4 interconnects. C8 interconnects can drive each other to extend their range as well as R8 interconnects for column-to-column connections. C8 interconnects are faster than two C4 interconnects.

C16 column interconnects span a length of 16 LABs and provide the fastest resource for long column connections between LABs, TriMatrix memory blocks, DSP blocks, and IOEs. C16 interconnects can cross M-RAM blocks and also drive to row and column interconnects at every fourth LAB. C16 interconnects drive LAB local interconnects via C4 and R4 interconnects and do not drive LAB local interconnects directly.

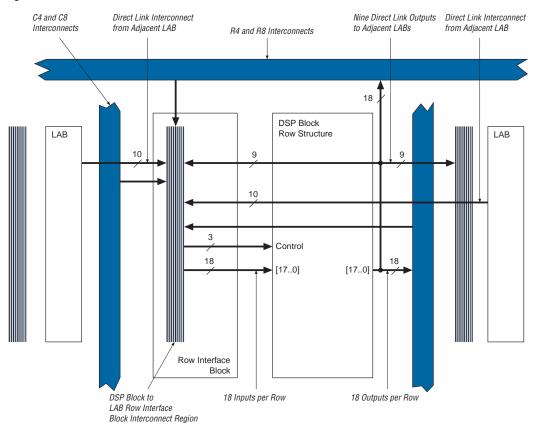

All embedded blocks communicate with the logic array similar to LAB-to-LAB interfaces. Each block (i.e., TriMatrix memory and DSP blocks) connects to row and column interconnects and has local interconnect regions driven by row and column interconnects. These blocks also have direct link interconnects for fast connections to and from a neighboring LAB. All blocks are fed by the row LAB clocks, labclk [7..0].

| Table 2–3. TriMatrix Memory Features (Part 2 of 2) |                                                                         |                                                                                                  |                                                                                                                  |  |  |

|----------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|

| Memory Feature                                     | M512 RAM Block<br>(32 × 18 Bits)                                        | M4K RAM Block<br>(128 × 36 Bits)                                                                 | M-RAM Block<br>(4K × 144 Bits)                                                                                   |  |  |

| Configurations                                     | 512 × 1<br>256 × 2<br>128 × 4<br>64 × 8<br>64 × 9<br>32 × 16<br>32 × 18 | 4K × 1<br>2K × 2<br>1K × 4<br>512 × 8<br>512 × 9<br>256 × 16<br>256 × 18<br>128 × 32<br>128 × 36 | 64K × 8<br>64K × 9<br>32K × 16<br>32K × 18<br>16K × 32<br>16K × 36<br>8K × 64<br>8K × 72<br>4K × 128<br>4K × 144 |  |  |

*Notes to Table 2–3:*

- (1) See Table 4–36 for maximum performance information.

- (2) The M-RAM block does not support memory initializations. However, the M-RAM block can emulate a ROM function using a dual-port RAM bock. The Stratix device must write to the dual-port memory once and then disable the write-enable ports afterwards.

Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

# **Memory Modes**

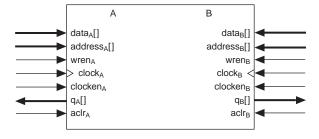

TriMatrix memory blocks include input registers that synchronize writes and output registers to pipeline designs and improve system performance. M4K and M-RAM memory blocks offer a true dual-port mode to support any combination of two-port operations: two reads, two writes, or one read and one write at two different clock frequencies. Figure 2–12 shows true dual-port memory.

Figure 2-12. True Dual-Port Memory Configuration

The memory address depths and output widths can be configured as  $4,096 \times 1, 2,048 \times 2, 1,024 \times 4,512 \times 8$  (or  $512 \times 9$  bits),  $256 \times 16$  (or  $256 \times 18$  bits), and  $128 \times 32$  (or  $128 \times 36$  bits). The  $128 \times 32$ - or 36-bit configuration is not available in the true dual-port mode. Mixed-width configurations are also possible, allowing different read and write widths. Tables 2–5 and 2–6 summarize the possible M4K RAM block configurations.

| Table 2-5. M4 | Table 2–5. M4K RAM Block Configurations (Simple Dual-Port) |            |          |          |          |          |          |             |          |

|---------------|------------------------------------------------------------|------------|----------|----------|----------|----------|----------|-------------|----------|

| Dood Dood     |                                                            | Write Port |          |          |          |          |          |             |          |

| Read Port     | 4K × 1                                                     | 2K × 2     | 1K × 4   | 512 × 8  | 256 × 16 | 128 × 32 | 512 × 9  | 256 × 18    | 128 × 36 |

| 4K × 1        | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |

| 2K × 2        | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | ~        | <b>✓</b> | <b>✓</b> |          |             |          |

| 1K × 4        | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | ~        | <b>✓</b> | <b>✓</b> |          |             |          |

| 512 × 8       | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | ~        | <b>✓</b> | <b>✓</b> |          |             |          |

| 256 × 16      | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | ~        | <b>✓</b> | <b>✓</b> |          |             |          |

| 128 × 32      | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | ✓        |          |             |          |

| 512 × 9       |                                                            |            |          |          |          |          | <b>✓</b> | <b>✓</b>    | <b>✓</b> |

| 256 × 18      |                                                            |            |          |          |          |          | <b>✓</b> | <b>✓</b>    | <b>✓</b> |

| 128 × 36      |                                                            |            |          |          |          |          | <b>✓</b> | <b>&gt;</b> | <b>✓</b> |

| Table 2–6. M4K RAM | able 2–6. M4K RAM Block Configurations (True Dual-Port) |          |          |          |          |          |          |

|--------------------|---------------------------------------------------------|----------|----------|----------|----------|----------|----------|

| Don't A            |                                                         |          |          | Port B   |          |          |          |

| Port A             | 4K × 1                                                  | 2K × 2   | 1K × 4   | 512 × 8  | 256 × 16 | 512 × 9  | 256 × 18 |

| 4K × 1             | <b>✓</b>                                                | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |

| 2K × 2             | ✓                                                       | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |

| 1K × 4             | ✓                                                       | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |

| 512 × 8            | ✓                                                       | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |

| 256 × 16           | ✓                                                       | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |

| 512 × 9            |                                                         |          |          |          |          | <b>✓</b> | <b>✓</b> |

| 256 × 18           |                                                         |          |          |          |          | <b>✓</b> | <b>✓</b> |

When the M4K RAM block is configured as a shift register block, you can create a shift register up to 4,608 bits ( $w \times m \times n$ ).

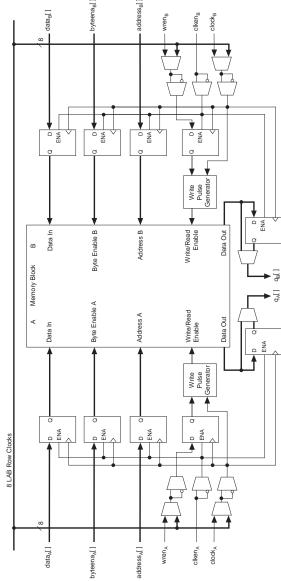

Figure 2–24. Independent Clock Mode Notes (1), (2)

Notes to Figure 2-24

- (1) All registers shown have asynchronous clear ports.

- (2) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

# **Input/Output Clock Mode**

Input/output clock mode can be implemented for both the true and simple dual-port memory modes. On each of the two ports, A or B, one clock controls all registers for inputs into the memory block: data input, wren, and address. The other clock controls the block's data output registers. Each memory block port, A or B, also supports independent clock enables and asynchronous clear signals for input and output registers. Figures 2–25 and 2–26 show the memory block in input/output clock mode.

Figure 2-41. DSP Block Interface to Interconnect

A bus of 18 control signals feeds the entire DSP block. These signals include clock[0..3] clocks, aclr[0..3] asynchronous clears, ena[1..4] clock enables, signa, signb signed/unsigned control signals, addnsub1 and addnsub3 addition and subtraction control signals, and accum sload[0..1] accumulator synchronous loads. The

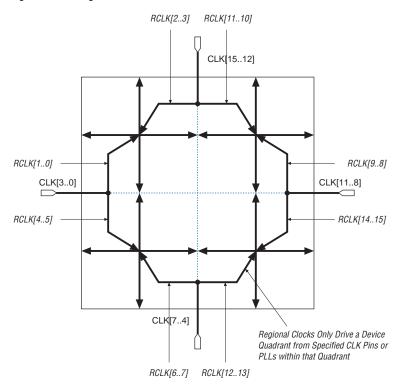

Figure 2-43. Regional Clocks

### Fast Regional Clock Network

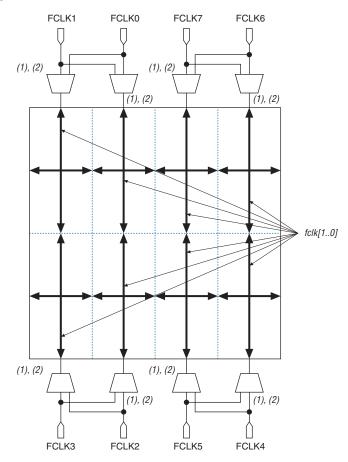

In EP1S25, EP1S20, and EP1S10 devices, there are two fast regional clock networks, FCLK [1..0], within each quadrant, fed by input pins that can connect to fast regional clock networks (see Figure 2–44). In EP1S30 and larger devices, there are two fast regional clock networks within each half-quadrant (see Figure 2–45). Dual-purpose FCLK pins drive the fast clock networks. All devices have eight FCLK pins to drive fast regional clock networks. Any I/O pin can drive a clock or control signal onto any fast regional clock network with the addition of a delay. This signal is driven via the I/O interconnect. The fast regional clock networks can also be driven from internal logic elements.

Figure 2–45. EP1S30 Device Fast Regional Clock Pin Connections to Fast Regional Clocks

Notes to Figure 2-45:

- (1) This is a set of two multiplexers.

- (2) In addition to the FCLK pin inputs, there is also an input from the I/O interconnect.

#### Combined Resources

Within each region, there are 22 distinct dedicated clocking resources consisting of 16 global clock lines, four regional clock lines, and two fast regional clock lines. Multiplexers are used with these clocks to form eight bit busses to drive LAB row clocks, column IOE clocks, or row IOE clocks. Another multiplexer is used at the LAB level to select two of the eight row clocks to feed the LE registers within the LAB. See Figure 2–46.

The variation due to process, voltage, and temperature is about ±15% on the delay settings. PLL reconfiguration can control the clock delay shift elements, but not the VCO phase shift multiplexers, during system operation.

#### Spread-Spectrum Clocking

Stratix device enhanced PLLs use spread-spectrum technology to reduce electromagnetic interference generation from a system by distributing the energy over a broader frequency range. The enhanced PLL typically provides 0.5% down spread modulation using a triangular profile. The modulation frequency is programmable. Enabling spread-spectrum for a PLL affects all of its outputs.

#### Lock Detect

The lock output indicates that there is a stable clock output signal in phase with the reference clock. Without any additional circuitry, the lock signal may toggle as the PLL begins tracking the reference clock. You may need to gate the lock signal for use as a system control. The lock signal from the locked port can drive the logic array or an output pin.

Whenever the PLL loses lock (for example, inclk jitter, clock switchover, PLL reconfiguration, power supply noise, and so on), the PLL must be reset with the areset signal to guarantee correct phase relationship between the PLL output clocks. If the phase relationship between the input clock versus output clock, and between different output clocks from the PLL is not important in the design, then the PLL need not be reset.

See the *Stratix FPGA Errata Sheet* for more information on implementing the gated lock signal in a design.

#### Programmable Duty Cycle

The programmable duty cycle allows enhanced PLLs to generate clock outputs with a variable duty cycle. This feature is supported on each enhanced PLL post-scale counter (*g*0..*g*3, *l*0..*l*3, *e*0..*e*3). The duty cycle setting is achieved by a low and high time count setting for the post-scale dividers. The Quartus II software uses the frequency input and the required multiply or divide rate to determine the duty cycle choices.

#### Advanced Clear & Enable Control

There are several control signals for clearing and enabling PLLs and their outputs. You can use these signals to control PLL resynchronization and gate PLL output clocks for low-power applications.

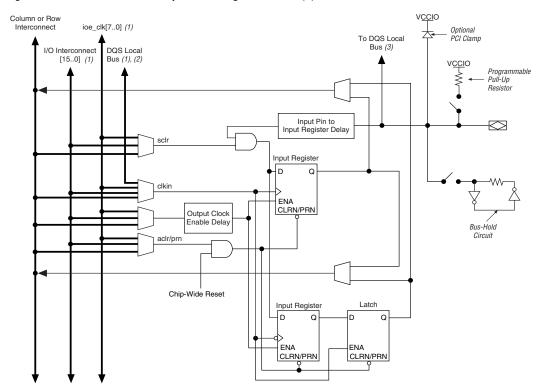

Figure 2–65. Stratix IOE in DDR Input I/O Configuration Note (1)

*Notes to Figure 2–65:*

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) This signal connection is only allowed on dedicated DQ function pins.

- (3) This signal is for dedicated DQS function pins only.

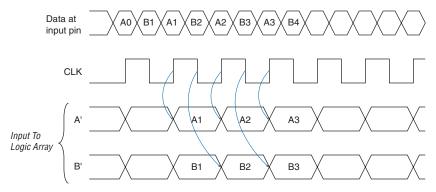

Figure 2-66. Input Timing Diagram in DDR Mode

When using the IOE for DDR outputs, the two output registers are configured to clock two data paths from LEs on rising clock edges. These output registers are multiplexed by the clock to drive the output pin at a  $\times 2$  rate. One output register clocks the first bit out on the clock high time, while the other output register clocks the second bit out on the clock low time. Figure 2–67 shows the IOE configured for DDR output. Figure 2–68 shows the DDR output timing diagram.

| Table 2-27. | Table 2–27. DQS & DQ Bus Mode Support (Part 2 of 2) Note (1)    |                        |                         |                         |  |  |

|-------------|-----------------------------------------------------------------|------------------------|-------------------------|-------------------------|--|--|

| Device      | Package                                                         | Number of ×8<br>Groups | Number of ×16<br>Groups | Number of ×32<br>Groups |  |  |

| EP1S25      | 672-pin BGA<br>672-pin FineLine BGA                             | 16 (3)                 | 8                       | 4                       |  |  |

|             | 780-pin FineLine BGA<br>1,020-pin FineLine BGA                  | 20                     | 8                       | 4                       |  |  |

| EP1S30      | 956-pin BGA<br>780-pin FineLine BGA<br>1,020-pin FineLine BGA   | 20                     | 8                       | 4                       |  |  |

| EP1S40      | 956-pin BGA<br>1,020-pin FineLine BGA<br>1,508-pin FineLine BGA | 20                     | 8                       | 4                       |  |  |

| EP1S60      | 956-pin BGA<br>1,020-pin FineLine BGA<br>1,508-pin FineLine BGA | 20                     | 8                       | 4                       |  |  |

| EP1S80      | 956-pin BGA<br>1,508-pin FineLine BGA<br>1,923-pin FineLine BGA | 20                     | 8                       | 4                       |  |  |

#### *Notes to Table 2–27:*

- See the Selectable I/O Standards in Stratix & Stratix GX Devices chapter in the Stratix Device Handbook, Volume 2 for V<sub>RFF</sub> guidelines.

- (2) These packages have six groups in I/O banks 3 and 4 and six groups in I/O banks 7 and 8.

- (3) These packages have eight groups in I/O banks 3 and 4 and eight groups in I/O banks 7 and 8.

- (4) This package has nine groups in I/O banks 3 and 4 and nine groups in I/O banks 7 and 8.

- (5) These packages have three groups in I/O banks 3 and 4 and four groups in I/O banks 7 and 8.

A compensated delay element on each DQS pin automatically aligns input DQS synchronization signals with the data window of their corresponding DQ data signals. The DQS signals drive a local DQS bus in the top and bottom I/O banks. This DQS bus is an additional resource to the I/O clocks and is used to clock DQ input registers with the DQS signal.

Two separate single phase-shifting reference circuits are located on the top and bottom of the Stratix device. Each circuit is driven by a system reference clock through the CLK pins that is the same frequency as the DQS signal. Clock pins CLK [15..12] p feed the phase-shift circuitry on the top of the device and clock pins CLK [7..4] p feed the phase-shift circuitry on the bottom of the device. The phase-shifting reference circuit on the top of the device controls the compensated delay elements for all 10 DQS pins located at the top of the device. The phase-shifting reference circuit on the bottom of the device controls the compensated delay elements for all 10 DQS pins located on the bottom of the device. All 10 delay elements (DQS signals) on either the top or bottom of the device

The transmitter external clock output is transmitted on a data channel. The txclk pin for each bank is located in between data transmitter pins. For  $\times 1$  clocks (e.g., 622 Mbps, 622 MHz), the high-speed PLL clock bypasses the SERDES to drive the output pins. For half-rate clocks (e.g., 622 Mbps, 311 MHz) or any other even-numbered factor such as 1/4, 1/7, 1/8, or 1/10, the SERDES automatically generates the clock in the Ouartus II software.

For systems that require more than four or eight high-speed differential I/O clock domains, a SERDES bypass implementation is possible using IOEs.

## **Byte Alignment**

For high-speed source synchronous interfaces such as POS-PHY 4, XSBI, RapidIO, and HyperTransport technology, the source synchronous clock rate is not a byte- or SERDES-rate multiple of the data rate. Byte alignment is necessary for these protocols since the source synchronous clock does not provide a byte or word boundary since the clock is one half the data rate, not one eighth. The Stratix device's high-speed differential I/O circuitry provides dedicated data realignment circuitry for user-controlled byte boundary shifting. This simplifies designs while saving LE resources. An input signal to each fast PLL can stall deserializer parallel data outputs by one bit period. You can use an LE-based state machine to signal the shift of receiver byte boundaries until a specified pattern is detected to indicate byte alignment.

# Power Sequencing & Hot Socketing

Because Stratix devices can be used in a mixed-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. Therefore, the VCCIO and VCCINT power supplies may be powered in any order.

Although you can power up or down the VCCIO and VCCINT power supplies in any sequence, you should not power down any I/O banks that contain configuration pins while leaving other I/O banks powered on. For power up and power down, all supplies (VCCINT and all VCCIO power planes) must be powered up and down within 100 ms of each other. This prevents I/O pins from driving out.

Signals can be driven into Stratix devices before and during power up without damaging the device. In addition, Stratix devices do not drive out during power up. Once operating conditions are reached and the device is configured, Stratix devices operate as specified by the user. For more information, see *Hot Socketing* in the *Selectable I/O Standards in Stratix & Stratix GX Devices* chapter in the *Stratix Device Handbook*, *Volume 2*.

| JTAG Instruction          | Instruction Code | Description                                                                                                                                                                                                                                                                                                                                        |

|---------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SAMPLE/PRELOAD            | 00 0000 0101     | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins. Also used by the SignalTap II embedded logic analyzer.                                                                                                            |

| EXTEST (1)                | 00 0000 0000     | Allows the external circuitry and board-level interconnects to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                                                                                                                                                |

| BYPASS                    | 11 1111 1111     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation.                                                                                                                                                        |

| USERCODE                  | 00 0000 0111     | Selects the 32-bit USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                                                                                                                                                          |

| IDCODE                    | 00 0000 0110     | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                                                                                                                                              |

| HIGHZ (1)                 | 00 0000 1011     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation, while tri-stating all of the I/O pins.                                                                                                                 |

| CLAMP (1)                 | 00 0000 1010     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation while holding I/O pins to a state defined by the data in the boundary-scan register.                                                                    |

| ICR instructions          |                  | Used when configuring an Stratix device via the JTAG port with a MasterBlaster™, ByteBlasterMV™, or ByteBlaster™ II download cable, or when using a Jam File or Jam Byte-Code File via an embedded processor or JRunner.                                                                                                                           |

| PULSE_NCONFIG             | 00 0000 0001     | Emulates pulsing the nCONFIG pin low to trigger reconfiguration even though the physical pin is unaffected.                                                                                                                                                                                                                                        |

| CONFIG_IO                 | 00 0000 1101     | Allows configuration of I/O standards through the JTAG chain for JTAG testing. Can be executed before, after, or during configuration. Stops configuration if executed during configuration. Once issued, the CONFIG_IO instruction will hold nSTATUS low to reset the configuration device. nSTATUS is held low until the device is reconfigured. |

| SignalTap II instructions |                  | Monitors internal device operation with the SignalTap II embedded logic analyzer.                                                                                                                                                                                                                                                                  |

### Note to Table 3–1:

(1) Bus hold and weak pull-up resistor features override the high-impedance state of HIGHZ, CLAMP, and EXTEST.

Table 4–52 shows the external I/O timing parameters when using fast regional clock networks.

|                    | <b>Table 4–52. Stratix Fast Regional Clock External I/O Timing Parameters</b> Notes (1), (2)                         |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol             | Parameter                                                                                                            |  |  |  |  |

| t <sub>INSU</sub>  | Setup time for input or bidirectional pin using IOE input register with fast regional clock fed by FCLK pin          |  |  |  |  |

| t <sub>INH</sub>   | Hold time for input or bidirectional pin using IOE input register with fast regional clock fed by FCLK pin           |  |  |  |  |

| t <sub>outco</sub> | Clock-to-output delay output or bidirectional pin using IOE output register with fast regional clock fed by FCLK pin |  |  |  |  |

| t <sub>XZ</sub>    | Synchronous IOE output enable register to output pin disable delay using fast regional clock fed by FCLK pin         |  |  |  |  |

| t <sub>ZX</sub>    | Synchronous IOE output enable register to output pin enable delay using fast regional clock fed by FCLK pin          |  |  |  |  |

Notes to Table 4-52:

- (1) These timing parameters are sample-tested only.

- (2) These timing parameters are for column and row IOE pins. You should use the Quartus II software to verify the external timing for any pin.

Table 4–53 shows the external I/O timing parameters when using regional clock networks.

| Symbol                | Parameter                                                                                                                               |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>INSU</sub>     | Setup time for input or bidirectional pin using IOE input register with regional clock fed by CLK pin                                   |

| t <sub>INH</sub>      | Hold time for input or bidirectional pin using IOE input register with regional clock fed by CLK pin                                    |

| t <sub>OUTCO</sub>    | Clock-to-output delay output or bidirectional pin using IOE output register with regional clock fed by CLK pin                          |

| t <sub>INSUPLL</sub>  | Setup time for input or bidirectional pin using IOE input register with regional clock fed by Enhanced PLL with default phase setting   |

| t <sub>INHPLL</sub>   | Hold time for input or bidirectional pin using IOE input register with regional clock fed by Enhanced PLL with default phase setting    |

| t <sub>OUTCOPLL</sub> | Clock-to-output delay output or bidirectional pin using IOE output register with regional clock Enhanced PLL with default phase setting |

| Table 4–97. Output Pin Timing Skew Definitions (Part 2 of 2) |                                                                       |  |  |  |

|--------------------------------------------------------------|-----------------------------------------------------------------------|--|--|--|

| Symbol Definition                                            |                                                                       |  |  |  |

| t <sub>LR_HIO</sub>                                          | Across all HIO banks (1, 2, 5, 6); across four similar type I/O banks |  |  |  |

| t <sub>TB_VIO</sub>                                          | Across all VIO banks (3, 4, 7, 8); across four similar type I/O banks |  |  |  |

| t <sub>OVERALL</sub>                                         | Output timing skew for all I/O pins on the device.                    |  |  |  |

#### Notes to Table 4-97:

- (1) See Figure 4–5 on page 4–57.

- (2) See Figure 4–6 on page 4–58.

Table 4–98 shows the I/O skews when using the same global or regional clock to feed IOE registers in I/O banks around each device. These values can be used for calculating the timing budget on the output (write) side of a memory interface. These values already factor in the package skew.

| Table 4–98. Output Skew for Stratix by Device Density |                  |        |                 |  |  |  |  |  |  |  |

|-------------------------------------------------------|------------------|--------|-----------------|--|--|--|--|--|--|--|

| Symbol                                                | Skew (ps) (1)    |        |                 |  |  |  |  |  |  |  |

|                                                       | EP1S10 to EP1S30 | EP1S40 | EP1S60 & EP1S80 |  |  |  |  |  |  |  |

| t <sub>SB_HIO</sub>                                   | 90               | 290    | 500             |  |  |  |  |  |  |  |

| t <sub>SB_VIO</sub>                                   | 160              | 290    | 500             |  |  |  |  |  |  |  |

| t <sub>SS_HIO</sub>                                   | 90               | 460    | 600             |  |  |  |  |  |  |  |

| t <sub>SS_VIO</sub>                                   | 180              | 520    | 630             |  |  |  |  |  |  |  |

| t <sub>LR_HIO</sub>                                   | 150              | 490    | 600             |  |  |  |  |  |  |  |

| t <sub>TB_VIO</sub>                                   | 190              | 580    | 670             |  |  |  |  |  |  |  |

| t <sub>OVERALL</sub>                                  | 430              | 630    | 880             |  |  |  |  |  |  |  |

Note to Table 4-98:

(1) The skew numbers in Table 4–98 account for worst case package skews.

|                                       | Conditions                                                            | -6 Speed Grade |     | -7 Speed Grade |       |     | -8 Speed Grade |       |     |      |      |

|---------------------------------------|-----------------------------------------------------------------------|----------------|-----|----------------|-------|-----|----------------|-------|-----|------|------|

| Symbol                                |                                                                       | Min            | Тур | Max            | Min   | Тур | Max            | Min   | Тур | Max  | Unit |

| SW                                    | PCML (J = 4, 7, 8, 10) only                                           | 800            |     |                | 800   |     |                | 800   |     |      | ps   |

|                                       | PCML (J = 2) only                                                     | 1,200          |     |                | 1,200 |     |                | 1,200 |     |      | ps   |

|                                       | PCML (J = 1) only                                                     | 1,700          |     |                | 1,700 |     |                | 1,700 |     |      | ps   |

|                                       | LVDS and LVPECL (J = 1) only                                          | 550            |     |                | 550   |     |                | 550   |     |      | ps   |

|                                       | LVDS, LVPECL,<br>HyperTransport technology<br>(J = 2 through 10) only | 500            |     |                | 500   |     |                | 500   |     |      | ps   |

| Input jitter tolerance (peak-to-peak) | All                                                                   |                |     | 250            |       |     | 250            |       |     | 250  | ps   |

| Output jitter (peak-to-<br>peak)      | All                                                                   |                |     | 200            |       |     | 200            |       |     | 200  | ps   |

| Output t <sub>RISE</sub>              | LVDS                                                                  | 80             | 110 | 120            | 80    | 110 | 120            | 80    | 110 | 120  | ps   |

|                                       | HyperTransport technology                                             | 120            | 170 | 200            | 120   | 170 | 200            | 120   | 170 | 200  | ps   |

|                                       | LVPECL                                                                | 100            | 135 | 150            | 100   | 135 | 150            | 100   | 135 | 150  | ps   |

|                                       | PCML                                                                  | 80             | 110 | 135            | 80    | 110 | 135            | 80    | 110 | 135  | ps   |

| Output t <sub>FALL</sub>              | LVDS                                                                  | 80             | 110 | 120            | 80    | 110 | 120            | 80    | 110 | 120  | ps   |

|                                       | HyperTransport                                                        | 110            | 170 | 200            | 110   | 170 | 200            | 110   | 170 | 200  | ps   |

|                                       | LVPECL                                                                | 100            | 135 | 160            | 100   | 135 | 160            | 100   | 135 | 160  | ps   |

|                                       | PCML                                                                  | 110            | 145 | 175            | 110   | 145 | 175            | 110   | 145 | 175  | ps   |

| touty                                 | LVDS (J = 2 through10) only                                           | 47.5           | 50  | 52.5           | 47.5  | 50  | 52.5           | 47.5  | 50  | 52.5 | %    |

|                                       | LVDS (J =1) and LVPECL,<br>PCML, HyperTransport<br>technology         | 45             | 50  | 55             | 45    | 50  | 55             | 45    | 50  | 55   | %    |

| t <sub>LOCK</sub>                     | All                                                                   |                |     | 100            |       |     | 100            |       |     | 100  | μs   |

Table 4–126. High-Speed I/O Specifications for Wire-Bond Packages (Part 2 of 2)