Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 2566                                                     |

| Number of Logic Elements/Cells | 25660                                                    |

| Total RAM Bits                 | 1944576                                                  |

| Number of I/O                  | 473                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 672-BBGA                                                 |

| Supplier Device Package        | 672-FBGA (27x27)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s25f672c7n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Copyright © 2006 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published in

formation and before placing orders for products or services.

I.S. EN ISO 9001

ii Altera Corporation

With the LAB-wide addnsub control signal, a single LE can implement a one-bit adder and subtractor. This saves LE resources and improves performance for logic functions such as DSP correlators and signed multipliers that alternate between addition and subtraction depending on data.

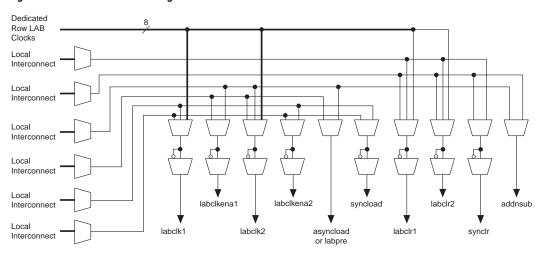

The LAB row clocks [7..0] and LAB local interconnect generate the LAB-wide control signals. The MultiTrack $^{\text{IM}}$  interconnect's inherent low skew allows clock and control signal distribution in addition to data. Figure 2–4 shows the LAB control signal generation circuit.

Figure 2-4. LAB-Wide Control Signals

# **Logic Elements**

The smallest unit of logic in the Stratix architecture, the LE, is compact and provides advanced features with efficient logic utilization. Each LE contains a four-input LUT, which is a function generator that can implement any function of four variables. In addition, each LE contains a programmable register and carry chain with carry select capability. A single LE also supports dynamic single bit addition or subtraction mode selectable by an LAB-wide control signal. Each LE drives all types of interconnects: local, row, column, LUT chain, register chain, and direct link interconnects. See Figure 2–5.

TriMatrix memory architecture can implement pipelined RAM by registering both the input and output signals to the RAM block. All TriMatrix memory block inputs are registered providing synchronous write cycles. In synchronous operation, the memory block generates its own self-timed strobe write enable (WREN) signal derived from the global or regional clock. In contrast, a circuit using asynchronous RAM must generate the RAM WREN signal while ensuring its data and address signals meet setup and hold time specifications relative to the WREN signal. The output registers can be bypassed. Flow-through reading is possible in the simple dual-port mode of M512 and M4K RAM blocks by clocking the read enable and read address registers on the negative clock edge and bypassing the output registers.

Two single-port memory blocks can be implemented in a single M4K block as long as each of the two independent block sizes is equal to or less than half of the M4K block size.

The Quartus II software automatically implements larger memory by combining multiple TriMatrix memory blocks. For example, two  $256 \times 16$ -bit RAM blocks can be combined to form a  $256 \times 32$ -bit RAM block. Memory performance does not degrade for memory blocks using the maximum number of words available in one memory block. Logical memory blocks using less than the maximum number of words use physical blocks in parallel, eliminating any external control logic that would increase delays. To create a larger high-speed memory block, the Quartus II software automatically combines memory blocks with LE control logic.

# Clear Signals

When applied to input registers, the asynchronous clear signal for the TriMatrix embedded memory immediately clears the input registers. However, the output of the memory block does not show the effects until the next clock edge. When applied to output registers, the asynchronous clear signal clears the output registers and the effects are seen immediately.

## **Parity Bit Support**

The memory blocks support a parity bit for each byte. The parity bit, along with internal LE logic, can implement parity checking for error detection to ensure data integrity. You can also use parity-size data words to store user-specified control bits. In the M4K and M-RAM blocks, byte enables are also available for data input masking during write operations.

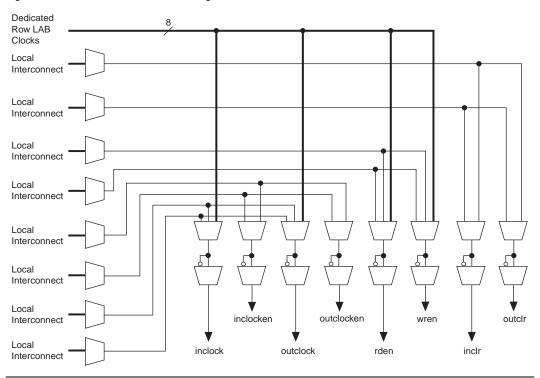

Figure 2-15. M512 RAM Block Control Signals

Table 2–19 shows the enhanced PLL and fast PLL features in Stratix devices.

| Feature                           | Enhanced PLL                                                    | Fast PLL                           |

|-----------------------------------|-----------------------------------------------------------------|------------------------------------|

| Clock multiplication and division | $m/(n \times post-scale counter)$ (1)                           | m/(post-scale counter) (2)         |

| Phase shift                       | Down to 156.25-ps increments (3), (4)                           | Down to 125-ps increments (3), (4) |

| Delay shift                       | 250-ps increments for ±3 ns                                     |                                    |

| Clock switchover                  | <b>✓</b>                                                        |                                    |

| PLL reconfiguration               | <b>✓</b>                                                        |                                    |

| Programmable bandwidth            | <b>✓</b>                                                        |                                    |

| Spread spectrum clocking          | ✓                                                               |                                    |

| Programmable duty cycle           | <b>✓</b>                                                        | ✓                                  |

| Number of internal clock outputs  | 6                                                               | 3 (5)                              |

| Number of external clock outputs  | Four differential/eight singled-ended or one single-ended $(6)$ | (7)                                |

| Number of feedback clock inputs   | 2 (8)                                                           |                                    |

#### Notes to Table 2-19:

- (1) For enhanced PLLs, *m*, *n*, range from 1 to 512 and post-scale counters *g*, *l*, *e* range from 1 to 1024 with 50% duty cycle. With a non-50% duty cycle the post-scale counters *g*, *l*, *e* range from 1 to 512.

- (2) For fast PLLs, *m* and post-scale counters range from 1 to 32.

- (3) The smallest phase shift is determined by the voltage controlled oscillator (VCO) period divided by 8.

- (4) For degree increments, Stratix devices can shift all output frequencies in increments of at least 45°. Smaller degree increments are possible depending on the frequency and divide parameters.

- (5) PLLs 7, 8, 9, and 10 have two output ports per PLL. PLLs 1, 2, 3, and 4 have three output ports per PLL.

- (6) Every Stratix device has two enhanced PLLs (PLLs 5 and 6) with either eight single-ended outputs or four differential outputs each. Two additional enhanced PLLs (PLLs 11 and 12) in EPIS80, EPIS60, and EPIS40 devices each have one single-ended output. Devices in the 780 pin FineLine BGA packages do not support PLLs 11 and 12.

- (7) Fast PLLs can drive to any I/O pin as an external clock. For high-speed differential I/O pins, the device uses a data channel to generate txclkout.

- (8) Every Stratix device has two enhanced PLLs with one single-ended or differential external feedback input per PLL.

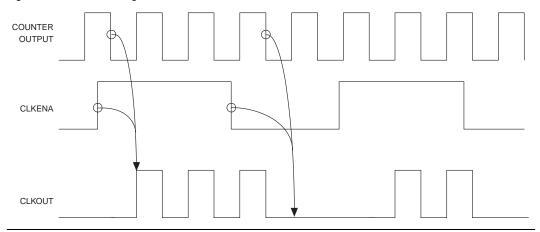

resynchronization or relock period. The clkena signal can also disable clock outputs if the system is not tolerant to frequency overshoot during resynchronization.

The extclkena signals work in the same way as the clkena signals, but they control the external clock output counters (e0, e1, e2, and e3). Upon re-enabling, the PLL does not need a resynchronization or relock period unless the PLL is using external feedback mode. In order to lock in external feedback mode, the external output must drive the board trace back to the FBIN pin.

Figure 2-57. extclkena Signals

## **Fast PLLs**

Stratix devices contain up to eight fast PLLs with high-speed serial interfacing ability, along with general-purpose features. Figure 2–58 shows a diagram of the fast PLL.

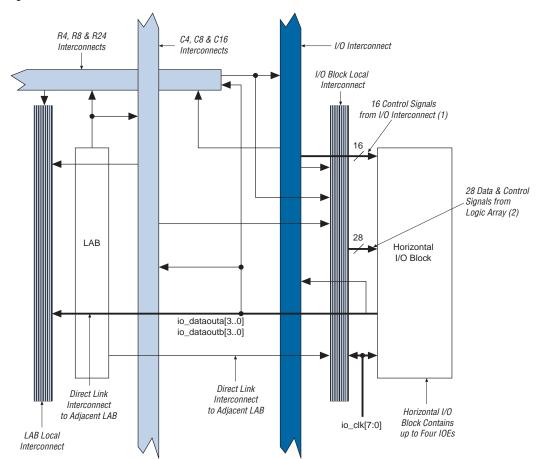

Figure 2-60. Row I/O Block Connection to the Interconnect

#### *Notes to Figure 2–60:*

- (1) The 16 control signals are composed of four output enables io\_boe[3..0], four clock enables io\_boe[3..0], four clocks io\_clk[3..0], and four clear signals io\_bclr[3..0].

- (2) The 28 data and control signals consist of eight data out lines: four lines each for DDR applications io\_dataouta[3..0] and io\_dataoutb[3..0], four output enables io\_coe[3..0], four input clock enables io\_cce\_in[3..0], four output clock enables io\_cce\_out[3..0], four clocks io\_cclk[3..0], and four clear signals io\_cclr[3..0].

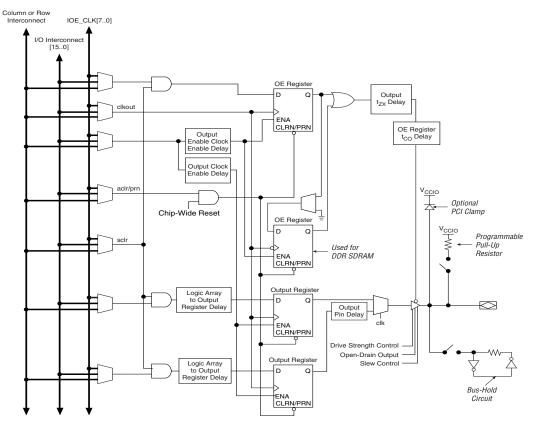

Stratix devices have an I/O interconnect similar to the R4 and C4 interconnect to drive high-fanout signals to and from the I/O blocks. There are 16 signals that drive into the I/O blocks composed of four output enables <code>io\_boe[3..0]</code>, four clock enables <code>io\_bce[3..0]</code>, four clocks <code>io\_bclk[3..0]</code>, and four clear signals <code>io\_bclr[3..0]</code>. The pin's <code>datain</code> signals can drive the IO interconnect, which in turn drives the logic array or other I/O blocks. In addition, the control and data signals can be driven from the logic array, providing a slower but more flexible routing resource. The row or column IOE clocks, <code>io\_clk[7..0]</code>, provide a dedicated routing resource for low-skew, high-speed clocks. I/O clocks are generated from regional, global, or fast regional clocks (see "PLLs & Clock Networks" on page 2–73). Figure 2–62 illustrates the signal paths through the I/O block.

Row or Column io\_clk[7..0] io\_boe[3..0] To Other io\_bce[3..0] 10Es From I/O Interconnect io\_bclk[3..0] io\_bclr[3..0] io\_datain0 To Logic Array io datain1 ◀ oe ce\_in ce\_out io coe Control IOE aclr/apreset io cce in Signal Selection sclr/spreset io cce out clk in From Logic io\_cclr Array clk out io\_cclk io\_dataout0 io\_dataout1

Figure 2-62. Signal Path through the I/O Block

Figure 2–67. Stratix IOE in DDR Output I/O Configuration Notes (1), (2)

*Notes to Figure 2–67:*

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) The tristate is by default active high. It can, however, be designed to be active low.

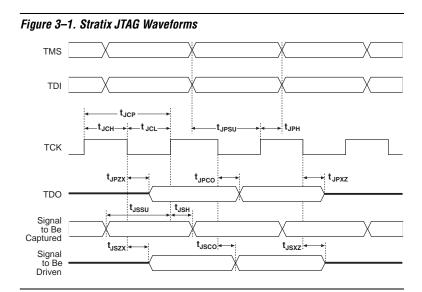

Figure 3–1 shows the timing requirements for the JTAG signals.

Table 3–4 shows the JTAG timing parameters and values for Stratix devices.

| Table 3–4. Stratix JTAG Timing Parameters & Values |                                                |     |     |      |  |  |  |

|----------------------------------------------------|------------------------------------------------|-----|-----|------|--|--|--|

| Symbol                                             | Parameter                                      | Min | Max | Unit |  |  |  |

| t <sub>JCP</sub>                                   | TCK clock period                               | 100 |     | ns   |  |  |  |

| t <sub>JCH</sub>                                   | TCK clock high time                            | 50  |     | ns   |  |  |  |

| t <sub>JCL</sub>                                   | TCK clock low time                             | 50  |     | ns   |  |  |  |

| t <sub>JPSU</sub>                                  | JTAG port setup time                           | 20  |     | ns   |  |  |  |

| t <sub>JPH</sub>                                   | JTAG port hold time                            | 45  |     | ns   |  |  |  |

| t <sub>JPCO</sub>                                  | JTAG port clock to output                      |     | 25  | ns   |  |  |  |

| t <sub>JPZX</sub>                                  | JTAG port high impedance to valid output       |     | 25  | ns   |  |  |  |

| t <sub>JPXZ</sub>                                  | JTAG port valid output to high impedance       |     | 25  | ns   |  |  |  |

| t <sub>JSSU</sub>                                  | Capture register setup time                    | 20  |     | ns   |  |  |  |

| t <sub>JSH</sub>                                   | Capture register hold time                     | 45  |     | ns   |  |  |  |

| t <sub>JSCO</sub>                                  | Update register clock to output                |     | 35  | ns   |  |  |  |

| t <sub>JSZX</sub>                                  | Update register high impedance to valid output |     | 35  | ns   |  |  |  |

| t <sub>JSXZ</sub>                                  | Update register valid output to high impedance |     | 35  | ns   |  |  |  |

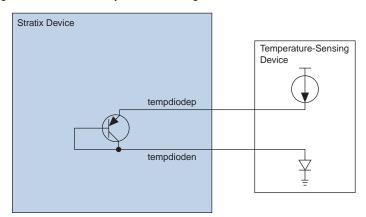

Figure 3-5. External Temperature-Sensing Diode

Table 3–6 shows the specifications for bias voltage and current of the Stratix temperature sensing diode.

| Table 3–6. Temperature-Sensing Diode Electrical Characteristics |     |     |     |    |  |  |  |

|-----------------------------------------------------------------|-----|-----|-----|----|--|--|--|

| Parameter Minimum Typical Maximum Unit                          |     |     |     |    |  |  |  |

| I <sub>BIAS</sub> high                                          | 80  | 100 | 120 | μΑ |  |  |  |

| I <sub>BIAS</sub> low                                           | 8   | 10  | 12  | μΑ |  |  |  |

| $V_{BP} - V_{BN}$                                               | 0.3 |     | 0.9 | V  |  |  |  |

| V <sub>BN</sub>                                                 |     | 0.7 |     | V  |  |  |  |

| Series resistance                                               |     |     | 3   | W  |  |  |  |

| Table 4–22. SSTL-3 Class I Specifications (Part 2 of 2) |           |                               |                       |         |                        |      |

|---------------------------------------------------------|-----------|-------------------------------|-----------------------|---------|------------------------|------|

| Symbol                                                  | Parameter | Conditions                    | Minimum               | Typical | Maximum                | Unit |

| V <sub>IL(AC)</sub> Low-level AC input voltage          |           |                               |                       |         | V <sub>REF</sub> - 0.4 | V    |

| V <sub>OH</sub> High-level output voltage               |           | $I_{OH} = -8 \text{ mA } (3)$ | V <sub>TT</sub> + 0.6 |         |                        | V    |

| V <sub>OL</sub> Low-level output voltage                |           | I <sub>OL</sub> = 8 mA (3)    |                       |         | V <sub>TT</sub> – 0.6  | V    |

| Table 4–23. SSTL-3 Class II Specifications |                             |                                |                         |           |                         |      |  |  |

|--------------------------------------------|-----------------------------|--------------------------------|-------------------------|-----------|-------------------------|------|--|--|

| Symbol                                     | Parameter                   | Conditions                     | Minimum                 | Typical   | Maximum                 | Unit |  |  |

| V <sub>CCIO</sub>                          | Output supply voltage       |                                | 3.0                     | 3.3       | 3.6                     | V    |  |  |

| V <sub>TT</sub>                            | Termination voltage         |                                | V <sub>REF</sub> - 0.05 | $V_{REF}$ | V <sub>REF</sub> + 0.05 | V    |  |  |

| V <sub>REF</sub>                           | Reference voltage           |                                | 1.3                     | 1.5       | 1.7                     | V    |  |  |

| V <sub>IH(DC)</sub>                        | High-level DC input voltage |                                | V <sub>REF</sub> + 0.2  |           | V <sub>CCIO</sub> + 0.3 | V    |  |  |

| V <sub>IL(DC)</sub>                        | Low-level DC input voltage  |                                | -0.3                    |           | V <sub>REF</sub> - 0.2  | V    |  |  |

| V <sub>IH(AC)</sub>                        | High-level AC input voltage |                                | V <sub>REF</sub> + 0.4  |           |                         | V    |  |  |

| V <sub>IL(AC)</sub>                        | Low-level AC input voltage  |                                |                         |           | V <sub>REF</sub> - 0.4  | V    |  |  |

| V <sub>OH</sub>                            | High-level output voltage   | $I_{OH} = -16 \text{ mA } (3)$ | V <sub>TT</sub> + 0.8   |           |                         | V    |  |  |

| V <sub>OL</sub>                            | Low-level output voltage    | I <sub>OL</sub> = 16 mA (3)    |                         |           | V <sub>TT</sub> – 0.8   | V    |  |  |

| Table 4–24. 3.3-V AGP 2× Specifications |                              |                             |                         |         |                         |      |  |

|-----------------------------------------|------------------------------|-----------------------------|-------------------------|---------|-------------------------|------|--|

| Symbol                                  | Parameter                    | Conditions                  | Minimum                 | Typical | Maximum                 | Unit |  |

| $V_{CCIO}$                              | Output supply voltage        |                             | 3.15                    | 3.3     | 3.45                    | V    |  |

| $V_{REF}$                               | Reference voltage            |                             | $0.39 \times V_{CCIO}$  |         | $0.41 \times V_{CCIO}$  | V    |  |

| V <sub>IH</sub>                         | High-level input voltage (4) |                             | $0.5 \times V_{CCIO}$   |         | V <sub>CCIO</sub> + 0.5 | V    |  |

| V <sub>IL</sub>                         | Low-level input voltage (4)  |                             |                         |         | $0.3 \times V_{CCIO}$   | V    |  |

| V <sub>OH</sub>                         | High-level output voltage    | $I_{OUT} = -0.5 \text{ mA}$ | 0.9 × V <sub>CCIO</sub> |         | 3.6                     | V    |  |

| V <sub>OL</sub>                         | Low-level output voltage     | I <sub>OUT</sub> = 1.5 mA   |                         |         | 0.1 × V <sub>CCIO</sub> | V    |  |

| Table 4–25. 3.3-V AGP 1× Specifications (Part 1 of 2) |                              |         |                       |         |                         |   |  |

|-------------------------------------------------------|------------------------------|---------|-----------------------|---------|-------------------------|---|--|

| Symbol                                                | Parameter                    | Minimum | Typical               | Maximum | Unit                    |   |  |

| V <sub>CCIO</sub>                                     | Output supply voltage        |         | 3.15                  | 3.3     | 3.45                    | V |  |

| V <sub>IH</sub>                                       | High-level input voltage (4) |         | $0.5 \times V_{CCIO}$ |         | V <sub>CCIO</sub> + 0.5 | V |  |

| V <sub>IL</sub>                                       | Low-level input voltage (4)  |         |                       |         | 0.3 × V <sub>CCIO</sub> | V |  |

| Table 4–36. Stratix Performance (Part 2 of 2) Notes (1), (2) |                                      |     |             |               |                      |                      |                      |                      |       |

|--------------------------------------------------------------|--------------------------------------|-----|-------------|---------------|----------------------|----------------------|----------------------|----------------------|-------|

|                                                              |                                      | F   | Resources L | Jsed          | Performance          |                      |                      |                      |       |

|                                                              | Applications                         |     |             | DSP<br>Blocks | -5<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade | Units |

| TriMatrix<br>memory                                          | True dual-port<br>RAM 16K × 36 bit   | 0   | 1           | 0             | 269.83               | 237.69               | 206.82               | 175.74               | MHz   |

| M-RAM<br>block                                               | Single port<br>RAM 32K × 18 bit      | 0   | 1           | 0             | 275.86               | 244.55               | 212.76               | 180.83               | MHz   |

|                                                              | Simple dual-port<br>RAM 32K × 18 bit | 0   | 1           | 0             | 275.86               | 244.55               | 212.76               | 180.83               | MHz   |

|                                                              | True dual-port<br>RAM 32K × 18 bit   | 0   | 1           | 0             | 275.86               | 244.55               | 212.76               | 180.83               | MHz   |

|                                                              | Single port<br>RAM 64K × 9 bit       | 0   | 1           | 0             | 287.85               | 253.29               | 220.36               | 187.26               | MHz   |

|                                                              | Simple dual-port<br>RAM 64K × 9 bit  | 0   | 1           | 0             | 287.85               | 253.29               | 220.36               | 187.26               | MHz   |

|                                                              | True dual-port<br>RAM 64K × 9 bit    | 0   | 1           | 0             | 287.85               | 253.29               | 220.36               | 187.26               | MHz   |

| DSP block                                                    | 9 × 9-bit multiplier (3)             | 0   | 0           | 1             | 335.0                | 293.94               | 255.68               | 217.24               | MHz   |

|                                                              | 18 × 18-bit multiplier (4)           | 0   | 0           | 1             | 278.78               | 237.41               | 206.52               | 175.50               | MHz   |

|                                                              | $36 \times 36$ -bit multiplier (4)   | 0   | 0           | 1             | 148.25               | 134.71               | 117.16               | 99.59                | MHz   |

|                                                              | 36 × 36-bit multiplier (5)           | 0   | 0           | 1             | 278.78               | 237.41               | 206.52               | 175.5                | MHz   |

|                                                              | 18-bit, 4-tap FIR filter             | 0   | 0           | 1             | 278.78               | 237.41               | 206.52               | 175.50               | MHz   |

| Larger<br>Designs                                            | 8-bit, 16-tap parallel<br>FIR filter | 58  | 0           | 4             | 141.26               | 133.49               | 114.88               | 100.28               | MHz   |

|                                                              | 8-bit, 1,024-point FFT function      | 870 | 5           | 1             | 261.09               | 235.51               | 205.21               | 175.22               | MHz   |

### Notes to Table 4–36:

- (1) These design performance numbers were obtained using the Quartus II software.

- (2) Numbers not listed will be included in a future version of the data sheet.

- (3) This application uses registered inputs and outputs.

- (4) This application uses registered multiplier input and output stages within the DSP block.

- (5) This application uses registered multiplier input, pipeline, and output stages within the DSP block.

| Table 4–39. DSP              | Block Internal Timing Microparameter Descriptions                                                                                                                                                                                                                                                                                                         |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                       | Parameter                                                                                                                                                                                                                                                                                                                                                 |

| t <sub>SU</sub>              | Input, pipeline, and output register setup time before clock                                                                                                                                                                                                                                                                                              |

| t <sub>H</sub>               | Input, pipeline, and output register hold time after clock                                                                                                                                                                                                                                                                                                |

| t <sub>co</sub>              | Input, pipeline, and output register clock-to-output delay                                                                                                                                                                                                                                                                                                |

| t <sub>INREG2PIPE9</sub>     | Input Register to DSP Block pipeline register in $9\times9$ -bit mode                                                                                                                                                                                                                                                                                     |

| t <sub>INREG2PIPE18</sub>    | Input Register to DSP Block pipeline register in 18 $\times$ 18-bit mode                                                                                                                                                                                                                                                                                  |

| t <sub>PIPE2OUTREG2ADD</sub> | DSP Block Pipeline Register to output register delay in Two-Multipliers Adder mode                                                                                                                                                                                                                                                                        |

| t <sub>PIPE2OUTREG4ADD</sub> | DSP Block Pipeline Register to output register delay in Four-Multipliers Adder mode                                                                                                                                                                                                                                                                       |

| t <sub>PD9</sub>             | Combinatorial input to output delay for $9 \times 9$                                                                                                                                                                                                                                                                                                      |

| t <sub>PD18</sub>            | Combinatorial input to output delay for 18 × 18                                                                                                                                                                                                                                                                                                           |

| t <sub>PD36</sub>            | Combinatorial input to output delay for $36 \times 36$                                                                                                                                                                                                                                                                                                    |

| t <sub>CLR</sub>             | Minimum clear pulse width                                                                                                                                                                                                                                                                                                                                 |

| t <sub>CLKHL</sub>           | Register minimum clock high or low time. This is a limit on the min time for the clock on the registers in these blocks. The actual performance is dependent upon the internal point-to-point delays in the blocks and may give slower performance as shown in Table 4–36 on page 4–20 and as reported by the timing analyzer in the Quartus II software. |

| Table 4–53. Stratix Regional Clock External I/O Ti | iming Parameters (Part 2 |

|----------------------------------------------------|--------------------------|

| <b>of 2)</b> Notes (1), (2)                        |                          |

|                                                    |                          |

| Symbol             | Parameter                                                                                                                              |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>XZPLL</sub> | Synchronous IOE output enable register to output pin disable delay using regional clock fed by Enhanced PLL with default phase setting |

| t <sub>ZXPLL</sub> | Synchronous IOE output enable register to output pin enable delay using regional clock fed by Enhanced PLL with default phase setting  |

#### *Notes to Table 4–53:*

- (1) These timing parameters are sample-tested only.

- (2) These timing parameters are for column and row IOE pins. You should use the Quartus II software to verify the external timing for any pin.

Table 4–54 shows the external I/O timing parameters when using global clock networks.

| <b>Table 4–3</b> (2)  | <b>Table 4–54. Stratix Global Clock External I/O Timing Parameters</b> Notes (1), (2)                                                 |  |  |  |  |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Symbol                | Parameter                                                                                                                             |  |  |  |  |  |  |

| t <sub>INSU</sub>     | Setup time for input or bidirectional pin using IOE input register with global clock fed by ${\tt CLK}$ pin                           |  |  |  |  |  |  |

| t <sub>INH</sub>      | Hold time for input or bidirectional pin using IOE input register with global clock fed by ${\tt CLK}$ pin                            |  |  |  |  |  |  |

| t <sub>OUTCO</sub>    | Clock-to-output delay output or bidirectional pin using IOE output register with global clock fed by CLK pin                          |  |  |  |  |  |  |

| t <sub>INSUPLL</sub>  | Setup time for input or bidirectional pin using IOE input register with global clock fed by Enhanced PLL with default phase setting   |  |  |  |  |  |  |

| t <sub>INHPLL</sub>   | Hold time for input or bidirectional pin using IOE input register with global clock fed by Enhanced PLL with default phase setting    |  |  |  |  |  |  |

| t <sub>OUTCOPLL</sub> | Clock-to-output delay output or bidirectional pin using IOE output register with global clock Enhanced PLL with default phase setting |  |  |  |  |  |  |

| t <sub>XZPLL</sub>    | Synchronous IOE output enable register to output pin disable delay using global clock fed by Enhanced PLL with default phase setting  |  |  |  |  |  |  |

| t <sub>ZXPLL</sub>    | Synchronous IOE output enable register to output pin enable delay using global clock fed by Enhanced PLL with default phase setting   |  |  |  |  |  |  |

#### Notes to Table 4-54:

- (1) These timing parameters are sample-tested only.

- (2) These timing parameters are for column and row IOE pins. You should use the Quartus II software to verify the external timing for any pin.

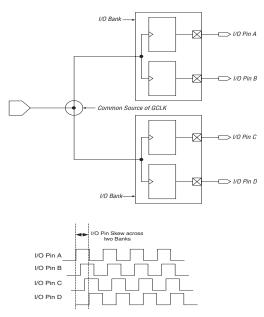

Figure 4–6 shows the case where four IOE registers are located in two different I/O banks.

Figure 4-6. I/O Skew Across Two I/O Banks

Table 4–97 defines the timing parameters used to define the timing for horizontal I/O pins (side banks 1, 2, 5, 6) and vertical I/O pins (top and bottom banks 3, 4, 7, 8). The timing parameters define the skew within an I/O bank, across two neighboring I/O banks on the same side of the device, across all horizontal I/O banks, across all vertical I/O banks, and the skew for the overall device.

| Table 4–97. Output Pin Timing Skew Definitions (Part 1 of 2) |                                                                |  |  |  |  |

|--------------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|

| Symbol Definition                                            |                                                                |  |  |  |  |

| t <sub>SB_HIO</sub>                                          | Row I/O (HIO) within one I/O bank (1)                          |  |  |  |  |

| t <sub>SB_VIO</sub>                                          | Column I/O (VIO) within one I/O bank (1)                       |  |  |  |  |

| t <sub>SS_HIO</sub>                                          | Row I/O (HIO) same side of the device, across two banks (2)    |  |  |  |  |

| t <sub>SS_VIO</sub>                                          | Column I/O (VIO) same side of the device, across two banks (2) |  |  |  |  |

**Table 4–110. Stratix IOE Programmable Delays on Row Pins** Note (1) -5 Speed Grade -6 Speed Grade -7 Speed Grade -8 Speed Grade **Parameter** Settina Unit Min Max Min Max Min Max Min Max Decrease input delay Off 3,970 4,367 5,022 5,908 ps to internal cells Small 3,390 3.729 4,288 5,045 ps 2.810 3.091 3.554 Medium 4.181 ps Large 173 181 208 245 ps On 173 181 208 245 ps Decrease input delay Off 3.900 4.290 4.933 5,804 ps to input register On 0 0 0 0 ps Decrease input delay Off 1.240 1.364 1.568 1.845 ps to output register On 0 0 0 0 ps Increase delay to Off 0 0 0 0 ps output pin On 397 417 417 417 ps Increase delay to Off 0 0 0 0 ps output enable pin 383 441 On 348 518 ps 0 Increase output clock Off 0 0 0 ps enable delay 180 227 Small 198 267 ps Large 260 286 328 386 ps On 260 286 328 386 ps Increase input clock Off 0 0 0 0 ps enable delay Small 180 198 227 267 ps Large 260 286 328 386 ps On 260 286 328 386 ps Off Increase output 0 0 0 0 ps enable clock enable Small 540 594 683 804 ps delav 1.285 Large 1.016 1.118 1,512 ps On 1,016 1,118 1,285 1,512 ps Increase tzx delay to Off 0 0 0 0 ps output pin On 1.993 2.092 2.092 2.092 ps

Note to Table 4-109 and Table 4-110:

<sup>(1)</sup> The delay chain delays vary for different device densities. These timing values only apply to EP1S30 and EP1S40 devices. Reference the timing information reported by the Quartus II software for other devices.

## **Maximum Input & Output Clock Rates**

Tables 4–114 through 4–119 show the maximum input clock rate for column and row pins in Stratix devices.

Table 4–114. Stratix Maximum Input Clock Rate for CLK[7..4] & CLK[15..12] Pins in Flip-Chip Packages (Part 1 of 2)

| Time in this emp t dendges (t dis t of 2) |                   |                   |                   |                   |      |  |  |  |

|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|------|--|--|--|

| I/O Standard                              | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |  |  |  |

| LVTTL                                     | 422               | 422               | 390               | 390               | MHz  |  |  |  |

| 2.5 V                                     | 422               | 422               | 390               | 390               | MHz  |  |  |  |

| 1.8 V                                     | 422               | 422               | 390               | 390               | MHz  |  |  |  |

| 1.5 V                                     | 422               | 422               | 390               | 390               | MHz  |  |  |  |

| LVCMOS                                    | 422               | 422               | 390               | 390               | MHz  |  |  |  |

| GTL                                       | 300               | 250               | 200               | 200               | MHz  |  |  |  |

| GTL+                                      | 300               | 250               | 200               | 200               | MHz  |  |  |  |

| SSTL-3 Class I                            | 400               | 350               | 300               | 300               | MHz  |  |  |  |

| SSTL-3 Class II                           | 400               | 350               | 300               | 300               | MHz  |  |  |  |

| SSTL-2 Class I                            | 400               | 350               | 300               | 300               | MHz  |  |  |  |

| SSTL-2 Class II                           | 400               | 350               | 300               | 300               | MHz  |  |  |  |

| SSTL-18 Class I                           | 400               | 350               | 300               | 300               | MHz  |  |  |  |

| SSTL-18 Class II                          | 400               | 350               | 300               | 300               | MHz  |  |  |  |

| 1.5-V HSTL Class I                        | 400               | 350               | 300               | 300               | MHz  |  |  |  |

| 1.5-V HSTL Class II                       | 400               | 350               | 300               | 300               | MHz  |  |  |  |

| 1.8-V HSTL Class I                        | 400               | 350               | 300               | 300               | MHz  |  |  |  |

| 1.8-V HSTL Class II                       | 400               | 350               | 300               | 300               | MHz  |  |  |  |

| 3.3-V PCI                                 | 422               | 422               | 390               | 390               | MHz  |  |  |  |

| 3.3-V PCI-X 1.0                           | 422               | 422               | 390               | 390               | MHz  |  |  |  |

| Compact PCI                               | 422               | 422               | 390               | 390               | MHz  |  |  |  |

| AGP 1×                                    | 422               | 422               | 390               | 390               | MHz  |  |  |  |

| AGP 2×                                    | 422               | 422               | 390               | 390               | MHz  |  |  |  |

| CTT                                       | 300               | 250               | 200               | 200               | MHz  |  |  |  |

| Differential 1.5-V HSTL<br>C1             | 400               | 350               | 300               | 300               | MHz  |  |  |  |

| LVPECL (1)                                | 645               | 645               | 622               | 622               | MHz  |  |  |  |

| PCML (1)                                  | 300               | 275               | 275               | 275               | MHz  |  |  |  |

Tables 4–125 and 4–126 show the high-speed I/O timing for Stratix devices.

| Symbol                                                                                                                                         | Conditions                         | -5 Speed Grade |     | -6 Speed Grade |     | -7 Speed Grade |     |     | -8 Speed Grade |     |     | IIn:4 |       |      |

|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|-----|----------------|-----|----------------|-----|-----|----------------|-----|-----|-------|-------|------|

|                                                                                                                                                |                                    | Min            | Тур | Max            | Min | Тур            | Max | Min | Тур            | Max | Min | Тур   | Max   | Unit |

| f <sub>HSCLK</sub> (Clock<br>frequency)<br>(LVDS,<br>LVPECL,<br>HyperTransport<br>technology)<br>f <sub>HSCLK</sub> = f <sub>HSDR</sub> /<br>W | W = 4 to 30<br>(Serdes used)       | 10             |     | 210            | 10  |                | 210 | 10  |                | 156 | 10  |       | 115.5 | MHz  |

|                                                                                                                                                | W = 2 (Serdes bypass)              | 50             |     | 231            | 50  |                | 231 | 50  |                | 231 | 50  |       | 231   | MHz  |

|                                                                                                                                                | W = 2 (Serdes used)                | 150            |     | 420            | 150 |                | 420 | 150 |                | 312 | 150 |       | 231   | MHz  |

|                                                                                                                                                | W = 1 (Serdes bypass)              | 100            |     | 462            | 100 |                | 462 | 100 |                | 462 | 100 |       | 462   | MHz  |

|                                                                                                                                                | W = 1 (Serdes used)                | 300            |     | 717            | 300 |                | 717 | 300 |                | 624 | 300 |       | 462   | MHz  |

| f <sub>HSDR</sub> Device<br>operation<br>(LVDS,<br>LVPECL,<br>HyperTransport<br>technology)                                                    | J = 10                             | 300            |     | 840            | 300 |                | 840 | 300 |                | 640 | 300 |       | 462   | Mbps |

|                                                                                                                                                | J = 8                              | 300            |     | 840            | 300 |                | 840 | 300 |                | 640 | 300 |       | 462   | Mbps |

|                                                                                                                                                | J = 7                              | 300            |     | 840            | 300 |                | 840 | 300 |                | 640 | 300 |       | 462   | Mbps |

|                                                                                                                                                | J = 4                              | 300            |     | 840            | 300 |                | 840 | 300 |                | 640 | 300 |       | 462   | Mbps |

|                                                                                                                                                | J = 2                              | 100            |     | 462            | 100 |                | 462 | 100 |                | 640 | 100 |       | 462   | Mbps |

|                                                                                                                                                | J = 1 (LVDS<br>and LVPECL<br>only) | 100            |     | 462            | 100 |                | 462 | 100 |                | 640 | 100 |       | 462   | Mbps |

Tables 4–131 through 4–133 describe the Stratix device fast PLL specifications.

| Symbol                             | Parameter                                                                             | Min   | Max   | Unit    |

|------------------------------------|---------------------------------------------------------------------------------------|-------|-------|---------|

| f <sub>IN</sub>                    | CLKIN frequency (1), (2), (3)                                                         | 10    | 717   | MHz     |

| f <sub>INPFD</sub>                 | Input frequency to PFD                                                                | 10    | 500   | MHz     |

| f <sub>OUT</sub>                   | Output frequency for internal global or regional clock (3)                            | 9.375 | 420   | MHz     |

| f <sub>OUT_DIFFIO</sub>            | Output frequency for external clock driven out on a differential I/O data channel (2) | (5)   | (5)   |         |

| f <sub>VCO</sub>                   | VCO operating frequency                                                               | 300   | 1,000 | MHz     |

| t <sub>INDUTY</sub>                | CLKIN duty cycle                                                                      | 40    | 60    | %       |

| t <sub>INJITTER</sub>              | Period jitter for CLKIN pin                                                           |       | ±200  | ps      |

| t <sub>DUTY</sub>                  | Duty cycle for DFFIO 1× CLKOUT pin (6)                                                | 45    | 55    | %       |

| t <sub>JITTER</sub>                | Period jitter for DIFFIO clock out (6)                                                |       | (5)   | ps      |

| t <sub>LOCK</sub>                  | Time required for PLL to acquire lock                                                 | 10    | 100   | μs      |

| m                                  | Multiplication factors for <i>m</i> counter (6)                                       | 1     | 32    | Integer |

| <i>l</i> 0, <i>l</i> 1, <i>g</i> 0 | Multiplication factors for I0, I1, and g0 counter (7), (8)                            | 1     | 32    | Integer |

| t <sub>ARESET</sub>                | Minimum pulse width on areset signal                                                  | 10    |       | ns      |

| Table 4–132. Fast PLL Specifications for -7 Speed Grades (Part 1 of 2) |                                                                                   |       |      |      |  |  |  |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------|------|------|--|--|--|

| Symbol                                                                 | Parameter                                                                         | Min   | Max  | Unit |  |  |  |

| f <sub>IN</sub>                                                        | CLKIN frequency (1), (3)                                                          | 10    | 640  | MHz  |  |  |  |

| f <sub>INPFD</sub>                                                     | Input frequency to PFD                                                            | 10    | 500  | MHz  |  |  |  |

| f <sub>OUT</sub>                                                       | Output frequency for internal global or regional clock (4)                        | 9.375 | 420  | MHz  |  |  |  |

| fout_diffio                                                            | Output frequency for external clock driven out on a differential I/O data channel | (5)   | (5)  | MHz  |  |  |  |

| f <sub>VCO</sub>                                                       | VCO operating frequency                                                           | 300   | 700  | MHz  |  |  |  |

| t <sub>INDUTY</sub>                                                    | CLKIN duty cycle                                                                  | 40    | 60   | %    |  |  |  |

| t <sub>INJITTER</sub>                                                  | Period jitter for CLKIN pin                                                       |       | ±200 | ps   |  |  |  |

| t <sub>DUTY</sub>                                                      | Duty cycle for DFFIO 1× CLKOUT pin (6)                                            | 45    | 55   | %    |  |  |  |