Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 2566                                                    |

| Number of Logic Elements/Cells | 25660                                                   |

| Total RAM Bits                 | 1944576                                                 |

| Number of I/O                  | 473                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                         |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 672-BBGA                                                |

| Supplier Device Package        | 672-FBGA (27x27)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s25f672c8 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Chapter Revision Dates**

The chapters in this book, *Stratix Device Handbook*, *Volume 1*, were revised on the following dates. Where chapters or groups of chapters are available separately, part numbers are listed.

Chapter 1. Introduction

Revised: July 2005 Part number: S51001-3.2

Chapter 2. Stratix Architecture

Revised: July 2005 Part number: S51002-3.2

Chapter 3. Configuration & Testing

Revised: July 2005 Part number: S51003-1.3

Chapter 4. DC & Switching Characteristics

Revised: January 2006 Part number: S51004-3.4

Chapter 5. Reference & Ordering Information

Revised: September 2004 Part number: S51005-2.1

Altera Corporation vii

### **About This Handbook**

This handbook provides comprehensive information about the Altera® Stratix family of devices.

## How to Find Information

You can find more information in the following ways:

- The Adobe Acrobat Find feature, which searches the text of a PDF document. Click the binoculars toolbar icon to open the Find dialog box.

- Acrobat bookmarks, which serve as an additional table of contents in PDF documents.

- Thumbnail icons, which provide miniature previews of each page, provide a link to the pages.

- Numerous links, shown in green text, which allow you to jump to related information.

#### How to Contact Altera

For the most up-to-date information about Altera products, go to the Altera world-wide web site at www.altera.com. For technical support on this product, go to www.altera.com/mysupport. For additional information about Altera products, consult the sources shown below.

| Information Type               | USA & Canada                                                   | All Other Locations                                                    |

|--------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------|

| Technical support              | www.altera.com/mysupport/                                      | www.altera.com/mysupport/                                              |

|                                | (800) 800-EPLD (3753)<br>(7:00 a.m. to 5:00 p.m. Pacific Time) | +1 408-544-8767<br>7:00 a.m. to 5:00 p.m. (GMT -8:00)<br>Pacific Time  |

| Product literature             | www.altera.com                                                 | www.altera.com                                                         |

| Altera literature services     | literature@altera.com                                          | literature@altera.com                                                  |

| Non-technical customer service | (800) 767-3753                                                 | + 1 408-544-7000<br>7:00 a.m. to 5:00 p.m. (GMT -8:00)<br>Pacific Time |

| FTP site                       | ftp.altera.com                                                 | ftp.altera.com                                                         |

Altera Corporation ix

# Section I. Stratix Device Family Data Sheet

This section provides the data sheet specifications for Stratix® devices. They contain feature definitions of the internal architecture, configuration and JTAG boundary-scan testing information, DC operating conditions, AC timing parameters, a reference to power consumption, and ordering information for Stratix devices.

This section contains the following chapters:

- Chapter 1, Introduction

- Chapter 2, Stratix Architecture

- Chapter 3, Configuration & Testing

- Chapter 4, DC & Switching Characteristics

- Chapter 5, Reference & Ordering Information

#### **Revision History**

The table below shows the revision history for Chapters 1 through 5.

| Chapter | Date/Version         | Changes Made                                                                                                                                                                                                                                                                                                                     |

|---------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | July 2005, v3.2      | Minor content changes.                                                                                                                                                                                                                                                                                                           |

|         | September 2004, v3.1 | Updated Table 1–6 on page 1–5.                                                                                                                                                                                                                                                                                                   |

|         | April 2004, v3.0     | <ul> <li>Main section page numbers changed on first page.</li> <li>Changed PCI-X to PCI-X 1.0 in "Features" on page 1–2.</li> <li>Global change from SignalTap to SignalTap II.</li> <li>The DSP blocks in "Features" on page 1–2 provide dedicated implementation of multipliers that are now "faster than 300 MHz."</li> </ul> |

|         | January 2004, v2.2   | Updated -5 speed grade device information in Table 1-6.                                                                                                                                                                                                                                                                          |

|         | October 2003, v2.1   | Add -8 speed grade device information.                                                                                                                                                                                                                                                                                           |

|         | July 2003, v2.0      | Format changes throughout chapter.                                                                                                                                                                                                                                                                                               |

Altera Corporation Section I–1

| Table 1–1. Stratix Device Features — EP1\$10, EP1\$20, EP1\$25, EP1\$30 |         |           |           |           |  |  |

|-------------------------------------------------------------------------|---------|-----------|-----------|-----------|--|--|

| Feature                                                                 | EP1S10  | EP1S20    | EP1S25    | EP1S30    |  |  |

| LEs                                                                     | 10,570  | 18,460    | 25,660    | 32,470    |  |  |

| M512 RAM blocks (32 × 18 bits)                                          | 94      | 194       | 224       | 295       |  |  |

| M4K RAM blocks (128 × 36 bits)                                          | 60      | 82        | 138       | 171       |  |  |

| M-RAM blocks (4K × 144 bits)                                            | 1       | 2         | 2         | 4         |  |  |

| Total RAM bits                                                          | 920,448 | 1,669,248 | 1,944,576 | 3,317,184 |  |  |

| DSP blocks                                                              | 6       | 10        | 10        | 12        |  |  |

| Embedded multipliers (1)                                                | 48      | 80        | 80        | 96        |  |  |

| PLLs                                                                    | 6       | 6         | 6         | 10        |  |  |

| Maximum user I/O pins                                                   | 426     | 586       | 706       | 726       |  |  |

| Table 1–2. Stratix Device Features — EP1S40, EP1S60, EP1S80 |           |           |           |  |  |  |  |

|-------------------------------------------------------------|-----------|-----------|-----------|--|--|--|--|

| Feature EP1S40 EP1S60 EP1S80                                |           |           |           |  |  |  |  |

| LEs                                                         | 41,250    | 57,120    | 79,040    |  |  |  |  |

| M512 RAM blocks (32 × 18 bits)                              | 384       | 574       | 767       |  |  |  |  |

| M4K RAM blocks (128 × 36 bits)                              | 183       | 292       | 364       |  |  |  |  |

| M-RAM blocks (4K × 144 bits)                                | 4         | 6         | 9         |  |  |  |  |

| Total RAM bits                                              | 3,423,744 | 5,215,104 | 7,427,520 |  |  |  |  |

| DSP blocks                                                  | 14        | 18        | 22        |  |  |  |  |

| Embedded multipliers (1)                                    | 112       | 144       | 176       |  |  |  |  |

| PLLs                                                        | 12        | 12        | 12        |  |  |  |  |

| Maximum user I/O pins                                       | 822       | 1,022     | 1,238     |  |  |  |  |

#### Note to Tables 1–1 and 1–2:

<sup>(1)</sup> This parameter lists the total number of  $9 \times 9$ -bit multipliers for each device. For the total number of  $18 \times 18$ -bit multipliers per device, divide the total number of  $9 \times 9$ -bit multipliers by 2. For the total number of  $36 \times 36$ -bit multipliers per device, divide the total number of  $9 \times 9$ -bit multipliers by 8.

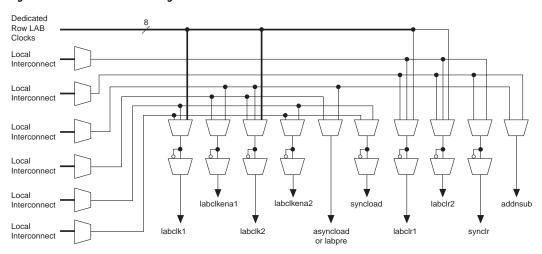

With the LAB-wide addnsub control signal, a single LE can implement a one-bit adder and subtractor. This saves LE resources and improves performance for logic functions such as DSP correlators and signed multipliers that alternate between addition and subtraction depending on data.

The LAB row clocks [7..0] and LAB local interconnect generate the LAB-wide control signals. The MultiTrack $^{\text{IM}}$  interconnect's inherent low skew allows clock and control signal distribution in addition to data. Figure 2–4 shows the LAB control signal generation circuit.

Figure 2-4. LAB-Wide Control Signals

#### **Logic Elements**

The smallest unit of logic in the Stratix architecture, the LE, is compact and provides advanced features with efficient logic utilization. Each LE contains a four-input LUT, which is a function generator that can implement any function of four variables. In addition, each LE contains a programmable register and carry chain with carry select capability. A single LE also supports dynamic single bit addition or subtraction mode selectable by an LAB-wide control signal. Each LE drives all types of interconnects: local, row, column, LUT chain, register chain, and direct link interconnects. See Figure 2–5.

functions. Another special packing mode allows the register output to feed back into the LUT of the same LE so that the register is packed with its own fan-out LUT. This provides another mechanism for improved fitting. The LE can also drive out registered and unregistered versions of the LUT output.

#### **LUT Chain & Register Chain**

In addition to the three general routing outputs, the LEs within an LAB have LUT chain and register chain outputs. LUT chain connections allow LUTs within the same LAB to cascade together for wide input functions. Register chain outputs allow registers within the same LAB to cascade together. The register chain output allows an LAB to use LUTs for a single combinatorial function and the registers to be used for an unrelated shift register implementation. These resources speed up connections between LABs while saving local interconnect resources. See "MultiTrack Interconnect" on page 2–14 for more information on LUT chain and register chain connections.

#### addnsub Signal

The LE's dynamic adder/subtractor feature saves logic resources by using one set of LEs to implement both an adder and a subtractor. This feature is controlled by the LAB-wide control signal addnsub. The addnsub signal sets the LAB to perform either A+B or A-B. The LUT computes addition, and subtraction is computed by adding the two's complement of the intended subtractor. The LAB-wide signal converts to two's complement by inverting the B bits within the LAB and setting carry-in = 1 to add one to the least significant bit (LSB). The LSB of an adder/subtractor must be placed in the first LE of the LAB, where the LAB-wide addnsub signal automatically sets the carry-in to 1. The Quartus II Compiler automatically places and uses the adder/subtractor feature when using adder/subtractor parameterized functions.

#### **LE Operating Modes**

The Stratix LE can operate in one of the following modes:

- Normal mode

- Dynamic arithmetic mode

Each mode uses LE resources differently. In each mode, eight available inputs to the LE—the four data inputs from the LAB local interconnect; carry-in0 and carry-in1 from the previous LE; the LAB carry-in from the previous carry-chain LAB; and the register chain connection—are directed to different destinations to implement the desired logic function. LAB-wide signals provide clock, asynchronous clear,

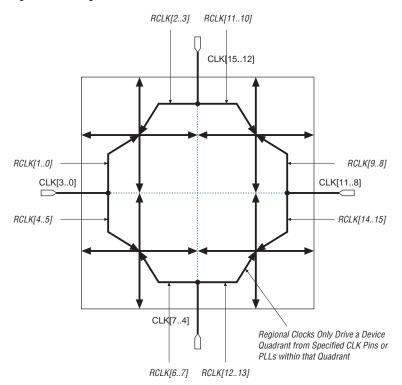

Figure 2-43. Regional Clocks

#### Fast Regional Clock Network

In EP1S25, EP1S20, and EP1S10 devices, there are two fast regional clock networks, FCLK [1..0], within each quadrant, fed by input pins that can connect to fast regional clock networks (see Figure 2–44). In EP1S30 and larger devices, there are two fast regional clock networks within each half-quadrant (see Figure 2–45). Dual-purpose FCLK pins drive the fast clock networks. All devices have eight FCLK pins to drive fast regional clock networks. Any I/O pin can drive a clock or control signal onto any fast regional clock network with the addition of a delay. This signal is driven via the I/O interconnect. The fast regional clock networks can also be driven from internal logic elements.

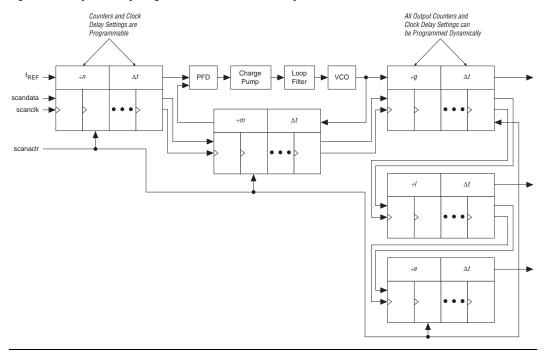

Figure 2–54. Dynamically Programmable Counters & Delays in Stratix Device Enhanced PLLs

PLL reconfiguration data is shifted into serial registers from the logic array or external devices. The PLL input shift data uses a reference input shift clock. Once the last bit of the serial chain is clocked in, the register chain is synchronously loaded into the PLL configuration bits. The shift circuitry also provides an asynchronous clear for the serial registers.

For more information on PLL reconfiguration, see *AN 282: Implementing PLL Reconfiguration in Stratix & Stratix GX Devices.*

#### Programmable Bandwidth

You have advanced control of the PLL bandwidth using the programmable control of the PLL loop characteristics, including loop filter and charge pump. The PLL's bandwidth is a measure of its ability to track the input clock and jitter. A high-bandwidth PLL can quickly lock onto a reference clock and react to any changes in the clock. It also will allow a wide band of input jitter spectrum to pass to the output. A low-bandwidth PLL will take longer to lock, but it will attenuate all high-frequency jitter components. The Quartus II software can adjust PLL characteristics to achieve the desired bandwidth. The programmable

Post-Scale Counters → diffioclk1 (2) Global or ÷/0 regional clock txload\_en (3) VCO Phase Selection Selectable at each PLL Output Port Phase rxload\_en (3) Frequency ÷/1 Global or Detector Global or regional clock regional clock (1) ► diffioclk2 (2) Charge Loop Global or PFD VCO ÷ g0 Clock □ Pump Filter regional clock Input [  $\pm m$

Figure 2-58. Stratix Device Fast PLL

#### *Notes to Figure 2–58:*

- The global or regional clock input can be driven by an output from another PLL or any dedicated CLK or FCLK pin.

It cannot be driven by internally-generated global signals.

- (2) In high-speed differential I/O support mode, this high-speed PLL clock feeds the SERDES. Stratix devices only support one rate of data transfer per fast PLL in high-speed differential I/O support mode.

- (3) This signal is a high-speed differential I/O support SERDES control signal.

#### Clock Multiplication & Division

Stratix device fast PLLs provide clock synthesis for PLL output ports using m/(post scaler) scaling factors. The input clock is multiplied by the m feedback factor. Each output port has a unique post scale counter to divide down the high-frequency VCO. There is one multiply divider, m, per fast PLL with a range of 1 to 32. There are two post scale L dividers for regional and/or LVDS interface clocks, and g0 counter for global clock output port; all range from 1 to 32.

In the case of a high-speed differential interface, set the output counter to 1 to allow the high-speed VCO frequency to drive the SERDES. When used for clocking the SERDES, the m counter can range from 1 to 30. The VCO frequency is equal to  $f_{\rm IN}\times m$ , where VCO frequency must be between 300 and 1000 MHz.

| Table 2–22. Fast PLL Port I/O Standards (Part 2 of 2) |          |           |  |  |

|-------------------------------------------------------|----------|-----------|--|--|

| I/O Standard                                          | Input    |           |  |  |

| I/O Standard                                          | INCLK    | PLLENABLE |  |  |

| SSTL-2 Class II                                       | <b>✓</b> |           |  |  |

| SSTL-3 Class I                                        | ✓        |           |  |  |

| SSTL-3 Class II                                       | <b>✓</b> |           |  |  |

| AGP (1× and 2×)                                       |          |           |  |  |

| СТТ                                                   | <b>✓</b> |           |  |  |

Table 2–23 shows the performance on each of the fast PLL clock inputs when using LVDS, LVPECL, 3.3-V PCML, or HyperTransport technology.

| Table 2–23. LVDS Performance on Fast PLL Input                         |                               |  |  |

|------------------------------------------------------------------------|-------------------------------|--|--|

| Fast PLL Clock Input                                                   | Maximum Input Frequency (MHz) |  |  |

| CLK0, CLK2, CLK9, CLK11,<br>FPLL7CLK, FPLL8CLK, FPLL9CLK,<br>FPLL10CLK | 717 <i>(</i> 1)               |  |  |

| CLK1, CLK3, CLK8, CLK10                                                | 645                           |  |  |

*Note to Table 2–23:*

#### External Clock Outputs

Each fast PLL supports differential or single-ended outputs for source-synchronous transmitters or for general-purpose external clocks. There are no dedicated external clock output pins. Any I/O pin can be driven by the fast PLL global or regional outputs as an external output pin. The I/O standards supported by any particular bank determines what standards are possible for an external clock output driven by the fast PLL in that bank.

#### Phase Shifting

Stratix device fast PLLs have advanced clock shift capability that enables programmable phase shifts. You can enter a phase shift (in degrees or time units) for each PLL clock output port or for all outputs together in one shift. You can perform phase shifting in time units with a resolution range of 125 to 416.66 ps. This resolution is a function of the VCO period, with the finest step being equal to an eighth (×0.125) of the VCO period.

<sup>(1)</sup> See the chapter DC & Switching Characteristics of the Stratix Device Handbook, Volume 1 for more information.

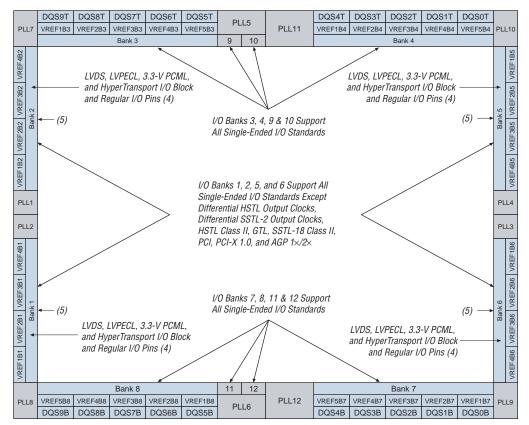

**Figure 2–70. Stratix I/O Banks** Notes (1), (2), (3)

#### *Notes to Figure 2–70:*

- (1) Figure 2–70 is a top view of the silicon die. This will correspond to a top-down view for non-flip-chip packages, but will be a reverse view for flip-chip packages.

- (2) Figure 2–70 is a graphic representation only. See the device pin-outs on the web (www.altera.com) and the Quartus II software for exact locations.

- (3) Banks 9 through 12 are enhanced PLL external clock output banks.

- (4) If the high-speed differential I/O pins are not used for high-speed differential signaling, they can support all of the I/O standards except HSTL Class I and II, GTL, SSTL-18 Class II, PCI, PCI-X 1.0, and AGP 1×/2×.

- (5) For guidelines for placing single-ended I/O pads next to differential I/O pads, see the Selectable I/O Standards in Stratix and Stratix GX Devices chapter in the Stratix Device Handbook, Volume 2.

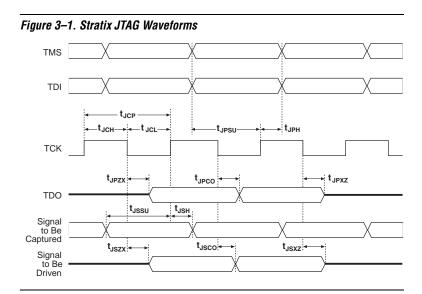

Figure 3–1 shows the timing requirements for the JTAG signals.

Table 3–4 shows the JTAG timing parameters and values for Stratix devices.

| Table 3-          | Table 3–4. Stratix JTAG Timing Parameters & Values |     |     |      |  |  |

|-------------------|----------------------------------------------------|-----|-----|------|--|--|

| Symbol            | Parameter                                          | Min | Max | Unit |  |  |

| $t_{\text{JCP}}$  | TCK clock period                                   | 100 |     | ns   |  |  |

| t <sub>JCH</sub>  | TCK clock high time                                | 50  |     | ns   |  |  |

| t <sub>JCL</sub>  | TCK clock low time                                 | 50  |     | ns   |  |  |

| t <sub>JPSU</sub> | JTAG port setup time                               | 20  |     | ns   |  |  |

| t <sub>JPH</sub>  | JTAG port hold time                                | 45  |     | ns   |  |  |

| t <sub>JPCO</sub> | JTAG port clock to output                          |     | 25  | ns   |  |  |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output           |     | 25  | ns   |  |  |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance           |     | 25  | ns   |  |  |

| t <sub>JSSU</sub> | Capture register setup time                        | 20  |     | ns   |  |  |

| t <sub>JSH</sub>  | Capture register hold time                         | 45  |     | ns   |  |  |

| t <sub>JSCO</sub> | Update register clock to output                    |     | 35  | ns   |  |  |

| t <sub>JSZX</sub> | Update register high impedance to valid output     |     | 35  | ns   |  |  |

| t <sub>JSXZ</sub> | Update register valid output to high impedance     |     | 35  | ns   |  |  |

| Table 4–7. 1.8-V I/O Specifications |                           |                                               |                          |                        |      |  |

|-------------------------------------|---------------------------|-----------------------------------------------|--------------------------|------------------------|------|--|

| Symbol                              | Parameter                 | Conditions                                    | Minimum                  | Maximum                | Unit |  |

| V <sub>CCIO</sub>                   | Output supply voltage     |                                               | 1.65                     | 1.95                   | V    |  |

| V <sub>IH</sub>                     | High-level input voltage  |                                               | $0.65 \times V_{CCIO}$   | 2.25                   | V    |  |

| V <sub>IL</sub>                     | Low-level input voltage   |                                               | -0.3                     | $0.35 \times V_{CCIO}$ | ٧    |  |

| V <sub>OH</sub>                     | High-level output voltage | $I_{OH} = -2 \text{ to } -8 \text{ mA } (10)$ | V <sub>CCIO</sub> - 0.45 |                        | ٧    |  |

| V <sub>OL</sub>                     | Low-level output voltage  | I <sub>OL</sub> = 2 to 8 mA (10)              |                          | 0.45                   | V    |  |

| Table 4–8. 1.5-V I/O Specifications |                           |                              |                        |                         |      |  |

|-------------------------------------|---------------------------|------------------------------|------------------------|-------------------------|------|--|

| Symbol                              | Parameter                 | Conditions                   | Minimum                | Maximum                 | Unit |  |

| V <sub>CCIO</sub>                   | Output supply voltage     |                              | 1.4                    | 1.6                     | V    |  |

| V <sub>IH</sub>                     | High-level input voltage  |                              | $0.65 \times V_{CCIO}$ | V <sub>CCIO</sub> + 0.3 | V    |  |

| V <sub>IL</sub>                     | Low-level input voltage   |                              | -0.3                   | $0.35 \times V_{CCIO}$  | V    |  |

| V <sub>OH</sub>                     | High-level output voltage | I <sub>OH</sub> = -2 mA (10) | $0.75 \times V_{CCIO}$ |                         | V    |  |

| V <sub>OL</sub>                     | Low-level output voltage  | I <sub>OL</sub> = 2 mA (10)  |                        | $0.25 \times V_{CCIO}$  | V    |  |

#### Notes to Tables 4–1 through 4–8:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Conditions beyond those listed in Table 4–1 may cause permanent damage to a device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse affects on the device.

- (3) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns, or overshoot to the voltage shown in Table 4–9, based on input duty cycle for input currents less than 100 mA. The overshoot is dependent upon duty cycle of the signal. The DC case is equivalent to 100% duty cycle.

- (4) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically.

- (5) V<sub>CCIO</sub> maximum and minimum conditions for LVPECL, LVDS, and 3.3-V PCML are shown in parentheses.

- (6) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (7) Typical values are for  $T_A$  = 25°C,  $V_{CCINT}$  = 1.5 V, and  $V_{CCIO}$  = 1.5 V, 1.8 V, 2.5 V, and 3.3 V.

- (8) This value is specified for normal device operation. The value may vary during power-up. This applies for all V<sub>CCIO</sub> settings (3.3, 2.5, 1.8, and 1.5 V).

- (9) Pin pull-up resistance values will lower if an external source drives the pin higher than V<sub>CCIO</sub>.

- (10) Drive strength is programmable according to the values shown in the *Stratix Architecture* chapter of the *Stratix Device Handbook, Volume 1*.

| Table 4–9. Overshoot Input Voltage with Respect to Duty Cycle (Part 1 of 2) |    |  |  |

|-----------------------------------------------------------------------------|----|--|--|

| Vin (V) Maximum Duty Cycle (%)                                              |    |  |  |

| 4.0 100                                                                     |    |  |  |

| 4.1 90                                                                      |    |  |  |

| 4.2                                                                         | 50 |  |  |

| Table 4–28. 1.8-V HSTL Class I Specifications |                             |                               |                         |                         |                        |      |

|-----------------------------------------------|-----------------------------|-------------------------------|-------------------------|-------------------------|------------------------|------|

| Symbol                                        | Parameter                   | Conditions                    | Minimum                 | Typical                 | Maximum                | Unit |

| $V_{CCIO}$                                    | Output supply voltage       |                               | 1.65                    | 1.80                    | 1.95                   | V    |

| $V_{REF}$                                     | Input reference voltage     |                               | 0.70                    | 0.90                    | 0.95                   | V    |

| V <sub>TT</sub>                               | Termination voltage         |                               |                         | V <sub>CCIO</sub> × 0.5 |                        | V    |

| V <sub>IH</sub> (DC)                          | DC high-level input voltage |                               | V <sub>REF</sub> + 0.1  |                         |                        | V    |

| V <sub>IL</sub> (DC)                          | DC low-level input voltage  |                               | -0.5                    |                         | V <sub>REF</sub> - 0.1 | V    |

| V <sub>IH</sub> (AC)                          | AC high-level input voltage |                               | V <sub>REF</sub> + 0.2  |                         |                        | V    |

| V <sub>IL</sub> (AC)                          | AC low-level input voltage  |                               |                         |                         | V <sub>REF</sub> - 0.2 | V    |

| V <sub>OH</sub>                               | High-level output voltage   | $I_{OH} = -8 \text{ mA } (3)$ | V <sub>CCIO</sub> - 0.4 |                         |                        | V    |

| V <sub>OL</sub>                               | Low-level output voltage    | I <sub>OL</sub> = 8 mA (3)    |                         |                         | 0.4                    | V    |

| Table 4–29. 1.8-V HSTL Class II Specifications |                             |                                    |                         |                         |                        |      |  |  |

|------------------------------------------------|-----------------------------|------------------------------------|-------------------------|-------------------------|------------------------|------|--|--|

| Symbol                                         | Parameter                   | Conditions                         | Minimum                 | Typical                 | Maximum                | Unit |  |  |

| V <sub>CCIO</sub>                              | Output supply voltage       |                                    | 1.65                    | 1.80                    | 1.95                   | V    |  |  |

| $V_{REF}$                                      | Input reference voltage     |                                    | 0.70                    | 0.90                    | 0.95                   | V    |  |  |

| V <sub>TT</sub>                                | Termination voltage         |                                    |                         | V <sub>CCIO</sub> × 0.5 |                        | V    |  |  |

| V <sub>IH</sub> (DC)                           | DC high-level input voltage |                                    | V <sub>REF</sub> + 0.1  |                         |                        | V    |  |  |

| V <sub>IL</sub> (DC)                           | DC low-level input voltage  |                                    | -0.5                    |                         | V <sub>REF</sub> - 0.1 | V    |  |  |

| V <sub>IH</sub> (AC)                           | AC high-level input voltage |                                    | V <sub>REF</sub> + 0.2  |                         |                        | V    |  |  |

| V <sub>IL</sub> (AC)                           | AC low-level input voltage  |                                    |                         |                         | V <sub>REF</sub> - 0.2 | V    |  |  |

| V <sub>OH</sub>                                | High-level output voltage   | $I_{OH} = -16 \text{ mA } (3)$     | V <sub>CCIO</sub> - 0.4 |                         |                        | V    |  |  |

| V <sub>OL</sub>                                | Low-level output voltage    | I <sub>OL</sub> = 16 mA <i>(3)</i> |                         |                         | 0.4                    | V    |  |  |

| Table 4–30. 1.5-V Differential HSTL Class I & Class II Specifications |                               |            |         |         |         |      |  |

|-----------------------------------------------------------------------|-------------------------------|------------|---------|---------|---------|------|--|

| Symbol                                                                | Parameter                     | Conditions | Minimum | Typical | Maximum | Unit |  |

| V <sub>CCIO</sub>                                                     | I/O supply voltage            |            | 1.4     | 1.5     | 1.6     | V    |  |

| V <sub>DIF</sub> (DC)                                                 | DC input differential voltage |            | 0.2     |         |         | V    |  |

| V <sub>CM</sub> (DC)                                                  | DC common mode input voltage  |            | 0.68    |         | 0.9     | V    |  |

| V <sub>DIF</sub> (AC)                                                 | AC differential input voltage |            | 0.4     |         |         | V    |  |

| Parameter             | -5 Speed Grade |       | -6 Spee | d Grade | -7 Speed Grade |       | -8 Speed Grade |     |      |

|-----------------------|----------------|-------|---------|---------|----------------|-------|----------------|-----|------|

|                       | Min            | Max   | Min     | Max     | Min            | Max   | Min            | Max | Unit |

| t <sub>INSU</sub>     | 1.351          |       | 1.479   |         | 1.699          |       | NA             |     | ns   |

| t <sub>INH</sub>      | 0.000          |       | 0.000   |         | 0.000          |       | NA             |     | ns   |

| t <sub>outco</sub>    | 2.732          | 5.380 | 2.732   | 5.728   | 2.732          | 6.240 | NA             | NA  | ns   |

| t <sub>XZ</sub>       | 2.672          | 5.254 | 2.672   | 5.596   | 2.672          | 6.116 | NA             | NA  | ns   |

| t <sub>ZX</sub>       | 2.672          | 5.254 | 2.672   | 5.596   | 2.672          | 6.116 | NA             | NA  | ns   |

| t <sub>INSUPLL</sub>  | 0.923          |       | 0.971   |         | 1.098          |       | NA             |     | ns   |

| t <sub>INHPLL</sub>   | 0.000          |       | 0.000   |         | 0.000          |       | NA             |     | ns   |

| t <sub>OUTCOPLL</sub> | 1.210          | 2.544 | 1.210   | 2.648   | 1.210          | 2.715 | NA             | NA  | ns   |

| t <sub>XZPLL</sub>    | 1.150          | 2.418 | 1.150   | 2.516   | 1.150          | 2.591 | NA             | NA  | ns   |

| t <sub>ZXPLL</sub>    | 1.150          | 2.418 | 1.150   | 2.516   | 1.150          | 2.591 | NA             | NA  | ns   |

| Table 4–64. EP1S20 External I/O Timing on Row Pins Using Fast Regional Clock Networks Note (1) |                |       |                |       |                |       |                |     |      |

|------------------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-----|------|

| Parameter                                                                                      | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |     |      |

|                                                                                                | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max | Unit |

| t <sub>INSU</sub>                                                                              | 2.032          |       | 2.207          |       | 2.535          |       | NA             |     | ns   |

| t <sub>INH</sub>                                                                               | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns   |

| t <sub>OUTCO</sub>                                                                             | 2.492          | 5.018 | 2.492          | 5.355 | 2.492          | 5.793 | NA             | NA  | ns   |

| t <sub>XZ</sub>                                                                                | 2.519          | 5.072 | 2.519          | 5.411 | 2.519          | 5.861 | NA             | NA  | ns   |

| t <sub>ZX</sub>                                                                                | 2.519          | 5.072 | 2.519          | 5.411 | 2.519          | 5.861 | NA             | NA  | ns   |

Tables 4–79 through 4–84 show the external timing parameters on column and row pins for EP1S40 devices.

| Table 4-79. I      | Table 4–79. EP1S40 External I/O Timing on Column Pins Using Fast Regional Clock Networks |       |                |       |                |       |                |       |          |

|--------------------|------------------------------------------------------------------------------------------|-------|----------------|-------|----------------|-------|----------------|-------|----------|

| Daramatar          | -5 Speed Grade                                                                           |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | II m i t |

| Parameter          | Min                                                                                      | Max   | Min            | Max   | Min            | Max   | Min            | Max   | Unit     |

| t <sub>INSU</sub>  | 2.696                                                                                    |       | 2.907          |       | 3.290          |       | 2.899          |       | ns       |

| t <sub>INH</sub>   | 0.000                                                                                    |       | 0.000          |       | 0.000          |       | 0.000          |       | ns       |

| t <sub>OUTCO</sub> | 2.506                                                                                    | 5.015 | 2.506          | 5.348 | 2.506          | 5.809 | 2.698          | 7.286 | ns       |

| t <sub>XZ</sub>    | 2.446                                                                                    | 4.889 | 2.446          | 5.216 | 2.446          | 5.685 | 2.638          | 7.171 | ns       |

| t <sub>ZX</sub>    | 2.446                                                                                    | 4.889 | 2.446          | 5.216 | 2.446          | 5.685 | 2.638          | 7.171 | ns       |

| Table 4-80. I        | Table 4–80. EP1S40 External I/O Timing on Column Pins Using Regional Clock Networks |       |         |         |                |       |         |         |      |

|----------------------|-------------------------------------------------------------------------------------|-------|---------|---------|----------------|-------|---------|---------|------|

| Parameter            | -5 Speed Grade                                                                      |       | -6 Spee | d Grade | -7 Speed Grade |       | -8 Spee | d Grade | 11:4 |

|                      | Min                                                                                 | Max   | Min     | Max     | Min            | Max   | Min     | Max     | Unit |

| t <sub>INSU</sub>    | 2.413                                                                               |       | 2.581   |         | 2.914          |       | 2.938   |         | ns   |

| t <sub>INH</sub>     | 0.000                                                                               |       | 0.000   |         | 0.000          |       | 0.000   |         | ns   |

| t <sub>outco</sub>   | 2.668                                                                               | 5.254 | 2.668   | 5.628   | 2.668          | 6.132 | 2.869   | 7.307   | ns   |

| t <sub>XZ</sub>      | 2.608                                                                               | 5.128 | 2.608   | 5.496   | 2.608          | 6.008 | 2.809   | 7.192   | ns   |

| t <sub>ZX</sub>      | 2.608                                                                               | 5.128 | 2.608   | 5.496   | 2.608          | 6.008 | 2.809   | 7.192   | ns   |

| t <sub>INSUPLL</sub> | 1.385                                                                               |       | 1.376   |         | 1.609          |       | 1.837   |         | ns   |

| t <sub>INHPLL</sub>  | 0.000                                                                               |       | 0.000   |         | 0.000          |       | 0.000   |         | ns   |

| toutcopll            | 1.117                                                                               | 2.382 | 1.117   | 2.552   | 1.117          | 2.504 | 1.117   | 2.542   | ns   |

| t <sub>XZPLL</sub>   | 1.057                                                                               | 2.256 | 1,057   | 2.420   | 1.057          | 2.380 | 1.057   | 2.427   | ns   |

| t <sub>ZXPLL</sub>   | 1.057                                                                               | 2.256 | 1,057   | 2.420   | 1.057          | 2.380 | 1.057   | 2.427   | ns   |

Tables 4–85 through 4–90 show the external timing parameters on column and row pins for EP1S60 devices.

| Table 4–85. EP1S60 External I/O Timing on Column Pins Using Fast Regional Clock Networks Note (1) |                |       |                |       |                |       |                |     |      |

|---------------------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-----|------|

| Parameter                                                                                         | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |     |      |

|                                                                                                   | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max | Unit |

| t <sub>INSU</sub>                                                                                 | 3.029          |       | 3.277          |       | 3.733          |       | NA             |     | ns   |

| t <sub>INH</sub>                                                                                  | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns   |

| t <sub>OUTCO</sub>                                                                                | 2.446          | 4.871 | 2.446          | 5.215 | 2.446          | 5.685 | NA             | NA  | ns   |

| t <sub>XZ</sub>                                                                                   | 2.386          | 4.745 | 2.386          | 5.083 | 2.386          | 5.561 | NA             | NA  | ns   |

| t <sub>ZX</sub>                                                                                   | 2.386          | 4.745 | 2.386          | 5.083 | 2.386          | 5.561 | NA             | NA  | ns   |

| Table 4-86. I         | Table 4–86. EP1S60 External I/O Timing on Column Pins Using Regional Clock Networks Note (1) |         |         |         |         |         |         |          |      |  |

|-----------------------|----------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|----------|------|--|

| Parameter             | -5 Spee                                                                                      | d Grade | -6 Spee | d Grade | -7 Spee | d Grade | -8 Spee | ed Grade | Unit |  |

|                       | Min                                                                                          | Max     | Min     | Max     | Min     | Max     | Min     | Max      |      |  |

| t <sub>INSU</sub>     | 2.491                                                                                        |         | 2.691   |         | 3.060   |         | NA      |          | ns   |  |

| t <sub>INH</sub>      | 0.000                                                                                        |         | 0.000   |         | 0.000   |         | NA      |          | ns   |  |

| t <sub>OUTCO</sub>    | 2.767                                                                                        | 5.409   | 2.767   | 5.801   | 2.767   | 6.358   | NA      | NA       | ns   |  |

| t <sub>XZ</sub>       | 2.707                                                                                        | 5.283   | 2.707   | 5.669   | 2.707   | 6.234   | NA      | NA       | ns   |  |

| t <sub>ZX</sub>       | 2.707                                                                                        | 5.283   | 2.707   | 5.669   | 2.707   | 6.234   | NA      | NA       | ns   |  |

| t <sub>INSUPLL</sub>  | 1.233                                                                                        |         | 1.270   |         | 1.438   |         | NA      |          | ns   |  |

| t <sub>INHPLL</sub>   | 0.000                                                                                        |         | 0.000   |         | 0.000   |         | NA      |          | ns   |  |

| t <sub>OUTCOPLL</sub> | 1.078                                                                                        | 2.278   | 1.078   | 2.395   | 1.078   | 2.428   | NA      | NA       | ns   |  |

| t <sub>XZPLL</sub>    | 1.018                                                                                        | 2.152   | 1.018   | 2.263   | 1.018   | 2.304   | NA      | NA       | ns   |  |

| t <sub>ZXPLL</sub>    | 1.018                                                                                        | 2.152   | 1.018   | 2.263   | 1.018   | 2.304   | NA      | NA       | ns   |  |

| Table 4–128. Enhanced PLL Specifications for -6 Speed Grades (Part 2 of 2) |                                                                                                                   |     |     |         |      |  |  |

|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|---------|------|--|--|

| Symbol                                                                     | Parameter                                                                                                         | Min | Тур | Max     | Unit |  |  |

| t <sub>SCANCLK</sub>                                                       | scanclk frequency (5)                                                                                             |     |     | 22      | MHz  |  |  |

| t <sub>DLOCK</sub>                                                         | Time required to lock dynamically (after switchover or reconfiguring any non-post-scale counters/delays) (7) (11) | (9) |     | 100     | μs   |  |  |

| t <sub>LOCK</sub>                                                          | Time required to lock from end of device configuration (11)                                                       | 10  |     | 400     | μs   |  |  |

| $f_{VCO}$                                                                  | PLL internal VCO operating range                                                                                  | 300 |     | 800 (8) | MHz  |  |  |

| t <sub>LSKEW</sub>                                                         | Clock skew between two external clock outputs driven by the same counter                                          |     | ±50 |         | ps   |  |  |

| t <sub>SKEW</sub>                                                          | Clock skew between two external clock outputs driven by the different counters with the same settings             |     | ±75 |         | ps   |  |  |

| f <sub>SS</sub>                                                            | Spread spectrum modulation frequency                                                                              | 30  |     | 150     | kHz  |  |  |

| % spread                                                                   | Percentage spread for spread spectrum frequency (10)                                                              | 0.4 | 0.5 | 0.6     | %    |  |  |

| t <sub>ARESET</sub>                                                        | Minimum pulse width on areset signal                                                                              | 10  |     |         | ns   |  |  |

| Table 4–12             | Table 4–129. Enhanced PLL Specifications for -7 Speed Grade (Part 1 of 2) |               |     |          |      |  |  |  |  |

|------------------------|---------------------------------------------------------------------------|---------------|-----|----------|------|--|--|--|--|

| Symbol                 | Parameter                                                                 | Min           | Тур | Max      | Unit |  |  |  |  |

| f <sub>IN</sub>        | Input clock frequency                                                     | 3<br>(1), (2) |     | 565      | MHz  |  |  |  |  |

| f <sub>INPFD</sub>     | Input frequency to PFD                                                    | 3             |     | 420      | MHz  |  |  |  |  |

| f <sub>INDUTY</sub>    | Input clock duty cycle                                                    | 40            |     | 60       | %    |  |  |  |  |

| f <sub>EINDUTY</sub>   | External feedback clock input duty cycle                                  | 40            |     | 60       | %    |  |  |  |  |

| t <sub>INJITTER</sub>  | Input clock period jitter                                                 |               |     | ±200 (3) | ps   |  |  |  |  |

| t <sub>EINJITTER</sub> | External feedback clock period jitter                                     |               |     | ±200 (3) | ps   |  |  |  |  |

| t <sub>FCOMP</sub>     | External feedback clock compensation time (4)                             |               |     | 6        | ns   |  |  |  |  |

| f <sub>OUT</sub>       | Output frequency for internal global or regional clock                    | 0.3           |     | 420      | MHz  |  |  |  |  |

| f <sub>OUT_EXT</sub>   | Output frequency for external clock (3)                                   | 0.3           |     | 434      | MHz  |  |  |  |  |

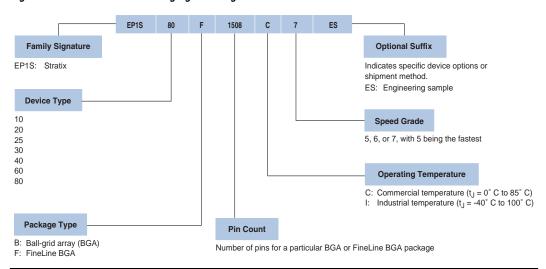

Figure 5-1. Stratix Device Packaging Ordering Information

| Fast Regional Clock External I/O Timing                    | I                                                                     |

|------------------------------------------------------------|-----------------------------------------------------------------------|

| Parameters 4–49<br>Global Clock External I/O Timing        | I/O<br>Standards                                                      |

| Parameters 4–50                                            | 1.5-V 4–14, 4–15                                                      |

| Regional Clock External I/O Timing Parameters 4–50         | I/O Specifications 4–4                                                |

| EP1S60 Devices                                             | 1.8-V                                                                 |

| Column Pin                                                 | I/O Specifications 4–4                                                |

| Fast Regional Clock External I/O Timing<br>Parameters 4–51 | 2.5-V I/O Specifications 4–3                                          |

| Global Clock External I/O Timing<br>Parameters 4–52        | 3.3-V 4–13<br>LVDS I/O Specifications 4–6                             |

| Regional Clock External I/O Timing Parameters 4–51         | PCI Specifications 4–9<br>PCML Specifications 4–8                     |

| M-RAM                                                      | Advanced I/O Standard Support 2–122                                   |

| Interface Locations 2–38                                   | Column I/O Block Connection to the                                    |

| Row Pin                                                    | Interconnect 2–107                                                    |

| Fast Regional Clock External I/O Timing                    | Column Pin                                                            |

| Parameters 4–52                                            | Input Delay Adders 4–66                                               |

| Global Clock External I/O Timing                           | Control Signal Selection per IOE 2–109<br>CTT I/O Specifications 4–16 |

| Parameters 4–53                                            | Differential LVDS Input On-Chip                                       |

| Regional Clock External I/O Timing                         | Termination 2–128                                                     |

| Parameters 4–53                                            | External I/O Delay Parameters 4–66                                    |

| EP1S80 Devices                                             | GTL+ I/O Specifications 4–10                                          |

| Column Pin                                                 | High-Speed Differential I/O                                           |

| Fast Regional Clock External I/O Timing                    | Support 2–130                                                         |

| Parameters 4–54                                            | HyperTransport Technology                                             |

| Global Clock External I/O Timing                           | Specifications 4–9                                                    |

| Parameters 4–55                                            | I/O Banks 2–125                                                       |

| Regional Clock External I/O Timing                         | I/O Structure 2–104                                                   |

| Parameters 4–54                                            | I/O Support by Bank 2–126                                             |

| Global Clock External I/O Timing                           | IOE Structure 2–105                                                   |

| Parameters 4–56                                            | LVCMOS Specifications 4–3                                             |

| Row Pin                                                    | LVDS Performance on Fast PLL                                          |

| Fast Regional Clock External I/O Timing                    | Input 2–103                                                           |

| Parameters 4–55                                            | LVPECL Specifications 4–8                                             |

| Regional Clock External I/O Timing                         | LVTTL Specifications 4–3                                              |

| Parameters 4–56                                            | MultiVolt I/O Interface 2–129                                         |

|                                                            | MultiVolt I/O Support 2–130                                           |

| H                                                          | Output Delay Adders for Fast Slew Rate                                |

|                                                            | on Column Pins 4–68                                                   |

| HSTL Class I Specifications 4 14 4 15                      | Output Delay Adders for Fast Slew Rate                                |

| Class I Specifications 4–14, 4–15                          | on Row Pins 4–69                                                      |

| Class II Specifications 4–14, 4–15                         | Output Delay Adders for Slow Slew Rate                                |

|                                                            | on Column Pins 4–70                                                   |

|                                                            | Package Options & I/O Pin Counts 1–4                                  |

|                                                            | Receiver Input Waveforms for Differential                             |

Index-4 Altera Corporation