Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 2566                                                     |

| Number of Logic Elements/Cells | 25660                                                    |

| Total RAM Bits                 | 1944576                                                  |

| Number of I/O                  | 473                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 672-BBGA                                                 |

| Supplier Device Package        | 672-FBGA (27x27)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s25f672c8n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Chapter Revision Dates**

The chapters in this book, *Stratix Device Handbook*, *Volume 1*, were revised on the following dates. Where chapters or groups of chapters are available separately, part numbers are listed.

Chapter 1. Introduction

Revised: July 2005 Part number: S51001-3.2

Chapter 2. Stratix Architecture

Revised: July 2005 Part number: S51002-3.2

Chapter 3. Configuration & Testing

Revised: July 2005 Part number: S51003-1.3

Chapter 4. DC & Switching Characteristics

Revised: January 2006 Part number: S51004-3.4

Chapter 5. Reference & Ordering Information

Revised: September 2004 Part number: S51005-2.1

Altera Corporation vii

| Chapter | Date/Version         | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2       | July 2003, v2.0      | <ul> <li>Added reference on page 2-73 to Figures 2-50 and 2-51 for RCLK connections.</li> <li>Updated ranges for EPLL post-scale and pre-scale dividers on page 2-85.</li> <li>Updated PLL Reconfiguration frequency from 25 to 22 MHz on page 2-87.</li> <li>New requirement to assert are set signal each PLL when it has to reacquire lock on either a new clock after loss of lock (page 2-96).</li> <li>Updated max input frequency for CLK [1,3,8,10] from 462 to 500, Table 2-24.</li> <li>Renamed impedance matching to series termination throughout.</li> <li>Updated naming convention for DQS pins on page 2-112 to match pin tables.</li> <li>Added DDR SDRAM Performance Specification on page 2-117.</li> <li>Added external reference resistor values for terminator technology (page 2-136).</li> <li>Added Terminator Technology Specification on pages 2-137 and 2-138.</li> <li>Updated Tables 2-45 to 2-49 to reflect PLL cross-bank support for high speed differential channels at full speed.</li> <li>Wire bond package performance specification for "high" speed channels was increased to 624 Mbps from 462 Mbps throughout chapter.</li> </ul> |

| 3       | July 2005, v1.3      | <ul> <li>Updated "Operating Modes" section.</li> <li>Updated "Temperature Sensing Diode" section.</li> <li>Updated "IEEE Std. 1149.1 (JTAG) Boundary-Scan Support" section.</li> <li>Updated "Configuration" section.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | January 2005, v1.2   | Updated limits for JTAG chain of devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | September 2004, v1.1 | <ul> <li>Added new section, "Stratix Automated Single Event Upset (SEU)         Detection" on page 3–12.</li> <li>Updated description of "Custom-Built Circuitry" on page 3–13.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | April 2003, v1.0     | No new changes in Stratix Device Handbook v2.0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4       | January 2006, v3.4   | Added Table 4–135.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | July 2005, v3.3      | <ul> <li>Updated Tables 4–6 and 4–30.</li> <li>Updated Tables 4–103 through 4–108.</li> <li>Updated Tables 4–114 through 4–124.</li> <li>Updated Table 4–129.</li> <li>Added Table 4–130.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Altera Corporation Section I–3

| Table 1–1. Stratix Device Features — EP1S10, EP1S20, EP1S25, EP1S30 |         |           |           |           |  |  |  |  |  |  |  |

|---------------------------------------------------------------------|---------|-----------|-----------|-----------|--|--|--|--|--|--|--|

| Feature                                                             | EP1S10  | EP1S20    | EP1S25    | EP1S30    |  |  |  |  |  |  |  |

| LEs                                                                 | 10,570  | 18,460    | 25,660    | 32,470    |  |  |  |  |  |  |  |

| M512 RAM blocks (32 × 18 bits)                                      | 94      | 194       | 224       | 295       |  |  |  |  |  |  |  |

| M4K RAM blocks (128 × 36 bits)                                      | 60      | 82        | 138       | 171       |  |  |  |  |  |  |  |

| M-RAM blocks (4K × 144 bits)                                        | 1       | 2         | 2         | 4         |  |  |  |  |  |  |  |

| Total RAM bits                                                      | 920,448 | 1,669,248 | 1,944,576 | 3,317,184 |  |  |  |  |  |  |  |

| DSP blocks                                                          | 6       | 10        | 10        | 12        |  |  |  |  |  |  |  |

| Embedded multipliers (1)                                            | 48      | 80        | 80        | 96        |  |  |  |  |  |  |  |

| PLLs                                                                | 6       | 6         | 6         | 10        |  |  |  |  |  |  |  |

| Maximum user I/O pins                                               | 426     | 586       | 706       | 726       |  |  |  |  |  |  |  |

| Table 1–2. Stratix Device Features — EP1S40, EP1S60, EP1S80 |           |           |           |  |  |  |  |  |  |  |

|-------------------------------------------------------------|-----------|-----------|-----------|--|--|--|--|--|--|--|

| Feature                                                     | EP1S40    | EP1S60    | EP1S80    |  |  |  |  |  |  |  |

| LEs                                                         | 41,250    | 57,120    | 79,040    |  |  |  |  |  |  |  |

| M512 RAM blocks (32 × 18 bits)                              | 384       | 574       | 767       |  |  |  |  |  |  |  |

| M4K RAM blocks (128 × 36 bits)                              | 183       | 292       | 364       |  |  |  |  |  |  |  |

| M-RAM blocks (4K × 144 bits)                                | 4         | 6         | 9         |  |  |  |  |  |  |  |

| Total RAM bits                                              | 3,423,744 | 5,215,104 | 7,427,520 |  |  |  |  |  |  |  |

| DSP blocks                                                  | 14        | 18        | 22        |  |  |  |  |  |  |  |

| Embedded multipliers (1)                                    | 112       | 144       | 176       |  |  |  |  |  |  |  |

| PLLs                                                        | 12        | 12        | 12        |  |  |  |  |  |  |  |

| Maximum user I/O pins                                       | 822       | 1,022     | 1,238     |  |  |  |  |  |  |  |

#### Note to Tables 1–1 and 1–2:

<sup>(1)</sup> This parameter lists the total number of  $9 \times 9$ -bit multipliers for each device. For the total number of  $18 \times 18$ -bit multipliers per device, divide the total number of  $9 \times 9$ -bit multipliers by 2. For the total number of  $36 \times 36$ -bit multipliers per device, divide the total number of  $9 \times 9$ -bit multipliers by 8.

## 2. Stratix Architecture

\$51002-3.2

# Functional Description

Stratix® devices contain a two-dimensional row- and column-based architecture to implement custom logic. A series of column and row interconnects of varying length and speed provide signal interconnects between logic array blocks (LABs), memory block structures, and DSP blocks.

The logic array consists of LABs, with 10 logic elements (LEs) in each LAB. An LE is a small unit of logic providing efficient implementation of user logic functions. LABs are grouped into rows and columns across the device.

M512 RAM blocks are simple dual-port memory blocks with 512 bits plus parity (576 bits). These blocks provide dedicated simple dual-port or single-port memory up to 18-bits wide at up to 318 MHz. M512 blocks are grouped into columns across the device in between certain LABs.

M4K RAM blocks are true dual-port memory blocks with 4K bits plus parity (4,608 bits). These blocks provide dedicated true dual-port, simple dual-port, or single-port memory up to 36-bits wide at up to 291 MHz. These blocks are grouped into columns across the device in between certain LABs.

M-RAM blocks are true dual-port memory blocks with 512K bits plus parity (589,824 bits). These blocks provide dedicated true dual-port, simple dual-port, or single-port memory up to 144-bits wide at up to 269 MHz. Several M-RAM blocks are located individually or in pairs within the device's logic array.

Digital signal processing (DSP) blocks can implement up to either eight full-precision  $9\times 9$ -bit multipliers, four full-precision  $18\times 18$ -bit multipliers, or one full-precision  $36\times 36$ -bit multiplier with add or subtract features. These blocks also contain 18-bit input shift registers for digital signal processing applications, including FIR and infinite impulse response (IIR) filters. DSP blocks are grouped into two columns in each device.

Each Stratix device I/O pin is fed by an I/O element (IOE) located at the end of LAB rows and columns around the periphery of the device. I/O pins support numerous single-ended and differential I/O standards. Each IOE contains a bidirectional I/O buffer and six registers for registering input, output, and output-enable signals. When used with

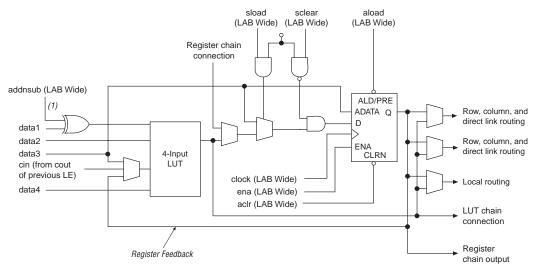

asynchronous preset load, synchronous clear, synchronous load, and clock enable control for the register. These LAB-wide signals are available in all LE modes. The addnsub control signal is allowed in arithmetic mode.

The Quartus II software, in conjunction with parameterized functions such as library of parameterized modules (LPM) functions, automatically chooses the appropriate mode for common functions such as counters, adders, subtractors, and arithmetic functions. If required, you can also create special-purpose functions that specify which LE operating mode to use for optimal performance.

#### Normal Mode

The normal mode is suitable for general logic applications and combinatorial functions. In normal mode, four data inputs from the LAB local interconnect are inputs to a four-input LUT (see Figure 2–6). The Quartus II Compiler automatically selects the carry-in or the data3 signal as one of the inputs to the LUT. Each LE can use LUT chain connections to drive its combinatorial output directly to the next LE in the LAB. Asynchronous load data for the register comes from the data3 input of the LE. LEs in normal mode support packed registers.

Figure 2-6. LE in Normal Mode

Note to Figure 2-6:

(1) This signal is only allowed in normal mode if the LE is at the end of an adder/subtractor chain.

Figure 2–8 shows the carry-select circuitry in an LAB for a 10-bit full adder. One portion of the LUT generates the sum of two bits using the input signals and the appropriate carry-in bit; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used for accumulator functions. Another portion of the LUT generates carry-out bits. An LAB-wide carry in bit selects which chain is used for the addition of given inputs. The carry-in signal for each chain, carry-in0 or carry-in1, selects the carry-out to carry forward to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it is fed to local, row, or column interconnects.

The Quartus II Compiler automatically creates carry chain logic during design processing, or you can create it manually during design entry. Parameterized functions such as LPM functions automatically take advantage of carry chains for the appropriate functions.

The Quartus II Compiler creates carry chains longer than 10 LEs by linking LABs together automatically. For enhanced fitting, a long carry chain runs vertically allowing fast horizontal connections to  $TriMatrix^{TM}$  memory and DSP blocks. A carry chain can continue as far as a full column.

C8 interconnects span eight LABs, M512, or M4K blocks up or down from a source LAB. Every LAB has its own set of C8 interconnects to drive either up or down. C8 interconnect connections between the LABs in a column are similar to the C4 connections shown in Figure 2–11 with the exception that they connect to eight LABs above and below. The C8 interconnects can drive and be driven by all types of architecture blocks similar to C4 interconnects. C8 interconnects can drive each other to extend their range as well as R8 interconnects for column-to-column connections. C8 interconnects are faster than two C4 interconnects.

C16 column interconnects span a length of 16 LABs and provide the fastest resource for long column connections between LABs, TriMatrix memory blocks, DSP blocks, and IOEs. C16 interconnects can cross M-RAM blocks and also drive to row and column interconnects at every fourth LAB. C16 interconnects drive LAB local interconnects via C4 and R4 interconnects and do not drive LAB local interconnects directly.

All embedded blocks communicate with the logic array similar to LAB-to-LAB interfaces. Each block (i.e., TriMatrix memory and DSP blocks) connects to row and column interconnects and has local interconnect regions driven by row and column interconnects. These blocks also have direct link interconnects for fast connections to and from a neighboring LAB. All blocks are fed by the row LAB clocks, labclk [7..0].

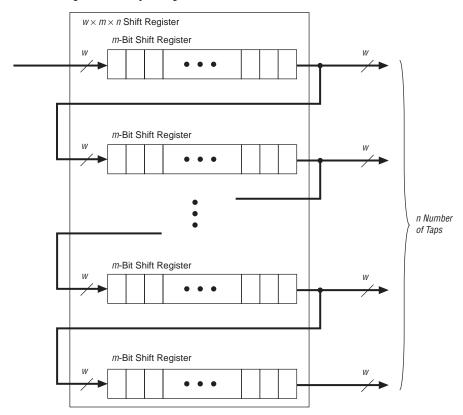

Figure 2-14. Shift Register Memory Configuration

## **Memory Block Size**

TriMatrix memory provides three different memory sizes for efficient application support. The large number of M512 blocks are ideal for designs with many shallow first-in first-out (FIFO) buffers. M4K blocks provide additional resources for channelized functions that do not require large amounts of storage. The M-RAM blocks provide a large single block of RAM ideal for data packet storage. The different-sized blocks allow Stratix devices to efficiently support variable-sized memory in designs.

The Quartus II software automatically partitions the user-defined memory into the embedded memory blocks using the most efficient size combinations. You can also manually assign the memory to a specific block size or a mixture of block sizes.

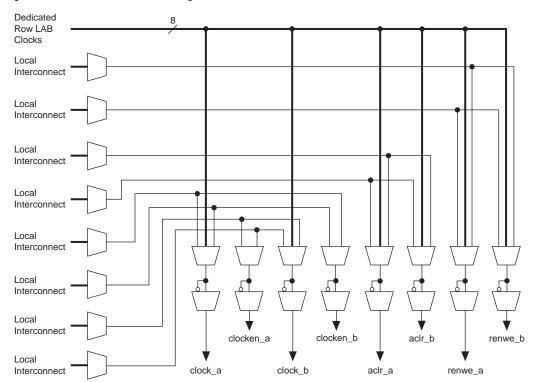

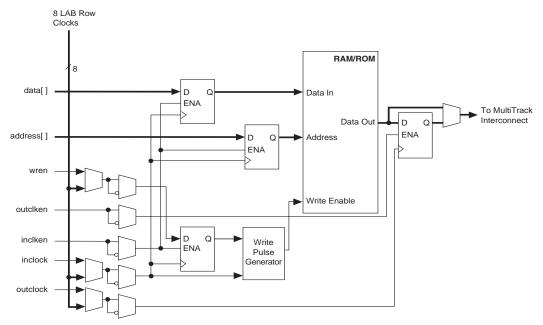

Figure 2-19. M-RAM Block Control Signals

One of the M-RAM block's horizontal sides drive the address and control signal (clock, renwe, byteena, etc.) inputs. Typically, the horizontal side closest to the device perimeter contains the interfaces. The one exception is when two M-RAM blocks are paired next to each other. In this case, the side of the M-RAM block opposite the common side of the two blocks contains the input interface. The top and bottom sides of any M-RAM block contain data input and output interfaces to the logic array. The top side has 72 data inputs and 72 data outputs for port B, and the bottom side has another 72 data inputs and 72 data outputs for port A. Figure 2–20 shows an example floorplan for the EP1S60 device and the location of the M-RAM interfaces.

## **Single-Port Mode**

The memory blocks also support single-port mode, used when simultaneous reads and writes are not required. See Figure 2–28. A single block in a memory block can support up to two single-port mode RAM blocks in the M4K RAM blocks if each RAM block is less than or equal to 2K bits in size.

Figure 2–28. Single-Port Mode Note (1)

Note to Figure 2-28:

(1) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

## Digital Signal Processing Block

The most commonly used DSP functions are finite impulse response (FIR) filters, complex FIR filters, infinite impulse response (IIR) filters, fast Fourier transform (FFT) functions, direct cosine transform (DCT) functions, and correlators. All of these blocks have the same fundamental building block: the multiplier. Additionally, some applications need specialized operations such as multiply-add and multiply-accumulate operations. Stratix devices provide DSP blocks to meet the arithmetic requirements of these functions.

Each Stratix device has two columns of DSP blocks to efficiently implement DSP functions faster than LE-based implementations. Larger Stratix devices have more DSP blocks per column (see Table 2–13). Each DSP block can be configured to support up to:

- Eight 9 × 9-bit multipliers

- Four 18 × 18-bit multipliers

- One 36 × 36-bit multiplier

As indicated, the Stratix DSP block can support one  $36 \times 36$ -bit multiplier in a single DSP block. This is true for any matched sign multiplications (either unsigned by unsigned or signed by signed), but the capabilities for dynamic and mixed sign multiplications are handled differently. The following list provides the largest functions that can fit into a single DSP block.

- 36 × 36-bit unsigned by unsigned multiplication

- 36 × 36-bit signed by signed multiplication

- 35 × 36-bit unsigned by signed multiplication

- 36 × 35-bit signed by unsigned multiplication

- 36 × 35-bit signed by dynamic sign multiplication

- 35 × 36-bit dynamic sign by signed multiplication

- 35 × 36-bit unsigned by dynamic sign multiplication

- 36 × 35-bit dynamic sign by unsigned multiplication

- 35 x 35-bit dynamic sign multiplication when the sign controls for each operand are different

- $36 \times 36$ -bit dynamic sign multiplication when the same sign control is used for both operands

This list only shows functions that can fit into a single DSP block. Multiple DSP blocks can support larger multiplication functions.

Figure 2–29 shows one of the columns with surrounding LAB rows.

For FIR filters, the DSP block combines the four-multipliers adder mode with the shift register inputs. One set of shift inputs contains the filter data, while the other holds the coefficients loaded in serial or parallel. The input shift register eliminates the need for shift registers external to the DSP block (i.e., implemented in LEs). This architecture simplifies filter design since the DSP block implements all of the filter circuitry.

One DSP block can implement an entire 18-bit FIR filter with up to four taps. For FIR filters larger than four taps, DSP blocks can be cascaded with additional adder stages implemented in LEs.

Table 2–16 shows the different number of multipliers possible in each DSP block mode according to size. These modes allow the DSP blocks to implement numerous applications for DSP including FFTs, complex FIR, FIR, and 2D FIR filters, equalizers, IIR, correlators, matrix multiplication and many other functions.

| Table 2–16. Multiplier Size & Configurations per DSP block |                                              |                                            |                                        |  |  |  |  |  |  |  |

|------------------------------------------------------------|----------------------------------------------|--------------------------------------------|----------------------------------------|--|--|--|--|--|--|--|

| DSP Block Mode                                             | 9 × 9                                        | 18 × 18                                    | <b>36</b> × <b>36</b> (1)              |  |  |  |  |  |  |  |

| Multiplier                                                 | Eight multipliers with eight product outputs | Four multipliers with four product outputs | One multiplier with one product output |  |  |  |  |  |  |  |

| Multiply-accumulator                                       | Two multiply and accumulate (52 bits)        | Two multiply and accumulate (52 bits)      | _                                      |  |  |  |  |  |  |  |

| Two-multipliers adder                                      | Four sums of two multiplier products each    | Two sums of two multiplier products each   | -                                      |  |  |  |  |  |  |  |

| Four-multipliers adder                                     | Two sums of four multiplier products each    | One sum of four multiplier products each   | -                                      |  |  |  |  |  |  |  |

Note to Table 2–16:

The number of supported multiply functions shown is based on signed/signed or unsigned/unsigned implementations.

#### **DSP Block Interface**

Stratix device DSP block outputs can cascade down within the same DSP block column. Dedicated connections between DSP blocks provide fast connections between the shift register inputs to cascade the shift register chains. You can cascade DSP blocks for  $9 \times 9$ - or  $18 \times 18$ -bit FIR filters larger than four taps, with additional adder stages implemented in LEs. If the DSP block is configured as  $36 \times 36$  bits, the adder, subtractor, or accumulator stages are implemented in LEs. Each DSP block can route the shift register chain out of the block to cascade two full columns of DSP blocks.

During switchover, the PLL VCO continues to run and will either slow down or speed up, generating frequency drift on the PLL outputs. The clock switchover transitions without any glitches. After the switch, there is a finite resynchronization period to lock onto new clock as the VCO ramps up. The exact amount of time it takes for the PLL to relock relates to the PLL configuration and may be adjusted by using the programmable bandwidth feature of the PLL. The specification for the maximum time to relock is  $100~\mu s$ .

For more information on clock switchover, see *AN 313, Implementing Clock Switchover in Stratix & Stratix GX Devices*.

#### PLL Reconfiguration

The PLL reconfiguration feature enables system logic to change Stratix device enhanced PLL counters and delay elements without reloading a Programmer Object File (.pof). This provides considerable flexibility for frequency synthesis, allowing real-time PLL frequency and output clock delay variation. You can sweep the PLL output frequencies and clock delay in prototype environments. The PLL reconfiguration feature can also dynamically or intelligently control system clock speeds or  $t_{\rm CO}$  delays in end systems.

Clock delay elements at each PLL output port implement variable delay. Figure 2–54 shows a diagram of the overall dynamic PLL control feature for the counters and the clock delay elements. The configuration time is less than 20 µs for the enhanced PLL using a input shift clock rate of 22 MHz. The charge pump, loop filter components, and phase shifting using VCO phase taps cannot be dynamically adjusted.

| Table 2–26. External RAM Support in EP1S60 & EP1S80 Devices |              |                          |                |                |  |  |  |  |  |  |  |

|-------------------------------------------------------------|--------------|--------------------------|----------------|----------------|--|--|--|--|--|--|--|

| DDD Momory Type                                             | I/O Standard | Maximum Clock Rate (MHz) |                |                |  |  |  |  |  |  |  |

| DDR Memory Type                                             | I/O Standard | -5 Speed Grade           | -6 Speed Grade | -7 Speed Grade |  |  |  |  |  |  |  |

| DDR SDRAM (1), (2)                                          | SSTL-2       | 167                      | 167            | 133            |  |  |  |  |  |  |  |

| DDR SDRAM - side banks (2), (3)                             | SSTL-2       | 150                      | 133            | 133            |  |  |  |  |  |  |  |

| QDR SRAM (4)                                                | 1.5-V HSTL   | 133                      | 133            | 133            |  |  |  |  |  |  |  |

| QDRII SRAM (4)                                              | 1.5-V HSTL   | 167                      | 167            | 133            |  |  |  |  |  |  |  |

| ZBT SRAM (5)                                                | LVTTL        | 200                      | 200            | 167            |  |  |  |  |  |  |  |

#### Notes to Table 2-26:

- (1) These maximum clock rates apply if the Stratix device uses DQS phase-shift circuitry to interface with DDR SDRAM. DQS phase-shift circuitry is only available in the top and bottom I/O banks (I/O banks 3, 4, 7, and 8).

- (2) For more information on DDR SDRAM, see AN 342: Interfacing DDR SDRAM with Stratix & Stratix GX Devices.

- (3) DDR SDRAM is supported on the Stratix device side I/O banks (I/O banks 1, 2, 5, and 6) without dedicated DQS phase-shift circuitry. The read DQS signal is ignored in this mode. Numbers are preliminary.

- (4) For more information on QDR or QDRII SRAM, see AN 349: QDR SRAM Controller Reference Design for Stratix & Stratix GX Devices.

- (5) For more information on ZBT SRAM, see AN 329: ZBT SRAM Controller Reference Design for Stratix & Stratix GX Devices.

In addition to six I/O registers and one input latch in the IOE for interfacing to these high-speed memory interfaces, Stratix devices also have dedicated circuitry for interfacing with DDR SDRAM. In every Stratix device, the I/O banks at the top (I/O banks 3 and 4) and bottom (I/O banks 7 and 8) of the device support DDR SDRAM up to 200 MHz. These pins support DQS signals with DQ bus modes of  $\times 8$ ,  $\times 16$ , or  $\times 32$ .

Table 2–27 shows the number of DQ and DQS buses that are supported per device.

| Table 2–27. DQS & DQ Bus Mode Support (Part 1 of 2) Note (1) |                                              |                        |                         |                         |  |  |  |  |  |  |

|--------------------------------------------------------------|----------------------------------------------|------------------------|-------------------------|-------------------------|--|--|--|--|--|--|

| Device                                                       | Package                                      | Number of ×8<br>Groups | Number of ×16<br>Groups | Number of ×32<br>Groups |  |  |  |  |  |  |

| EP1S10                                                       | 672-pin BGA<br>672-pin FineLine BGA          | 12 (2)                 | 0                       | 0                       |  |  |  |  |  |  |

|                                                              | 484-pin FineLine BGA<br>780-pin FineLine BGA | 16 (3)                 | 0                       | 4                       |  |  |  |  |  |  |

| EP1S20                                                       | 484-pin FineLine BGA                         | 18(4)                  | 7 (5)                   | 4                       |  |  |  |  |  |  |

|                                                              | 672-pin BGA<br>672-pin FineLine BGA          | 16(3)                  | 7 (5)                   | 4                       |  |  |  |  |  |  |

|                                                              | 780-pin FineLine BGA                         | 20                     | 7 (5)                   | 4                       |  |  |  |  |  |  |

The only way you can use the rx\_data\_align is if one of the following is true:

- The receiver PLL is only clocking receive channels (no resources for the transmitter)

- If all channels can fit in one I/O bank

| Table 2-38            | . EP1S30 Diffe  | erential Cha | nnels Note      | (1)       |           |           |           |                           |      |      |        |

|-----------------------|-----------------|--------------|-----------------|-----------|-----------|-----------|-----------|---------------------------|------|------|--------|

|                       | Transmitter     | Total        | Maximum         | C         | enter F   | ast PLI   | _S        | Corner Fast PLLs (2), (3) |      |      |        |

| Package               | /Receiver       | Channels     | Speed<br>(Mbps) | PLL1      | PLL2      | PLL3      | PLL4      | PLL7                      | PLL8 | PLL9 | PLL10  |

| 780-pin               | Transmitter     | 70           | 840             | 18        | 17        | 17        | 18        | (6)                       | (6)  | (6)  | (6)    |

| FineLine<br>BGA       | (4)             |              | 840 (5)         | 35        | 35        | 35        | 35        | (6)                       | (6)  | (6)  | (6)    |

|                       | Receiver        | 66           | 840             | 17        | 16        | 16        | 17        | (6)                       | (6)  | (6)  | (6)    |

|                       |                 |              | 840 (5)         | 33        | 33        | 33        | 33        | (6)                       | (6)  | (6)  | (6)    |

| 956-pin               | Transmitter     | ()           | 840             | 19        | 20        | 20        | 19        | 20                        | 20   | 20   | 20     |

| BGA                   | (4)             |              | 840 (5)         | 39        | 39        | 39        | 39        | 20                        | 20   | 20   | 20     |

|                       | Receiver        |              | 840             | 20        | 20        | 20        | 20        | 19                        | 20   | 20   | 19     |

|                       |                 |              | 840 (5)         | 40        | 40        | 40        | 40        | 19                        | 20   | 20   | 19     |

| 1,020-pin<br>FineLine | Transmitter (4) | 30 (2) (1)   | 840             | 19<br>(1) | 20        | 20        | 19<br>(1) | 20                        | 20   | 20   | 20     |

| BGA                   |                 |              | 840 (5),(8)     | 39<br>(1) | 39<br>(1) | 39<br>(1) | 39<br>(1) | 20                        | 20   | 20   | 20     |

|                       | Receiver        | 80 (2) (7)   | 840             | 20        | 20        | 20        | 20        | 19 (1)                    | 20   | 20   | 19 (1) |

|                       |                 |              | 840 (5),(8)     | 40        | 40        | 40        | 40        | 19 (1)                    | 20   | 20   | 19 (1) |

| Table 2-39                       | Table 2–39. EP1S40 Differential Channels (Part 1 of 2) Note (1) |                 |         |                  |      |      |      |                           |      |       |     |  |  |

|----------------------------------|-----------------------------------------------------------------|-----------------|---------|------------------|------|------|------|---------------------------|------|-------|-----|--|--|

| Package Transmitter/<br>Receiver | Transmitter/                                                    | Total           | Maximum | Center Fast PLLs |      |      |      | Corner Fast PLLs (2), (3) |      |       |     |  |  |

|                                  | Channels                                                        | Speed<br>(Mbps) | PLL1    | PLL2             | PLL3 | PLL4 | PLL7 | PLL8                      | PLL9 | PLL10 |     |  |  |

| 780-pin                          | •                                                               | 68              | 840     | 18               | 16   | 16   | 18   | (6)                       | (6)  | (6)   | (6) |  |  |

| FineLine<br>BGA                  | (4)                                                             |                 | 840 (5) | 34               | 34   | 34   | 34   | (6)                       | (6)  | (6)   | (6) |  |  |

|                                  | Receiver                                                        | 66              | 840     | 17               | 16   | 16   | 17   | (6)                       | (6)  | (6)   | (6) |  |  |

|                                  |                                                                 |                 | 840 (5) | 33               | 33   | 33   | 33   | (6)                       | (6)  | (6)   | (6) |  |  |

The transmitter external clock output is transmitted on a data channel. The txclk pin for each bank is located in between data transmitter pins. For  $\times 1$  clocks (e.g., 622 Mbps, 622 MHz), the high-speed PLL clock bypasses the SERDES to drive the output pins. For half-rate clocks (e.g., 622 Mbps, 311 MHz) or any other even-numbered factor such as 1/4, 1/7, 1/8, or 1/10, the SERDES automatically generates the clock in the Ouartus II software.

For systems that require more than four or eight high-speed differential I/O clock domains, a SERDES bypass implementation is possible using IOEs.

### **Byte Alignment**

For high-speed source synchronous interfaces such as POS-PHY 4, XSBI, RapidIO, and HyperTransport technology, the source synchronous clock rate is not a byte- or SERDES-rate multiple of the data rate. Byte alignment is necessary for these protocols since the source synchronous clock does not provide a byte or word boundary since the clock is one half the data rate, not one eighth. The Stratix device's high-speed differential I/O circuitry provides dedicated data realignment circuitry for user-controlled byte boundary shifting. This simplifies designs while saving LE resources. An input signal to each fast PLL can stall deserializer parallel data outputs by one bit period. You can use an LE-based state machine to signal the shift of receiver byte boundaries until a specified pattern is detected to indicate byte alignment.

## Power Sequencing & Hot Socketing

Because Stratix devices can be used in a mixed-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. Therefore, the VCCIO and VCCINT power supplies may be powered in any order.

Although you can power up or down the VCCIO and VCCINT power supplies in any sequence, you should not power down any I/O banks that contain configuration pins while leaving other I/O banks powered on. For power up and power down, all supplies (VCCINT and all VCCIO power planes) must be powered up and down within 100 ms of each other. This prevents I/O pins from driving out.

Signals can be driven into Stratix devices before and during power up without damaging the device. In addition, Stratix devices do not drive out during power up. Once operating conditions are reached and the device is configured, Stratix devices operate as specified by the user. For more information, see *Hot Socketing* in the *Selectable I/O Standards in Stratix & Stratix GX Devices* chapter in the *Stratix Device Handbook*, *Volume 2*.

Stratix, Stratix II, Cyclone<sup>®</sup>, and Cyclone II devices must be within the first 17 devices in a JTAG chain. All of these devices have the same JTAG controller. If any of the Stratix, Stratix II, Cyclone, and Cyclone II devices are in the 18th or after they will fail configuration. This does not affect SignalTap II.

For more information on JTAG, see the following documents:

- AN 39: IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices

- Jam Programming & Test Language Specification

## SignalTap II Embedded Logic Analyzer

Stratix devices feature the SignalTap II embedded logic analyzer, which monitors design operation over a period of time through the IEEE Std. 1149.1 (JTAG) circuitry. You can analyze internal logic at speed without bringing internal signals to the I/O pins. This feature is particularly important for advanced packages, such as FineLine BGA® packages, because it can be difficult to add a connection to a pin during the debugging process after a board is designed and manufactured.

## Configuration

The logic, circuitry, and interconnects in the Stratix architecture are configured with CMOS SRAM elements. Altera® devices are reconfigurable. Because every device is tested with a high-coverage production test program, you do not have to perform fault testing and can focus on simulation and design verification.

Stratix devices are configured at system power-up with data stored in an Altera serial configuration device or provided by a system controller. Altera offers in-system programmability (ISP)-capable configuration devices that configure Stratix devices via a serial data stream. Stratix devices can be configured in under 100 ms using 8-bit parallel data at 100 MHz. The Stratix device's optimized interface allows microprocessors to configure it serially or in parallel, and synchronously or asynchronously. The interface also enables microprocessors to treat Stratix devices as memory and configure them by writing to a virtual memory location, making reconfiguration easy. After a Stratix device has been configured, it can be reconfigured in-circuit by resetting the device and loading new data. Real-time changes can be made during system operation, enabling innovative reconfigurable computing applications.

## **Operating Modes**

The Stratix architecture uses SRAM configuration elements that require configuration data to be loaded each time the circuit powers up. The process of physically loading the SRAM data into the device is called configuration. During initialization, which occurs immediately after

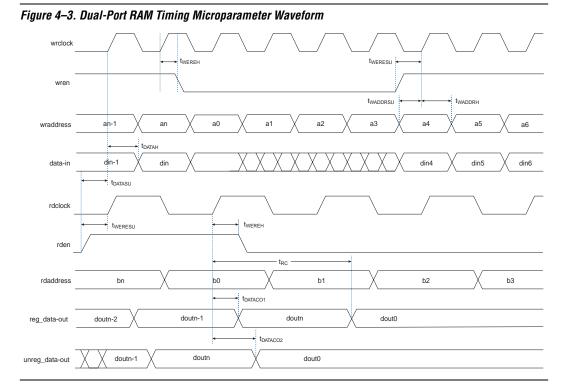

Figure 4–3 shows the TriMatrix memory waveforms for the M512, M4K, and M-RAM timing parameters shown in Tables 4–40 through 4–42.

Internal timing parameters are specified on a speed grade basis independent of device density. Tables 4–44 through 4–50 show the internal timing microparameters for LEs, IOEs, TriMatrix memory structures, DSP blocks, and MultiTrack interconnects.

| Table 4–43. Routing Delay Internal Timing Microparameter<br>Descriptions (Part 1 of 2) |                                                                                    |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Symbol                                                                                 | Parameter                                                                          |  |  |  |  |  |  |  |  |

| t <sub>R4</sub>                                                                        | Delay for an R4 line with average loading; covers a distance of four LAB columns.  |  |  |  |  |  |  |  |  |

| t <sub>R8</sub>                                                                        | Delay for an R8 line with average loading; covers a distance of eight LAB columns. |  |  |  |  |  |  |  |  |

| t <sub>R24</sub>                                                                       | Delay for an R24 line with average loading; covers a distance of 24 LAB columns.   |  |  |  |  |  |  |  |  |

Tables 4–61 through 4–66 show the external timing parameters on column and row pins for EP1S20 devices.

Table 4–61. EP1S20 External I/O Timing on Column Pins Using Fast Regional Clock Networks Note (1) -5 Speed Grade -6 Speed Grade -7 Speed Grade -8 Speed Grade Parameter Unit Min Max Min Max Min Max Min Max 2.065 2.245 2.576 NA ns t<sub>INSU</sub> 0.000 0.000 0.000 NA ns  $t_{INH}$ 2.283 4.622 2.283 4.916 2.283 5.310 NA NA toutco ns 2.223 2.223 4.496 4.784 2.223 5.186 NA NA  $t_{XZ}$ ns 2.223 4.496 2.223 4.784 2.223 5.186 NA NA  $t_{ZX}$ ns

| Table 4–62. I         | Table 4–62. EP1S20 External I/O Timing on Column Pins Using Regional Clock Networks Note (1) |         |         |         |         |         |         |     |      |  |  |  |  |

|-----------------------|----------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|-----|------|--|--|--|--|

| Davamatav             | -5 Spee                                                                                      | d Grade | -6 Spee | d Grade | -7 Spee | d Grade | -8 Spee |     |      |  |  |  |  |

| Parameter             | Min                                                                                          | Max     | Min     | Max     | Min     | Max     | Min     | Max | Unit |  |  |  |  |

| t <sub>INSU</sub>     | 1.541                                                                                        |         | 1.680   |         | 1.931   |         | NA      |     | ns   |  |  |  |  |

| t <sub>INH</sub>      | 0.000                                                                                        |         | 0.000   |         | 0.000   |         | NA      |     | ns   |  |  |  |  |

| t <sub>OUTCO</sub>    | 2.597                                                                                        | 5.146   | 2.597   | 5.481   | 2.597   | 5.955   | NA      | NA  | ns   |  |  |  |  |

| t <sub>XZ</sub>       | 2.537                                                                                        | 5.020   | 2.537   | 5.349   | 2.537   | 5.831   | NA      | NA  | ns   |  |  |  |  |

| t <sub>ZX</sub>       | 2.537                                                                                        | 5.020   | 2.537   | 5.349   | 2.537   | 5.831   | NA      | NA  | ns   |  |  |  |  |

| t <sub>INSUPLL</sub>  | 0.777                                                                                        |         | 0.818   |         | 0.937   |         | NA      |     | ns   |  |  |  |  |

| t <sub>INHPLL</sub>   | 0.000                                                                                        |         | 0.000   |         | 0.000   |         | NA      |     | ns   |  |  |  |  |

| t <sub>OUTCOPLL</sub> | 1.296                                                                                        | 2.690   | 1.296   | 2.801   | 1.296   | 2.876   | NA      | NA  | ns   |  |  |  |  |

| t <sub>XZPLL</sub>    | 1.236                                                                                        | 2.564   | 1.236   | 2.669   | 1.236   | 2.752   | NA      | NA  | ns   |  |  |  |  |

| t <sub>ZXPLL</sub>    | 1.236                                                                                        | 2.564   | 1.236   | 2.669   | 1.236   | 2.752   | NA      | NA  | ns   |  |  |  |  |

| O                                           | 0                                                                                 | -5 8  | Speed G | irade | -6 8  | Speed G | rade | -7 Speed Grade |     |     | -8 Speed Grade |     |     | 11!4 |

|---------------------------------------------|-----------------------------------------------------------------------------------|-------|---------|-------|-------|---------|------|----------------|-----|-----|----------------|-----|-----|------|

| Symbol                                      | Conditions                                                                        | Min   | Тур     | Max   | Min   | Тур     | Max  | Min            | Тур | Max | Min            | Тур | Max | Unit |

| SW                                          | PCML ( <i>J</i> = 4, 7, 8, 10)                                                    | 750   |         |       | 750   |         |      | 800            |     |     | 800            |     |     | ps   |

|                                             | PCML ( <i>J</i> = 2)                                                              | 900   |         |       | 900   |         |      | 1,200          |     |     | 1,200          |     |     | ps   |

|                                             | PCML ( <i>J</i> = 1)                                                              | 1,500 |         |       | 1,500 |         |      | 1,700          |     |     | 1,700          |     |     | ps   |

|                                             | LVDS and LVPECL (J = 1)                                                           | 500   |         |       | 500   |         |      | 550            |     |     | 550            |     |     | ps   |

|                                             | LVDS,<br>LVPECL,<br>HyperTransport<br>technology<br>( <i>J</i> = 2 through<br>10) | 440   |         |       | 440   |         |      | 500            |     |     | 500            |     |     | ps   |

| Input jitter<br>tolerance<br>(peak-to-peak) | All                                                                               |       |         | 250   |       |         | 250  |                |     | 250 |                |     | 250 | ps   |

| Output jitter<br>(peak-to-peak)             | All                                                                               |       |         | 160   |       |         | 160  |                |     | 200 |                |     | 200 | ps   |

| Output t <sub>RISE</sub>                    | LVDS                                                                              | 80    | 110     | 120   | 80    | 110     | 120  | 80             | 110 | 120 | 80             | 110 | 120 | ps   |

|                                             | HyperTransport technology                                                         | 110   | 170     | 200   | 110   | 170     | 200  | 120            | 170 | 200 | 120            | 170 | 200 | ps   |

|                                             | LVPECL                                                                            | 90    | 130     | 150   | 90    | 130     | 150  | 100            | 135 | 150 | 100            | 135 | 150 | ps   |

|                                             | PCML                                                                              | 80    | 110     | 135   | 80    | 110     | 135  | 80             | 110 | 135 | 80             | 110 | 135 | ps   |

| Output t <sub>FALL</sub>                    | LVDS                                                                              | 80    | 110     | 120   | 80    | 110     | 120  | 80             | 110 | 120 | 80             | 110 | 120 | ps   |

|                                             | HyperTransport technology                                                         | 110   | 170     | 200   | 110   | 170     | 200  | 110            | 170 | 200 | 110            | 170 | 200 | ps   |

|                                             | LVPECL                                                                            | 90    | 130     | 160   | 90    | 130     | 160  | 100            | 135 | 160 | 100            | 135 | 160 | ps   |

|                                             | PCML                                                                              | 105   | 140     | 175   | 105   | 140     | 175  | 110            | 145 | 175 | 110            | 145 | 175 | ps   |

**High-Speed I/O Specification**