Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 2566                                                     |

| Number of Logic Elements/Cells | 25660                                                    |

| Total RAM Bits                 | 1944576                                                  |

| Number of I/O                  | 473                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                       |

| Package / Case                 | 672-BBGA                                                 |

| Supplier Device Package        | 672-FBGA (27x27)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s25f672i7n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

viii Altera Corporation

| Table 1–5. Stratix FineLine BGA Package Sizes                                                    |         |         |         |           |           |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------|---------|---------|---------|-----------|-----------|--|--|--|--|--|

| Dimension                                                                                        | 484 Pin | 672 Pin | 780 Pin | 1,020 Pin | 1,508 Pin |  |  |  |  |  |

| Pitch (mm)                                                                                       | 1.00    | 1.00    | 1.00    | 1.00      | 1.00      |  |  |  |  |  |

| Area (mm²)                                                                                       | 529     | 729     | 841     | 1,089     | 1,600     |  |  |  |  |  |

| $\begin{array}{c} \text{Length} \times \text{width} \\ \text{(mm} \times \text{mm)} \end{array}$ | 23 × 23 | 27 × 27 | 29 × 29 | 33 × 33   | 40 × 40   |  |  |  |  |  |

Stratix devices are available in up to four speed grades, -5, -6, -7, and -8, with -5 being the fastest. Table 1–6 shows Stratix device speed-grade offerings.

| Table 1–6. | Table 1–6. Stratix Device Speed Grades |                |                            |                            |                            |                              |                              |  |  |  |  |  |

|------------|----------------------------------------|----------------|----------------------------|----------------------------|----------------------------|------------------------------|------------------------------|--|--|--|--|--|

| Device     | 672-Pin<br>BGA                         | 956-Pin<br>BGA | 484-Pin<br>FineLine<br>BGA | 672-Pin<br>FineLine<br>BGA | 780-Pin<br>FineLine<br>BGA | 1,020-Pin<br>FineLine<br>BGA | 1,508-Pin<br>FineLine<br>BGA |  |  |  |  |  |

| EP1S10     | -6, -7                                 |                | -5, -6, -7                 | -6, -7                     | -5, -6, -7                 |                              |                              |  |  |  |  |  |

| EP1S20     | -6, -7                                 |                | -5, -6, -7                 | -6, -7                     | -5, -6, -7                 |                              |                              |  |  |  |  |  |

| EP1S25     | -6, -7                                 |                |                            | -6, -7, -8                 | -5, -6, -7                 | -5, -6, -7                   |                              |  |  |  |  |  |

| EP1S30     |                                        | -5, -6, -7     |                            |                            | -5, -6, -7, -8             | -5, -6, -7                   |                              |  |  |  |  |  |

| EP1S40     |                                        | -5, -6, -7     |                            |                            | -5, -6, -7, -8             | -5, -6, -7                   | -5, -6, -7                   |  |  |  |  |  |

| EP1S60     |                                        | -6, -7         |                            |                            |                            | -5, -6, -7                   | -6, -7                       |  |  |  |  |  |

| EP1S80     |                                        | -6, -7         |                            |                            |                            | -5, -6, -7                   | -5, -6, -7                   |  |  |  |  |  |

dedicated clocks, these registers provide exceptional performance and interface support with external memory devices such as DDR SDRAM, FCRAM, ZBT, and QDR SRAM devices.

High-speed serial interface channels support transfers at up to 840 Mbps using LVDS, LVPECL, 3.3-V PCML, or HyperTransport technology I/O standards.

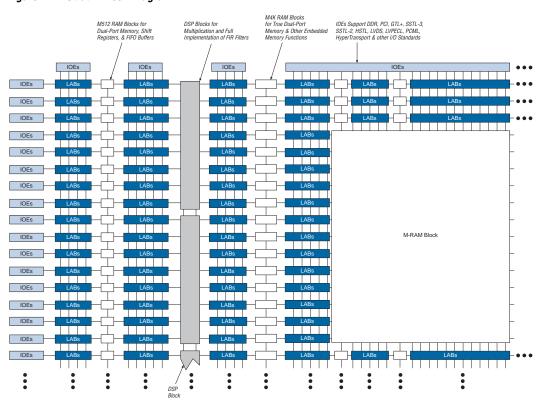

Figure 2–1 shows an overview of the Stratix device.

Figure 2-1. Stratix Block Diagram

blocks facing to the left, and another 10 possible from the right adjacent LABs for M-RAM blocks facing to the right. For column interfacing, every M-RAM column unit connects to the right and left column lines, allowing each M-RAM column unit to communicate directly with three columns of LABs. Figures 2–21 through 2–23 show the interface between the M-RAM block and the logic array.

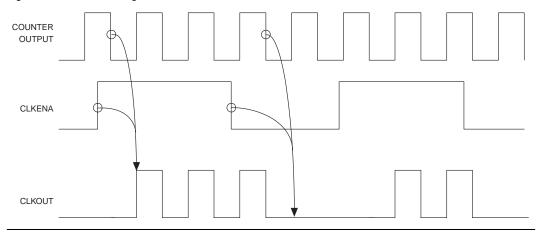

resynchronization or relock period. The clkena signal can also disable clock outputs if the system is not tolerant to frequency overshoot during resynchronization.

The extclkena signals work in the same way as the clkena signals, but they control the external clock output counters (e0, e1, e2, and e3). Upon re-enabling, the PLL does not need a resynchronization or relock period unless the PLL is using external feedback mode. In order to lock in external feedback mode, the external output must drive the board trace back to the FBIN pin.

Figure 2-57. extclkena Signals

### **Fast PLLs**

Stratix devices contain up to eight fast PLLs with high-speed serial interfacing ability, along with general-purpose features. Figure 2–58 shows a diagram of the fast PLL.

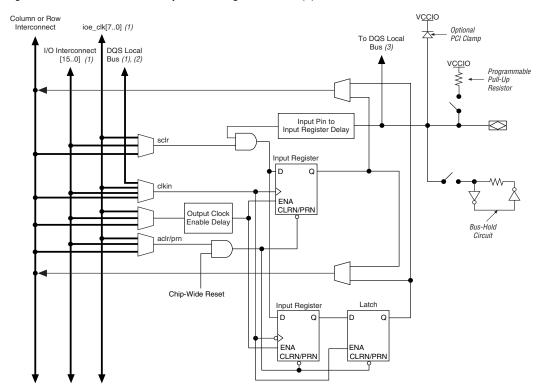

Each IOE contains its own control signal selection for the following control signals: oe, ce\_in, ce\_out, aclr/preset, sclr/preset, clk\_in, and clk\_out. Figure 2–63 illustrates the control signal selection.

io bclk[3..0] io\_bce[3..0] io\_bclr[3..0] io\_boe[3..0] Dedicated I/O Clock [7..0] I/O Interconnect [15..0] io\_coe Local Interconnect io\_cclr Local Interconnect io\_cce\_out Local Interconnect io cce in Local Interconnect io\_cclk clk\_out ce\_out sclr/preset Local Interconnect

ce\_in

clk in

Figure 2-63. Control Signal Selection per IOE

In normal bidirectional operation, the input register can be used for input data requiring fast setup times. The input register can have its own clock input and clock enable separate from the OE and output registers. The output register can be used for data requiring fast clock-to-output performance. The OE register can be used for fast clock-to-output enable timing. The OE and output register share the same clock source and the same clock enable source from local interconnect in the associated LAB, dedicated I/O clocks, and the column and row interconnects. Figure 2–64 shows the IOE in bidirectional configuration.

aclr/preset

oe

Figure 2–65. Stratix IOE in DDR Input I/O Configuration Note (1)

*Notes to Figure 2–65:*

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) This signal connection is only allowed on dedicated DQ function pins.

- (3) This signal is for dedicated DQS function pins only.

shift by the same degree amount. For example, all 10 DQS pins on the top of the device can be shifted by 90° and all 10 DQS pins on the bottom of the device can be shifted by 72°. The reference circuits require a maximum of 256 system reference clock cycles to set the correct phase on the DQS delay elements. Figure 2–69 illustrates the phase-shift reference circuit control of each DQS delay shift on the top of the device. This same circuit is duplicated on the bottom of the device.

Input

Reference

Clock

Phase

Comparator

Up/Down

Counter

Delay Chains

Control Signals to DQS Pins

Figure 2-69. Simplified Diagram of the DQS Phase-Shift Circuitry

See the *External Memory Interfaces* chapter in the *Stratix Device Handbook, Volume 2* for more information on external memory interfaces.

## **Programmable Drive Strength**

The output buffer for each Stratix device I/O pin has a programmable drive strength control for certain I/O standards. The LVTTL and LVCMOS standard has several levels of drive strength that the user can control. SSTL-3 Class I and II, SSTL-2 Class I and II, HSTL Class I and II, and 3.3-V GTL+ support a minimum setting, the lowest drive strength that guarantees the  $I_{OH}/I_{OL}$  of the standard. Using minimum settings provides signal slew rate control to reduce system noise and signal overshoot.

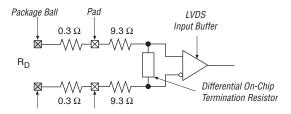

However, there is additional resistance present between the device ball and the input of the receiver buffer, as shown in Figure 2–72. This resistance is because of package trace resistance (which can be calculated as the resistance from the package ball to the pad) and the parasitic layout metal routing resistance (which is shown between the pad and the intersection of the on-chip termination and input buffer).

Figure 2-72. Differential Resistance of LVDS Differential Pin Pair (Rp)

Table 2–35 defines the specification for internal termination resistance for commercial devices.

| Table 2-3          | Table 2–35. Differential On-Chip Termination |                     |             |      |     |   |  |  |  |  |  |

|--------------------|----------------------------------------------|---------------------|-------------|------|-----|---|--|--|--|--|--|

| Cumbal             | Description                                  | Conditions          | R           | Unit |     |   |  |  |  |  |  |

| Symbol             | Description                                  | Collations          | Min Typ Max |      |     |   |  |  |  |  |  |

| R <sub>D</sub> (2) | Internal differential termination for LVDS   | Commercial (1), (3) | 110         | 135  | 165 | W |  |  |  |  |  |

|                    |                                              | Industrial (2), (3) | 100         | 135  | 170 | W |  |  |  |  |  |

Notes to Table 2-35:

- (1) Data measured over minimum conditions ( $T_j = 0 \text{ C}$ ,  $V_{\text{CCIO}} + 5\%$ ) and maximum conditions ( $T_j = 85 \text{ C}$ ,  $V_{\text{CCIO}} = -5\%$ ).

- (2) Data measured over minimum conditions ( $T_j = -40$  C,  $V_{CCIO} + 5\%$ ) and maximum conditions ( $T_j = 100$  C,  $V_{CCIO} = -5\%$ ).

- (3) LVDS data rate is supported for 840 Mbps using internal differential termination.

#### MultiVolt I/O Interface

The Stratix architecture supports the MultiVolt I/O interface feature, which allows Stratix devices in all packages to interface with systems of different supply voltages.

The Stratix VCCINT pins must always be connected to a 1.5-V power supply. With a 1.5-V  $V_{CCINT}$  level, input pins are 1.5-V, 1.8-V, 2.5-V, and 3.3-V tolerant. The VCCIO pins can be connected to either a 1.5-V, 1.8-V, 2.5-V, or 3.3-V power supply, depending on the output requirements.

The only way you can use the rx\_data\_align is if one of the following is true:

- The receiver PLL is only clocking receive channels (no resources for the transmitter)

- If all channels can fit in one I/O bank

| Table 2-38            | Table 2–38. EP1S30 Differential Channels Note (1) |            |                 |           |           |           |           |        |                         |      |        |    |

|-----------------------|---------------------------------------------------|------------|-----------------|-----------|-----------|-----------|-----------|--------|-------------------------|------|--------|----|

|                       | Transmitter                                       | Total      | Maximum         | C         | enter F   | ast PLI   | _S        | Corn   | Corner Fast PLLs (2), ( |      |        |    |

| Package               | /Receiver                                         | Channels   | Speed<br>(Mbps) | PLL1      | PLL2      | PLL3      | PLL4      | PLL7   | PLL8                    | PLL9 | PLL10  |    |

| 780-pin               | Transmitter                                       | 70         | 840             | 18        | 17        | 17        | 18        | (6)    | (6)                     | (6)  | (6)    |    |

| FineLine<br>BGA       | (4)                                               |            | 840 (5)         | 35        | 35        | 35        | 35        | (6)    | (6)                     | (6)  | (6)    |    |

| 20.71                 | Receiver                                          | 66         | 840             | 17        | 16        | 16        | 17        | (6)    | (6)                     | (6)  | (6)    |    |

|                       |                                                   |            | 840 (5)         | 33        | 33        | 33        | 33        | (6)    | (6)                     | (6)  | (6)    |    |

| 956-pin               | Transmitter (4)                                   |            | 80              | 840       | 19        | 20        | 20        | 19     | 20                      | 20   | 20     | 20 |

| BGA                   |                                                   |            | 840 (5)         | 39        | 39        | 39        | 39        | 20     | 20                      | 20   | 20     |    |

|                       | Receiver                                          | 80         | 840             | 20        | 20        | 20        | 20        | 19     | 20                      | 20   | 19     |    |

|                       |                                                   |            | 840 (5)         | 40        | 40        | 40        | 40        | 19     | 20                      | 20   | 19     |    |

| 1,020-pin<br>FineLine | Transmitter (4)                                   | 80 (2) (7) | 840             | 19<br>(1) | 20        | 20        | 19<br>(1) | 20     | 20                      | 20   | 20     |    |

| BGA                   |                                                   |            | 840 (5),(8)     | 39<br>(1) | 39<br>(1) | 39<br>(1) | 39<br>(1) | 20     | 20                      | 20   | 20     |    |

|                       | Receiver                                          | 80 (2) (7) | 840             | 20        | 20        | 20        | 20        | 19 (1) | 20                      | 20   | 19 (1) |    |

|                       |                                                   |            | 840 (5),(8)     | 40        | 40        | 40        | 40        | 19 (1) | 20                      | 20   | 19 (1) |    |

| Table 2–39. EP1S40 Differential Channels (Part 1 of 2) Note (1) |                 |          |                 |      |         |         |      |      |                      |      |       |  |

|-----------------------------------------------------------------|-----------------|----------|-----------------|------|---------|---------|------|------|----------------------|------|-------|--|

|                                                                 | Transmitter/    | Total    | Maximum         | C    | enter F | ast PLI | -S   | Corn | Corner Fast PLLs (2) |      |       |  |

| Package                                                         | Receiver        | Channels | Speed<br>(Mbps) | PLL1 | PLL2    | PLL3    | PLL4 | PLL7 | PLL8                 | PLL9 | PLL10 |  |

| 780-pin                                                         | Transmitter (4) |          | 840             | 18   | 16      | 16      | 18   | (6)  | (6)                  | (6)  | (6)   |  |

| FineLine<br>BGA                                                 |                 |          | 840 (5)         | 34   | 34      | 34      | 34   | (6)  | (6)                  | (6)  | (6)   |  |

|                                                                 | Receiver        | 66       | 840             | 17   | 16      | 16      | 17   | (6)  | (6)                  | (6)  | (6)   |  |

|                                                                 |                 |          | 840 (5)         | 33   | 33      | 33      | 33   | (6)  | (6)                  | (6)  | (6)   |  |

The Stratix device instruction register length is 10 bits and the USERCODE register length is 32 bits. Tables 3–2 and 3–3 show the boundary-scan register length and device IDCODE information for Stratix devices.

| Table 3–2. Stratix Boundary-Scan Register Length |                               |  |  |  |  |  |  |  |

|--------------------------------------------------|-------------------------------|--|--|--|--|--|--|--|

| Device                                           | Boundary-Scan Register Length |  |  |  |  |  |  |  |

| EP1S10                                           | 1,317                         |  |  |  |  |  |  |  |

| EP1S20                                           | 1,797                         |  |  |  |  |  |  |  |

| EP1S25                                           | 2,157                         |  |  |  |  |  |  |  |

| EP1S30                                           | 2,253                         |  |  |  |  |  |  |  |

| EP1S40                                           | 2,529                         |  |  |  |  |  |  |  |

| EP1S60                                           | 3,129                         |  |  |  |  |  |  |  |

| EP1S80                                           | 3,777                         |  |  |  |  |  |  |  |

| Table 3–3 | Table 3–3. 32-Bit Stratix Device IDCODE |                       |                                    |                 |  |  |  |  |  |  |  |

|-----------|-----------------------------------------|-----------------------|------------------------------------|-----------------|--|--|--|--|--|--|--|

|           | IDCODE (32 Bits) (1)                    |                       |                                    |                 |  |  |  |  |  |  |  |

| Device    | Version (4 Bits)                        | Part Number (16 Bits) | Manufacturer Identity<br>(11 Bits) | LSB (1 Bit) (2) |  |  |  |  |  |  |  |

| EP1S10    | 0000                                    | 0010 0000 0000 0001   | 000 0110 1110                      | 1               |  |  |  |  |  |  |  |

| EP1S20    | 0000                                    | 0010 0000 0000 0010   | 000 0110 1110                      | 1               |  |  |  |  |  |  |  |

| EP1S25    | 0000                                    | 0010 0000 0000 0011   | 000 0110 1110                      | 1               |  |  |  |  |  |  |  |

| EP1S30    | 0000                                    | 0010 0000 0000 0100   | 000 0110 1110                      | 1               |  |  |  |  |  |  |  |

| EP1S40    | 0000                                    | 0010 0000 0000 0101   | 000 0110 1110                      | 1               |  |  |  |  |  |  |  |

| EP1S60    | 0000                                    | 0010 0000 0000 0110   | 000 0110 1110                      | 1               |  |  |  |  |  |  |  |

| EP1S80    | 0000                                    | 0010 0000 0000 0111   | 000 0110 1110                      | 1               |  |  |  |  |  |  |  |

Notes to Tables 3-2 and 3-3:

- (1) The most significant bit (MSB) is on the left.

- (2) The IDCODE's least significant bit (LSB) is always 1.

While in the factory configuration, the factory-configuration logic performs the following operations:

- Loads a remote update-control register to determine the page address of the new application configuration

- Determines whether to enable a user watchdog timer for the application configuration

- Determines what the watchdog timer setting should be if it is enabled

The user watchdog timer is a counter that must be continually reset within a specific amount of time in the user mode of an application configuration to ensure that valid configuration occurred during a remote update. Only valid application configurations designed for remote update can reset the user watchdog timer in user mode. If a valid application configuration does not reset the user watchdog timer in a specific amount of time, the timer updates a status register and loads the factory configuration. The user watchdog timer is automatically disabled for factory configurations.

If an error occurs in loading the application configuration, the configuration logic writes a status register to specify the cause of the error. Once this occurs, the Stratix device automatically loads the factory configuration, which reads the status register and determines the reason for reconfiguration. Based on the reason, the factory configuration will take appropriate steps and will write the remote update control register to specify the next application configuration page to be loaded.

When the Stratix device successfully loads the application configuration, it enters into user mode. The Stratix device then executes the main application of the user. Intellectual property (IP), such as a Nios® (16-bit ISA) and Nios® II (32-bit ISA) embedded processors, can help the Stratix device determine when remote update is coming. The Nios embedded processor or user logic receives incoming data, writes it to the configuration device, and loads the factory configuration. The factory configuration will read the remote update status register and determine the valid application configuration to load. Figure 3–2 shows the Stratix remote update. Figure 3–3 shows the transition diagram for remote update mode.

Table 4–52 shows the external I/O timing parameters when using fast regional clock networks.

|                    | <b>Table 4–52. Stratix Fast Regional Clock External I/O Timing Parameters</b> <i>Notes</i> (1), (2)                  |  |  |  |  |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Symbol             | Parameter                                                                                                            |  |  |  |  |  |  |  |  |

| t <sub>INSU</sub>  | Setup time for input or bidirectional pin using IOE input register with fast regional clock fed by FCLK pin          |  |  |  |  |  |  |  |  |

| t <sub>INH</sub>   | Hold time for input or bidirectional pin using IOE input register with fast regional clock fed by FCLK pin           |  |  |  |  |  |  |  |  |

| t <sub>outco</sub> | Clock-to-output delay output or bidirectional pin using IOE output register with fast regional clock fed by FCLK pin |  |  |  |  |  |  |  |  |

| t <sub>XZ</sub>    | Synchronous IOE output enable register to output pin disable delay using fast regional clock fed by FCLK pin         |  |  |  |  |  |  |  |  |

| t <sub>ZX</sub>    | Synchronous IOE output enable register to output pin enable delay using fast regional clock fed by FCLK pin          |  |  |  |  |  |  |  |  |

Notes to Table 4-52:

- (1) These timing parameters are sample-tested only.

- (2) These timing parameters are for column and row IOE pins. You should use the Quartus II software to verify the external timing for any pin.

Table 4–53 shows the external I/O timing parameters when using regional clock networks.

| Symbol                | Parameter                                                                                                                               |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>INSU</sub>     | Setup time for input or bidirectional pin using IOE input register with regional clock fed by CLK pin                                   |

| t <sub>INH</sub>      | Hold time for input or bidirectional pin using IOE input register with regional clock fed by CLK pin                                    |

| t <sub>OUTCO</sub>    | Clock-to-output delay output or bidirectional pin using IOE output register with regional clock fed by CLK pin                          |

| t <sub>INSUPLL</sub>  | Setup time for input or bidirectional pin using IOE input register with regional clock fed by Enhanced PLL with default phase setting   |

| t <sub>INHPLL</sub>   | Hold time for input or bidirectional pin using IOE input register with regional clock fed by Enhanced PLL with default phase setting    |

| t <sub>OUTCOPLL</sub> | Clock-to-output delay output or bidirectional pin using IOE output register with regional clock Enhanced PLL with default phase setting |

| Table 4-87. I         | Table 4–87. EP1S60 External I/O Timing on Column Pins Using Global Clock Networks Note (1) |       |         |                |       |         |         |     |      |  |

|-----------------------|--------------------------------------------------------------------------------------------|-------|---------|----------------|-------|---------|---------|-----|------|--|

| Davamatav             | -5 Speed Grade                                                                             |       | -6 Spee | -6 Speed Grade |       | d Grade | -8 Spee |     |      |  |

| Parameter             | Min                                                                                        | Max   | Min     | Max            | Min   | Max     | Min     | Max | Unit |  |

| t <sub>INSU</sub>     | 2.000                                                                                      |       | 2.152   |                | 2.441 |         | NA      |     | ns   |  |

| t <sub>INH</sub>      | 0.000                                                                                      |       | 0.000   |                | 0.000 |         | NA      |     | ns   |  |

| t <sub>OUTCO</sub>    | 3.051                                                                                      | 5.900 | 3.051   | 6.340          | 3.051 | 6.977   | NA      | NA  | ns   |  |

| t <sub>XZ</sub>       | 2.991                                                                                      | 5.774 | 2.991   | 6.208          | 2.991 | 6.853   | NA      | NA  | ns   |  |

| t <sub>ZX</sub>       | 2.991                                                                                      | 5.774 | 2.991   | 6.208          | 2.991 | 6.853   | NA      | NA  | ns   |  |

| t <sub>INSUPLL</sub>  | 1.315                                                                                      |       | 1.362   |                | 1.543 |         | NA      |     | ns   |  |

| t <sub>INHPLL</sub>   | 0.000                                                                                      |       | 0.000   |                | 0.000 |         | NA      |     | ns   |  |

| t <sub>OUTCOPLL</sub> | 1.029                                                                                      | 2.196 | 1.029   | 2.303          | 1.029 | 2.323   | NA      | NA  | ns   |  |

| t <sub>XZPLL</sub>    | 0.969                                                                                      | 2.070 | 0.969   | 2.171          | 0.969 | 2.199   | NA      | NA  | ns   |  |

| t <sub>ZXPLL</sub>    | 0.969                                                                                      | 2.070 | 0.969   | 2.171          | 0.969 | 2.199   | NA      | NA  | ns   |  |

| Table 4–88. EP1S60 External I/O Timing on Row Pins Using Fast Regional Clock Networks Note (1) |                |       |                |       |                |       |                |     |      |  |

|------------------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-----|------|--|

| Parameter                                                                                      | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |     |      |  |

|                                                                                                | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max | Unit |  |

| t <sub>INSU</sub>                                                                              | 3.144          |       | 3.393          |       | 3.867          |       | NA             |     | ns   |  |

| t <sub>INH</sub>                                                                               | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns   |  |

| t <sub>OUTCO</sub>                                                                             | 2.643          | 5.275 | 2.643          | 5.654 | 2.643          | 6.140 | NA             | NA  | ns   |  |

| t <sub>XZ</sub>                                                                                | 2.670          | 5.329 | 2.670          | 5.710 | 2.670          | 6.208 | NA             | NA  | ns   |  |

| t <sub>ZX</sub>                                                                                | 2.670          | 5.329 | 2.670          | 5.710 | 2.670          | 6.208 | NA             | NA  | ns   |  |

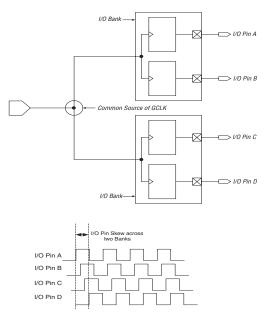

Figure 4–6 shows the case where four IOE registers are located in two different I/O banks.

Figure 4-6. I/O Skew Across Two I/O Banks

Table 4–97 defines the timing parameters used to define the timing for horizontal I/O pins (side banks 1, 2, 5, 6) and vertical I/O pins (top and bottom banks 3, 4, 7, 8). The timing parameters define the skew within an I/O bank, across two neighboring I/O banks on the same side of the device, across all horizontal I/O banks, across all vertical I/O banks, and the skew for the overall device.

| Table 4–97. Output Pin Timing Skew Definitions (Part 1 of 2) |                                                                |  |  |  |  |  |  |

|--------------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|--|--|

| Symbol                                                       | Definition                                                     |  |  |  |  |  |  |

| t <sub>SB_HIO</sub>                                          | Row I/O (HIO) within one I/O bank (1)                          |  |  |  |  |  |  |

| t <sub>SB_VIO</sub>                                          | Column I/O (VIO) within one I/O bank (1)                       |  |  |  |  |  |  |

| t <sub>SS_HIO</sub>                                          | Row I/O (HIO) same side of the device, across two banks (2)    |  |  |  |  |  |  |

| t <sub>SS_VIO</sub>                                          | Column I/O (VIO) same side of the device, across two banks (2) |  |  |  |  |  |  |

| Table 4–105. Stratix I/O Standard Output Delay Adders for Fast Slew Rate on Column Pins (Part 2 of 2) |         |          |                |       |                |       |                |       |      |  |

|-------------------------------------------------------------------------------------------------------|---------|----------|----------------|-------|----------------|-------|----------------|-------|------|--|

|                                                                                                       | -5 Spee | ed Grade | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | Ī    |  |

| Parameter                                                                                             | Min     | Max      | Min            | Max   | Min            | Max   | Min            | Max   | Unit |  |

| CTT                                                                                                   |         | 973      |                | 1,021 |                | 1,021 |                | 1,021 | ps   |  |

| SSTL-3 Class I                                                                                        |         | 719      |                | 755   |                | 755   |                | 755   | ps   |  |

| SSTL-3 Class II                                                                                       |         | 146      |                | 153   |                | 153   |                | 153   | ps   |  |

| SSTL-2 Class I                                                                                        |         | 678      |                | 712   |                | 712   |                | 712   | ps   |  |

| SSTL-2 Class II                                                                                       |         | 223      |                | 234   |                | 234   |                | 234   | ps   |  |

| SSTL-18 Class I                                                                                       |         | 1,032    |                | 1,083 |                | 1,083 |                | 1,083 | ps   |  |

| SSTL-18 Class II                                                                                      |         | 447      |                | 469   |                | 469   |                | 469   | ps   |  |

| 1.5-V HSTL Class I                                                                                    |         | 660      |                | 693   |                | 693   |                | 693   | ps   |  |

| 1.5-V HSTL Class II                                                                                   |         | 537      |                | 564   |                | 564   |                | 564   | ps   |  |

| 1.8-V HSTL Class I                                                                                    |         | 304      |                | 319   |                | 319   |                | 319   | ps   |  |

| 1.8-V HSTL Class II                                                                                   |         | 231      |                | 242   |                | 242   |                | 242   | ps   |  |

| Table 4-106. | Table 4–106. Stratix I/O Standard Output Delay Adders for Fast Slew Rate on Row Pins (Part 1 of 2) |         |                       |     |                          |     |                |     |         |    |  |

|--------------|----------------------------------------------------------------------------------------------------|---------|-----------------------|-----|--------------------------|-----|----------------|-----|---------|----|--|

| Parame       | ator.                                                                                              | -5 Spee | peed Grade   -6 Speed |     | d Grade   -7 Speed Grade |     | -8 Speed Grade |     | Unit    |    |  |

| ratallie     | iler                                                                                               | Min     | Max                   | Min | Max                      | Min | Max            | Min | Min Max |    |  |

| LVCMOS       | 2 mA                                                                                               |         | 1,518                 |     | 1,594                    |     | 1,594          |     | 1,594   | ps |  |

|              | 4 mA                                                                                               |         | 746                   |     | 783                      |     | 783            |     | 783     | ps |  |

|              | 8 mA                                                                                               |         | 96                    |     | 100                      |     | 100            |     | 100     | ps |  |

|              | 12 mA                                                                                              |         | 0                     |     | 0                        |     | 0              |     | 0       | ps |  |

| 3.3-V LVTTL  | 4 mA                                                                                               |         | 1,518                 |     | 1,594                    |     | 1,594          |     | 1,594   | ps |  |

|              | 8 mA                                                                                               |         | 1,038                 |     | 1,090                    |     | 1,090          |     | 1,090   | ps |  |

|              | 12 mA                                                                                              |         | 521                   |     | 547                      |     | 547            |     | 547     | ps |  |

|              | 16 mA                                                                                              |         | 414                   |     | 434                      |     | 434            |     | 434     | ps |  |

|              | 24 mA                                                                                              |         | 0                     |     | 0                        |     | 0              |     | 0       | ps |  |

| 2.5-V LVTTL  | 2 mA                                                                                               |         | 2,032                 |     | 2,133                    |     | 2,133          |     | 2,133   | ps |  |

|              | 8 mA                                                                                               |         | 699                   |     | 734                      |     | 734            |     | 734     | ps |  |

|              | 12 mA                                                                                              |         | 374                   |     | 392                      |     | 392            |     | 392     | ps |  |

|              | 16 mA                                                                                              |         | 165                   |     | 173                      |     | 173            |     | 173     | ps |  |

| 1.8-V LVTTL  | 2 mA                                                                                               |         | 3,714                 |     | 3,899                    |     | 3,899          |     | 3,899   | ps |  |

|              | 8 mA                                                                                               |         | 1,055                 |     | 1,107                    |     | 1,107          |     | 1,107   | ps |  |

|              | 12 mA                                                                                              |         | 830                   |     | 871                      |     | 871            |     | 871     | ps |  |

| 0h a l                                     | 0                            | -6  | Speed ( | Grade | -7 Speed Grade |     |       | -8 Speed Grade |     |       | 1114 |

|--------------------------------------------|------------------------------|-----|---------|-------|----------------|-----|-------|----------------|-----|-------|------|

| Symbol                                     | Conditions                   | Min | Тур     | Max   | Min            | Тур | Max   | Min            | Тур | Max   | Unit |

| f <sub>HSCLK</sub> (Clock                  | W = 4 to 30 (Serdes used)    | 10  |         | 156   | 10             |     | 115.5 | 10             |     | 115.5 | MHz  |

| frequency)                                 | W = 2 (Serdes bypass)        | 50  |         | 231   | 50             |     | 231   | 50             |     | 231   | MHz  |

| (LVDS,LVPECL,<br>HyperTransport            | W = 2 (Serdes used)          | 150 |         | 312   | 150            |     | 231   | 150            |     | 231   | MHz  |

| technology)                                | W = 1 (Serdes bypass)        | 100 |         | 311   | 100            |     | 270   | 100            |     | 270   | MHz  |

| $f_{HSCLK} = f_{HSDR} / W$                 | W = 1 (Serdes used)          | 300 |         | 624   | 300            |     | 462   | 300            |     | 462   | MHz  |

| f <sub>HSDR</sub> Device operation,        | J = 10                       | 300 |         | 624   | 300            |     | 462   | 300            |     | 462   | Mbps |

| (LVDS,LVPECL,<br>HyperTransport            | J = 8                        | 300 |         | 624   | 300            |     | 462   | 300            |     | 462   | Mbps |

| technology)                                | J = 7                        | 300 |         | 624   | 300            |     | 462   | 300            |     | 462   | Mbps |

| <i>G77</i>                                 | J = 4                        | 300 |         | 624   | 300            |     | 462   | 300            |     | 462   | Mbps |

|                                            | J = 2                        | 100 |         | 462   | 100            |     | 462   | 100            |     | 462   | Mbps |

|                                            | J = 1 (LVDS and LVPECL only) | 100 |         | 311   | 100            |     | 270   | 100            |     | 270   | Mbps |

| f <sub>HSCLK</sub> (Clock                  | W = 4 to 30 (Serdes used)    | 10  |         | 77.75 |                |     |       |                |     |       | MHz  |

| frequency)<br>(PCML)                       | W = 2 (Serdes bypass)        | 50  |         | 150   | 50             |     | 77.5  | 50             |     | 77.5  | MHz  |

| f <sub>HSCLK</sub> = f <sub>HSDR</sub> / W | W = 2 (Serdes used)          | 150 |         | 155.5 |                |     |       |                |     |       | MHz  |

| THOSE THOSE                                | W = 1 (Serdes bypass)        | 100 |         | 200   | 100            |     | 155   | 100            |     | 155   | MHz  |

|                                            | W = 1 (Serdes used)          | 300 |         | 311   |                |     |       |                |     |       | MHz  |

| Device operation,                          | J = 10                       | 300 |         | 311   |                |     |       |                |     |       | Mbps |

| f <sub>HSDR</sub>                          | J = 8                        | 300 |         | 311   |                |     |       |                |     |       | Mbps |

| (PCML)                                     | J = 7                        | 300 |         | 311   |                |     |       |                |     |       | Mbps |

|                                            | J = 4                        | 300 |         | 311   |                |     |       |                |     |       | Mbps |

|                                            | J = 2                        | 100 |         | 300   | 100            |     | 155   | 100            |     | 155   | Mbps |

|                                            | J = 1                        | 100 |         | 200   | 100            |     | 155   | 100            |     | 155   | Mbps |

| TCCS                                       | All                          |     |         | 400   |                |     | 400   |                |     | 400   | ps   |

High-Speed I/O Specification

# PLL Specifications

Tables 4–127 through 4–129 describe the Stratix device enhanced PLL specifications.

| Table 4–127. Enhanced PLL Specifications for -5 Speed Grades (Part 1 of 2) |                                                                                                              |               |     |                                                            |              |  |  |  |  |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------|-----|------------------------------------------------------------|--------------|--|--|--|--|

| Symbol                                                                     | Parameter                                                                                                    | Min           | Тур | Max                                                        | Unit         |  |  |  |  |

| f <sub>IN</sub>                                                            | Input clock frequency                                                                                        | 3<br>(1), (2) |     | 684                                                        | MHz          |  |  |  |  |

| f <sub>INPFD</sub>                                                         | Input frequency to PFD                                                                                       | 3             |     | 420                                                        | MHz          |  |  |  |  |

| f <sub>INDUTY</sub>                                                        | Input clock duty cycle                                                                                       | 40            |     | 60                                                         | %            |  |  |  |  |

| f <sub>EINDUTY</sub>                                                       | External feedback clock input duty cycle                                                                     | 40            |     | 60                                                         | %            |  |  |  |  |

| t <sub>INJITTER</sub>                                                      | Input clock period jitter                                                                                    |               |     | ±200 (3)                                                   | ps           |  |  |  |  |

| t <sub>EINJITTER</sub>                                                     | External feedback clock period jitter                                                                        |               |     | ±200 (3)                                                   | ps           |  |  |  |  |

| t <sub>FCOMP</sub>                                                         | External feedback clock compensation time (4)                                                                |               |     | 6                                                          | ns           |  |  |  |  |

| f <sub>OUT</sub>                                                           | Output frequency for internal global or regional clock                                                       | 0.3           |     | 500                                                        | MHz          |  |  |  |  |

| f <sub>OUT_EXT</sub>                                                       | Output frequency for external clock (3)                                                                      | 0.3           |     | 526                                                        | MHz          |  |  |  |  |

| t <sub>OUTDUTY</sub>                                                       | Duty cycle for external clock output (when set to 50%)                                                       | 45            |     | 55                                                         | %            |  |  |  |  |

| t <sub>JITTER</sub>                                                        | Period jitter for external clock output (6)                                                                  |               |     | ±100 ps for >200-MHz outclk<br>±20 mUI for <200-MHz outclk | ps or<br>mUI |  |  |  |  |

| t <sub>CONFIG5,6</sub>                                                     | Time required to reconfigure the scan chains for PLLs 5 and 6                                                |               |     | 289/f <sub>SCANCLK</sub>                                   |              |  |  |  |  |

| t <sub>CONFIG11,12</sub>                                                   | Time required to reconfigure the scan chains for PLLs 11 and 12                                              |               |     | 193/f <sub>SCANCLK</sub>                                   |              |  |  |  |  |

| t <sub>SCANCLK</sub>                                                       | scanclk frequency (5)                                                                                        |               |     | 22                                                         | MHz          |  |  |  |  |

| t <sub>DLOCK</sub>                                                         | Time required to lock dynamically (after switchover or reconfiguring any non-post-scale counters/delays) (7) |               |     | 100                                                        | μs           |  |  |  |  |

| t <sub>LOCK</sub>                                                          | Time required to lock from end of device configuration                                                       | 10            |     | 400                                                        | μs           |  |  |  |  |

| f <sub>VCO</sub>                                                           | PLL internal VCO operating range                                                                             | 300           |     | 800 (8)                                                    | MHz          |  |  |  |  |

| t <sub>LSKEW</sub>                                                         | Clock skew between two external clock outputs driven by the same counter                                     |               | ±50 |                                                            | ps           |  |  |  |  |

Tables 4–131 through 4–133 describe the Stratix device fast PLL specifications.

| Symbol                             | Parameter                                                                             | Min   | Max   | Unit    |

|------------------------------------|---------------------------------------------------------------------------------------|-------|-------|---------|

| f <sub>IN</sub>                    | CLKIN frequency (1), (2), (3)                                                         | 10    | 717   | MHz     |

| f <sub>INPFD</sub>                 | Input frequency to PFD                                                                | 10    | 500   | MHz     |

| f <sub>OUT</sub>                   | Output frequency for internal global or regional clock (3)                            | 9.375 | 420   | MHz     |

| f <sub>OUT_DIFFIO</sub>            | Output frequency for external clock driven out on a differential I/O data channel (2) | (5)   | (5)   |         |

| f <sub>VCO</sub>                   | VCO operating frequency                                                               | 300   | 1,000 | MHz     |

| t <sub>INDUTY</sub>                | CLKIN duty cycle                                                                      | 40    | 60    | %       |

| t <sub>INJITTER</sub>              | Period jitter for CLKIN pin                                                           |       | ±200  | ps      |

| t <sub>DUTY</sub>                  | Duty cycle for DFFIO 1× CLKOUT pin (6)                                                | 45    | 55    | %       |

| t <sub>JITTER</sub>                | Period jitter for DIFFIO clock out (6)                                                |       | (5)   | ps      |

| t <sub>LOCK</sub>                  | Time required for PLL to acquire lock                                                 | 10    | 100   | μs      |

| m                                  | Multiplication factors for <i>m</i> counter (6)                                       | 1     | 32    | Integer |

| <i>l</i> 0, <i>l</i> 1, <i>g</i> 0 | Multiplication factors for I0, I1, and g0 counter (7), (8)                            | 1     | 32    | Integer |

| t <sub>ARESET</sub>                | Minimum pulse width on areset signal                                                  | 10    |       | ns      |

| Table 4–132. Fast PLL Specifications for -7 Speed Grades (Part 1 of 2) |                                                                                   |       |      |      |  |  |  |  |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------|------|------|--|--|--|--|

| Symbol                                                                 | Parameter                                                                         | Min   | Max  | Unit |  |  |  |  |

| f <sub>IN</sub>                                                        | CLKIN frequency (1), (3)                                                          | 10    | 640  | MHz  |  |  |  |  |

| f <sub>INPFD</sub>                                                     | Input frequency to PFD                                                            | 10    | 500  | MHz  |  |  |  |  |

| f <sub>OUT</sub>                                                       | Output frequency for internal global or regional clock (4)                        | 9.375 | 420  | MHz  |  |  |  |  |

| fout_diffio                                                            | Output frequency for external clock driven out on a differential I/O data channel | (5)   | (5)  | MHz  |  |  |  |  |

| f <sub>VCO</sub>                                                       | VCO operating frequency                                                           | 300   | 700  | MHz  |  |  |  |  |

| t <sub>INDUTY</sub>                                                    | CLKIN duty cycle                                                                  | 40    | 60   | %    |  |  |  |  |

| t <sub>INJITTER</sub>                                                  | Period jitter for CLKIN pin                                                       |       | ±200 | ps   |  |  |  |  |

| t <sub>DUTY</sub>                                                      | Duty cycle for DFFIO 1× CLKOUT pin (6)                                            | 45    | 55   | %    |  |  |  |  |