Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 2566                                                    |

| Number of Logic Elements/Cells | 25660                                                   |

| Total RAM Bits                 | 1944576                                                 |

| Number of I/O                  | 597                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                         |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 780-BBGA                                                |

| Supplier Device Package        | 780-FBGA (29x29)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s25f780c5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Copyright © 2006 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published in

formation and before placing orders for products or services.

I.S. EN ISO 9001

ii Altera Corporation

## 2. Stratix Architecture

\$51002-3.2

# Functional Description

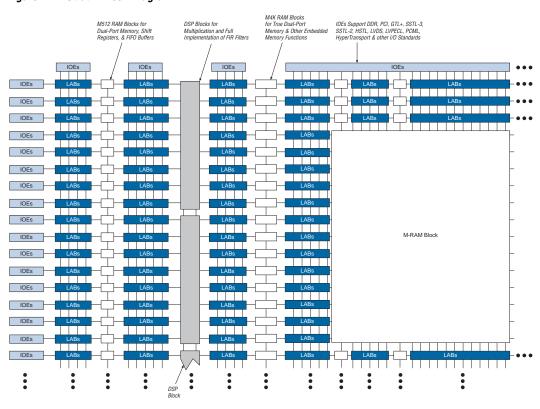

Stratix® devices contain a two-dimensional row- and column-based architecture to implement custom logic. A series of column and row interconnects of varying length and speed provide signal interconnects between logic array blocks (LABs), memory block structures, and DSP blocks.

The logic array consists of LABs, with 10 logic elements (LEs) in each LAB. An LE is a small unit of logic providing efficient implementation of user logic functions. LABs are grouped into rows and columns across the device.

M512 RAM blocks are simple dual-port memory blocks with 512 bits plus parity (576 bits). These blocks provide dedicated simple dual-port or single-port memory up to 18-bits wide at up to 318 MHz. M512 blocks are grouped into columns across the device in between certain LABs.

M4K RAM blocks are true dual-port memory blocks with 4K bits plus parity (4,608 bits). These blocks provide dedicated true dual-port, simple dual-port, or single-port memory up to 36-bits wide at up to 291 MHz. These blocks are grouped into columns across the device in between certain LABs.

M-RAM blocks are true dual-port memory blocks with 512K bits plus parity (589,824 bits). These blocks provide dedicated true dual-port, simple dual-port, or single-port memory up to 144-bits wide at up to 269 MHz. Several M-RAM blocks are located individually or in pairs within the device's logic array.

Digital signal processing (DSP) blocks can implement up to either eight full-precision  $9\times 9$ -bit multipliers, four full-precision  $18\times 18$ -bit multipliers, or one full-precision  $36\times 36$ -bit multiplier with add or subtract features. These blocks also contain 18-bit input shift registers for digital signal processing applications, including FIR and infinite impulse response (IIR) filters. DSP blocks are grouped into two columns in each device.

Each Stratix device I/O pin is fed by an I/O element (IOE) located at the end of LAB rows and columns around the periphery of the device. I/O pins support numerous single-ended and differential I/O standards. Each IOE contains a bidirectional I/O buffer and six registers for registering input, output, and output-enable signals. When used with

dedicated clocks, these registers provide exceptional performance and interface support with external memory devices such as DDR SDRAM, FCRAM, ZBT, and QDR SRAM devices.

High-speed serial interface channels support transfers at up to 840 Mbps using LVDS, LVPECL, 3.3-V PCML, or HyperTransport technology I/O standards.

Figure 2–1 shows an overview of the Stratix device.

Figure 2-1. Stratix Block Diagram

Figure 2-2. Stratix LAB Structure

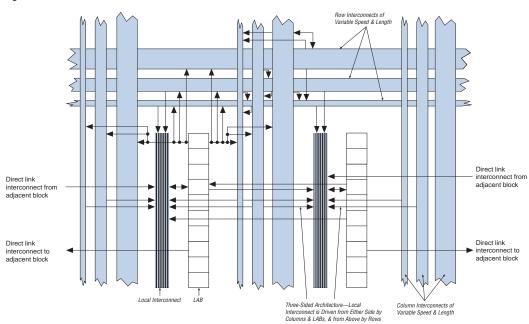

### LAB Interconnects

The LAB local interconnect can drive LEs within the same LAB. The LAB local interconnect is driven by column and row interconnects and LE outputs within the same LAB. Neighboring LABs, M512 RAM blocks, M4K RAM blocks, or DSP blocks from the left and right can also drive an LAB's local interconnect through the direct link connection. The direct link connection feature minimizes the use of row and column interconnects, providing higher performance and flexibility. Each LE can drive 30 other LEs through fast local and direct link interconnects. Figure 2–3 shows the direct link connection.

asynchronous load, and clear signals. An asynchronous clear signal takes precedence if both signals are asserted simultaneously. Each LAB supports up to two clears and one preset signal.

In addition to the clear and preset ports, Stratix devices provide a chip-wide reset pin (DEV\_CLRn) that resets all registers in the device. An option set before compilation in the Quartus II software controls this pin. This chip-wide reset overrides all other control signals.

## MultiTrack Interconnect

In the Stratix architecture, connections between LEs, TriMatrix memory, DSP blocks, and device I/O pins are provided by the MultiTrack interconnect structure with DirectDrive technology. The MultiTrack interconnect consists of continuous, performance-optimized routing lines of different lengths and speeds used for inter- and intra-design block connectivity. The Quartus II Compiler automatically places critical design paths on faster interconnects to improve design performance.

DirectDrive technology is a deterministic routing technology that ensures identical routing resource usage for any function regardless of placement within the device. The MultiTrack interconnect and DirectDrive technology simplify the integration stage of block-based designing by eliminating the re-optimization cycles that typically follow design changes and additions.

The MultiTrack interconnect consists of row and column interconnects that span fixed distances. A routing structure with fixed length resources for all devices allows predictable and repeatable performance when migrating through different device densities. Dedicated row interconnects route signals to and from LABs, DSP blocks, and TriMatrix memory within the same row. These row resources include:

- Direct link interconnects between LABs and adjacent blocks.

- R4 interconnects traversing four blocks to the right or left.

- R8 interconnects traversing eight blocks to the right or left.

- R24 row interconnects for high-speed access across the length of the device.

The direct link interconnect allows an LAB, DSP block, or TriMatrix memory block to drive into the local interconnect of its left and right neighbors and then back into itself. Only one side of a M-RAM block interfaces with direct link and row interconnects. This provides fast communication between adjacent LABs and/or blocks without using row interconnect resources.

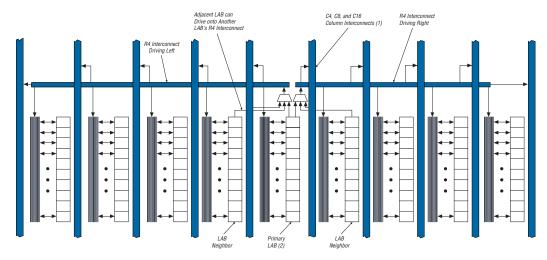

The R4 interconnects span four LABs, three LABs and one M512 RAM block, two LABs and one M4K RAM block, or two LABs and one DSP block to the right or left of a source LAB. These resources are used for fast

row connections in a four-LAB region. Every LAB has its own set of R4 interconnects to drive either left or right. Figure 2–9 shows R4 interconnect connections from an LAB. R4 interconnects can drive and be driven by DSP blocks and RAM blocks and horizontal IOEs. For LAB interfacing, a primary LAB or LAB neighbor can drive a given R4 interconnect. For R4 interconnects that drive to the right, the primary LAB and right neighbor can drive on to the interconnect. For R4 interconnects that drive to the left, the primary LAB and its left neighbor can drive on to the interconnects can drive other R4 interconnects to extend the range of LABs they can drive. R4 interconnects can also drive C4 and C16 interconnects for connections from one row to another. Additionally, R4 interconnects can drive R24 interconnects.

Figure 2-9. R4 Interconnect Connections

#### *Notes to Figure 2–9:*

- (1) C4 interconnects can drive R4 interconnects.

- (2) This pattern is repeated for every LAB in the LAB row.

The R8 interconnects span eight LABs, M512 or M4K RAM blocks, or DSP blocks to the right or left from a source LAB. These resources are used for fast row connections in an eight-LAB region. Every LAB has its own set of R8 interconnects to drive either left or right. R8 interconnect connections between LABs in a row are similar to the R4 connections shown in Figure 2–9, with the exception that they connect to eight LABs to the right or left, not four. Like R4 interconnects, R8 interconnects can drive and be driven by all types of architecture blocks. R8 interconnects

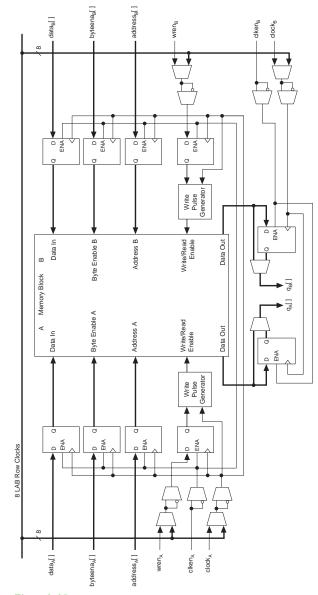

Figure 2–25. Input/Output Clock Mode in True Dual-Port Mode Notes (1), (2)

Notes to Figure 2-25:

- (1) All registers shown have asynchronous clear ports.

- (2) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

## Read/Write Clock Mode

The memory blocks implement read/write clock mode for simple dual-port memory. You can use up to two clocks in this mode. The write clock controls the block's data inputs, wraddress, and wren. The read clock controls the data output, rdaddress, and rden. The memory blocks support independent clock enables for each clock and asynchronous clear signals for the read- and write-side registers. Figure 2–27 shows a memory block in read/write clock mode.

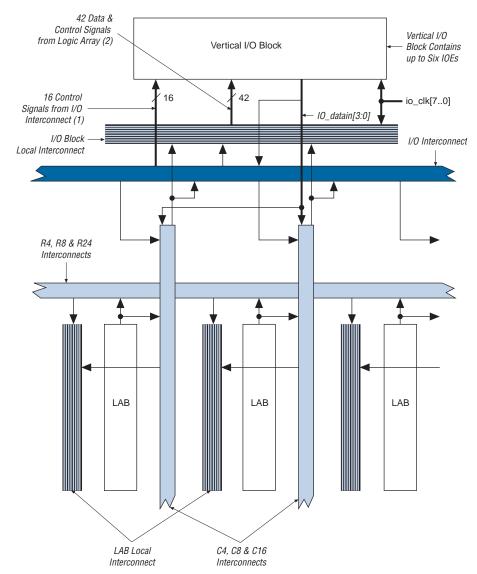

Figure 2-61. Column I/O Block Connection to the Interconnect

#### *Notes to Figure 2–61:*

- (1) The 16 control signals are composed of four output enables io\_boe[3..0], four clock enables io\_boe[3..0], four clocks io\_bclk[3..0], and four clear signals io\_bclr[3..0].

- (2) The 42 data and control signals consist of 12 data out lines; six lines each for DDR applications io\_dataouta[5..0] and io\_dataoutb[5..0], six output enables io\_coe[5..0], six input clock enables io\_cce\_in[5..0], six output clock enables io\_cce\_out[5..0], six clocks io\_cclk[5..0], and six clear signals io cclr[5..0].

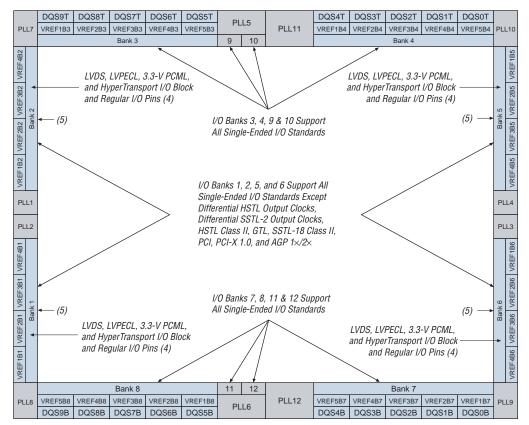

**Figure 2–70. Stratix I/O Banks** Notes (1), (2), (3)

#### *Notes to Figure 2–70:*

- (1) Figure 2–70 is a top view of the silicon die. This will correspond to a top-down view for non-flip-chip packages, but will be a reverse view for flip-chip packages.

- (2) Figure 2–70 is a graphic representation only. See the device pin-outs on the web (www.altera.com) and the Quartus II software for exact locations.

- (3) Banks 9 through 12 are enhanced PLL external clock output banks.

- (4) If the high-speed differential I/O pins are not used for high-speed differential signaling, they can support all of the I/O standards except HSTL Class I and II, GTL, SSTL-18 Class II, PCI, PCI-X 1.0, and AGP 1×/2×.

- (5) For guidelines for placing single-ended I/O pads next to differential I/O pads, see the Selectable I/O Standards in Stratix and Stratix GX Devices chapter in the Stratix Device Handbook, Volume 2.

Table 2–32 shows I/O standard support for each I/O bank.

| I/O Standard                      | Top & Bottom Banks<br>(3, 4, 7 & 8) | Left & Right Banks<br>(1, 2, 5 & 6) | Enhanced PLL External<br>Clock Output Banks<br>(9, 10, 11 & 12) |

|-----------------------------------|-------------------------------------|-------------------------------------|-----------------------------------------------------------------|

| LVTTL                             | <b>✓</b>                            | <b>✓</b>                            | <b>✓</b>                                                        |

| LVCMOS                            | ✓                                   | <b>✓</b>                            | <b>✓</b>                                                        |

| 2.5 V                             | ✓                                   | ✓                                   | ✓                                                               |

| 1.8 V                             | ✓                                   | ✓                                   | ✓                                                               |

| 1.5 V                             | ✓                                   | <b>✓</b>                            | <b>✓</b>                                                        |

| 3.3-V PCI                         | <b>✓</b>                            |                                     | <b>✓</b>                                                        |

| 3.3-V PCI-X 1.0                   | <b>✓</b>                            |                                     | <b>✓</b>                                                        |

| LVPECL                            |                                     | <b>✓</b>                            | <b>✓</b>                                                        |

| 3.3-V PCML                        |                                     | <b>✓</b>                            | <b>✓</b>                                                        |

| LVDS                              |                                     | <b>✓</b>                            | <b>✓</b>                                                        |

| HyperTransport technology         |                                     | <b>✓</b>                            | <b>✓</b>                                                        |

| Differential HSTL (clock inputs)  | <b>✓</b>                            | <b>✓</b>                            |                                                                 |

| Differential HSTL (clock outputs) |                                     |                                     | ✓                                                               |

| Differential SSTL (clock outputs) |                                     |                                     | ✓                                                               |

| 3.3-V GTL                         | ✓                                   |                                     | ✓                                                               |

| 3.3-V GTL+                        | ✓                                   | ✓                                   | <b>✓</b>                                                        |

| 1.5-V HSTL Class I                | ✓                                   | ✓                                   | ✓                                                               |

| 1.5-V HSTL Class II               | ✓                                   |                                     | ✓                                                               |

| 1.8-V HSTL Class I                | ✓                                   | ✓                                   | <b>✓</b>                                                        |

| 1.8-V HSTL Class II               | ✓                                   |                                     | ✓                                                               |

| SSTL-18 Class I                   | ✓                                   | ✓                                   | ✓                                                               |

| SSTL-18 Class II                  | ✓                                   |                                     | ✓                                                               |

| SSTL-2 Class I                    | ✓                                   | <b>✓</b>                            | <b>✓</b>                                                        |

| SSTL-2 Class II                   | ✓                                   | ✓                                   | <b>✓</b>                                                        |

| SSTL-3 Class I                    | <b>✓</b>                            | <b>✓</b>                            | <b>✓</b>                                                        |

The Stratix device instruction register length is 10 bits and the USERCODE register length is 32 bits. Tables 3–2 and 3–3 show the boundary-scan register length and device IDCODE information for Stratix devices.

| Table 3–2. Stratix Boundary-Scan Register Length |       |  |  |  |

|--------------------------------------------------|-------|--|--|--|

| Device Boundary-Scan Register Length             |       |  |  |  |

| EP1S10                                           | 1,317 |  |  |  |

| EP1S20                                           | 1,797 |  |  |  |

| EP1S25                                           | 2,157 |  |  |  |

| EP1S30                                           | 2,253 |  |  |  |

| EP1S40                                           | 2,529 |  |  |  |

| EP1S60                                           | 3,129 |  |  |  |

| EP1S80                                           | 3,777 |  |  |  |

| Table 3–3. 32-Bit Stratix Device IDCODE |                      |                       |                                    |                 |  |

|-----------------------------------------|----------------------|-----------------------|------------------------------------|-----------------|--|

|                                         | IDCODE (32 Bits) (1) |                       |                                    |                 |  |

| Device                                  | Version (4 Bits)     | Part Number (16 Bits) | Manufacturer Identity<br>(11 Bits) | LSB (1 Bit) (2) |  |

| EP1S10                                  | 0000                 | 0010 0000 0000 0001   | 000 0110 1110                      | 1               |  |

| EP1S20                                  | 0000                 | 0010 0000 0000 0010   | 000 0110 1110                      | 1               |  |

| EP1S25                                  | 0000                 | 0010 0000 0000 0011   | 000 0110 1110                      | 1               |  |

| EP1S30                                  | 0000                 | 0010 0000 0000 0100   | 000 0110 1110                      | 1               |  |

| EP1S40                                  | 0000                 | 0010 0000 0000 0101   | 000 0110 1110                      | 1               |  |

| EP1S60                                  | 0000                 | 0010 0000 0000 0110   | 000 0110 1110                      | 1               |  |

| EP1S80                                  | 0000                 | 0010 0000 0000 0111   | 000 0110 1110                      | 1               |  |

Notes to Tables 3-2 and 3-3:

- (1) The most significant bit (MSB) is on the left.

- (2) The IDCODE's least significant bit (LSB) is always 1.

| Symbol            | Parameter                                          | Conditions         | Minimum      | Maximum           | Unit |

|-------------------|----------------------------------------------------|--------------------|--------------|-------------------|------|

| V <sub>CCIO</sub> | Supply voltage for output buffers, 3.3-V operation | (4), (5)           | 3.00 (3.135) | 3.60 (3.465)      | V    |

|                   | Supply voltage for output buffers, 2.5-V operation | (4)                | 2.375        | 2.625             | ٧    |

|                   | Supply voltage for output buffers, 1.8-V operation | (4)                | 1.71         | 1.89              | ٧    |

|                   | Supply voltage for output buffers, 1.5-V operation | (4)                | 1.4          | 1.6               | ٧    |

| VI                | Input voltage                                      | (3), (6)           | -0.5         | 4.0               | V    |

| V <sub>O</sub>    | Output voltage                                     |                    | 0            | V <sub>CCIO</sub> | V    |

| TJ                | Operating junction                                 | For commercial use | 0            | 85                | °C   |

| temp              | temperature                                        | For industrial use | -40          | 100               | °C   |

| Table 4–3        | Table 4–3. Stratix Device DC Operating Conditions Note (7) (Part 1 of 2) |                                                              |         |         |         |      |

|------------------|--------------------------------------------------------------------------|--------------------------------------------------------------|---------|---------|---------|------|

| Symbol           | Parameter                                                                | Conditions                                                   | Minimum | Typical | Maximum | Unit |

| I <sub>I</sub>   | Input pin leakage current                                                | $V_I = V_{CCIOmax}$ to 0 V (8)                               | -10     |         | 10      | μА   |

| I <sub>OZ</sub>  | Tri-stated I/O pin leakage current                                       | V <sub>O</sub> = V <sub>CCIOmax</sub> to 0 V (8)             | -10     |         | 10      | μА   |

| I <sub>CC0</sub> | V <sub>CC</sub> supply current (standby) (All                            | V <sub>I</sub> = ground, no load, no toggling inputs         |         |         |         | mA   |

|                  | memory blocks in power-down mode)                                        | EP1S10. V <sub>I</sub> = ground, no load, no toggling inputs |         | 37      |         | mA   |

|                  |                                                                          | EP1S20. V <sub>I</sub> = ground, no load, no toggling inputs |         | 65      |         | mA   |

|                  |                                                                          | EP1S25. V <sub>I</sub> = ground, no load, no toggling inputs |         | 90      |         | mA   |

|                  |                                                                          | EP1S30. V <sub>I</sub> = ground, no load, no toggling inputs |         | 114     |         | mA   |

|                  |                                                                          | EP1S40. V <sub>I</sub> = ground, no load, no toggling inputs |         | 145     |         | mA   |

|                  |                                                                          | EP1S60. V <sub>I</sub> = ground, no load, no toggling inputs |         | 200     |         | mA   |

|                  |                                                                          | EP1S80. V <sub>I</sub> = ground, no load, no toggling inputs |         | 277     |         | mA   |

device. Decoupling capacitors were not used in this measurement. To factor in the current for decoupling capacitors, sum up the current for each capacitor using the following equation:

$$I = C (dV/dt)$$

If the regulator or power supply minimum output current is more than the Stratix device requires, then the device may consume more current than the maximum current listed in Table 4–34. However, the device does not require any more current to successfully power up than what is listed in Table 4–34.

| Table 4–34. Stratix Power-Up Current (I <sub>CCINT</sub> ) Requirements Note (1) |                |         |       |  |

|----------------------------------------------------------------------------------|----------------|---------|-------|--|

| Device                                                                           | Power-Up Curre | Unit    |       |  |

| Device                                                                           | Typical        | Maximum | Ullit |  |

| EP1S10                                                                           | 250            | 700     | mA    |  |

| EP1S20                                                                           | 400            | 1,200   | mA    |  |

| EP1S25                                                                           | 500            | 1,500   | mA    |  |

| EP1S30                                                                           | 550            | 1,900   | mA    |  |

| EP1S40                                                                           | 650            | 2,300   | mA    |  |

| EP1S60                                                                           | 800            | 2,600   | mA    |  |

| EP1S80                                                                           | 1,000          | 3,000   | mA    |  |

Note to Table 4-34:

The exact amount of current consumed varies according to the process, temperature, and power ramp rate. Stratix devices typically require less current during power up than shown in Table 4–34. The user-mode current during device operation is generally higher than the power-up current.

The duration of the  $I_{CCINT}$  power-up requirement depends on the  $V_{CCINT}$  voltage supply rise time. The power-up current consumption drops when the  $V_{CCINT}$  supply reaches approximately 0.75 V.

<sup>(1)</sup> The maximum test conditions are for  $0^{\circ}$  C and typical test conditions are for  $40^{\circ}$  C

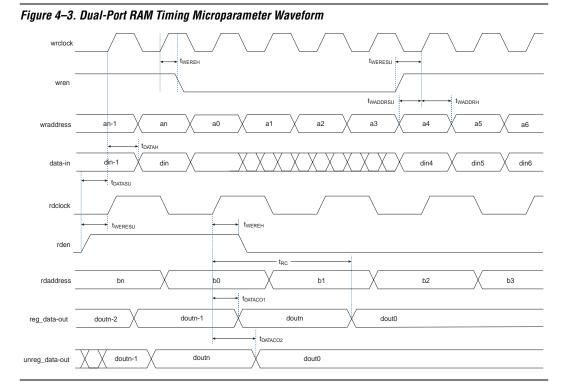

Figure 4–3 shows the TriMatrix memory waveforms for the M512, M4K, and M-RAM timing parameters shown in Tables 4–40 through 4–42.

Internal timing parameters are specified on a speed grade basis independent of device density. Tables 4–44 through 4–50 show the internal timing microparameters for LEs, IOEs, TriMatrix memory structures, DSP blocks, and MultiTrack interconnects.

| Table 4–43. Routing Delay Internal Timing Microparameter Descriptions (Part 1 of 2) |                                                                                    |  |  |  |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|

| Symbol                                                                              | Parameter                                                                          |  |  |  |

| t <sub>R4</sub>                                                                     | Delay for an R4 line with average loading; covers a distance of four LAB columns.  |  |  |  |

| t <sub>R8</sub>                                                                     | Delay for an R8 line with average loading; covers a distance of eight LAB columns. |  |  |  |

| t <sub>R24</sub>                                                                    | Delay for an R24 line with average loading; covers a distance of 24 LAB columns.   |  |  |  |

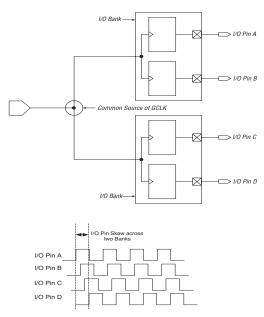

Figure 4–6 shows the case where four IOE registers are located in two different I/O banks.

Figure 4-6. I/O Skew Across Two I/O Banks

Table 4–97 defines the timing parameters used to define the timing for horizontal I/O pins (side banks 1, 2, 5, 6) and vertical I/O pins (top and bottom banks 3, 4, 7, 8). The timing parameters define the skew within an I/O bank, across two neighboring I/O banks on the same side of the device, across all horizontal I/O banks, across all vertical I/O banks, and the skew for the overall device.

| Table 4–97. Output Pin Timing Skew Definitions (Part 1 of 2) |                                                                |  |  |  |

|--------------------------------------------------------------|----------------------------------------------------------------|--|--|--|

| Symbol Definition                                            |                                                                |  |  |  |

| t <sub>SB_HIO</sub>                                          | Row I/O (HIO) within one I/O bank (1)                          |  |  |  |

| t <sub>SB_VIO</sub>                                          | Column I/O (VIO) within one I/O bank (1)                       |  |  |  |

| t <sub>SS_HIO</sub>                                          | Row I/O (HIO) same side of the device, across two banks (2)    |  |  |  |

| t <sub>SS_VIO</sub>                                          | Column I/O (VIO) same side of the device, across two banks (2) |  |  |  |

| Table 4–97. Output Pin Timing Skew Definitions (Part 2 of 2) |                                                                       |  |  |  |

|--------------------------------------------------------------|-----------------------------------------------------------------------|--|--|--|

| Symbol Definition                                            |                                                                       |  |  |  |

| t <sub>LR_HIO</sub>                                          | Across all HIO banks (1, 2, 5, 6); across four similar type I/O banks |  |  |  |

| t <sub>TB_VIO</sub>                                          | Across all VIO banks (3, 4, 7, 8); across four similar type I/O banks |  |  |  |

| t <sub>OVERALL</sub>                                         | Output timing skew for all I/O pins on the device.                    |  |  |  |

#### Notes to Table 4-97:

- (1) See Figure 4–5 on page 4–57.

- (2) See Figure 4–6 on page 4–58.

Table 4–98 shows the I/O skews when using the same global or regional clock to feed IOE registers in I/O banks around each device. These values can be used for calculating the timing budget on the output (write) side of a memory interface. These values already factor in the package skew.

| Table 4–98. Output Skew for Stratix by Device Density |                  |               |                 |  |  |

|-------------------------------------------------------|------------------|---------------|-----------------|--|--|

|                                                       |                  | Skew (ps) (1) |                 |  |  |

| Symbol                                                | EP1S10 to EP1S30 | EP1S40        | EP1S60 & EP1S80 |  |  |

| t <sub>SB_HIO</sub>                                   | 90               | 290           | 500             |  |  |

| t <sub>SB_VIO</sub>                                   | 160              | 290           | 500             |  |  |

| t <sub>SS_HIO</sub>                                   | 90               | 460           | 600             |  |  |

| t <sub>SS_VIO</sub>                                   | 180              | 520           | 630             |  |  |

| t <sub>LR_HIO</sub>                                   | 150              | 490           | 600             |  |  |

| t <sub>TB_VIO</sub>                                   | 190              | 580           | 670             |  |  |

| t <sub>OVERALL</sub>                                  | 430              | 630           | 880             |  |  |

Note to Table 4-98:

(1) The skew numbers in Table 4–98 account for worst case package skews.

Table 4–120. Stratix Maximum Output Clock Rate for PLL[5, 6, 11, 12] Pins in Flip-Chip Packages (Part 2 of 2)

| I/O Standard                        | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------------|-------------------|-------------------|-------------------|-------------------|------|

| SSTL-2 Class II (3)                 | 200               | 200               | 167               | 167               | MHz  |

| SSTL-2 Class II (4)                 | 200               | 200               | 167               | 167               | MHz  |

| SSTL-2 Class II (5)                 | 150               | 134               | 134               | 134               | MHz  |

| SSTL-18 Class I                     | 150               | 133               | 133               | 133               | MHz  |

| SSTL-18 Class II                    | 150               | 133               | 133               | 133               | MHz  |

| 1.5-V HSTL Class I                  | 250               | 225               | 200               | 200               | MHz  |

| 1.5-V HSTL Class II                 | 225               | 200               | 200               | 200               | MHz  |

| 1.8-V HSTL Class I                  | 250               | 225               | 200               | 200               | MHz  |

| 1.8-V HSTL Class II                 | 225               | 200               | 200               | 200               | MHz  |

| 3.3-V PCI                           | 350               | 300               | 250               | 250               | MHz  |

| 3.3-V PCI-X 1.0                     | 350               | 300               | 250               | 250               | MHz  |

| Compact PCI                         | 350               | 300               | 250               | 250               | MHz  |

| AGP 1×                              | 350               | 300               | 250               | 250               | MHz  |

| AGP 2×                              | 350               | 300               | 250               | 250               | MHz  |

| CTT                                 | 200               | 200               | 200               | 200               | MHz  |

| Differential 1.5-V HSTL<br>C1       | 225               | 200               | 200               | 200               | MHz  |

| Differential 1.8-V HSTL<br>Class I  | 250               | 225               | 200               | 200               | MHz  |

| Differential 1.8-V HSTL<br>Class II | 225               | 200               | 200               | 200               | MHz  |

| Differential SSTL-2 (6)             | 200               | 200               | 167               | 167               | MHz  |

| LVPECL (2)                          | 500               | 500               | 500               | 500               | MHz  |

| PCML (2)                            | 350               | 350               | 350               | 350               | MHz  |

| LVDS (2)                            | 500               | 500               | 500               | 500               | MHz  |

| HyperTransport technology (2)       | 350               | 350               | 350               | 350               | MHz  |

# Table 4–123. Stratix Maximum Output Clock Rate (Using I/O Pins) for PLL[1, 2, 3, 4] Pins in Wire-Bond Packages (Part 2 of 2)

| I/O Standard                  | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------|-------------------|-------------------|-------------------|------|

| LVDS (2)                      | 400               | 311               | 311               | MHz  |

| HyperTransport technology (2) | 420               | 400               | 400               | MHz  |

#### Notes to Tables 4-120 through 4-123:

- (1) Differential SSTL-2 outputs are only available on column clock pins.

- (2) These parameters are only available on row I/O pins.

- (3) SSTL-2 in maximum drive strength condition. See Table 4–101 on page 4–62 for more information on exact loading conditions for each I/O standard.

- (4) SSTL-2 in minimum drive strength with  $\leq$ 10pF output load condition.

- (5) SSTL-2 in minimum drive strength with > 10pF output load condition.

- (6) Differential SSTL-2 outputs are only supported on column clock pins.

| Fast Regional Clock External I/O Timing            | I                                                           |

|----------------------------------------------------|-------------------------------------------------------------|

| Parameters 4–49                                    | I/O                                                         |

| Global Clock External I/O Timing                   | Standards                                                   |

| Parameters 4–50 Regional Clock External I/O Timing | 1.5-V 4-14, 4-15                                            |

| Parameters 4–50                                    | I/O Specifications 4–4                                      |

| EP1S60 Devices                                     | 1.8-V                                                       |

| Column Pin                                         | I/O Specifications 4–4                                      |

| Fast Regional Clock External I/O Timing            | 2.5-V                                                       |

| Parameters 4–51                                    | I/O Specifications 4–3                                      |

| Global Clock External I/O Timing                   | 3.3-V 4–13                                                  |

| Parameters 4–52                                    | LVDS I/O Specifications 4–6                                 |

| Regional Clock External I/O Timing                 | PCI Specifications 4–9                                      |

| Parameters 4–51                                    | PCML Specifications 4–8                                     |

| M-RAM                                              | Advanced I/O Standard Support 2–122                         |

| Interface Locations 2–38                           | Column I/O Block Connection to the                          |

| Row Pin                                            | Interconnect 2–107                                          |

| Fast Regional Clock External I/O Timing            | Column Pin                                                  |

| Parameters 4–52                                    | Input Delay Adders 4–66                                     |

| Global Clock External I/O Timing                   | Control Signal Selection per IOE 2–109                      |

| Parameters 4–53                                    | CTT I/O Specifications 4–16                                 |

| Regional Clock External I/O Timing                 | Differential LVDS Input On-Chip                             |

| Parameters 4–53                                    | Termination 2–128                                           |

| EP1S80 Devices                                     | External I/O Delay Parameters 4–66                          |

| Column Pin                                         | GTL+ I/O Specifications 4–10<br>High-Speed Differential I/O |

| Fast Regional Clock External I/O Timing            | Support 2–130                                               |

| Parameters 4–54                                    | HyperTransport Technology                                   |

| Global Clock External I/O Timing                   | Specifications 4–9                                          |

| Parameters 4–55                                    | I/O Banks 2–125                                             |

| Regional Clock External I/O Timing                 | I/O Structure 2–104                                         |

| Parameters 4–54                                    | I/O Support by Bank 2–126                                   |

| Global Clock External I/O Timing                   | IOE Structure 2–105                                         |

| Parameters 4–56                                    | LVCMOS Specifications 4–3                                   |

| Row Pin                                            | LVDS Performance on Fast PLL                                |

| Fast Regional Clock External I/O Timing            | Input 2–103                                                 |

| Parameters 4–55                                    | LVPECL Specifications 4–8                                   |

| Regional Clock External I/O Timing                 | LVTTL Specifications 4–3                                    |

| Parameters 4–56                                    | MultiVolt I/O Interface 2–129                               |

|                                                    | MultiVolt I/O Support 2–130                                 |

| H                                                  | Output Delay Adders for Fast Slew Rate                      |

| HSTL                                               | on Column Pins 4–68                                         |

| Class I Specifications 4–14, 4–15                  | Output Delay Adders for Fast Slew Rate                      |

| Class II Specifications 4–14, 4–15                 | on Row Pins 4–69                                            |

| Ciass II Specifications 4-14, 4-15                 | Output Delay Adders for Slow Slew Rate                      |

|                                                    | on Column Pins 4–70                                         |

|                                                    | Package Options & I/O Pin Counts 1–4                        |

|                                                    | Receiver Input Waveforms for Differential                   |

Index-4 Altera Corporation