Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 2566                                                    |

| Number of Logic Elements/Cells | 25660                                                   |

| Total RAM Bits                 | 1944576                                                 |

| Number of I/O                  | 597                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                         |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 780-BBGA                                                |

| Supplier Device Package        | 780-FBGA (29x29)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s25f780c6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

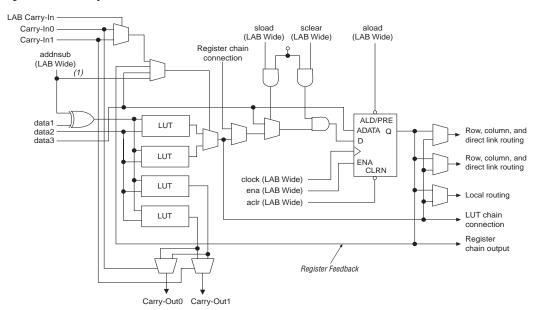

Figure 2-7. LE in Dynamic Arithmetic Mode

*Note to Figure 2–7:*

(1) The addnsub signal is tied to the carry input for the first LE of a carry chain only.

#### Carry-Select Chain

The carry-select chain provides a very fast carry-select function between LEs in arithmetic mode. The carry-select chain uses the redundant carry calculation to increase the speed of carry functions. The LE is configured to calculate outputs for a possible carry-in of 1 and carry-in of 0 in parallel. The carry-in0 and carry-in1 signals from a lower-order bit feed forward into the higher-order bit via the parallel carry chain and feed into both the LUT and the next portion of the carry chain. Carry-select chains can begin in any LE within an LAB.

The speed advantage of the carry-select chain is in the parallel precomputation of carry chains. Since the LAB carry-in selects the precomputed carry chain, not every LE is in the critical path. Only the propagation delay between LAB carry-in generation (LE 5 and LE 10) are now part of the critical path. This feature allows the Stratix architecture to implement high-speed counters, adders, multipliers, parity functions, and comparators of arbitrary width.

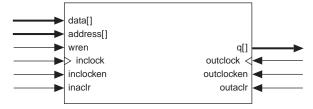

In addition to true dual-port memory, the memory blocks support simple dual-port and single-port RAM. Simple dual-port memory supports a simultaneous read and write and can either read old data before the write occurs or just read the don't care bits. Single-port memory supports non-simultaneous reads and writes, but the q[] port will output the data once it has been written to the memory (if the outputs are not registered) or after the next rising edge of the clock (if the outputs are registered). For more information, see Chapter 2, TriMatrix Embedded Memory Blocks in Stratix & Stratix GX Devices of the *Stratix Device Handbook, Volume 2*. Figure 2–13 shows these different RAM memory port configurations for TriMatrix memory.

Figure 2–13. Simple Dual-Port & Single-Port Memory Configurations

# data[] rdaddress[] wraddress[] rden wren q[] inclock outclock inclocken outclocken inaclr outaclr

#### Single-Port Memory (1)

Simple Dual-Port Memory

Note to Figure 2-13:

Two single-port memory blocks can be implemented in a single M4K block as long as each of the two independent block sizes is equal to or less than half of the M4K block size.

The memory blocks also enable mixed-width data ports for reading and writing to the RAM ports in dual-port RAM configuration. For example, the memory block can be written in  $\times 1$  mode at port A and read out in  $\times 16$  mode from port B.

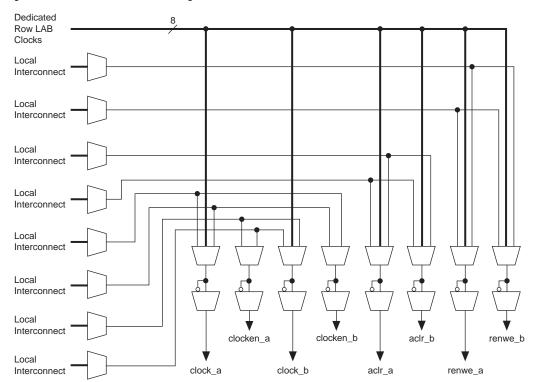

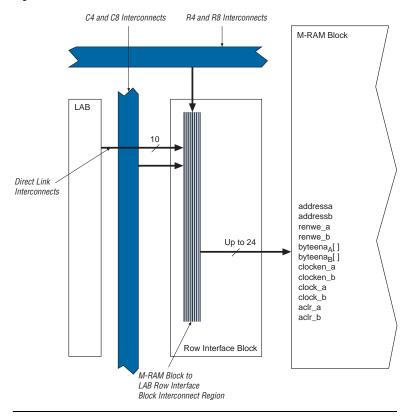

Figure 2-19. M-RAM Block Control Signals

One of the M-RAM block's horizontal sides drive the address and control signal (clock, renwe, byteena, etc.) inputs. Typically, the horizontal side closest to the device perimeter contains the interfaces. The one exception is when two M-RAM blocks are paired next to each other. In this case, the side of the M-RAM block opposite the common side of the two blocks contains the input interface. The top and bottom sides of any M-RAM block contain data input and output interfaces to the logic array. The top side has 72 data inputs and 72 data outputs for port B, and the bottom side has another 72 data inputs and 72 data outputs for port A. Figure 2–20 shows an example floorplan for the EP1S60 device and the location of the M-RAM interfaces.

Figure 2–22. M-RAM Row Unit Interface to Interconnect

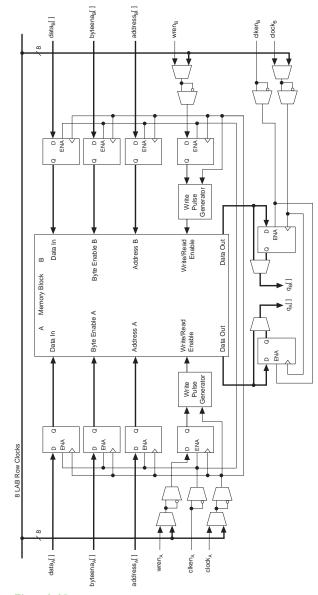

Figure 2–25. Input/Output Clock Mode in True Dual-Port Mode Notes (1), (2)

Notes to Figure 2-25:

- (1) All registers shown have asynchronous clear ports.

- (2) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

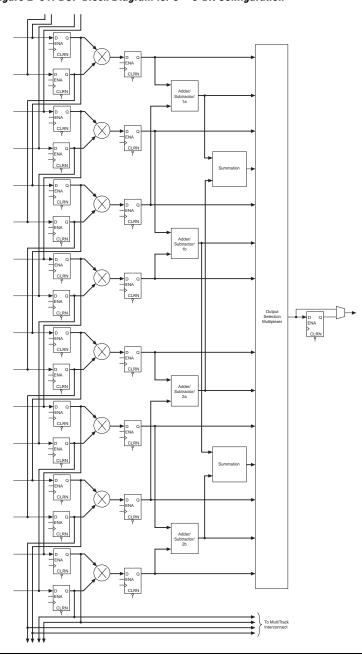

Figure 2–31. DSP Block Diagram for  $9 \times 9$ -Bit Configuration

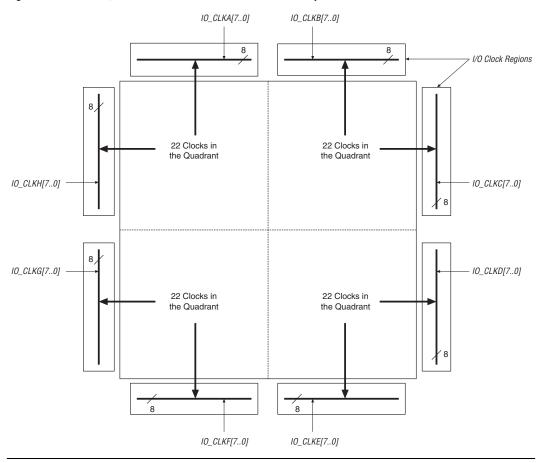

Figure 2-47. EP1S10, EP1S20 & EP1S25 Device I/O Clock Groups

VCO period from up to eight taps for individual fine step selection. Also, each clock output counter can use a unique initial count setting to achieve individual coarse shift selection in steps of one VCO period. The combination of coarse and fine shifts allows phase shifting for the entire input clock period.

The equation to determine the precision of the phase shifting in degrees is:  $45^{\circ}$  ÷ post-scale counter value. Therefore, the maximum step size is  $45^{\circ}$ , and smaller steps are possible depending on the multiplication and division ratio necessary on the output counter port.

This type of phase shift provides the highest precision since it is the least sensitive to process, supply, and temperature variation.

#### **Clock Delay**

In addition to the phase shift feature, the ability to fine tune the  $\Delta t$  clock delay provides advanced time delay shift control on each of the four PLL outputs. There are time delays for each post-scale counter (e, g, or l) from the PLL, the n counter, and m counter. Each of these can shift in 250-ps increments for a range of 3.0 ns. The m delay shifts all outputs earlier in time, while n delay shifts all outputs later in time. Individual delays on post-scale counters (e, g, and l) provide positive delay for each output. Table 2–21 shows the combined delay for each output for normal or zero delay buffer mode where  $\Delta t_e$ ,  $\Delta t_o$ , or  $\Delta t_l$  is unique for each PLL output.

The  $t_{OUTPUT}$  for a single output can range from -3 ns to +6 ns. The total delay shift difference between any two PLL outputs, however, must be less than  $\pm 3$  ns. For example, shifts on two outputs of -1 and +2 ns is allowed, but not -1 and +2.5 ns because these shifts would result in a difference of 3.5 ns. If the design uses external feedback, the  $\Delta t_e$  delay will remove delay from outputs, represented by a negative sign (see Table 2–21). This effect occurs because the  $\Delta t_e$  delay is then part of the feedback loop.

| Table 2–21. Output Clock Delay for Enhanced PLLs                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Normal or Zero Delay Buffer Mode External Feedback Mode                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| $\begin{split} \Delta t_{e \text{OUTPUT}} &= \Delta t_n - \!\!\! \Delta t_m + \Delta t_e \\ \Delta t_{g \text{OUTPUT}} &= \Delta t_n - \!\!\! \Delta t_m + \Delta t_g \\ \Delta t_{l \text{OUTPUT}} &= \Delta t_n - \!\!\! \Delta t_m + \Delta t_l \end{split}$ | $\begin{split} \Delta \mathbf{t}_{\text{OUTPUT}} &= \Delta \mathbf{t}_{n} - \Delta \mathbf{t}_{m} - \Delta \mathbf{t}_{e} \ (1) \\ \Delta \mathbf{t}_{\text{gOUTPUT}} &= \Delta \mathbf{t}_{n} - \Delta \mathbf{t}_{m} + \Delta \mathbf{t}_{g} \\ \Delta \mathbf{t}_{\text{DUTPUT}} &= \Delta \mathbf{t}_{n} - \Delta \mathbf{t}_{m} + \Delta \mathbf{t}_{l} \end{split}$ |  |  |  |  |  |  |

Note to Table 2-21:

(1)  $\Delta t_e$  removes delay from outputs in external feedback mode.

The pllenable pin is a dedicated pin that enables/disables PLLs. When the pllenable pin is low, the clock output ports are driven by GND and all the PLLs go out of lock. When the pllenable pin goes high again, the PLLs relock and resynchronize to the input clocks. You can choose which PLLs are controlled by the pllenable signal by connecting the pllenable input port of the altpll megafunction to the common pllenable input pin.

The areset signals are reset/resynchronization inputs for each PLL. The areset signal should be asserted every time the PLL loses lock to guarantee correct phase relationship between the PLL output clocks. Users should include the areset signal in designs if any of the following conditions are true:

- PLL Reconfiguration or Clock switchover enables in the design.

- Phase relationships between output clocks need to be maintained after a loss of lock condition

The device input pins or logic elements (LEs) can drive these input signals. When driven high, the PLL counters will reset, clearing the PLL output and placing the PLL out of lock. The VCO will set back to its nominal setting (~700 MHz). When driven low again, the PLL will resynchronize to its input as it relocks. If the target VCO frequency is below this nominal frequency, then the output frequency will start at a higher value than desired as the PLL locks. If the system cannot tolerate this, the clkena signal can disable the output clocks until the PLL locks.

The pfdena signals control the phase frequency detector (PFD) output with a programmable gate. If you disable the PFD, the VCO operates at its last set value of control voltage and frequency with some long-term drift to a lower frequency. The system continues running when the PLL goes out of lock or the input clock is disabled. By maintaining the last locked frequency, the system has time to store its current settings before shutting down. You can either use your own control signal or a clkloss status signal to trigger pfdena.

The clkena signals control the enhanced PLL regional and global outputs. Each regional and global output port has its own clkena signal. The clkena signals synchronously disable or enable the clock at the PLL output port by gating the outputs of the g and l counters. The clkena signals are registered on the falling edge of the counter output clock to enable or disable the clock without glitches. Figure 2–57 shows the waveform example for a PLL clock port enable. The PLL can remain locked independent of the clkena signals since the loop-related counters are not affected. This feature is useful for applications that require a low power or sleep mode. Upon re-enabling, the PLL does not need a

shift by the same degree amount. For example, all 10 DQS pins on the top of the device can be shifted by 90° and all 10 DQS pins on the bottom of the device can be shifted by 72°. The reference circuits require a maximum of 256 system reference clock cycles to set the correct phase on the DQS delay elements. Figure 2–69 illustrates the phase-shift reference circuit control of each DQS delay shift on the top of the device. This same circuit is duplicated on the bottom of the device.

Input

Reference

Clock

Phase

Comparator

Up/Down

Counter

Delay Chains

Control Signals to DQS Pins

Figure 2-69. Simplified Diagram of the DQS Phase-Shift Circuitry

See the *External Memory Interfaces* chapter in the *Stratix Device Handbook, Volume 2* for more information on external memory interfaces.

# **Programmable Drive Strength**

The output buffer for each Stratix device I/O pin has a programmable drive strength control for certain I/O standards. The LVTTL and LVCMOS standard has several levels of drive strength that the user can control. SSTL-3 Class I and II, SSTL-2 Class I and II, HSTL Class I and II, and 3.3-V GTL+ support a minimum setting, the lowest drive strength that guarantees the  $I_{OH}/I_{OL}$  of the standard. Using minimum settings provides signal slew rate control to reduce system noise and signal overshoot.

Table 2–28 shows the possible settings for the I/O standards with drive strength control.

| Table 2–28. Programmable Drive Strength                                                                                         |                                                                 |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|--|--|--|--|

| I/O Standard                                                                                                                    | I <sub>OH</sub> / I <sub>OL</sub> Current Strength Setting (mA) |  |  |  |  |  |  |

| 3.3-V LVTTL                                                                                                                     | 24 (1), 16, 12, 8, 4                                            |  |  |  |  |  |  |

| 3.3-V LVCMOS                                                                                                                    | 24 (2), 12 (1), 8, 4, 2                                         |  |  |  |  |  |  |

| 2.5-V LVTTL/LVCMOS                                                                                                              | 16 (1), 12, 8, 2                                                |  |  |  |  |  |  |

| 1.8-V LVTTL/LVCMOS                                                                                                              | 12 (1), 8, 2                                                    |  |  |  |  |  |  |

| 1.5-V LVCMOS                                                                                                                    | 8 (1), 4, 2                                                     |  |  |  |  |  |  |

| GTL/GTL+ 1.5-V HSTL Class I and II 1.8-V HSTL Class I and II SSTL-3 Class I and II SSTL-2 Class I and II SSTL-18 Class I and II | Support max and min strength                                    |  |  |  |  |  |  |

Notes to Table 2-28:

- (1) This is the Quartus II software default current setting.

- (2) I/O banks 1, 2, 5, and 6 do not support this setting.

Quartus II software version 4.2 and later will report current strength as "PCI Compliant" for 3.3-V PCI, 3.3-V PCI-X 1.0, and Compact PCI I/O standards.

Stratix devices support series on-chip termination (OCT) using programmable drive strength. For more information, contact your Altera Support Representative.

# Open-Drain Output

Stratix devices provide an optional open-drain (equivalent to an open-collector) output for each I/O pin. This open-drain output enables the device to provide system-level control signals (e.g., interrupt and write-enable signals) that can be asserted by any of several devices.

#### Slew-Rate Control

The output buffer for each Stratix device I/O pin has a programmable output slew-rate control that can be configured for low-noise or high-speed performance. A faster slew rate provides high-speed transitions for high-performance systems. However, these fast transitions may introduce noise transients into the system. A slow slew rate reduces system noise, but adds a nominal delay to rising and falling edges. Each

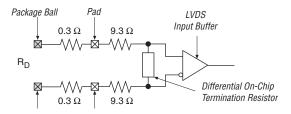

However, there is additional resistance present between the device ball and the input of the receiver buffer, as shown in Figure 2–72. This resistance is because of package trace resistance (which can be calculated as the resistance from the package ball to the pad) and the parasitic layout metal routing resistance (which is shown between the pad and the intersection of the on-chip termination and input buffer).

Figure 2-72. Differential Resistance of LVDS Differential Pin Pair (Rp)

Table 2–35 defines the specification for internal termination resistance for commercial devices.

| Table 2-3          | Table 2–35. Differential On-Chip Termination |                     |     |         |     |       |  |  |  |  |  |  |

|--------------------|----------------------------------------------|---------------------|-----|---------|-----|-------|--|--|--|--|--|--|

| Cumbal             | Description                                  | Conditions          | R   | esistan | ce  | Unit  |  |  |  |  |  |  |

| Symbol             | Description                                  | Collations          | Min | Тур     | Max | UIIIL |  |  |  |  |  |  |

| R <sub>D</sub> (2) | Internal differential termination for LVDS   | Commercial (1), (3) | 110 | 135     | 165 | W     |  |  |  |  |  |  |

|                    |                                              | Industrial (2), (3) | 100 | 135     | 170 | W     |  |  |  |  |  |  |

Notes to Table 2-35:

- (1) Data measured over minimum conditions ( $T_j = 0 \text{ C}$ ,  $V_{\text{CCIO}} + 5\%$ ) and maximum conditions ( $T_j = 85 \text{ C}$ ,  $V_{\text{CCIO}} = -5\%$ ).

- (2) Data measured over minimum conditions ( $T_j = -40$  C,  $V_{CCIO} + 5\%$ ) and maximum conditions ( $T_j = 100$  C,  $V_{CCIO} = -5\%$ ).

- (3) LVDS data rate is supported for 840 Mbps using internal differential termination.

#### MultiVolt I/O Interface

The Stratix architecture supports the MultiVolt I/O interface feature, which allows Stratix devices in all packages to interface with systems of different supply voltages.

The Stratix VCCINT pins must always be connected to a 1.5-V power supply. With a 1.5-V  $V_{CCINT}$  level, input pins are 1.5-V, 1.8-V, 2.5-V, and 3.3-V tolerant. The VCCIO pins can be connected to either a 1.5-V, 1.8-V, 2.5-V, or 3.3-V power supply, depending on the output requirements.

The only way you can use the rx\_data\_align is if one of the following is true:

- The receiver PLL is only clocking receive channels (no resources for the transmitter)

- If all channels can fit in one I/O bank

| Table 2-38            | Table 2–38. EP1S30 Differential Channels Note (1) |             |                 |           |           |           |           |                           |      |      |        |  |  |

|-----------------------|---------------------------------------------------|-------------|-----------------|-----------|-----------|-----------|-----------|---------------------------|------|------|--------|--|--|

|                       | Transmitter                                       | Total       | Maximum         | C         | enter F   | ast PLI   | _S        | Corner Fast PLLs (2), (3) |      |      |        |  |  |

| Package               | /Receiver                                         | Channels    | Speed<br>(Mbps) | PLL1      | PLL2      | PLL3      | PLL4      | PLL7                      | PLL8 | PLL9 | PLL10  |  |  |

| 780-pin               | Transmitter                                       | 70          | 840             | 18        | 17        | 17        | 18        | (6)                       | (6)  | (6)  | (6)    |  |  |

| FineLine<br>BGA       | (4)                                               |             | 840 (5)         | 35        | 35        | 35        | 35        | (6)                       | (6)  | (6)  | (6)    |  |  |

|                       | Receiver                                          | 66          | 840             | 17        | 16        | 16        | 17        | (6)                       | (6)  | (6)  | (6)    |  |  |

|                       |                                                   |             | 840 (5)         | 33        | 33        | 33        | 33        | (6)                       | (6)  | (6)  | (6)    |  |  |

| 956-pin               | Transmitter                                       | 80          | 840             | 19        | 20        | 20        | 19        | 20                        | 20   | 20   | 20     |  |  |

| BGA                   | (4)                                               |             | 840 (5)         | 39        | 39        | 39        | 39        | 20                        | 20   | 20   | 20     |  |  |

|                       | Receiver                                          | Receiver 80 | 840             | 20        | 20        | 20        | 20        | 19                        | 20   | 20   | 19     |  |  |

|                       |                                                   |             | 840 (5)         | 40        | 40        | 40        | 40        | 19                        | 20   | 20   | 19     |  |  |

| 1,020-pin<br>FineLine | Transmitter (4)                                   |             | 840             | 19<br>(1) | 20        | 20        | 19<br>(1) | 20                        | 20   | 20   | 20     |  |  |

| BGA                   | [                                                 | 840 (5),(8) | 39<br>(1)       | 39<br>(1) | 39<br>(1) | 39<br>(1) | 20        | 20                        | 20   | 20   |        |  |  |

|                       | Receiver                                          | 80 (2) (7)  | 840             | 20        | 20        | 20        | 20        | 19 (1)                    | 20   | 20   | 19 (1) |  |  |

|                       |                                                   |             | 840 (5),(8)     | 40        | 40        | 40        | 40        | 19 (1)                    | 20   | 20   | 19 (1) |  |  |

| Table 2-39      | Table 2–39. EP1S40 Differential Channels (Part 1 of 2) Note (1) |           |               |      |         |         |      |                           |      |      |       |  |  |

|-----------------|-----------------------------------------------------------------|-----------|---------------|------|---------|---------|------|---------------------------|------|------|-------|--|--|

|                 | Transmitter/                                                    | Total     | Total Maximum |      | enter F | ast PLI | -S   | Corner Fast PLLs (2), (3) |      |      |       |  |  |

| Package         | 1                                                               | Channels  | Sneed         | PLL1 | PLL2    | PLL3    | PLL4 | PLL7                      | PLL8 | PLL9 | PLL10 |  |  |

| 780-pin         | Transmitter 68                                                  | 68        | 840           | 18   | 16      | 16      | 18   | (6)                       | (6)  | (6)  | (6)   |  |  |

| FineLine<br>BGA | (4)                                                             |           | 840 (5)       | 34   | 34      | 34      | 34   | (6)                       | (6)  | (6)  | (6)   |  |  |

|                 | Receiver                                                        | ceiver 66 | 840           | 17   | 16      | 16      | 17   | (6)                       | (6)  | (6)  | (6)   |  |  |

|                 |                                                                 |           | 840 (5)       | 33   | 33      | 33      | 33   | (6)                       | (6)  | (6)  | (6)   |  |  |

### **Configuring Stratix FPGAs with JRunner**

JRunner is a software driver that configures Altera FPGAs, including Stratix FPGAs, through the ByteBlaster II or ByteBlasterMV cables in JTAG mode. The programming input file supported is in Raw Binary File (.rbf) format. JRunner also requires a Chain Description File (.cdf) generated by the Quartus II software. JRunner is targeted for embedded JTAG configuration. The source code is developed for the Windows NT operating system (OS), but can be customized to run on other platforms. For more information on the JRunner software driver, see the JRunner Software Driver: An Embedded Solution to the JTAG Configuration White Paper and the source files on the Altera web site (www.altera.com).

## **Configuration Schemes**

You can load the configuration data for a Stratix device with one of five configuration schemes (see Table 3–5), chosen on the basis of the target application. You can use a configuration device, intelligent controller, or the JTAG port to configure a Stratix device. A configuration device can automatically configure a Stratix device at system power-up.

Multiple Stratix devices can be configured in any of five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.

| Table 3–5. Data Sources for Configuration |                                                                                                                     |  |  |  |  |  |  |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Configuration Scheme Data Source          |                                                                                                                     |  |  |  |  |  |  |

| Configuration device                      | Enhanced or EPC2 configuration device                                                                               |  |  |  |  |  |  |

| Passive serial (PS)                       | MasterBlaster, ByteBlasterMV, or ByteBlaster II download cable or serial data source                                |  |  |  |  |  |  |

| Passive parallel asynchronous (PPA)       | Parallel data source                                                                                                |  |  |  |  |  |  |

| Fast passive parallel                     | Parallel data source                                                                                                |  |  |  |  |  |  |

| JTAG                                      | MasterBlaster, ByteBlasterMV, or ByteBlaster II download cable, a microprocessor with a Jam or JBC file, or JRunner |  |  |  |  |  |  |

# **Partial Reconfiguration**

The enhanced PLLs within the Stratix device family support partial reconfiguration of their multiply, divide, and time delay settings without reconfiguring the entire device. You can use either serial data from the logic array or regular I/O pins to program the PLL's counter settings in a serial chain. This option provides considerable flexibility for frequency

| Table 4–13                         | Table 4–13. HyperTransport Technology Specifications |                        |         |         |         |      |  |  |  |

|------------------------------------|------------------------------------------------------|------------------------|---------|---------|---------|------|--|--|--|

| Symbol                             | Parameter                                            | Conditions             | Minimum | Typical | Maximum | Unit |  |  |  |

| V <sub>CCIO</sub>                  | I/O supply voltage                                   |                        | 2.375   | 2.5     | 2.625   | ٧    |  |  |  |

| V <sub>ID</sub> (peak-<br>to-peak) | Input differential voltage swing (single-ended)      |                        | 300     |         | 900     | mV   |  |  |  |

| V <sub>ICM</sub>                   | Input common mode voltage                            |                        | 300     |         | 900     | mV   |  |  |  |

| V <sub>OD</sub>                    | Output differential voltage (single-ended)           | $R_L = 100 \Omega$     | 380     | 485     | 820     | mV   |  |  |  |

| $\Delta$ V <sub>OD</sub>           | Change in V <sub>OD</sub> between high and low       | $R_L = 100 \Omega$     |         |         | 50      | mV   |  |  |  |

| V <sub>OCM</sub>                   | Output common mode voltage                           | R <sub>L</sub> = 100 Ω | 440     | 650     | 780     | mV   |  |  |  |

| Δ V <sub>OCM</sub>                 | Change in V <sub>OCM</sub> between high and low      | $R_L = 100 \Omega$     |         |         | 50      | mV   |  |  |  |

| R <sub>L</sub>                     | Receiver differential input resistor                 |                        | 90      | 100     | 110     | Ω    |  |  |  |

| Table 4–14        | . 3.3-V PCI Specifications |                             |                            |         |                            |      |

|-------------------|----------------------------|-----------------------------|----------------------------|---------|----------------------------|------|

| Symbol            | Parameter                  | Conditions                  | Minimum                    | Typical | Maximum                    | Unit |

| V <sub>CCIO</sub> | Output supply voltage      |                             | 3.0                        | 3.3     | 3.6                        | V    |

| V <sub>IH</sub>   | High-level input voltage   |                             | 0.5 ×<br>V <sub>CCIO</sub> |         | V <sub>CCIO</sub> + 0.5    | V    |

| V <sub>IL</sub>   | Low-level input voltage    |                             | -0.5                       |         | 0.3 ×<br>V <sub>CCIO</sub> | V    |

| V <sub>OH</sub>   | High-level output voltage  | I <sub>OUT</sub> = -500 μA  | 0.9 ×<br>V <sub>CCIO</sub> |         |                            | V    |

| V <sub>OL</sub>   | Low-level output voltage   | I <sub>OUT</sub> = 1,500 μA |                            |         | 0.1 ×<br>V <sub>CCIO</sub> | V    |

| Table 4-25.     | Table 4–25. 3.3-V AGP 1× Specifications (Part 2 of 2) |                             |                       |         |                         |      |  |  |  |

|-----------------|-------------------------------------------------------|-----------------------------|-----------------------|---------|-------------------------|------|--|--|--|

| Symbol          | Parameter                                             | Conditions                  | Minimum               | Typical | Maximum                 | Unit |  |  |  |

| $V_{OH}$        | High-level output voltage                             | $I_{OUT} = -0.5 \text{ mA}$ | $0.9 \times V_{CCIO}$ |         | 3.6                     | V    |  |  |  |

| V <sub>OL</sub> | Low-level output voltage                              | I <sub>OUT</sub> = 1.5 mA   |                       |         | 0.1 × V <sub>CCIO</sub> | V    |  |  |  |

| Table 4-26           | . 1.5-V HSTL Class I Specific | cations                       |                         |         |                        |      |

|----------------------|-------------------------------|-------------------------------|-------------------------|---------|------------------------|------|

| Symbol               | Parameter                     | Conditions                    | Minimum                 | Typical | Maximum                | Unit |

| V <sub>CCIO</sub>    | Output supply voltage         |                               | 1.4                     | 1.5     | 1.6                    | V    |

| V <sub>REF</sub>     | Input reference voltage       |                               | 0.68                    | 0.75    | 0.9                    | V    |

| V <sub>TT</sub>      | Termination voltage           |                               | 0.7                     | 0.75    | 0.8                    | V    |

| V <sub>IH</sub> (DC) | DC high-level input voltage   |                               | V <sub>REF</sub> + 0.1  |         |                        | V    |

| V <sub>IL</sub> (DC) | DC low-level input voltage    |                               | -0.3                    |         | V <sub>REF</sub> – 0.1 | V    |

| V <sub>IH</sub> (AC) | AC high-level input voltage   |                               | V <sub>REF</sub> + 0.2  |         |                        | V    |

| V <sub>IL</sub> (AC) | AC low-level input voltage    |                               |                         |         | V <sub>REF</sub> - 0.2 | V    |

| V <sub>OH</sub>      | High-level output voltage     | $I_{OH} = -8 \text{ mA } (3)$ | V <sub>CCIO</sub> - 0.4 |         |                        | V    |

| V <sub>OL</sub>      | Low-level output voltage      | I <sub>OL</sub> = 8 mA (3)    |                         |         | 0.4                    | V    |

| Symbol               | Parameter                   | Conditions                     | Minimum                 | Typical | Maximum                | Unit |

|----------------------|-----------------------------|--------------------------------|-------------------------|---------|------------------------|------|

| V <sub>CCIO</sub>    | Output supply voltage       |                                | 1.4                     | 1.5     | 1.6                    | V    |

| V <sub>REF</sub>     | Input reference voltage     |                                | 0.68                    | 0.75    | 0.9                    | V    |

| V <sub>TT</sub>      | Termination voltage         |                                | 0.7                     | 0.75    | 0.8                    | V    |

| V <sub>IH</sub> (DC) | DC high-level input voltage |                                | V <sub>REF</sub> + 0.1  |         |                        | V    |

| V <sub>IL</sub> (DC) | DC low-level input voltage  |                                | -0.3                    |         | V <sub>REF</sub> – 0.1 | V    |

| V <sub>IH</sub> (AC) | AC high-level input voltage |                                | V <sub>REF</sub> + 0.2  |         |                        | V    |

| V <sub>IL</sub> (AC) | AC low-level input voltage  |                                |                         |         | V <sub>REF</sub> - 0.2 | V    |

| V <sub>OH</sub>      | High-level output voltage   | $I_{OH} = -16 \text{ mA } (3)$ | V <sub>CCIO</sub> - 0.4 |         |                        | V    |

| V <sub>OL</sub>      | Low-level output voltage    | $I_{OL} = 16 \text{ mA } (3)$  |                         |         | 0.4                    | V    |

| Parameter             | -5 Speed Grade |       | -6 Spee | -6 Speed Grade |       | d Grade | -8 Speed Grade |     |      |

|-----------------------|----------------|-------|---------|----------------|-------|---------|----------------|-----|------|

|                       | Min            | Max   | Min     | Max            | Min   | Max     | Min            | Max | Unit |

| t <sub>INSU</sub>     | 0.884          |       | 0.976   |                | 1.118 |         | NA             |     | ns   |

| t <sub>INH</sub>      | 0.000          |       | 0.000   |                | 0.000 |         | NA             |     | ns   |

| t <sub>outco</sub>    | 3.267          | 6.274 | 3.267   | 6.721          | 3.267 | 7.415   | NA             | NA  | ns   |

| t <sub>XZ</sub>       | 3.207          | 6.148 | 3.207   | 6.589          | 3.207 | 7.291   | NA             | NA  | ns   |

| t <sub>ZX</sub>       | 3.207          | 6.148 | 3.207   | 6.589          | 3.207 | 7.291   | NA             | NA  | ns   |

| t <sub>INSUPLL</sub>  | 0.506          |       | 0.656   |                | 0.838 |         | NA             |     | ns   |

| t <sub>INHPLL</sub>   | 0.000          |       | 0.000   |                | 0.000 |         | NA             |     | ns   |

| t <sub>OUTCOPLL</sub> | 1.635          | 2.805 | 1.635   | 2.809          | 1.635 | 2.828   | NA             | NA  | ns   |

| t <sub>XZPLL</sub>    | 1.575          | 2.679 | 1.575   | 2.677          | 1.575 | 2.704   | NA             | NA  | ns   |

| t <sub>ZXPLL</sub>    | 1.575          | 2.679 | 1.575   | 2.677          | 1.575 | 2.704   | NA             | NA  | ns   |

| Table 4–94. EP1S80 External I/O Timing on Row Pins Using Fast Regional Clock Networks Note (1) |         |         |         |         |         |         |                |     |      |  |

|------------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|----------------|-----|------|--|

| Parameter                                                                                      | -5 Spee | d Grade | -6 Spee | d Grade | -7 Spee | d Grade | -8 Speed Grade |     | Unit |  |

|                                                                                                | Min     | Max     | Min     | Max     | Min     | Max     | Min            | Max |      |  |

| t <sub>INSU</sub>                                                                              | 2.792   |         | 2.993   |         | 3.386   |         | NA             |     | ns   |  |

| t <sub>INH</sub>                                                                               | 0.000   |         | 0.000   |         | 0.000   |         | NA             |     | ns   |  |

| t <sub>outco</sub>                                                                             | 2.619   | 5.235   | 2.619   | 5.609   | 2.619   | 6.086   | NA             | NA  | ns   |  |

| t <sub>XZ</sub>                                                                                | 2.646   | 5.289   | 2.646   | 5.665   | 2.646   | 6.154   | NA             | NA  | ns   |  |

| t <sub>ZX</sub>                                                                                | 2.646   | 5.289   | 2.646   | 5.665   | 2.646   | 6.154   | NA             | NA  | ns   |  |

| Table 4–102. Reporting Methodology For Minimum Timi | ng For Single-Ended Output Pins (Part 2 of 2) |

|-----------------------------------------------------|-----------------------------------------------|

| Notes (1), (2), (3)                                 |                                               |

| I/O Standard |                   | Measurement<br>Point |                |                  |                          |            |                        |                   |

|--------------|-------------------|----------------------|----------------|------------------|--------------------------|------------|------------------------|-------------------|

|              | $\mathbf{R}_{UP}$ | $R_{DN}$             | R <sub>S</sub> | $\mathbf{R}_{T}$ | V <sub>CCIO</sub><br>(V) | VTT<br>(V) | C <sub>L</sub><br>(pF) | V <sub>MEAS</sub> |

| 3.3-V CTT    | _                 | =-                   | 25             | 50               | 3.600                    | 1.650      | 30                     | 1.650             |

#### Notes to Table 4–102:

- (1) Input measurement point at internal node is  $0.5 \times V_{CCINT}$ .

- (2) Output measuring point for data is V<sub>MEAS</sub>. When two values are given, the first is the measurement point on the rising edge and the other is for the falling edge.

- (3) Input stimulus edge rate is 0 to V<sub>CCINT</sub> in 0.5 ns (internal signal) from the driver preceding the I/O buffer.

- (4) The first value is for the output rising edge and the second value is for the output falling edge. The hyphen (-) indicates infinite resistance or disconnection.

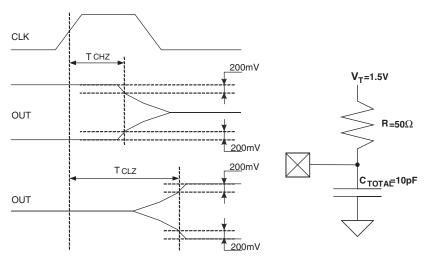

Figure 4–8 shows the measurement setup for output disable and output enable timing. The  $T_{CHZ}$  stands for clock to high Z time delay and is the same as  $T_{XZ}.$  The  $T_{CLZ}$  stands for clock to low Z (driving) time delay and is the same as  $T_{ZX}.$

Figure 4–8. Measurement Setup for  $T_{XZ}$  and  $T_{ZX}$

| Table 4–128. Enhanced PLL Specifications for -6 Speed Grades (Part 2 of 2) |                                                                                                                   |     |     |         |      |  |  |

|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|---------|------|--|--|

| Symbol                                                                     | Parameter                                                                                                         | Min | Тур | Max     | Unit |  |  |

| t <sub>SCANCLK</sub>                                                       | scanclk frequency (5)                                                                                             |     |     | 22      | MHz  |  |  |

| t <sub>DLOCK</sub>                                                         | Time required to lock dynamically (after switchover or reconfiguring any non-post-scale counters/delays) (7) (11) | (9) |     | 100     | μs   |  |  |

| t <sub>LOCK</sub>                                                          | Time required to lock from end of device configuration (11)                                                       | 10  |     | 400     | μs   |  |  |

| $f_{VCO}$                                                                  | PLL internal VCO operating range                                                                                  | 300 |     | 800 (8) | MHz  |  |  |

| t <sub>LSKEW</sub>                                                         | Clock skew between two external clock outputs driven by the same counter                                          |     | ±50 |         | ps   |  |  |

| t <sub>SKEW</sub>                                                          | Clock skew between two external clock outputs driven by the different counters with the same settings             |     | ±75 |         | ps   |  |  |

| f <sub>SS</sub>                                                            | Spread spectrum modulation frequency                                                                              | 30  |     | 150     | kHz  |  |  |

| % spread                                                                   | Percentage spread for spread spectrum frequency (10)                                                              | 0.4 | 0.5 | 0.6     | %    |  |  |

| t <sub>ARESET</sub>                                                        | Minimum pulse width on areset signal                                                                              | 10  |     |         | ns   |  |  |

| Table 4-12             | Table 4–129. Enhanced PLL Specifications for -7 Speed Grade (Part 1 of 2) |               |     |          |      |  |  |  |  |

|------------------------|---------------------------------------------------------------------------|---------------|-----|----------|------|--|--|--|--|

| Symbol                 | Parameter                                                                 | Min           | Тур | Max      | Unit |  |  |  |  |

| f <sub>IN</sub>        | Input clock frequency                                                     | 3<br>(1), (2) |     | 565      | MHz  |  |  |  |  |

| f <sub>INPFD</sub>     | Input frequency to PFD                                                    | 3             |     | 420      | MHz  |  |  |  |  |

| f <sub>INDUTY</sub>    | Input clock duty cycle                                                    | 40            |     | 60       | %    |  |  |  |  |

| f <sub>EINDUTY</sub>   | External feedback clock input duty cycle                                  | 40            |     | 60       | %    |  |  |  |  |

| t <sub>INJITTER</sub>  | Input clock period jitter                                                 |               |     | ±200 (3) | ps   |  |  |  |  |

| t <sub>EINJITTER</sub> | External feedback clock period jitter                                     |               |     | ±200 (3) | ps   |  |  |  |  |

| t <sub>FCOMP</sub>     | External feedback clock compensation time (4)                             |               |     | 6        | ns   |  |  |  |  |

| f <sub>OUT</sub>       | Output frequency for internal global or regional clock                    | 0.3           |     | 420      | MHz  |  |  |  |  |

| f <sub>OUT_EXT</sub>   | Output frequency for external clock (3)                                   | 0.3           |     | 434      | MHz  |  |  |  |  |

| Table 4-12               | Table 4–129. Enhanced PLL Specifications for -7 Speed Grade (Part 2 of 2)                                         |     |     |                                                            |              |  |  |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|------------------------------------------------------------|--------------|--|--|--|--|

| Symbol                   | Parameter                                                                                                         | Min | Тур | Max                                                        | Unit         |  |  |  |  |

| t <sub>OUTDUTY</sub>     | Duty cycle for external clock output (when set to 50%)                                                            | 45  |     | 55                                                         | %            |  |  |  |  |

| t <sub>JITTER</sub>      | Period jitter for external clock output (6)                                                                       |     |     | ±100 ps for >200-MHz outclk<br>±20 mUI for <200-MHz outclk | ps or<br>mUI |  |  |  |  |

| t <sub>CONFIG5,6</sub>   | Time required to reconfigure the scan chains for PLLs 5 and 6                                                     |     |     | 289/f <sub>SCANCLK</sub>                                   |              |  |  |  |  |

| t <sub>CONFIG11,12</sub> | Time required to reconfigure the scan chains for PLLs 11 and 12                                                   |     |     | 193/f <sub>SCANCLK</sub>                                   |              |  |  |  |  |

| t <sub>SCANCLK</sub>     | scanclk frequency (5)                                                                                             |     |     | 22                                                         | MHz          |  |  |  |  |

| t <sub>DLOCK</sub>       | Time required to lock dynamically (after switchover or reconfiguring any non-post-scale counters/delays) (7) (11) | (9) |     | 100                                                        | μs           |  |  |  |  |

| t <sub>LOCK</sub>        | Time required to lock from end of device configuration (11)                                                       | 10  |     | 400                                                        | μs           |  |  |  |  |

| f <sub>VCO</sub>         | PLL internal VCO operating range                                                                                  | 300 |     | 600 (8)                                                    | MHz          |  |  |  |  |

| t <sub>LSKEW</sub>       | Clock skew between two external clock outputs driven by the same counter                                          |     | ±50 |                                                            | ps           |  |  |  |  |

| t <sub>SKEW</sub>        | Clock skew between two external clock outputs driven by the different counters with the same settings             |     | ±75 |                                                            | ps           |  |  |  |  |

| f <sub>SS</sub>          | Spread spectrum modulation frequency                                                                              | 30  |     | 150                                                        | kHz          |  |  |  |  |

| % spread                 | Percentage spread for spread spectrum frequency (10)                                                              | 0.5 |     | 0.6                                                        | %            |  |  |  |  |

| t <sub>ARESET</sub>      | Minimum pulse width on areset signal                                                                              | 10  |     |                                                            | ns           |  |  |  |  |

| Table 4–130. Enhanced PLL Specifications for -8 Speed Grade (Part 1 of 3) |                                          |               |     |          |      |  |  |  |

|---------------------------------------------------------------------------|------------------------------------------|---------------|-----|----------|------|--|--|--|

| Symbol                                                                    | Parameter                                | Min           | Тур | Max      | Unit |  |  |  |

| f <sub>IN</sub>                                                           | Input clock frequency                    | 3<br>(1), (2) |     | 480      | MHz  |  |  |  |

| f <sub>INPFD</sub>                                                        | Input frequency to PFD                   | 3             |     | 420      | MHz  |  |  |  |

| f <sub>INDUTY</sub>                                                       | Input clock duty cycle                   | 40            |     | 60       | %    |  |  |  |

| f <sub>EINDUTY</sub>                                                      | External feedback clock input duty cycle | 40            |     | 60       | %    |  |  |  |

| t <sub>INJITTER</sub>                                                     | Input clock period jitter                |               |     | ±200 (3) | ps   |  |  |  |