Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 2566                                                    |

| Number of Logic Elements/Cells | 25660                                                   |

| Total RAM Bits                 | 1944576                                                 |

| Number of I/O                  | 597                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                         |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 780-BBGA                                                |

| Supplier Device Package        | 780-FBGA (29x29)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s25f780c7 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

viii Altera Corporation

Table 2–13 shows the number of DSP blocks in each Stratix device.

| Table 2–13. DSP Blocks in Stratix Devices Notes (1), (2) |            |                            |                              |                              |  |  |  |  |  |  |

|----------------------------------------------------------|------------|----------------------------|------------------------------|------------------------------|--|--|--|--|--|--|

| Device                                                   | DSP Blocks | Total 9 × 9<br>Multipliers | Total 18 × 18<br>Multipliers | Total 36 × 36<br>Multipliers |  |  |  |  |  |  |

| EP1S10                                                   | 6          | 48                         | 24                           | 6                            |  |  |  |  |  |  |

| EP1S20                                                   | 10         | 80                         | 40                           | 10                           |  |  |  |  |  |  |

| EP1S25                                                   | 10         | 80                         | 40                           | 10                           |  |  |  |  |  |  |

| EP1S30                                                   | 12         | 96                         | 48                           | 12                           |  |  |  |  |  |  |

| EP1S40                                                   | 14         | 112                        | 56                           | 14                           |  |  |  |  |  |  |

| EP1S60                                                   | 18         | 144                        | 72                           | 18                           |  |  |  |  |  |  |

| EP1S80                                                   | 22         | 176                        | 88                           | 22                           |  |  |  |  |  |  |

#### *Notes to Table 2–13:*

- (1) Each device has either the number of  $9 \times 9$ -,  $18 \times 18$ -, or  $36 \times 36$ -bit multipliers shown. The total number of multipliers for each device is not the sum of all the multipliers.

- (2) The number of supported multiply functions shown is based on signed/signed or unsigned/unsigned implementations.

DSP block multipliers can optionally feed an adder/subtractor or accumulator within the block depending on the configuration. This makes routing to LEs easier, saves LE routing resources, and increases performance, because all connections and blocks are within the DSP block. Additionally, the DSP block input registers can efficiently implement shift registers for FIR filter applications.

Figure 2–30 shows the top-level diagram of the DSP block configured for  $18 \times 18$ -bit multiplier mode. Figure 2–31 shows the  $9 \times 9$ -bit multiplier configuration of the DSP block.

single DSP block can implement two sums or differences from two  $18 \times 18$ -bit multipliers each or four sums or differences from two  $9 \times 9$ -bit multipliers each.

You can use the two-multipliers adder mode for complex multiplications, which are written as:

$$(a+jb)\times(c+jd) = [(a\times c) - (b\times d)] + j\times[(a\times d) + (b\times c)]$$

The two-multipliers adder mode allows a single DSP block to calculate the real part  $[(a \times c) - (b \times d)]$  using one subtractor and the imaginary part  $[(a \times d) + (b \times c)]$  using one adder, for data widths up to 18 bits. Two complex multiplications are possible for data widths up to 9 bits using four adder/subtractor/accumulator blocks. Figure 2–38 shows an 18-bit two-multipliers adder.

Figure 2–38. Two-Multipliers Adder Mode Implementing Complex Multiply

#### Four-Multipliers Adder Mode

In the four-multipliers adder mode, the DSP block adds the results of two first -stage adder/subtractor blocks. One sum of four  $18 \times 18$ -bit multipliers or two different sums of two sets of four  $9 \times 9$ -bit multipliers can be implemented in a single DSP block. The product width for each multiplier must be the same size. The four-multipliers adder mode is useful for FIR filter applications. Figure 2–39 shows the four multipliers adder mode.

The DSP block is divided into eight block units that interface with eight LAB rows on the left and right. Each block unit can be considered half of an 18 × 18-bit multiplier sub-block with 18 inputs and 18 outputs. A local interconnect region is associated with each DSP block. Like an LAB, this interconnect region can be fed with 10 direct link interconnects from the LAB to the left or right of the DSP block in the same row. All row and column routing resources can access the DSP block's local interconnect region. The outputs also work similarly to LAB outputs as well. Nine outputs from the DSP block can drive to the left LAB through direct link interconnects and nine can drive to the right LAB though direct link interconnects. All 18 outputs can drive to all types of row and column routing. Outputs can drive right- or left-column routing. Figures 2–40 and 2–41 show the DSP block interfaces to LAB rows.

DSP Block OA[17..0] MultiTrack MultiTrack Interconnect \ Interconnect A1[17..0] OB[17..0] B1[17..0] OC[17..0] A2[17..0] OD[17..0] B2[17..0] OE[17..0] A3[17..0] OF[17..0] B3[17..0] OG[17..0] A4[17..0] OH[17..0] ►B4[17..0]

Figure 2-40. DSP Block Interconnect Interface

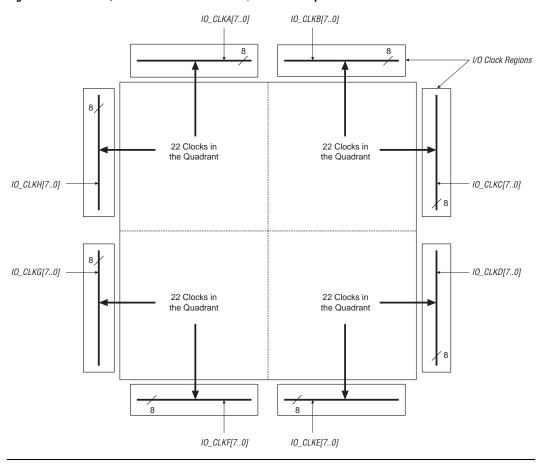

Figure 2-47. EP1S10, EP1S20 & EP1S25 Device I/O Clock Groups

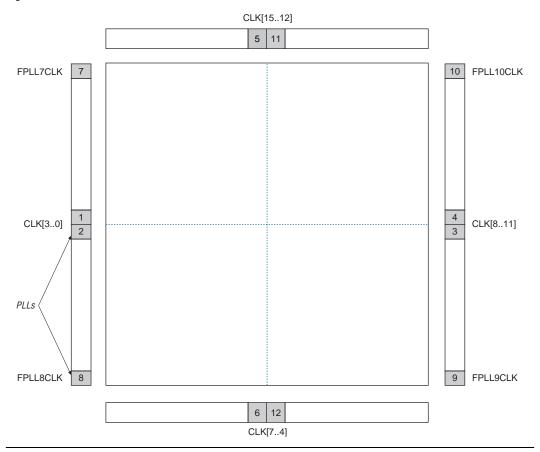

Figure 2–49 shows a top-level diagram of the Stratix device and PLL floorplan.

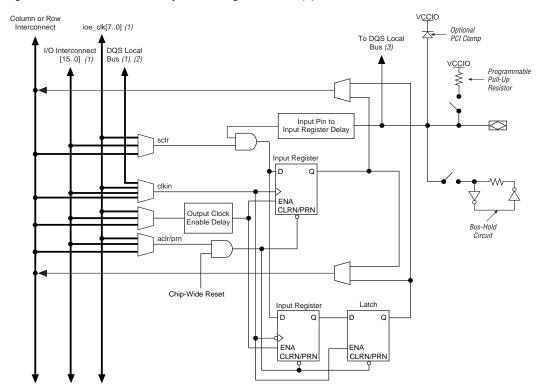

Figure 2–65. Stratix IOE in DDR Input I/O Configuration Note (1)

*Notes to Figure 2–65:*

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) This signal connection is only allowed on dedicated DQ function pins.

- (3) This signal is for dedicated DQS function pins only.

shift by the same degree amount. For example, all 10 DQS pins on the top of the device can be shifted by 90° and all 10 DQS pins on the bottom of the device can be shifted by 72°. The reference circuits require a maximum of 256 system reference clock cycles to set the correct phase on the DQS delay elements. Figure 2–69 illustrates the phase-shift reference circuit control of each DQS delay shift on the top of the device. This same circuit is duplicated on the bottom of the device.

Input

Reference

Clock

Phase

Comparator

Up/Down

Counter

Delay Chains

Control Signals to DQS Pins

Figure 2-69. Simplified Diagram of the DQS Phase-Shift Circuitry

See the *External Memory Interfaces* chapter in the *Stratix Device Handbook, Volume 2* for more information on external memory interfaces.

### **Programmable Drive Strength**

The output buffer for each Stratix device I/O pin has a programmable drive strength control for certain I/O standards. The LVTTL and LVCMOS standard has several levels of drive strength that the user can control. SSTL-3 Class I and II, SSTL-2 Class I and II, HSTL Class I and II, and 3.3-V GTL+ support a minimum setting, the lowest drive strength that guarantees the  $I_{OH}/I_{OL}$  of the standard. Using minimum settings provides signal slew rate control to reduce system noise and signal overshoot.

For more information on I/O standards supported by Stratix devices, see the *Selectable I/O Standards in Stratix & Stratix GX Devices* chapter of the *Stratix Device Handbook, Volume 2*.

Stratix devices contain eight I/O banks in addition to the four enhanced PLL external clock out banks, as shown in Figure 2–70. The four I/O banks on the right and left of the device contain circuitry to support high-speed differential I/O for LVDS, LVPECL, 3.3-V PCML, and HyperTransport inputs and outputs. These banks support all I/O standards listed in Table 2–31 except PCI I/O pins or PCI-X 1.0, GTL, SSTL-18 Class II, and HSTL Class II outputs. The top and bottom I/O banks support all single-ended I/O standards. Additionally, Stratix devices support four enhanced PLL external clock output banks, allowing clock output capabilities such as differential support for SSTL and HSTL. Table 2–32 shows I/O standard support for each I/O bank.

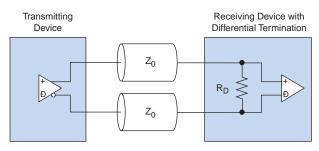

Figure 2-71. LVDS Input Differential On-Chip Termination

I/O banks on the left and right side of the device support LVDS receiver (far-end) differential termination.

Table 2–33 shows the Stratix device differential termination support.

| Table 2–33. Differential Termination Supported by I/O Banks                                          |      |  |          |  |  |  |  |

|------------------------------------------------------------------------------------------------------|------|--|----------|--|--|--|--|

| Differential Termination Support I/O Standard Support Top & Bottom Banks (3, 4, 7 & 8) (1, 2, 5 & 6) |      |  |          |  |  |  |  |

| Differential termination (1), (2)                                                                    | LVDS |  | <b>✓</b> |  |  |  |  |

Notes to Table 2-33:

- (1) Clock pin CLK0, CLK2, CLK9, CLK11, and pins FPLL [7..10] CLK do not support differential termination.

- (2) Differential termination is only supported for LVDS because of a 3.3-V  $V_{\rm CCIO}$ .

Table 2–34 shows the termination support for different pin types.

| Table 2–34. Differential Termination Support Across Pin Types |                |  |  |  |  |  |

|---------------------------------------------------------------|----------------|--|--|--|--|--|

| Pin Type                                                      | R <sub>D</sub> |  |  |  |  |  |

| Top and bottom I/O banks (3, 4, 7, and 8)                     |                |  |  |  |  |  |

| DIFFIO_RX[]                                                   | <b>✓</b>       |  |  |  |  |  |

| CLK[0,2,9,11],CLK[4-7],CLK[12-15]                             |                |  |  |  |  |  |

| CLK[1,3,8,10]                                                 | <b>✓</b>       |  |  |  |  |  |

| FCLK                                                          |                |  |  |  |  |  |

| FPLL[710]CLK                                                  |                |  |  |  |  |  |

The differential on-chip resistance at the receiver input buffer is 118  $\Omega\!\pm\!20$  %.

## 3. Configuration & Testing

\$51003-1.3

### IEEE Std. 1149.1 (JTAG) Boundary-Scan Support

All Stratix® devices provide JTAG BST circuitry that complies with the IEEE Std. 1149.1a-1990 specification. JTAG boundary-scan testing can be performed either before or after, but not during configuration. Stratix devices can also use the JTAG port for configuration together with either the Quartus® II software or hardware using either Jam Files (.jam) or Jam Byte-Code Files (.jbc).

Stratix devices support IOE I/O standard setting reconfiguration through the JTAG BST chain. The JTAG chain can update the I/O standard for all input and output pins any time before or during user mode through the CONFIG\_IO instruction. You can use this ability for JTAG testing before configuration when some of the Stratix pins drive or receive from other devices on the board using voltage-referenced standards. Since the Stratix device may not be configured before JTAG testing, the I/O pins may not be configured for appropriate electrical standards for chip-to-chip communication. Programming those I/O standards via JTAG allows you to fully test the I/O connection to other devices.

The enhanced PLL reconfiguration bits are part of the JTAG chain before configuration and after power-up. After device configuration, the PLL reconfiguration bits are not part of the JTAG chain.

The JTAG pins support 1.5-V/1.8-V or 2.5-V/3.3-V I/O standards. The TDO pin voltage is determined by the  $V_{\rm CCIO}$  of the bank where it resides. The VCCSEL pin selects whether the JTAG inputs are 1.5-V, 1.8-V, 2.5-V, or 3.3-V compatible.

Stratix devices also use the JTAG port to monitor the logic operation of the device with the SignalTap<sup>®</sup> II embedded logic analyzer. Stratix devices support the JTAG instructions shown in Table 3–1.

The Quartus II software has an Auto Usercode feature where you can choose to use the checksum value of a programming file as the JTAG user code. If selected, the checksum is automatically loaded to the USERCODE register. In the Settings dialog box in the Assignments menu, click **Device & Pin Options**, then **General**, and then turn on the **Auto Usercode** option.

| Table 4-10          | D. 3.3-V LVDS I/O Specification                                                   | ons (Part 2 of 2)                                                                          |         |         |         |      |

|---------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------|---------|---------|------|

| Symbol              | Parameter                                                                         | Conditions                                                                                 | Minimum | Typical | Maximum | Unit |

| V <sub>ICM</sub>    | Input common mode voltage (6)                                                     | LVDS<br>$0.3 \text{ V} \leq \text{V}_{\text{ID}} \leq 1.0 \text{ V}$<br>W = 1  through  10 | 100     |         | 1,100   | mV   |

|                     |                                                                                   | LVDS<br>$0.3 \text{ V} \leq \text{V}_{\text{ID}} \leq 1.0 \text{ V}$<br>W = 1  through  10 | 1,600   |         | 1,800   | mV   |

|                     |                                                                                   | LVDS<br>0.2 V ≤V <sub>ID</sub> ≤1.0 V<br>W = 1                                             | 1,100   |         | 1,600   | mV   |

|                     |                                                                                   | LVDS<br>$0.1 \text{ V} \leq \text{V}_{\text{ID}} \leq 1.0 \text{ V}$<br>W = 2  through  10 | 1,100   |         | 1,600   | mV   |

| V <sub>OD</sub> (1) | Output differential voltage (single-ended)                                        | R <sub>L</sub> = 100 Ω                                                                     | 250     | 375     | 550     | mV   |

| Δ V <sub>OD</sub>   | Change in V <sub>OD</sub> between high and low                                    | R <sub>L</sub> = 100 Ω                                                                     |         |         | 50      | mV   |

| V <sub>OCM</sub>    | Output common mode voltage                                                        | R <sub>L</sub> = 100 Ω                                                                     | 1,125   | 1,200   | 1,375   | mV   |

| Δ V <sub>OCM</sub>  | Change in V <sub>OCM</sub> between high and low                                   | R <sub>L</sub> = 100 Ω                                                                     |         |         | 50      | mV   |

| R <sub>L</sub>      | Receiver differential input<br>discrete resistor (external<br>to Stratix devices) |                                                                                            | 90      | 100     | 110     | Ω    |

| Symbol              | Parameter                   | Conditions                     | Minimum                 | Typical   | Maximum                 | Unit |

|---------------------|-----------------------------|--------------------------------|-------------------------|-----------|-------------------------|------|

| V <sub>CCIO</sub>   | Output supply voltage       |                                | 2.375                   | 2.5       | 2.625                   | V    |

| $V_{TT}$            | Termination voltage         |                                | V <sub>REF</sub> - 0.04 | $V_{REF}$ | V <sub>REF</sub> + 0.04 | V    |

| $V_{REF}$           | Reference voltage           |                                | 1.15                    | 1.25      | 1.35                    | V    |

| V <sub>IH(DC)</sub> | High-level DC input voltage |                                | V <sub>REF</sub> + 0.18 |           | 3.0                     | V    |

| V <sub>IL(DC)</sub> | Low-level DC input voltage  |                                | -0.3                    |           | V <sub>REF</sub> – 0.18 | V    |

| V <sub>IH(AC)</sub> | High-level AC input voltage |                                | V <sub>REF</sub> + 0.35 |           |                         | V    |

| V <sub>IL(AC)</sub> | Low-level AC input voltage  |                                |                         |           | V <sub>REF</sub> - 0.35 | ٧    |

| V <sub>OH</sub>     | High-level output voltage   | $I_{OH} = -8.1 \text{ mA}$ (3) | V <sub>TT</sub> + 0.57  |           |                         | V    |

| V <sub>OL</sub>     | Low-level output voltage    | I <sub>OL</sub> = 8.1 mA (3)   |                         |           | V <sub>TT</sub> – 0.57  | V    |

| Table 4-21          | Table 4–21. SSTL-2 Class II Specifications |                                 |                         |           |                         |      |  |  |  |  |  |  |  |

|---------------------|--------------------------------------------|---------------------------------|-------------------------|-----------|-------------------------|------|--|--|--|--|--|--|--|

| Symbol              | Parameter                                  | Conditions                      | Minimum                 | Typical   | Maximum                 | Unit |  |  |  |  |  |  |  |

| V <sub>CCIO</sub>   | Output supply voltage                      |                                 | 2.375                   | 2.5       | 2.625                   | V    |  |  |  |  |  |  |  |

| V <sub>TT</sub>     | Termination voltage                        |                                 | V <sub>REF</sub> – 0.04 | $V_{REF}$ | V <sub>REF</sub> + 0.04 | V    |  |  |  |  |  |  |  |

| V <sub>REF</sub>    | Reference voltage                          |                                 | 1.15                    | 1.25      | 1.35                    | V    |  |  |  |  |  |  |  |

| V <sub>IH(DC)</sub> | High-level DC input voltage                |                                 | V <sub>REF</sub> + 0.18 |           | V <sub>CCIO</sub> + 0.3 | ٧    |  |  |  |  |  |  |  |

| V <sub>IL(DC)</sub> | Low-level DC input voltage                 |                                 | -0.3                    |           | V <sub>REF</sub> – 0.18 | V    |  |  |  |  |  |  |  |

| V <sub>IH(AC)</sub> | High-level AC input voltage                |                                 | V <sub>REF</sub> + 0.35 |           |                         | V    |  |  |  |  |  |  |  |

| V <sub>IL(AC)</sub> | Low-level AC input voltage                 |                                 |                         |           | V <sub>REF</sub> – 0.35 | V    |  |  |  |  |  |  |  |

| V <sub>OH</sub>     | High-level output voltage                  | $I_{OH} = -16.4 \text{ mA}$ (3) | V <sub>TT</sub> + 0.76  |           |                         | V    |  |  |  |  |  |  |  |

| V <sub>OL</sub>     | Low-level output voltage                   | I <sub>OL</sub> = 16.4 mA (3)   |                         |           | V <sub>TT</sub> – 0.76  | V    |  |  |  |  |  |  |  |

| Table 4-22          | Table 4–22. SSTL-3 Class I Specifications (Part 1 of 2) |            |                         |           |                         |      |  |  |  |  |  |  |  |

|---------------------|---------------------------------------------------------|------------|-------------------------|-----------|-------------------------|------|--|--|--|--|--|--|--|

| Symbol              | Parameter                                               | Conditions | Minimum                 | Typical   | Maximum                 | Unit |  |  |  |  |  |  |  |

| V <sub>CCIO</sub>   | Output supply voltage                                   |            | 3.0                     | 3.3       | 3.6                     | V    |  |  |  |  |  |  |  |

| V <sub>TT</sub>     | Termination voltage                                     |            | V <sub>REF</sub> - 0.05 | $V_{REF}$ | V <sub>REF</sub> + 0.05 | V    |  |  |  |  |  |  |  |

| V <sub>REF</sub>    | Reference voltage                                       |            | 1.3                     | 1.5       | 1.7                     | V    |  |  |  |  |  |  |  |

| V <sub>IH(DC)</sub> | High-level DC input voltage                             |            | V <sub>REF</sub> + 0.2  |           | V <sub>CCIO</sub> + 0.3 | V    |  |  |  |  |  |  |  |

| V <sub>IL(DC)</sub> | Low-level DC input voltage                              |            | -0.3                    |           | V <sub>REF</sub> – 0.2  | V    |  |  |  |  |  |  |  |

| V <sub>IH(AC)</sub> | High-level AC input voltage                             |            | V <sub>REF</sub> + 0.4  |           |                         | V    |  |  |  |  |  |  |  |

| Symbol                       | Parameter                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>SU</sub>              | Input, pipeline, and output register setup time before clock                                                                                                                                                                                                                                                                                              |

| t <sub>H</sub>               | Input, pipeline, and output register hold time after clock                                                                                                                                                                                                                                                                                                |

| t <sub>CO</sub>              | Input, pipeline, and output register clock-to-output delay                                                                                                                                                                                                                                                                                                |

| t <sub>INREG2PIPE9</sub>     | Input Register to DSP Block pipeline register in $9 \times 9$ -bit mode                                                                                                                                                                                                                                                                                   |

| t <sub>INREG2PIPE18</sub>    | Input Register to DSP Block pipeline register in 18 $\times$ 18-bit mode                                                                                                                                                                                                                                                                                  |

| t <sub>PIPE2OUTREG2ADD</sub> | DSP Block Pipeline Register to output register delay in Two-Multipliers Adder mode                                                                                                                                                                                                                                                                        |

| t <sub>PIPE2OUTREG4ADD</sub> | DSP Block Pipeline Register to output register delay in Four-Multipliers Adder mode                                                                                                                                                                                                                                                                       |

| t <sub>PD9</sub>             | Combinatorial input to output delay for 9 × 9                                                                                                                                                                                                                                                                                                             |

| t <sub>PD18</sub>            | Combinatorial input to output delay for 18 × 18                                                                                                                                                                                                                                                                                                           |

| t <sub>PD36</sub>            | Combinatorial input to output delay for 36 × 36                                                                                                                                                                                                                                                                                                           |

| t <sub>CLR</sub>             | Minimum clear pulse width                                                                                                                                                                                                                                                                                                                                 |

| t <sub>CLKHL</sub>           | Register minimum clock high or low time. This is a limit on the min time for the clock on the registers in these blocks. The actual performance is dependent upon the internal point-to-point delays in the blocks and may give slower performance as shown in Table 4–36 on page 4–20 and as reported by the timing analyzer in the Quartus II software. |

| Table 4-77. L         | Table 4–77. EP1S30 External I/O Timing on Row Pins Using Regional Clock Networks |         |         |                |       |                |       |                |      |  |  |

|-----------------------|----------------------------------------------------------------------------------|---------|---------|----------------|-------|----------------|-------|----------------|------|--|--|

|                       | -5 Spee                                                                          | d Grade | -6 Spee | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |      |  |  |

| Parameter             | Min                                                                              | Max     | Min     | Max            | Min   | Max            | Min   | Max            | Unit |  |  |

| t <sub>INSU</sub>     | 2.322                                                                            |         | 2.467   |                | 2.828 |                | 3.342 |                | ns   |  |  |

| t <sub>INH</sub>      | 0.000                                                                            |         | 0.000   |                | 0.000 |                | 0.000 |                | ns   |  |  |

| t <sub>OUTCO</sub>    | 2.731                                                                            | 5.408   | 2.731   | 5.843          | 2.731 | 6.360          | 2.731 | 7.036          | ns   |  |  |

| t <sub>XZ</sub>       | 2.758                                                                            | 5.462   | 2.758   | 5.899          | 2.758 | 6.428          | 2.758 | 7.118          | ns   |  |  |

| t <sub>ZX</sub>       | 2.758                                                                            | 5.462   | 2.758   | 5.899          | 2.758 | 6.428          | 2.758 | 7.118          | ns   |  |  |

| t <sub>INSUPLL</sub>  | 1.291                                                                            |         | 1.283   |                | 1.469 |                | 1.832 |                | ns   |  |  |

| t <sub>INHPLL</sub>   | 0.000                                                                            |         | 0.000   |                | 0.000 |                | 0.000 |                | ns   |  |  |

| t <sub>OUTCOPLL</sub> | 1.192                                                                            | 2.539   | 1.192   | 2.737          | 1.192 | 2.786          | 1.192 | 2.742          | ns   |  |  |

| t <sub>XZPLL</sub>    | 1.219                                                                            | 2.539   | 1.219   | 2.793          | 1.219 | 2.854          | 1.219 | 2.824          | ns   |  |  |

| t <sub>ZXPLL</sub>    | 1.219                                                                            | 2.539   | 1.219   | 2.793          | 1.219 | 2.854          | 1.219 | 2.824          | ns   |  |  |

| Table 4-78. I         | Table 4–78. EP1S30 External I/O Timing on Row Pins Using Global Clock Networks |         |         |                |       |                |       |                |      |  |  |

|-----------------------|--------------------------------------------------------------------------------|---------|---------|----------------|-------|----------------|-------|----------------|------|--|--|

|                       | -5 Spee                                                                        | d Grade | -6 Spee | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |      |  |  |

| Parameter             | Min                                                                            | Max     | Min     | Max            | Min   | Max            | Min   | Max            | Unit |  |  |

| t <sub>INSU</sub>     | 1.995                                                                          |         | 2.089   |                | 2.398 |                | 2.830 |                | ns   |  |  |

| t <sub>INH</sub>      | 0.000                                                                          |         | 0.000   |                | 0.000 |                | 0.000 |                | ns   |  |  |

| t <sub>OUTCO</sub>    | 2.917                                                                          | 5.735   | 2.917   | 6.221          | 2.917 | 6.790          | 2.917 | 7.548          | ns   |  |  |

| t <sub>XZ</sub>       | 2.944                                                                          | 5.789   | 2.944   | 6.277          | 2.944 | 6.858          | 2.944 | 7.630          | ns   |  |  |

| t <sub>ZX</sub>       | 2.944                                                                          | 5.789   | 2.944   | 6.277          | 2.944 | 6.858          | 2.944 | 7.630          | ns   |  |  |

| t <sub>INSUPLL</sub>  | 1.337                                                                          |         | 1.312   |                | 1.508 |                | 1.902 |                | ns   |  |  |

| t <sub>INHPLL</sub>   | 0.000                                                                          |         | 0.000   |                | 0.000 |                | 0.000 |                | ns   |  |  |

| t <sub>OUTCOPLL</sub> | 1.164                                                                          | 2.493   | 1.164   | 2.708          | 1.164 | 2.747          | 1.164 | 2.672          | ns   |  |  |

| t <sub>XZPLL</sub>    | 1.191                                                                          | 2.547   | 1.191   | 2.764          | 1.191 | 2.815          | 1.191 | 2.754          | ns   |  |  |

| t <sub>ZXPLL</sub>    | 1.191                                                                          | 2.547   | 1.191   | 2.764          | 1.191 | 2.815          | 1.191 | 2.754          | ns   |  |  |

Tables 4–79 through 4–84 show the external timing parameters on column and row pins for EP1S40 devices.

| Table 4-79. I      | Table 4–79. EP1S40 External I/O Timing on Column Pins Using Fast Regional Clock Networks |         |                |       |                |       |                |       |      |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------|---------|----------------|-------|----------------|-------|----------------|-------|------|--|--|--|--|

|                    | -5 Spee                                                                                  | d Grade | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       |      |  |  |  |  |

| Parameter          | Min                                                                                      | Max     | Min            | Max   | Min            | Max   | Min            | Max   | Unit |  |  |  |  |

| t <sub>INSU</sub>  | 2.696                                                                                    |         | 2.907          |       | 3.290          |       | 2.899          |       | ns   |  |  |  |  |

| t <sub>INH</sub>   | 0.000                                                                                    |         | 0.000          |       | 0.000          |       | 0.000          |       | ns   |  |  |  |  |

| t <sub>OUTCO</sub> | 2.506                                                                                    | 5.015   | 2.506          | 5.348 | 2.506          | 5.809 | 2.698          | 7.286 | ns   |  |  |  |  |

| t <sub>XZ</sub>    | 2.446                                                                                    | 4.889   | 2.446          | 5.216 | 2.446          | 5.685 | 2.638          | 7.171 | ns   |  |  |  |  |

| t <sub>ZX</sub>    | 2.446                                                                                    | 4.889   | 2.446          | 5.216 | 2.446          | 5.685 | 2.638          | 7.171 | ns   |  |  |  |  |

| Table 4–80. EP1S40 External I/O Timing on Column Pins Using Regional Clock Networks |         |         |                     |       |                |       |                |       |      |

|-------------------------------------------------------------------------------------|---------|---------|---------------------|-------|----------------|-------|----------------|-------|------|

| Parameter                                                                           | -5 Spee | d Grade | rade -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | 11!4 |

| Parameter                                                                           | Min     | Max     | Min                 | Max   | Min            | Max   | Min Max Unit   |       |      |

| t <sub>INSU</sub>                                                                   | 2.413   |         | 2.581               |       | 2.914          |       | 2.938          |       | ns   |

| t <sub>INH</sub>                                                                    | 0.000   |         | 0.000               |       | 0.000          |       | 0.000          |       | ns   |

| t <sub>outco</sub>                                                                  | 2.668   | 5.254   | 2.668               | 5.628 | 2.668          | 6.132 | 2.869          | 7.307 | ns   |

| t <sub>XZ</sub>                                                                     | 2.608   | 5.128   | 2.608               | 5.496 | 2.608          | 6.008 | 2.809          | 7.192 | ns   |

| t <sub>ZX</sub>                                                                     | 2.608   | 5.128   | 2.608               | 5.496 | 2.608          | 6.008 | 2.809          | 7.192 | ns   |

| t <sub>INSUPLL</sub>                                                                | 1.385   |         | 1.376               |       | 1.609          |       | 1.837          |       | ns   |

| t <sub>INHPLL</sub>                                                                 | 0.000   |         | 0.000               |       | 0.000          |       | 0.000          |       | ns   |

| t <sub>OUTCOPLL</sub>                                                               | 1.117   | 2.382   | 1.117               | 2.552 | 1.117          | 2.504 | 1.117          | 2.542 | ns   |

| t <sub>XZPLL</sub>                                                                  | 1.057   | 2.256   | 1,057               | 2.420 | 1.057          | 2.380 | 1.057          | 2.427 | ns   |

| t <sub>ZXPLL</sub>                                                                  | 1.057   | 2.256   | 1,057               | 2.420 | 1.057          | 2.380 | 1.057          | 2.427 | ns   |

| Davamatav             | -5 Speed Grade -6 Spee |       | ed Grade -7 Speed |       | d Grade | -8 Speed Grade |     |     |      |

|-----------------------|------------------------|-------|-------------------|-------|---------|----------------|-----|-----|------|

| Parameter             | Min                    | Max   | Min               | Max   | Min     | Max            | Min | Max | Unit |

| t <sub>INSU</sub>     | 0.884                  |       | 0.976             |       | 1.118   |                | NA  |     | ns   |

| t <sub>INH</sub>      | 0.000                  |       | 0.000             |       | 0.000   |                | NA  |     | ns   |

| t <sub>outco</sub>    | 3.267                  | 6.274 | 3.267             | 6.721 | 3.267   | 7.415          | NA  | NA  | ns   |

| t <sub>XZ</sub>       | 3.207                  | 6.148 | 3.207             | 6.589 | 3.207   | 7.291          | NA  | NA  | ns   |

| t <sub>ZX</sub>       | 3.207                  | 6.148 | 3.207             | 6.589 | 3.207   | 7.291          | NA  | NA  | ns   |

| t <sub>INSUPLL</sub>  | 0.506                  |       | 0.656             |       | 0.838   |                | NA  |     | ns   |

| t <sub>INHPLL</sub>   | 0.000                  |       | 0.000             |       | 0.000   |                | NA  |     | ns   |

| t <sub>OUTCOPLL</sub> | 1.635                  | 2.805 | 1.635             | 2.809 | 1.635   | 2.828          | NA  | NA  | ns   |

| t <sub>XZPLL</sub>    | 1.575                  | 2.679 | 1.575             | 2.677 | 1.575   | 2.704          | NA  | NA  | ns   |

| t <sub>ZXPLL</sub>    | 1.575                  | 2.679 | 1.575             | 2.677 | 1.575   | 2.704          | NA  | NA  | ns   |

| Table 4–94. l      | Table 4–94. EP1880 External I/O Timing on Row Pins Using Fast Regional Clock Networks Note (1) |       |                |       |                            |       |                |     |                |  |      |

|--------------------|------------------------------------------------------------------------------------------------|-------|----------------|-------|----------------------------|-------|----------------|-----|----------------|--|------|

| Parameter          | -5 Speed Grade                                                                                 |       | -5 Speed Grade |       | Speed Grade -6 Speed Grade |       | -7 Speed Grade |     | -8 Speed Grade |  | Unit |

|                    | Min                                                                                            | Max   | Min            | Max   | Min                        | Max   | Min            | Max |                |  |      |

| t <sub>INSU</sub>  | 2.792                                                                                          |       | 2.993          |       | 3.386                      |       | NA             |     | ns             |  |      |

| t <sub>INH</sub>   | 0.000                                                                                          |       | 0.000          |       | 0.000                      |       | NA             |     | ns             |  |      |

| t <sub>OUTCO</sub> | 2.619                                                                                          | 5.235 | 2.619          | 5.609 | 2.619                      | 6.086 | NA             | NA  | ns             |  |      |

| t <sub>XZ</sub>    | 2.646                                                                                          | 5.289 | 2.646          | 5.665 | 2.646                      | 6.154 | NA             | NA  | ns             |  |      |

| t <sub>ZX</sub>    | 2.646                                                                                          | 5.289 | 2.646          | 5.665 | 2.646                      | 6.154 | NA             | NA  | ns             |  |      |

Table 4–114. Stratix Maximum Input Clock Rate for CLK[7..4] & CLK[15..12] Pins in Flip-Chip Packages (Part 2 of 2)

| I/O Standard                  | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------|-------------------|-------------------|-------------------|-------------------|------|

| LVDS (1)                      | 645               | 645               | 622               | 622               | MHz  |

| HyperTransport technology (1) | 500               | 500               | 450               | 450               | MHz  |

Table 4–115. Stratix Maximum Input Clock Rate for CLK[0, 2, 9, 11] Pins & FPLL[10..7]CLK Pins in Flip-Chip Packages

| I/O Standard                  | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------|-------------------|-------------------|-------------------|-------------------|------|

| LVTTL                         | 422               | 422               | 390               | 390               | MHz  |

| 2.5 V                         | 422               | 422               | 390               | 390               | MHz  |

| 1.8 V                         | 422               | 422               | 390               | 390               | MHz  |

| 1.5 V                         | 422               | 422               | 390               | 390               | MHz  |

| LVCMOS                        | 422               | 422               | 390               | 390               | MHz  |

| GTL+                          | 300               | 250               | 200               | 200               | MHz  |

| SSTL-3 Class I                | 400               | 350               | 300               | 300               | MHz  |

| SSTL-3 Class II               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-2 Class I                | 400               | 350               | 300               | 300               | MHz  |

| SSTL-2 Class II               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-18 Class I               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-18 Class II              | 400               | 350               | 300               | 300               | MHz  |

| 1.5-V HSTL Class I            | 400               | 350               | 300               | 300               | MHz  |

| 1.8-V HSTL Class I            | 400               | 350               | 300               | 300               | MHz  |

| CTT                           | 300               | 250               | 200               | 200               | MHz  |

| Differential 1.5-V HSTL<br>C1 | 400               | 350               | 300               | 300               | MHz  |

| LVPECL (1)                    | 717               | 717               | 640               | 640               | MHz  |

| PCML (1)                      | 400               | 375               | 350               | 350               | MHz  |

| LVDS (1)                      | 717               | 717               | 640               | 640               | MHz  |

| HyperTransport technology (1) | 717               | 717               | 640               | 640               | MHz  |

| Table 4–129. Enhanced PLL Specifications for -7 Speed Grade (Part 2 of 2) |                                                                                                                   |     |     |                                                            |              |  |  |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|------------------------------------------------------------|--------------|--|--|

| Symbol                                                                    | Parameter                                                                                                         | Min | Тур | Max                                                        | Unit         |  |  |

| t <sub>OUTDUTY</sub>                                                      | Duty cycle for external clock output (when set to 50%)                                                            | 45  |     | 55                                                         | %            |  |  |

| t <sub>JITTER</sub>                                                       | Period jitter for external clock output (6)                                                                       |     |     | ±100 ps for >200-MHz outclk<br>±20 mUI for <200-MHz outclk | ps or<br>mUI |  |  |

| t <sub>CONFIG5,6</sub>                                                    | Time required to reconfigure the scan chains for PLLs 5 and 6                                                     |     |     | 289/f <sub>SCANCLK</sub>                                   |              |  |  |

| t <sub>CONFIG11,12</sub>                                                  | Time required to reconfigure the scan chains for PLLs 11 and 12                                                   |     |     | 193/f <sub>SCANCLK</sub>                                   |              |  |  |

| t <sub>SCANCLK</sub>                                                      | scanclk frequency (5)                                                                                             |     |     | 22                                                         | MHz          |  |  |

| t <sub>DLOCK</sub>                                                        | Time required to lock dynamically (after switchover or reconfiguring any non-post-scale counters/delays) (7) (11) | (9) |     | 100                                                        | μs           |  |  |

| t <sub>LOCK</sub>                                                         | Time required to lock from end of device configuration (11)                                                       | 10  |     | 400                                                        | μs           |  |  |

| f <sub>VCO</sub>                                                          | PLL internal VCO operating range                                                                                  | 300 |     | 600 (8)                                                    | MHz          |  |  |

| t <sub>LSKEW</sub>                                                        | Clock skew between two external clock outputs driven by the same counter                                          |     | ±50 |                                                            | ps           |  |  |

| t <sub>SKEW</sub>                                                         | Clock skew between two external clock outputs driven by the different counters with the same settings             |     | ±75 |                                                            | ps           |  |  |

| f <sub>SS</sub>                                                           | Spread spectrum modulation frequency                                                                              | 30  |     | 150                                                        | kHz          |  |  |

| % spread                                                                  | Percentage spread for spread spectrum frequency (10)                                                              | 0.5 |     | 0.6                                                        | %            |  |  |

| t <sub>ARESET</sub>                                                       | Minimum pulse width on areset signal                                                                              | 10  |     |                                                            | ns           |  |  |

| Table 4–130. Enhanced PLL Specifications for -8 Speed Grade (Part 1 of 3) |                                          |               |     |          |      |

|---------------------------------------------------------------------------|------------------------------------------|---------------|-----|----------|------|

| Symbol                                                                    | Parameter                                | Min           | Тур | Max      | Unit |

| f <sub>IN</sub>                                                           | Input clock frequency                    | 3<br>(1), (2) |     | 480      | MHz  |

| f <sub>INPFD</sub>                                                        | Input frequency to PFD                   | 3             |     | 420      | MHz  |

| f <sub>INDUTY</sub>                                                       | Input clock duty cycle                   | 40            |     | 60       | %    |

| f <sub>EINDUTY</sub>                                                      | External feedback clock input duty cycle | 40            |     | 60       | %    |

| t <sub>INJITTER</sub>                                                     | Input clock period jitter                |               |     | ±200 (3) | ps   |

| Mode 2–36                               | Port I/O Standards 2–102                            |

|-----------------------------------------|-----------------------------------------------------|

| Row & Column Interface Unit             | I/O Standards Supported for Enhanced PLL            |

| Signals 2–43                            | Pins 2–94                                           |

| Parity Bit Support 2–24                 | Lock Detect & Programmable Gated                    |

| Shift Register                          | Locked 2–98                                         |

| Memory Configuration 2–26               | PLL Locations 2–84                                  |

| Support 2–25                            | Programmable Bandwidth 2–91                         |

| Simple Dual-Port & Single-Port Memory   | Programmable Delay Chain 2-111                      |

| Configurations 2–23                     | Programmable Duty Cycle 2–98                        |

| Stratix IOE in DDR Input I/O            | Reconfiguration 2–90                                |

| Configuration 2–112                     |                                                     |

| Stratix IOE in DDR Output I/O           | Т                                                   |

| Configuration 2–114                     | ı                                                   |

| TriMatrix Memory 2–21                   | Testing                                             |

| True Dual-Port Memory                   | Temperature Sensing Diode 3–13                      |

| Configuration 2–22                      | Electrical Characteristics 3–14                     |

|                                         | External 3–14                                       |

| 0                                       | Temperature vs. Temperature-Sensing Diode           |

|                                         | Voltage 3–15                                        |

| Ordering Information 5–1                | Timing                                              |

| Device Pin-Outs 5–1                     | DSP                                                 |

| Packaging Ordering Information 5–2      | Block Internal Timing                               |

| Reference & Ordering Information 5–1    | Microparameter                                      |

| Output Registers 2–64                   | Descriptions 4–23                                   |

| Output Selection Multiplexer 2–64       | Microparameters 4–29                                |

|                                         | Dual-Port RAM Timing Microparameter                 |

| P                                       | Waveform 4–27                                       |

| P. 1                                    | External Timing in Stratix Devices 4–33             |

| Packaging                               | High-Speed I/O Timing 4–87                          |

| BGA Package Sizes 1–4                   | High-Speed Timing Specifications & Terminology 4–87 |

| Device Speed Grades 1–5                 | Internal Parameters 4–22                            |

| FineLine BGA Package Sizes 1–5          | IOE Internal Timing Microparameter                  |

| PCI-X 1.0 Specifications 4–10           | Descriptions 4–22                                   |

| Phase Shifting 2–103<br>PLL             | LE Internal Timing Microparameters 4–28             |

| Advanced Clear & Enable Control 2–98    | Logic Elements Internal Timing Microparam-          |

| Dynamically Programmable Counters & De- | eter Descriptions 4–22                              |

| lays in Stratix Device Enhanced         | Model 4–19                                          |

| PLLs 2–91                               | PLL Timing 4–94                                     |

| Enhanced                                | Preliminary & Final 4–19                            |

| Fast PLLs 2–81                          | Stratix Device Timing Model Status 4–19             |

| Fast PLL 2–100                          | Stratix JTAG                                        |

| Channel Layout EP1S10, EP1S20 or        | Timing Parameters & Values 3–4                      |

| EP1S25 Devices 2–138                    | TriMatrix Memory                                    |

| Channel Layout EP1S30 to EP1S80         | TriMatrix Memory Features 2–21                      |

| Devices 2–139                           | •                                                   |

Index-6 Altera Corporation