## Intel - EP1S25F780I6N Datasheet

Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Product Status                 | Obsolete                                                 |

|--------------------------------|----------------------------------------------------------|

| Number of LABs/CLBs            | 2566                                                     |

| Number of Logic Elements/Cells | 25660                                                    |

| Total RAM Bits                 | 1944576                                                  |

| Number of I/O                  | 597                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                       |

| Package / Case                 | 780-BBGA                                                 |

| Supplier Device Package        | 780-FBGA (29x29)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s25f780i6n |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Typographic Conventions

This document uses the typographic conventions shown below.

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial<br>Capital Letters   | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                                                                                              |

| bold type                                   | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: <b>f</b> <sub>MAX</sub> , <b>\qdesigns</b> directory, <b>d:</b> drive, <b>chiptrip.gdf</b> file.                                             |

| Italic Type with Initial Capital<br>Letters | Document titles are shown in italic type with initial capital letters. Example: AN 75:<br>High-Speed Board Designs.                                                                                                                                                                                                     |

| Italic type                                 | Internal timing parameters and variables are shown in italic type.<br>Examples: $t_{PlA}$ , $n + 1$ .                                                                                                                                                                                                                   |

|                                             | Variable names are enclosed in angle brackets (< >) and shown in italic type.<br>Example: <i><file name=""></file></i> , <i><project name="">.pof</project></i> file.                                                                                                                                                   |

| Initial Capital Letters                     | Keyboard keys and menu names are shown with initial capital letters. Examples:<br>Delete key, the Options menu.                                                                                                                                                                                                         |

| "Subheading Title"                          | References to sections within a document and titles of on-line help topics are shown in quotation marks. Example: "Typographic Conventions."                                                                                                                                                                            |

| Courier type                                | Signal and port names are shown in lowercase Courier type. Examples: data1, tdi, input. Active-low signals are denoted by suffix n, e.g., resetn.                                                                                                                                                                       |

|                                             | Anything that must be typed exactly as it appears is shown in Courier type. For example: c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an actual file, such as a Report File, references to parts of files (e.g., the AHDL keyword SUBDESIGN), as well as logic function names (e.g., TRI) are shown in Courier. |

| 1., 2., 3., and<br>a., b., c., etc.         | Numbered steps are used in a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                                                                                                                                                        |

| ••                                          | Bullets are used in a list of items when the sequence of the items is not important.                                                                                                                                                                                                                                    |

| $\checkmark$                                | The checkmark indicates a procedure that consists of one step only.                                                                                                                                                                                                                                                     |

|                                             | The hand points to information that requires special attention.                                                                                                                                                                                                                                                         |

| Ţ                                           | The angled arrow indicates you should press the Enter key.                                                                                                                                                                                                                                                              |

| •••                                         | The feet direct you to more information on a particular topic.                                                                                                                                                                                                                                                          |

dedicated clocks, these registers provide exceptional performance and interface support with external memory devices such as DDR SDRAM, FCRAM, ZBT, and QDR SRAM devices.

High-speed serial interface channels support transfers at up to 840 Mbps using LVDS, LVPECL, 3.3-V PCML, or HyperTransport technology I/O standards.

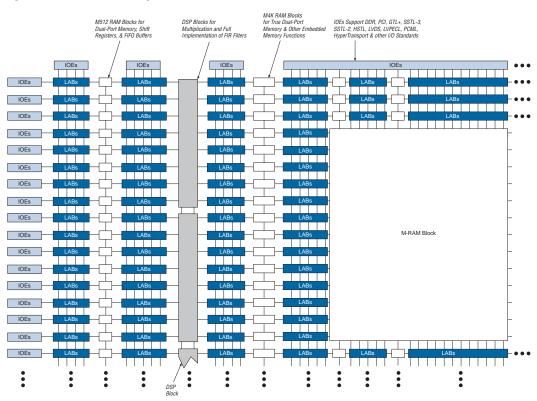

Figure 2–1 shows an overview of the Stratix device.

| Table 2–1. Stratix Device Resources |                            |                           |                 |                             |                |          |

|-------------------------------------|----------------------------|---------------------------|-----------------|-----------------------------|----------------|----------|

| Device                              | M512 RAM<br>Columns/Blocks | M4K RAM<br>Columns/Blocks | M-RAM<br>Blocks | DSP Block<br>Columns/Blocks | LAB<br>Columns | LAB Rows |

| EP1S10                              | 4 / 94                     | 2 / 60                    | 1               | 2/6                         | 40             | 30       |

| EP1S20                              | 6 / 194                    | 2 / 82                    | 2               | 2 / 10                      | 52             | 41       |

| EP1S25                              | 6 / 224                    | 3 / 138                   | 2               | 2 / 10                      | 62             | 46       |

| EP1S30                              | 7 / 295                    | 3 / 171                   | 4               | 2 / 12                      | 67             | 57       |

| EP1S40                              | 8 / 384                    | 3 / 183                   | 4               | 2 / 14                      | 77             | 61       |

| EP1S60                              | 10 / 574                   | 4 / 292                   | 6               | 2 / 18                      | 90             | 73       |

| EP1S80                              | 11 / 767                   | 4 / 364                   | 9               | 2 / 22                      | 101            | 91       |

The number of M512 RAM, M4K RAM, and DSP blocks varies by device along with row and column numbers and M-RAM blocks. Table 2–1 lists the resources available in Stratix devices.

# Logic Array Blocks

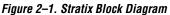

Each LAB consists of 10 LEs, LE carry chains, LAB control signals, local interconnect, LUT chain, and register chain connection lines. The local interconnect transfers signals between LEs in the same LAB. LUT chain connections transfer the output of one LE's LUT to the adjacent LE for fast sequential LUT connections within the same LAB. Register chain connections transfer the output of one LE's register to the adjacent LE's register within an LAB. The Quartus<sup>®</sup> II Compiler places associated logic within an LAB or adjacent LABs, allowing the use of local, LUT chain, and register chain connections for performance and area efficiency. Figure 2–2 shows the Stratix LAB.

blocks facing to the left, and another 10 possible from the right adjacent LABs for M-RAM blocks facing to the right. For column interfacing, every M-RAM column unit connects to the right and left column lines, allowing each M-RAM column unit to communicate directly with three columns of LABs. Figures 2–21 through 2–23 show the interface between the M-RAM block and the logic array.

## Input/Output Clock Mode

Input/output clock mode can be implemented for both the true and simple dual-port memory modes. On each of the two ports, A or B, one clock controls all registers for inputs into the memory block: data input, wren, and address. The other clock controls the block's data output registers. Each memory block port, A or B, also supports independent clock enables and asynchronous clear signals for input and output registers. Figures 2–25 and 2–26 show the memory block in input/output clock mode.

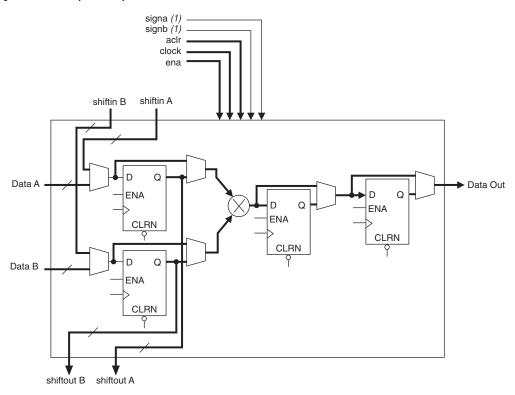

Figure 2–35. Simple Multiplier Mode

#### Note to Figure 2-35:

(1) These signals are not registered or registered once to match the data path pipeline.

DSP blocks can also implement one  $36 \times 36$ -bit multiplier in multiplier mode. DSP blocks use four  $18 \times 18$ -bit multipliers combined with dedicated adder and internal shift circuitry to achieve 36-bit multiplication. The input shift register feature is not available for the  $36 \times 36$ -bit multiplier. In  $36 \times 36$ -bit mode, the device can use the register that is normally a multiplier-result-output register as a pipeline stage for the  $36 \times 36$ -bit multiplier. Figure 2–36 shows the  $36 \times 36$ -bit multiply mode.

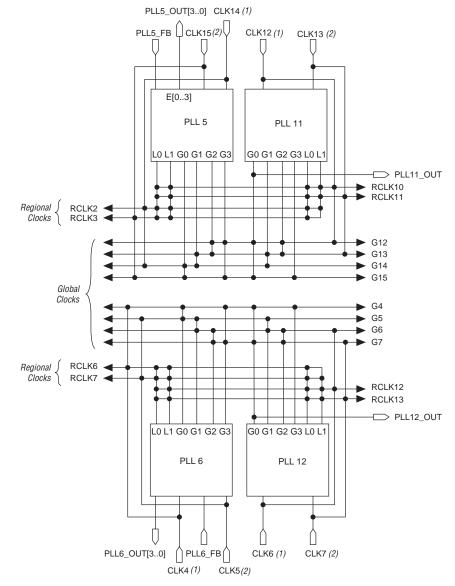

Figure 2–51. Global & Regional Clock Connections from Top Clock Pins & Enhanced PLL Outputs Note (1)

#### Notes to Figure 2–51:

- (1) PLLs 1 to 4 and 7 to 10 are fast PLLs. PLLs 5, 6, 11, and 12 are enhanced PLLs.

- (2) CLK4, CLK6, CLK12, and CLK14 feed the corresponding PLL's inclk0 port.

- (3) CLK5, CLK7, CLK13, and CLK15 feed the corresponding PLL's inclk1 port.

- (4) The EP1S40 device in the 780-pin FineLine BGA package does not support PLLs 11 and 12.

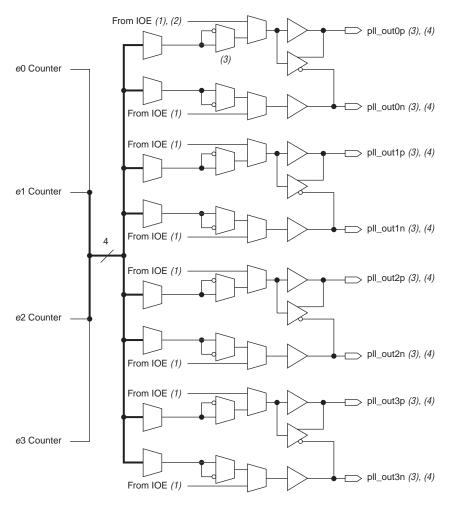

Figure 2–55. External Clock Outputs for PLLs 5 & 6

#### Notes to Figure 2–55:

- (1) The design can use each external clock output pin as a general-purpose output pin from the logic array. These pins are multiplexed with IOE outputs.

- (2) Two single-ended outputs are possible per output counter—either two outputs of the same frequency and phase or one shifted 180°.

- (3) EP1S10, EP1S20, and EP1S25 devices in 672-pin BGA and 484- and 672-pin FineLine BGA packages only have two pairs of external clocks (i.e., pll\_out0p, pll\_out0n, pll\_out1p, and pll\_out1n).

- (4) Differential SSTL and HSTL outputs are implemented using two single-ended output buffers, which are programmed to have opposite polarity.

### External Clock Inputs

Each fast PLL supports single-ended or differential inputs for source synchronous transmitters or for general-purpose use. Source-synchronous receivers support differential clock inputs. The fast PLL inputs are fed by CLK [0..3], CLK [8..11], and FPLL [7..10] CLK pins, as shown in Figure 2–50 on page 2–85.

Table 2–22 shows the I/O standards supported by fast PLL input pins.

| Table 2–22. Fast PLL Port I/O Standards (Part 1 of 2) |       |              |  |  |

|-------------------------------------------------------|-------|--------------|--|--|

| L/O Chandard                                          | Input |              |  |  |

| I/O Standard                                          | INCLK | PLLENABLE    |  |  |

| LVTTL                                                 | ~     | $\checkmark$ |  |  |

| LVCMOS                                                | ~     | $\checkmark$ |  |  |

| 2.5 V                                                 | ~     |              |  |  |

| 1.8 V                                                 | ~     |              |  |  |

| 1.5 V                                                 | ~     |              |  |  |

| 3.3-V PCI                                             |       |              |  |  |

| 3.3-V PCI-X 1.0                                       |       |              |  |  |

| LVPECL                                                | ~     |              |  |  |

| 3.3-V PCML                                            | ~     |              |  |  |

| LVDS                                                  | ~     |              |  |  |

| HyperTransport technology                             | ~     |              |  |  |

| Differential HSTL                                     | ~     |              |  |  |

| Differential SSTL                                     |       |              |  |  |

| 3.3-V GTL                                             |       |              |  |  |

| 3.3-V GTL+                                            | ~     |              |  |  |

| 1.5-V HSTL Class I                                    | ~     |              |  |  |

| 1.5-V HSTL Class II                                   |       |              |  |  |

| 1.8-V HSTL Class I                                    | ~     |              |  |  |

| 1.8-V HSTL Class II                                   |       |              |  |  |

| SSTL-18 Class I                                       | ~     |              |  |  |

| SSTL-18 Class II                                      |       |              |  |  |

| SSTL-2 Class I                                        | ~     |              |  |  |

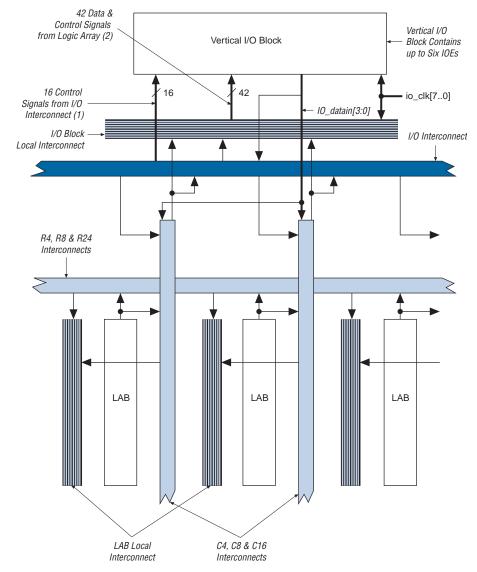

Figure 2–61. Column I/O Block Connection to the Interconnect

#### Notes to Figure 2–61:

- (1) The 16 control signals are composed of four output enables io\_boe[3..0], four clock enables io\_bce[3..0], four clocks io\_bclk[3..0], and four clear signals io\_bclr[3..0].

- (2) The 42 data and control signals consist of 12 data out lines; six lines each for DDR applications io\_dataouta[5..0] and io\_dataoutb[5..0], six output enables io\_coe[5..0], six input clock enables io\_cce\_in[5..0], six output clock enables io\_cce\_out[5..0], six clocks io\_cclk[5..0], and six clear signals io\_cclr[5..0].

and/or output enable registers. A programmable delay exists to increase the  $t_{ZX}$  delay to the output pin, which is required for ZBT interfaces. Table 2–24 shows the programmable delays for Stratix devices.

| Table 2–24. Stratix Programmable Delay Chain                                   |                                           |  |  |  |

|--------------------------------------------------------------------------------|-------------------------------------------|--|--|--|

| Programmable Delays                                                            | Quartus II Logic Option                   |  |  |  |

| Input pin to logic array delay                                                 | Decrease input delay to internal cells    |  |  |  |

| Input pin to input register delay                                              | Decrease input delay to input register    |  |  |  |

| Output pin delay Increase delay to output pin                                  |                                           |  |  |  |

| Output enable register t <sub>CO</sub> delay Increase delay to output enable p |                                           |  |  |  |

| Output t <sub>ZX</sub> delay                                                   | Increase $t_{ZX}$ delay to output pin     |  |  |  |

| Output clock enable delay                                                      | Increase output clock enable delay        |  |  |  |

| Input clock enable delay                                                       | Increase input clock enable delay         |  |  |  |

| Logic array to output register delay Decrease input delay to output register   |                                           |  |  |  |

| Output enable clock enable delay                                               | Increase output enable clock enable delay |  |  |  |

The IOE registers in Stratix devices share the same source for clear or preset. You can program preset or clear for each individual IOE. You can also program the registers to power up high or low after configuration is complete. If programmed to power up low, an asynchronous clear can control the registers. If programmed to power up high, an asynchronous preset can control the registers. This feature prevents the inadvertent activation of another device's active-low input upon power-up. If one register in an IOE uses a preset or clear signal then all registers in the IOE must use that same signal if they require preset or clear. Additionally a synchronous reset signal is available for the IOE registers.

## Double-Data Rate I/O Pins

Stratix devices have six registers in the IOE, which support DDR interfacing by clocking data on both positive and negative clock edges. The IOEs in Stratix devices support DDR inputs, DDR outputs, and bidirectional DDR modes.

When using the IOE for DDR inputs, the two input registers clock double rate input data on alternating edges. An input latch is also used within the IOE for DDR input acquisition. The latch holds the data that is present during the clock high times. This allows both bits of data to be synchronous with the same clock edge (either rising or falling). Figure 2–65 shows an IOE configured for DDR input. Figure 2–66 shows the DDR input timing diagram.

- 1.8-V HSTL Class I and II

- SSTL-3 Class I and II

- SSTL-2 Class I and II

- SSTL-18 Class I and II

- CTT

Table 2–31 describes the I/O standards supported by Stratix devices.

| I/O Standard                       | Туре               | Input Reference<br>Voltage (V <sub>REF</sub> )<br>(V) | Output Supply<br>Voltage (V <sub>CCIO</sub> )<br>(V) | Board<br>Termination<br>Voltage (V <sub>TT</sub> )<br>(V) |

|------------------------------------|--------------------|-------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------|

| LVTTL                              | Single-ended       | N/A                                                   | 3.3                                                  | N/A                                                       |

| LVCMOS                             | Single-ended       | N/A                                                   | 3.3                                                  | N/A                                                       |

| 2.5 V                              | Single-ended       | N/A                                                   | 2.5                                                  | N/A                                                       |

| 1.8 V                              | Single-ended       | N/A                                                   | 1.8                                                  | N/A                                                       |

| 1.5 V                              | Single-ended       | N/A                                                   | 1.5                                                  | N/A                                                       |

| 3.3-V PCI                          | Single-ended       | N/A                                                   | 3.3                                                  | N/A                                                       |

| 3.3-V PCI-X 1.0                    | Single-ended       | N/A                                                   | 3.3                                                  | N/A                                                       |

| LVDS                               | Differential       | N/A                                                   | 3.3                                                  | N/A                                                       |

| LVPECL                             | Differential       | N/A                                                   | 3.3                                                  | N/A                                                       |

| 3.3-V PCML                         | Differential       | N/A                                                   | 3.3                                                  | N/A                                                       |

| HyperTransport                     | Differential       | N/A                                                   | 2.5                                                  | N/A                                                       |

| Differential HSTL (1)              | Differential       | 0.75                                                  | 1.5                                                  | 0.75                                                      |

| Differential SSTL (2)              | Differential       | 1.25                                                  | 2.5                                                  | 1.25                                                      |

| GTL                                | Voltage-referenced | 0.8                                                   | N/A                                                  | 1.20                                                      |

| GTL+                               | Voltage-referenced | 1.0                                                   | N/A                                                  | 1.5                                                       |

| 1.5-V HSTL Class I and II          | Voltage-referenced | 0.75                                                  | 1.5                                                  | 0.75                                                      |

| 1.8-V HSTL Class I and II          | Voltage-referenced | 0.9                                                   | 1.8                                                  | 0.9                                                       |

| SSTL-18 Class I and II             | Voltage-referenced | 0.90                                                  | 1.8                                                  | 0.90                                                      |

| SSTL-2 Class I and II              | Voltage-referenced | 1.25                                                  | 2.5                                                  | 1.25                                                      |

| SSTL-3 Class I and II              | Voltage-referenced | 1.5                                                   | 3.3                                                  | 1.5                                                       |

| AGP (1 $\times$ and 2 $^{\circ}$ ) | Voltage-referenced | 1.32                                                  | 3.3                                                  | N/A                                                       |

| СТТ                                | Voltage-referenced | 1.5                                                   | 3.3                                                  | 1.5                                                       |

Notes to Table 2–31:

- (1) This I/O standard is only available on input and output clock pins.

- (2) This I/O standard is only available on output column clock pins.

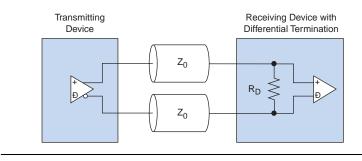

Figure 2–71. LVDS Input Differential On-Chip Termination

I/O banks on the left and right side of the device support LVDS receiver (far-end) differential termination.

Table 2–33 shows the Stratix device differential termination support.

| Table 2–33. Differential Termination Supported by I/O Banks                                                                |      |  |              |  |

|----------------------------------------------------------------------------------------------------------------------------|------|--|--------------|--|

| Differential Termination SupportI/O Standard SupportTop & Bottom<br>Banks (3, 4, 7 & 8)Left & Right Banks<br>(1, 2, 5 & 6) |      |  |              |  |

| Differential termination (1), (2)                                                                                          | LVDS |  | $\checkmark$ |  |

Notes to Table 2–33:

(1) Clock pin CLK0, CLK2, CLK9, CLK11, and pins FPLL [7..10] CLK do not support differential termination.

(2) Differential termination is only supported for LVDS because of a 3.3-V V<sub>CCIO</sub>.

Table 2–34 shows the termination support for different pin types.

| Table 2–34. Differential Termination Support Across Pin Types |                |  |  |

|---------------------------------------------------------------|----------------|--|--|

| Pin Type                                                      | R <sub>D</sub> |  |  |

| Top and bottom I/O banks (3, 4, 7, and 8)                     |                |  |  |

| DIFFIO_RX[]                                                   | $\checkmark$   |  |  |

| CLK[0,2,9,11],CLK[4-7],CLK[12-15]                             |                |  |  |

| CLK[1,3,8,10]                                                 | $\checkmark$   |  |  |

| FCLK                                                          |                |  |  |

| FPLL[710]CLK                                                  |                |  |  |

The differential on-chip resistance at the receiver input buffer is 118  $\Omega\pm 20$  %.

The Stratix device instruction register length is 10 bits and the USERCODE register length is 32 bits. Tables 3–2 and 3–3 show the boundary-scan register length and device IDCODE information for Stratix devices.

| Table 3–2. Stratix Boundary-Scan Register Length |                               |  |  |  |

|--------------------------------------------------|-------------------------------|--|--|--|

| Device                                           | Boundary-Scan Register Length |  |  |  |

| EP1S10                                           | 1,317                         |  |  |  |

| EP1S20                                           | 1,797                         |  |  |  |

| EP1S25                                           | 2,157                         |  |  |  |

| EP1S30                                           | 2,253                         |  |  |  |

| EP1S40                                           | 2,529                         |  |  |  |

| EP1S60                                           | 3,129                         |  |  |  |

| EP1S80                                           | 3,777                         |  |  |  |

| Table 3–3. 32-Bit Stratix Device IDCODE |                  |                             |                                    |                 |  |  |

|-----------------------------------------|------------------|-----------------------------|------------------------------------|-----------------|--|--|

|                                         |                  | <b>IDCODE (32 Bits)</b> (1) |                                    |                 |  |  |

| Device                                  | Version (4 Bits) | Part Number (16 Bits)       | Manufacturer Identity<br>(11 Bits) | LSB (1 Bit) (2) |  |  |

| EP1S10                                  | 0000             | 0010 0000 0000 0001         | 000 0110 1110                      | 1               |  |  |

| EP1S20                                  | 0000             | 0010 0000 0000 0010         | 000 0110 1110                      | 1               |  |  |

| EP1S25                                  | 0000             | 0010 0000 0000 0011         | 000 0110 1110                      | 1               |  |  |

| EP1S30                                  | 0000             | 0010 0000 0000 0100         | 000 0110 1110                      | 1               |  |  |

| EP1S40                                  | 0000             | 0010 0000 0000 0101         | 000 0110 1110                      | 1               |  |  |

| EP1S60                                  | 0000             | 0010 0000 0000 0110         | 000 0110 1110                      | 1               |  |  |

| EP1S80                                  | 0000             | 0010 0000 0000 0111         | 000 0110 1110                      | 1               |  |  |

Notes to Tables 3–2 and 3–3:

(1) The most significant bit (MSB) is on the left.

(2) The IDCODE's least significant bit (LSB) is always 1.

# 4. DC & Switching Characteristics

### S51004-3.4

## Operating Conditions

Stratix<sup>®</sup> devices are offered in both commercial and industrial grades. Industrial devices are offered in -6 and -7 speed grades and commercial devices are offered in -5 (fastest), -6, -7, and -8 speed grades. This section specifies the operation conditions for operating junction temperature,  $V_{CCINT}$  and  $V_{CCIO}$  voltage levels, and input voltage requirements. The voltage specifications in this section are specified at the pins of the device (and not the power supply). If the device operates outside these ranges, then all DC and AC specifications are not guaranteed. Furthermore, the reliability of the device may be affected. The timing parameters in this chapter apply to both commercial and industrial temperature ranges unless otherwise stated.

Tables 4–1 through 4–8 provide information on absolute maximum ratings.

| Table 4–1. Stratix Device Absolute Maximum Ratings Notes (1), (2) |                            |                         |         |         |      |  |

|-------------------------------------------------------------------|----------------------------|-------------------------|---------|---------|------|--|

| Symbol                                                            | Parameter                  | Conditions              | Minimum | Maximum | Unit |  |

| V <sub>CCINT</sub>                                                | Supply voltage             | With respect to ground  | -0.5    | 2.4     | V    |  |

| V <sub>CCIO</sub>                                                 | -                          |                         | -0.5    | 4.6     | V    |  |

| VI                                                                | DC input voltage (3)       |                         | -0.5    | 4.6     | V    |  |

| I <sub>OUT</sub>                                                  | DC output current, per pin |                         | -25     | 40      | mA   |  |

| T <sub>STG</sub>                                                  | Storage temperature        | No bias                 | -65     | 150     | °C   |  |

| TJ                                                                | Junction temperature       | BGA packages under bias |         | 135     | °C   |  |

| Table 4–2. Stratix Device Recommended Operating Conditions (Part 1 of 2) |                                                     |     |       |       |      |  |

|--------------------------------------------------------------------------|-----------------------------------------------------|-----|-------|-------|------|--|

| Symbol Parameter Conditions Minimum Maximum Ur                           |                                                     |     |       |       | Unit |  |

| V <sub>CCINT</sub>                                                       | Supply voltage for internal logic and input buffers | (4) | 1.425 | 1.575 | V    |  |

device. Decoupling capacitors were not used in this measurement. To factor in the current for decoupling capacitors, sum up the current for each capacitor using the following equation:

I = C (dV/dt)

If the regulator or power supply minimum output current is more than the Stratix device requires, then the device may consume more current than the maximum current listed in Table 4–34. However, the device does not require any more current to successfully power up than what is listed in Table 4–34.

| Table 4–34. Stratix Power-Up Current (I <sub>CCINT</sub> ) Requirements Note (1) |                |         |        |  |  |

|----------------------------------------------------------------------------------|----------------|---------|--------|--|--|

| Device                                                                           | Power-Up Curre | Unit    |        |  |  |

|                                                                                  | Typical        | Maximum | — Unit |  |  |

| EP1S10                                                                           | 250            | 700     | mA     |  |  |

| EP1S20                                                                           | 400            | 1,200   | mA     |  |  |

| EP1S25                                                                           | 500            | 1,500   | mA     |  |  |

| EP1S30                                                                           | 550            | 1,900   | mA     |  |  |

| EP1S40                                                                           | 650            | 2,300   | mA     |  |  |

| EP1S60                                                                           | 800            | 2,600   | mA     |  |  |

| EP1S80                                                                           | 1,000          | 3,000   | mA     |  |  |

Note to Table 4–34:

(1) The maximum test conditions are for  $0^{\circ}$  C and typical test conditions are for  $40^{\circ}$  C.

The exact amount of current consumed varies according to the process, temperature, and power ramp rate. Stratix devices typically require less current during power up than shown in Table 4–34. The user-mode current during device operation is generally higher than the power-up current.

The duration of the  $I_{CCINT}$  power-up requirement depends on the  $V_{CCINT}$  voltage supply rise time. The power-up current consumption drops when the  $V_{CCINT}$  supply reaches approximately 0.75 V.

Tables 4–91 through 4–96 show the external timing parameters on column and row pins for EP1S80 devices.

| Table 4–91. EP1S80 External I/O Timing on Column Pins Using Fast Regional Clock Networks Note (1) |                |       |                |       |                |       | e (1)          |     |      |

|---------------------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-----|------|

|                                                                                                   | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |     | 11   |

| Parameter                                                                                         | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max | Unit |

| t <sub>INSU</sub>                                                                                 | 2.328          |       | 2.528          |       | 2.900          |       | NA             |     | ns   |

| t <sub>INH</sub>                                                                                  | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns   |

| t <sub>OUTCO</sub>                                                                                | 2.422          | 4.830 | 2.422          | 5.169 | 2.422          | 5.633 | NA             | NA  | ns   |

| t <sub>xz</sub>                                                                                   | 2.362          | 4.704 | 2.362          | 5.037 | 2.362          | 5.509 | NA             | NA  | ns   |

| t <sub>ZX</sub>                                                                                   | 2.362          | 4.704 | 2.362          | 5.037 | 2.362          | 5.509 | NA             | NA  | ns   |

| Table 4–92. I         | Table 4–92. EP1S80 External I/O Timing on Column Pins Using Regional Clock Networks Note (1) |       |                |       |                |       |                |     |      |

|-----------------------|----------------------------------------------------------------------------------------------|-------|----------------|-------|----------------|-------|----------------|-----|------|

| Parameter             | -5 Speed Grade                                                                               |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |     |      |

|                       | Min                                                                                          | Max   | Min            | Max   | Min            | Max   | Min            | Max | Unit |

| t <sub>INSU</sub>     | 1.760                                                                                        |       | 1.912          |       | 2.194          |       | NA             |     | ns   |

| t <sub>INH</sub>      | 0.000                                                                                        |       | 0.000          |       | 0.000          |       | NA             |     | ns   |

| t <sub>outco</sub>    | 2.761                                                                                        | 5.398 | 2.761          | 5.785 | 2.761          | 6.339 | NA             | NA  | ns   |

| t <sub>xz</sub>       | 2.701                                                                                        | 5.272 | 2.701          | 5.653 | 2.701          | 6.215 | NA             | NA  | ns   |

| t <sub>ZX</sub>       | 2.701                                                                                        | 5.272 | 2.701          | 5.653 | 2.701          | 6.215 | NA             | NA  | ns   |

| t <sub>INSUPLL</sub>  | 0.462                                                                                        |       | 0.606          |       | 0.785          |       | NA             |     | ns   |

| t <sub>INHPLL</sub>   | 0.000                                                                                        |       | 0.000          |       | 0.000          |       | NA             |     | ns   |

| t <sub>OUTCOPLL</sub> | 1.661                                                                                        | 2.849 | 1.661          | 2.859 | 1.661          | 2.881 | NA             | NA  | ns   |

| t <sub>XZPLL</sub>    | 1.601                                                                                        | 2.723 | 1.601          | 2.727 | 1.601          | 2.757 | NA             | NA  | ns   |

| t <sub>ZXPLL</sub>    | 1.601                                                                                        | 2.723 | 1.601          | 2.727 | 1.601          | 2.757 | NA             | NA  | ns   |

# PLL Specifications

Tables 4–127 through 4–129 describe the Stratix device enhanced PLL specifications.

| Symbol                   | Parameter                                                                                                             | Min           | Тур | Max                                                                      | Unit         |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------|-----|--------------------------------------------------------------------------|--------------|

| f <sub>IN</sub>          | Input clock frequency                                                                                                 | 3<br>(1), (2) |     | 684                                                                      | MHz          |

| f <sub>INPFD</sub>       | Input frequency to PFD                                                                                                | 3             |     | 420                                                                      | MHz          |

| f <sub>INDUTY</sub>      | Input clock duty cycle                                                                                                | 40            |     | 60                                                                       | %            |

| f <sub>EINDUTY</sub>     | External feedback clock input duty cycle                                                                              | 40            |     | 60                                                                       | %            |

| t <sub>INJITTER</sub>    | Input clock period jitter                                                                                             |               |     | ±200 <i>(3)</i>                                                          | ps           |

| t <sub>EINJITTER</sub>   | External feedback clock period jitter                                                                                 |               |     | ±200 (3)                                                                 | ps           |

| t <sub>FCOMP</sub>       | External feedback clock compensation time (4)                                                                         |               |     | 6                                                                        | ns           |

| f <sub>OUT</sub>         | Output frequency for internal global<br>or regional clock                                                             |               |     | 500                                                                      | MHz          |

| f <sub>OUT_EXT</sub>     | Output frequency for external clock (3)                                                                               | 0.3           |     | 526                                                                      | MHz          |

| toutduty                 | Duty cycle for external clock output (when set to 50%)                                                                | 45            |     | 55                                                                       | %            |

| t <sub>JITTER</sub>      | Period jitter for external clock output (6)                                                                           |               |     | <pre>±100 ps for &gt;200-MHz outclk ±20 mUI for &lt;200-MHz outclk</pre> | ps or<br>mUI |

| t <sub>CONFIG5,6</sub>   | Time required to reconfigure the scan chains for PLLs 5 and 6                                                         |               |     | 289/f <sub>SCANCLK</sub>                                                 |              |

| t <sub>CONFIG11,12</sub> | Time required to reconfigure the scan chains for PLLs 11 and 12                                                       |               |     | 193/f <sub>SCANCLK</sub>                                                 |              |

| t <sub>SCANCLK</sub>     | scanclk frequency (5)                                                                                                 |               |     | 22                                                                       | MHz          |

| t <sub>DLOCK</sub>       | Time required to lock dynamically<br>(after switchover or reconfiguring<br>any non-post-scale<br>counters/delays) (7) |               |     | 100                                                                      | μs           |

| t <sub>LOCK</sub>        | Time required to lock from end of device configuration                                                                | 10            |     | 400                                                                      | μs           |

| f <sub>VCO</sub>         | PLL internal VCO operating range                                                                                      | 300           |     | 800 (8)                                                                  | MHz          |

| t <sub>LSKEW</sub>       | Clock skew between two external<br>clock outputs driven by the same<br>counter                                        |               | ±50 |                                                                          | ps           |

process and operating conditions. Run the timing analyzer in the Quartus II software at the fast and slow operating conditions to see the phase shift range that is achieved below these frequencies.

| Table 4–135. Stratix DLL Low Frequency Limit for Full Phase Shift |                                           |      |  |  |  |

|-------------------------------------------------------------------|-------------------------------------------|------|--|--|--|

| Phase Shift                                                       | Minimum Frequency for<br>Full Phase Shift | Unit |  |  |  |

| 72°                                                               | 119                                       | MHz  |  |  |  |

| 90°                                                               | 149                                       | MHz  |  |  |  |

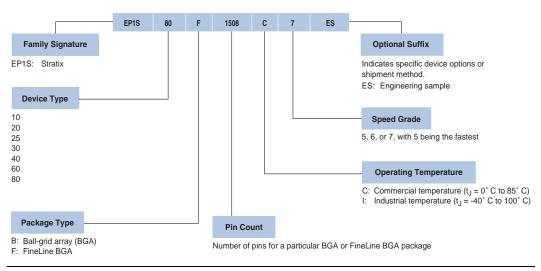

Figure 5–1. Stratix Device Packaging Ordering Information