# E·XFL

#### Altera - EP1S30F780C5N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Active                                                     |

| Number of LABs/CLBs            | 3247                                                       |

| Number of Logic Elements/Cells | 32470                                                      |

| Total RAM Bits                 | 3317184                                                    |

| Number of I/O                  | 597                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.425V ~ 1.575V                                            |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 780-BBGA, FCBGA                                            |

| Supplier Device Package        | 780-FBGA (29x29)                                           |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=ep1s30f780c5n |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

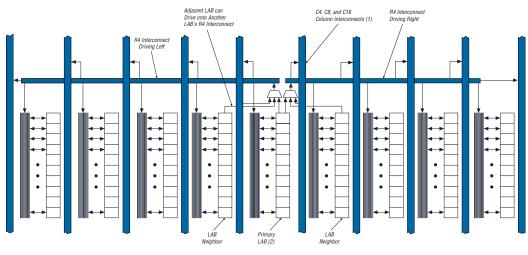

### Clear & Preset Logic Control

LAB-wide signals control the logic for the register's clear and preset signals. The LE directly supports an asynchronous clear and preset function. The register preset is achieved through the asynchronous load of a logic high. The direct asynchronous preset does not require a NOTgate push-back technique. Stratix devices support simultaneous preset/ row connections in a four-LAB region. Every LAB has its own set of R4 interconnects to drive either left or right. Figure 2–9 shows R4 interconnect connections from an LAB. R4 interconnects can drive and be driven by DSP blocks and RAM blocks and horizontal IOEs. For LAB interfacing, a primary LAB or LAB neighbor can drive a given R4 interconnect. For R4 interconnects that drive to the right, the primary LAB and right neighbor can drive on to the interconnect. For R4 interconnects can drive other R4 interconnects that drive to the left, the primary LAB and its left neighbor can drive on to the interconnects can drive other R4 interconnects to extend the range of LABs they can drive. R4 interconnects can also drive C4 and C16 interconnects for connections from one row to another. Additionally, R4 interconnects can drive R24 interconnects.

Notes to Figure 2–9:

(1) C4 interconnects can drive R4 interconnects.

(2) This pattern is repeated for every LAB in the LAB row.

The R8 interconnects span eight LABs, M512 or M4K RAM blocks, or DSP blocks to the right or left from a source LAB. These resources are used for fast row connections in an eight-LAB region. Every LAB has its own set of R8 interconnects to drive either left or right. R8 interconnect connections between LABs in a row are similar to the R4 connections shown in Figure 2–9, with the exception that they connect to eight LABs to the right or left, not four. Like R4 interconnects, R8 interconnects can drive and be driven by all types of architecture blocks. R8 interconnects

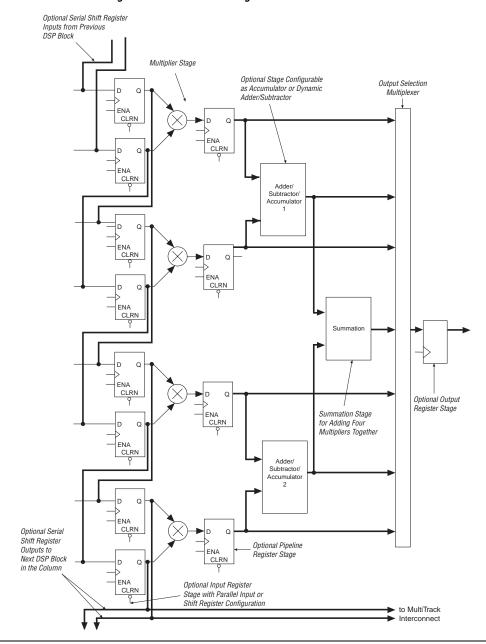

#### Figure 2–30. DSP Block Diagram for 18 × 18-Bit Configuration

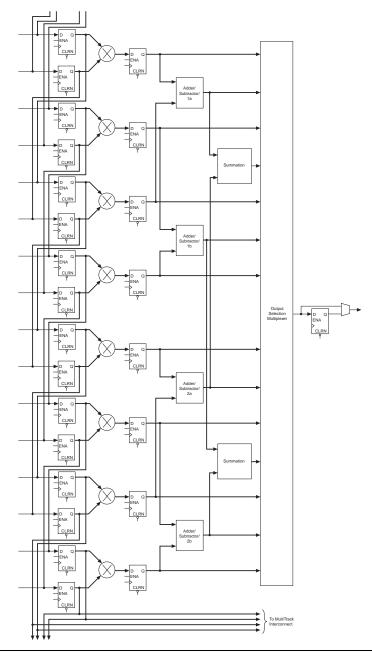

Figure 2–31. DSP Block Diagram for  $9 \times 9$ -Bit Configuration

2–56

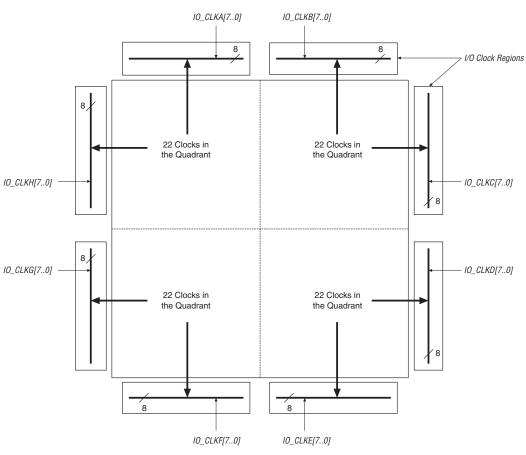

Figure 2–47. EP1S10, EP1S20 & EP1S25 Device I/O Clock Groups

Any of the four external output counters can drive the single-ended or differential clock outputs for PLLs 5 and 6. This means one counter or frequency can drive all output pins available from PLL 5 or PLL 6. Each pair of output pins (four pins total) has dedicated VCC and GND pins to reduce the output clock's overall jitter by providing improved isolation from switching I/O pins.

For PLLs 5 and 6, each pin of a single-ended output pair can either be in phase or 180° out of phase. The clock output pin pairs support the same I/O standards as standard output pins (in the top and bottom banks) as well as LVDS, LVPECL, 3.3-V PCML, HyperTransport technology, differential HSTL, and differential SSTL. Table 2–20 shows which I/O standards the enhanced PLL clock pins support. When in single-ended or differential mode, the two outputs operate off the same power supply. Both outputs use the same standards in single-ended mode to maintain performance. You can also use the external clock output pins as user output pins if external enhanced PLL clocking is not needed.

| Table 2–20. I/O Standards Supported for Enhanced PLL Pins (Part 1 of 2) |                      |              |              |              |  |  |  |  |

|-------------------------------------------------------------------------|----------------------|--------------|--------------|--------------|--|--|--|--|

| L/O Standard                                                            |                      | Output       |              |              |  |  |  |  |

| I/O Standard                                                            | INCLK                | FBIN         | PLLENABLE    | EXTCLK       |  |  |  |  |

| LVTTL                                                                   | $\checkmark$         | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |  |  |  |

| LVCMOS                                                                  | ~                    | $\checkmark$ | ~            | $\checkmark$ |  |  |  |  |

| 2.5 V                                                                   | ~                    | $\checkmark$ |              | $\checkmark$ |  |  |  |  |

| 1.8 V                                                                   | ~                    | $\checkmark$ |              | $\checkmark$ |  |  |  |  |

| 1.5 V                                                                   | ~                    | $\checkmark$ |              | $\checkmark$ |  |  |  |  |

| 3.3-V PCI                                                               | ~                    | $\checkmark$ |              | $\checkmark$ |  |  |  |  |

| 3.3-V PCI-X 1.0                                                         | ~                    | $\checkmark$ |              | $\checkmark$ |  |  |  |  |

| LVPECL                                                                  | ~                    | $\checkmark$ |              | $\checkmark$ |  |  |  |  |

| 3.3-V PCML                                                              | ~                    | $\checkmark$ |              | $\checkmark$ |  |  |  |  |

| LVDS                                                                    | ~                    | $\checkmark$ |              | $\checkmark$ |  |  |  |  |

| HyperTransport technology                                               | <ul> <li></li> </ul> | $\checkmark$ |              | $\checkmark$ |  |  |  |  |

| Differential HSTL                                                       | ~                    |              |              | $\checkmark$ |  |  |  |  |

| Differential SSTL                                                       |                      |              |              | $\checkmark$ |  |  |  |  |

| 3.3-V GTL                                                               | <ul> <li></li> </ul> | $\checkmark$ |              | $\checkmark$ |  |  |  |  |

| 3.3-V GTL+                                                              | <ul> <li></li> </ul> | $\checkmark$ |              | $\checkmark$ |  |  |  |  |

| 1.5-V HSTL Class I                                                      | <ul> <li></li> </ul> | $\checkmark$ |              | $\checkmark$ |  |  |  |  |

The pllenable pin is a dedicated pin that enables/disables PLLs. When the pllenable pin is low, the clock output ports are driven by GND and all the PLLs go out of lock. When the pllenable pin goes high again, the PLLs relock and resynchronize to the input clocks. You can choose which PLLs are controlled by the pllenable signal by connecting the pllenable input port of the altpll megafunction to the common pllenable input pin.

The areset signals are reset/resynchronization inputs for each PLL. The areset signal should be asserted every time the PLL loses lock to guarantee correct phase relationship between the PLL output clocks. Users should include the areset signal in designs if any of the following conditions are true:

- PLL Reconfiguration or Clock switchover enables in the design.

- Phase relationships between output clocks need to be maintained after a loss of lock condition

The device input pins or logic elements (LEs) can drive these input signals. When driven high, the PLL counters will reset, clearing the PLL output and placing the PLL out of lock. The VCO will set back to its nominal setting (~700 MHz). When driven low again, the PLL will resynchronize to its input as it relocks. If the target VCO frequency is below this nominal frequency, then the output frequency will start at a higher value than desired as the PLL locks. If the system cannot tolerate this, the clkena signal can disable the output clocks until the PLL locks.

The pfdena signals control the phase frequency detector (PFD) output with a programmable gate. If you disable the PFD, the VCO operates at its last set value of control voltage and frequency with some long-term drift to a lower frequency. The system continues running when the PLL goes out of lock or the input clock is disabled. By maintaining the last locked frequency, the system has time to store its current settings before shutting down. You can either use your own control signal or a clkloss status signal to trigger pfdena.

The clkena signals control the enhanced PLL regional and global outputs. Each regional and global output port has its own clkena signal. The clkena signals synchronously disable or enable the clock at the PLL output port by gating the outputs of the *g* and *l* counters. The clkena signals are registered on the falling edge of the counter output clock to enable or disable the clock without glitches. Figure 2–57 shows the waveform example for a PLL clock port enable. The PLL can remain locked independent of the clkena signals since the loop-related counters are not affected. This feature is useful for applications that require a low power or sleep mode. Upon re-enabling, the PLL does not need a

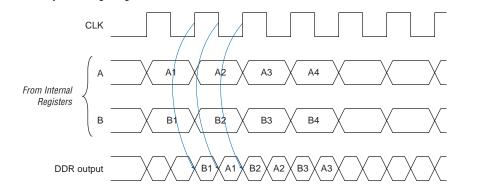

Figure 2–68. Output Timing Diagram in DDR Mode

The Stratix IOE operates in bidirectional DDR mode by combining the DDR input and DDR output configurations. Stratix device I/O pins transfer data on a DDR bidirectional bus to support DDR SDRAM. The negative-edge-clocked OE register holds the OE signal inactive until the falling edge of the clock. This is done to meet DDR SDRAM timing requirements.

#### **External RAM Interfacing**

Stratix devices support DDR SDRAM at up to 200 MHz (400-Mbps data rate) through dedicated phase-shift circuitry, QDR and QDRII SRAM interfaces up to 167 MHz, and ZBT SRAM interfaces up to 200 MHz. Stratix devices also provide preliminary support for reduced latency DRAM II (RLDRAM II) at rates up to 200 MHz through the dedicated phase-shift circuitry.

In addition to the required signals for external memory interfacing, Stratix devices offer the optional clock enable signal. By default the Quartus II software sets the clock enable signal high, which tells the output register to update with new values. The output registers hold their own values if the design sets the clock enable signal low. See Figure 2–64.

To find out more about the DDR SDRAM specification, see the JEDEC web site (**www.jedec.org**). For information on memory controller megafunctions for Stratix devices, see the Altera web site (**www.altera.com**). See AN 342: Interfacing DDR SDRAM with Stratix & Stratix GX Devices for more information on DDR SDRAM interface in Stratix. Also see AN 349: QDR SRAM Controller Reference Design for Stratix & Stratix GX Devices and AN 329: ZBT SRAM Controller Reference Design for Stratix & Stratix GX Devices.

- 1.8-V HSTL Class I and II

- SSTL-3 Class I and II

- SSTL-2 Class I and II

- SSTL-18 Class I and II

- CTT

Table 2–31 describes the I/O standards supported by Stratix devices.

| I/O Standard                       | Туре               | Input Reference<br>Voltage (V <sub>REF</sub> )<br>(V) | Output Supply<br>Voltage (V <sub>CCIO</sub> )<br>(V) | Board<br>Termination<br>Voltage (V <sub>TT</sub> )<br>(V) |

|------------------------------------|--------------------|-------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------|

| LVTTL                              | Single-ended       | N/A                                                   | 3.3                                                  | N/A                                                       |

| LVCMOS                             | Single-ended       | N/A                                                   | 3.3                                                  | N/A                                                       |

| 2.5 V                              | Single-ended       | N/A                                                   | 2.5                                                  | N/A                                                       |

| 1.8 V                              | Single-ended       | N/A                                                   | 1.8                                                  | N/A                                                       |

| 1.5 V                              | Single-ended       | N/A                                                   | 1.5                                                  | N/A                                                       |

| 3.3-V PCI                          | Single-ended       | N/A                                                   | 3.3                                                  | N/A                                                       |

| 3.3-V PCI-X 1.0                    | Single-ended       | N/A                                                   | 3.3                                                  | N/A                                                       |

| LVDS                               | Differential       | N/A                                                   | 3.3                                                  | N/A                                                       |

| LVPECL                             | Differential       | N/A                                                   | 3.3                                                  | N/A                                                       |

| 3.3-V PCML                         | Differential       | N/A                                                   | 3.3                                                  | N/A                                                       |

| HyperTransport                     | Differential       | N/A                                                   | 2.5                                                  | N/A                                                       |

| Differential HSTL (1)              | Differential       | 0.75                                                  | 1.5                                                  | 0.75                                                      |

| Differential SSTL (2)              | Differential       | 1.25                                                  | 2.5                                                  | 1.25                                                      |

| GTL                                | Voltage-referenced | 0.8                                                   | N/A                                                  | 1.20                                                      |

| GTL+                               | Voltage-referenced | 1.0                                                   | N/A                                                  | 1.5                                                       |

| 1.5-V HSTL Class I and II          | Voltage-referenced | 0.75                                                  | 1.5                                                  | 0.75                                                      |

| 1.8-V HSTL Class I and II          | Voltage-referenced | 0.9                                                   | 1.8                                                  | 0.9                                                       |

| SSTL-18 Class I and II             | Voltage-referenced | 0.90                                                  | 1.8                                                  | 0.90                                                      |

| SSTL-2 Class I and II              | Voltage-referenced | 1.25                                                  | 2.5                                                  | 1.25                                                      |

| SSTL-3 Class I and II              | Voltage-referenced | 1.5                                                   | 3.3                                                  | 1.5                                                       |

| AGP (1 $\times$ and 2 $^{\circ}$ ) | Voltage-referenced | 1.32                                                  | 3.3                                                  | N/A                                                       |

| СТТ                                | Voltage-referenced | 1.5                                                   | 3.3                                                  | 1.5                                                       |

Notes to Table 2–31:

- (1) This I/O standard is only available on input and output clock pins.

- (2) This I/O standard is only available on output column clock pins.

The output levels are compatible with systems of the same voltage as the power supply (i.e., when VCCIO pins are connected to a 1.5-V power supply, the output levels are compatible with 1.5-V systems). When VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3 V and is compatible with 3.3-V or 5.0-V systems.

Table 2-36 summarizes Stratix MultiVolt I/O support.

| Table 2–36. Stratix MultiVolt I/O Support Note (1) |                         |              |                         |                         |                         |                   |                         |              |              |              |

|----------------------------------------------------|-------------------------|--------------|-------------------------|-------------------------|-------------------------|-------------------|-------------------------|--------------|--------------|--------------|

| V (V)                                              |                         | Inp          | ut Signal               | (5)                     |                         | Output Signal (6) |                         |              |              |              |

| V <sub>ccio</sub> (V)                              | 1.5 V                   | 1.8 V        | 2.5 V                   | 3.3 V                   | 5.0 V                   | 1.5 V             | 1.8 V                   | 2.5 V        | 3.3 V        | 5.0 V        |

| 1.5                                                | $\checkmark$            | $\checkmark$ | <ul><li>✓ (2)</li></ul> | <ul><li>✓ (2)</li></ul> |                         | ~                 |                         |              |              |              |

| 1.8                                                | <ul><li>✓ (2)</li></ul> | ~            | <ul><li>✓ (2)</li></ul> | <ul><li>✓ (2)</li></ul> |                         | 🗸 (3)             | $\checkmark$            |              |              |              |

| 2.5                                                |                         |              | ~                       | $\checkmark$            |                         | 🗸 (3)             | 🗸 (3)                   | $\checkmark$ |              |              |

| 3.3                                                |                         |              | <ul> <li>(2)</li> </ul> | ~                       | <ul><li>✓ (4)</li></ul> | 🗸 (3)             | <ul><li>✓ (3)</li></ul> | 🗸 (3)        | $\checkmark$ | $\checkmark$ |

Notes to Table 2–36:

(1) To drive inputs higher than  $V_{CCIO}$  but less than 4.1 V, disable the PCI clamping diode. However, to drive 5.0-V inputs to the device, enable the PCI clamping diode to prevent  $V_1$  from rising above 4.0 V.

- (2) The input pin current may be slightly higher than the typical value.

- (3) Although V<sub>CCIO</sub> specifies the voltage necessary for the Stratix device to drive out, a receiving device powered at a different level can still interface with the Stratix device if it has inputs that tolerate the V<sub>CCIO</sub> value.

- (4) Stratix devices can be 5.0-V tolerant with the use of an external resistor and the internal PCI clamp diode.

- (5) This is the external signal that is driving the Stratix device.

- (6) This represents the system voltage that Stratix supports when a VCCIO pin is connected to a specific voltage level. For example, when VCCIO is 3.3 V and if the I/O standard is LVTTL/LVCMOS, the output high of the signal coming out from Stratix is 3.3 V and is compatible with 3.3-V or 5.0-V systems.

## High-Speed Differential I/O Support

Stratix devices contain dedicated circuitry for supporting differential standards at speeds up to 840 Mbps. The following differential I/O standards are supported in the Stratix device: LVDS, LVPECL, HyperTransport, and 3.3-V PCML.

There are four dedicated high-speed PLLs in the EP1S10 to EP1S25 devices and eight dedicated high-speed PLLs in the EP1S30 to EP1S80 devices to multiply reference clocks and drive high-speed differential SERDES channels.

See the Stratix device pin-outs at **www.altera.com** for additional high speed DIFFIO pin information for Stratix devices.

| Table 2–39            | Table 2–39. EP1S40 Differential Channels (Part 2 of 2) Note (1) |                |                     |           |                  |           |           |                           |           |           |        |

|-----------------------|-----------------------------------------------------------------|----------------|---------------------|-----------|------------------|-----------|-----------|---------------------------|-----------|-----------|--------|

|                       | Transmitter/                                                    | Total          | Total Maximum       |           | Center Fast PLLs |           |           | Corner Fast PLLs (2), (3) |           |           |        |

| Package               | Receiver                                                        | Channels       | Speed<br>(Mbps)     | PLL1      | PLL2             | PLL3      | PLL4      | PLL7                      | PLL8      | PLL9      | PLL10  |

| 956-pin               | Transmitter                                                     | 80             | 840                 | 18        | 17               | 17        | 18        | 20                        | 20        | 20        | 20     |

| BGA                   | (4)                                                             |                | 840 (5)             | 35        | 35               | 35        | 35        | 20                        | 20        | 20        | 20     |

|                       | Receiver                                                        | 80             | 840                 | 20        | 20               | 20        | 20        | 18                        | 17        | 17        | 18     |

|                       |                                                                 | 840 (5)        | 40                  | 40        | 40               | 40        | 18        | 17                        | 17        | 18        |        |

| 1,020-pin<br>FineLine | Transmitter (4)                                                 | 80 (10)<br>(7) | 840                 | 18<br>(2) | 17<br>(3)        | 17<br>(3) | 18<br>(2) | 20                        | 20        | 20        | 20     |

| BGA                   |                                                                 |                | 840 <i>(5), (8)</i> | 35<br>(5) | 35<br>(5)        | 35<br>(5) | 35<br>(5) | 20                        | 20        | 20        | 20     |

|                       | Receiver                                                        | 80 (10)<br>(7) | 840                 | 20        | 20               | 20        | 20        | 18<br>(2)                 | 17<br>(3) | 17<br>(3) | 18 (2) |

|                       |                                                                 |                | 840 <i>(5), (8)</i> | 40        | 40               | 40        | 40        | 18<br>(2)                 | 17<br>(3) | 17<br>(3) | 18 (2) |

| 1,508-pin<br>FineLine | Transmitter (4)                                                 | 80 (10)<br>(7) | 840                 | 18<br>(2) | 17<br>(3)        | 17<br>(3) | 18<br>(2) | 20                        | 20        | 20        | 20     |

| BGA                   |                                                                 |                | 840 <i>(5), (8)</i> | 35<br>(5) | 35<br>(5)        | 35<br>(5) | 35<br>(5) | 20                        | 20        | 20        | 20     |

|                       | Receiver                                                        | 80 (10)<br>(7) | 840                 | 20        | 20               | 20        | 20        | 18<br>(2)                 | 17<br>(3) | 17<br>(3) | 18 (2) |

|                       |                                                                 |                | 840 <i>(5), (8)</i> | 40        | 40               | 40        | 40        | 18<br>(2)                 | 17<br>(3) | 17<br>(3) | 18 (2) |

| Table 2–40. EP1S60 Differential Channels (Part 1 of 2) Note (1) |                |                |                     |      |      |      |      |                          |      |      |          |

|-----------------------------------------------------------------|----------------|----------------|---------------------|------|------|------|------|--------------------------|------|------|----------|

| Destroye                                                        | Transmitter/   | Total          | Maximum             |      |      |      | .s   | Corner Fast PLLs (2), (3 |      |      | (2), (3) |

| Packano                                                         | Receiver       | Channels       | Speed<br>(Mbps)     | PLL1 | PLL2 | PLL3 | PLL4 | PLL7                     | PLL8 | PLL9 | PLL10    |

| 956-pin                                                         | Transmitter 80 | Transmitter 80 | 840                 | 12   | 10   | 10   | 12   | 20                       | 20   | 20   | 20       |

| BGA                                                             | (4)            |                | 840 (5), (8)        | 22   | 22   | 22   | 22   | 20                       | 20   | 20   | 20       |

|                                                                 | Receiver 80    | 80             | 840                 | 20   | 20   | 20   | 20   | 12                       | 10   | 10   | 12       |

|                                                                 |                |                | 840 <i>(5), (8)</i> | 40   | 40   | 40   | 40   | 12                       | 10   | 10   | 12       |

The Stratix device instruction register length is 10 bits and the USERCODE register length is 32 bits. Tables 3–2 and 3–3 show the boundary-scan register length and device IDCODE information for Stratix devices.

| Table 3–2. Stratix Boundary-Scan Register Length |                               |  |  |  |  |  |

|--------------------------------------------------|-------------------------------|--|--|--|--|--|

| Device                                           | Boundary-Scan Register Length |  |  |  |  |  |

| EP1S10                                           | 1,317                         |  |  |  |  |  |

| EP1S20                                           | 1,797                         |  |  |  |  |  |

| EP1S25                                           | 2,157                         |  |  |  |  |  |

| EP1S30                                           | 2,253                         |  |  |  |  |  |

| EP1S40                                           | 2,529                         |  |  |  |  |  |

| EP1S60                                           | 3,129                         |  |  |  |  |  |

| EP1S80                                           | 3,777                         |  |  |  |  |  |

| Table 3–3            | Table 3–3. 32-Bit Stratix Device IDCODE |                       |                                    |                 |  |  |  |  |  |

|----------------------|-----------------------------------------|-----------------------|------------------------------------|-----------------|--|--|--|--|--|

| IDCODE (32 Bits) (1) |                                         |                       |                                    |                 |  |  |  |  |  |

| Device               | Version (4 Bits)                        | Part Number (16 Bits) | Manufacturer Identity<br>(11 Bits) | LSB (1 Bit) (2) |  |  |  |  |  |

| EP1S10               | 0000                                    | 0010 0000 0000 0001   | 000 0110 1110                      | 1               |  |  |  |  |  |

| EP1S20               | 0000                                    | 0010 0000 0000 0010   | 000 0110 1110                      | 1               |  |  |  |  |  |

| EP1S25               | 0000                                    | 0010 0000 0000 0011   | 000 0110 1110                      | 1               |  |  |  |  |  |

| EP1S30               | 0000                                    | 0010 0000 0000 0100   | 000 0110 1110                      | 1               |  |  |  |  |  |

| EP1S40               | 0000                                    | 0010 0000 0000 0101   | 000 0110 1110                      | 1               |  |  |  |  |  |

| EP1S60               | 0000                                    | 0010 0000 0000 0110   | 000 0110 1110                      | 1               |  |  |  |  |  |

| EP1S80               | 0000                                    | 0010 0000 0000 0111   | 000 0110 1110                      | 1               |  |  |  |  |  |

Notes to Tables 3–2 and 3–3:

(1) The most significant bit (MSB) is on the left.

(2) The IDCODE's least significant bit (LSB) is always 1.

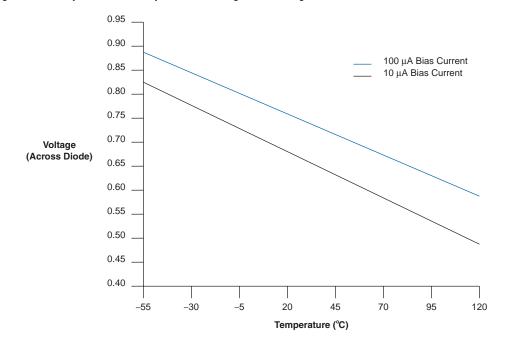

The temperature-sensing diode works for the entire operating range shown in Figure 3–6.

Figure 3–6. Temperature vs. Temperature-Sensing Diode Voltage

## 4. DC & Switching Characteristics

#### S51004-3.4

## Operating Conditions

Stratix<sup>®</sup> devices are offered in both commercial and industrial grades. Industrial devices are offered in -6 and -7 speed grades and commercial devices are offered in -5 (fastest), -6, -7, and -8 speed grades. This section specifies the operation conditions for operating junction temperature,  $V_{CCINT}$  and  $V_{CCIO}$  voltage levels, and input voltage requirements. The voltage specifications in this section are specified at the pins of the device (and not the power supply). If the device operates outside these ranges, then all DC and AC specifications are not guaranteed. Furthermore, the reliability of the device may be affected. The timing parameters in this chapter apply to both commercial and industrial temperature ranges unless otherwise stated.

Tables 4–1 through 4–8 provide information on absolute maximum ratings.

| Table 4–1          | Table 4–1. Stratix Device Absolute Maximum Ratings Notes (1), (2) |                         |         |         |      |  |  |  |  |

|--------------------|-------------------------------------------------------------------|-------------------------|---------|---------|------|--|--|--|--|

| Symbol             | Parameter                                                         | Conditions              | Minimum | Maximum | Unit |  |  |  |  |

| V <sub>CCINT</sub> | Supply voltage                                                    | With respect to ground  | -0.5    | 2.4     | V    |  |  |  |  |

| V <sub>CCIO</sub>  | -                                                                 |                         | -0.5    | 4.6     | V    |  |  |  |  |

| VI                 | DC input voltage (3)                                              |                         | -0.5    | 4.6     | V    |  |  |  |  |

| I <sub>OUT</sub>   | DC output current, per pin                                        |                         | -25     | 40      | mA   |  |  |  |  |

| T <sub>STG</sub>   | Storage temperature                                               | No bias                 | -65     | 150     | °C   |  |  |  |  |

| TJ                 | Junction temperature                                              | BGA packages under bias |         | 135     | °C   |  |  |  |  |

| Table 4–2. Stratix Device Recommended Operating Conditions (Part 1 of 2) |                                                     |            |         |         |      |  |  |

|--------------------------------------------------------------------------|-----------------------------------------------------|------------|---------|---------|------|--|--|

| Symbol                                                                   | Parameter                                           | Conditions | Minimum | Maximum | Unit |  |  |

| V <sub>CCINT</sub>                                                       | Supply voltage for internal logic and input buffers | (4)        | 1.425   | 1.575   | V    |  |  |

| Table 4–3. Stratix Device DC Operating Conditions Note (7) (Part 2 of 2) |                                                            |                                        |         |         |         |      |  |

|--------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------|---------|---------|---------|------|--|

| Symbol                                                                   | Parameter                                                  | Conditions                             | Minimum | Typical | Maximum | Unit |  |

| R <sub>CONF</sub>                                                        | Value of I/O pin pull-<br>up resistor before<br>and during | V <sub>CCIO</sub> = 3.0 V (9)          | 20      |         | 50      | kΩ   |  |

|                                                                          |                                                            | V <sub>CCIO</sub> = 2.375 V <i>(9)</i> | 30      |         | 80      | kΩ   |  |

|                                                                          | configuration                                              | V <sub>CCIO</sub> = 1.71 V <i>(9)</i>  | 60      |         | 150     | kΩ   |  |

| Table 4–4.        | Table 4–4. LVTTL Specifications |                                               |         |         |      |  |  |  |  |

|-------------------|---------------------------------|-----------------------------------------------|---------|---------|------|--|--|--|--|

| Symbol            | Parameter                       | Conditions                                    | Minimum | Maximum | Unit |  |  |  |  |

| V <sub>CCIO</sub> | Output supply voltage           |                                               | 3.0     | 3.6     | V    |  |  |  |  |

| V <sub>IH</sub>   | High-level input voltage        |                                               | 1.7     | 4.1     | V    |  |  |  |  |

| V <sub>IL</sub>   | Low-level input voltage         |                                               | -0.5    | 0.7     | V    |  |  |  |  |

| V <sub>OH</sub>   | High-level output voltage       | $I_{OH} = -4 \text{ to } -24 \text{ mA} (10)$ | 2.4     |         | V    |  |  |  |  |

| V <sub>OL</sub>   | Low-level output voltage        | I <sub>OL</sub> = 4 to 24 mA <i>(10)</i>      |         | 0.45    | V    |  |  |  |  |

| Table 4–5. LVCMOS Specifications |                           |                                                       |                         |         |      |  |  |  |  |  |

|----------------------------------|---------------------------|-------------------------------------------------------|-------------------------|---------|------|--|--|--|--|--|

| Symbol                           | Parameter                 | Conditions                                            | Minimum                 | Maximum | Unit |  |  |  |  |  |

| V <sub>CCIO</sub>                | Output supply voltage     |                                                       | 3.0                     | 3.6     | V    |  |  |  |  |  |

| V <sub>IH</sub>                  | High-level input voltage  |                                                       | 1.7                     | 4.1     | V    |  |  |  |  |  |

| V <sub>IL</sub>                  | Low-level input voltage   |                                                       | -0.5                    | 0.7     | V    |  |  |  |  |  |

| V <sub>OH</sub>                  | High-level output voltage | V <sub>CCIO</sub> = 3.0,<br>I <sub>OH</sub> = -0.1 mA | V <sub>CCIO</sub> - 0.2 |         | V    |  |  |  |  |  |

| V <sub>OL</sub>                  | Low-level output voltage  | $V_{CCIO} = 3.0,$<br>$I_{OL} = 0.1 \text{ mA}$        |                         | 0.2     | V    |  |  |  |  |  |

| Table 4–6. 2.5-V I/O Specifications |                           |                                    |         |         |      |  |  |  |  |  |

|-------------------------------------|---------------------------|------------------------------------|---------|---------|------|--|--|--|--|--|

| Symbol                              | Parameter                 | Conditions                         | Minimum | Maximum | Unit |  |  |  |  |  |

| V <sub>CCIO</sub>                   | Output supply voltage     |                                    | 2.375   | 2.625   | V    |  |  |  |  |  |

| V <sub>IH</sub>                     | High-level input voltage  |                                    | 1.7     | 4.1     | V    |  |  |  |  |  |

| V <sub>IL</sub>                     | Low-level input voltage   |                                    | -0.5    | 0.7     | V    |  |  |  |  |  |

| V <sub>OH</sub>                     | High-level output voltage | I <sub>OH</sub> = -1 mA (10)       | 2.0     |         | V    |  |  |  |  |  |

| V <sub>OL</sub>                     | Low-level output voltage  | I <sub>OL</sub> = 1 mA <i>(10)</i> |         | 0.4     | V    |  |  |  |  |  |

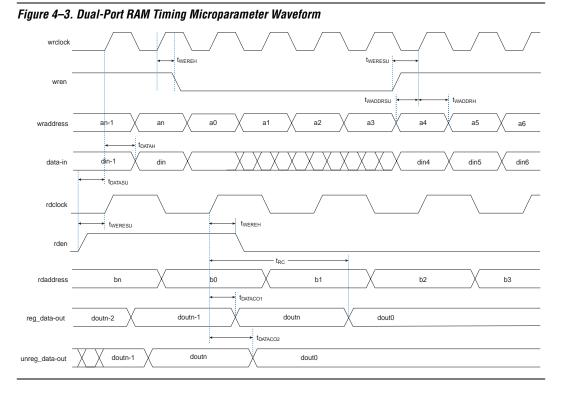

Figure 4–3 shows the TriMatrix memory waveforms for the M512, M4K, and M-RAM timing parameters shown in Tables 4–40 through 4–42.

Internal timing parameters are specified on a speed grade basis independent of device density. Tables 4–44 through 4–50 show the internal timing microparameters for LEs, IOEs, TriMatrix memory structures, DSP blocks, and MultiTrack interconnects.

| Table 4–43. Routing Delay Internal Timing Microparameter         Descriptions (Part 1 of 2) |                                                                                    |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Symbol                                                                                      | Parameter                                                                          |  |  |  |  |  |  |

| t <sub>R4</sub>                                                                             | Delay for an R4 line with average loading; covers a distance of four LAB columns.  |  |  |  |  |  |  |

| t <sub>R8</sub>                                                                             | Delay for an R8 line with average loading; covers a distance of eight LAB columns. |  |  |  |  |  |  |

| t <sub>R24</sub>                                                                            | Delay for an R24 line with average loading; covers a distance of 24 LAB columns.   |  |  |  |  |  |  |

ſ

| Table 4–57. I         | EP1S10 Ext | ernal I/O T | ïming on C | olumn Pin | s Using Gla | obal Clock | Networks | Note (1) |      |

|-----------------------|------------|-------------|------------|-----------|-------------|------------|----------|----------|------|

| Deremeter             | -5 Spee    | d Grade     | -6 Spee    | d Grade   | -7 Spee     | d Grade    | -8 Spee  | d Grade  | Unit |

| Parameter             | Min        | Max         | Min        | Max       | Min         | Max        | Min      | Max      | Unit |

| t <sub>INSU</sub>     | 1.647      |             | 1.692      |           | 1.940       |            | NA       |          | ns   |

| t <sub>INH</sub>      | 0.000      |             | 0.000      |           | 0.000       |            | NA       |          | ns   |

| t <sub>OUTCO</sub>    | 2.619      | 5.184       | 2.619      | 5.515     | 2.619       | 5.999      | NA       | NA       | ns   |

| t <sub>xz</sub>       | 2.559      | 5.058       | 2.559      | 5.383     | 2.559       | 5.875      | NA       | NA       | ns   |

| t <sub>ZX</sub>       | 2.559      | 5.058       | 2.559      | 5.383     | 2.559       | 5.875      | NA       | NA       | ns   |

| t <sub>INSUPLL</sub>  | 1.239      |             | 1.229      |           | 1.374       |            | NA       |          | ns   |

| t <sub>INHPLL</sub>   | 0.000      |             | 0.000      |           | 0.000       |            | NA       |          | ns   |

| t <sub>OUTCOPLL</sub> | 1.109      | 2.372       | 1.109      | 2.436     | 1.109       | 2.492      | NA       | NA       | ns   |

| t <sub>XZPLL</sub>    | 1.049      | 2.246       | 1.049      | 2.304     | 1.049       | 2.368      | NA       | NA       | ns   |

| t <sub>ZXPLL</sub>    | 1.049      | 2.246       | 1.049      | 2.304     | 1.049       | 2.368      | NA       | NA       | ns   |

| Table 4–58. EP1S10 External I/O Timing on Row Pin Using Fast Regional Clock Network Note (1) |         |         |         |         |         |         |         |         |       |  |  |

|----------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|-------|--|--|

| Parameter                                                                                    | -5 Spee | d Grade | -6 Spee | d Grade | -7 Spee | d Grade | -8 Spee | d Grade | Ilait |  |  |

|                                                                                              | Min     | Max     | Min     | Max     | Min     | Max     | Min     | Max     | Unit  |  |  |

| t <sub>INSU</sub>                                                                            | 2.212   |         | 2.403   |         | 2.759   |         | NA      |         | ns    |  |  |

| t <sub>INH</sub>                                                                             | 0.000   |         | 0.000   |         | 0.000   |         | NA      |         | ns    |  |  |

| t <sub>OUTCO</sub>                                                                           | 2.391   | 4.838   | 2.391   | 5.159   | 2.391   | 5.569   | NA      | NA      | ns    |  |  |

| t <sub>xz</sub>                                                                              | 2.418   | 4.892   | 2.418   | 5.215   | 2.418   | 5.637   | NA      | NA      | ns    |  |  |

| t <sub>ZX</sub>                                                                              | 2.418   | 4.892   | 2.418   | 5.215   | 2.418   | 5.637   | NA      | NA      | ns    |  |  |

| Table 4–89. l         | Table 4–89. EP1S60 External I/O Timing on Row Pins Using Regional Clock Networks Note (1) |         |         |         |         |         |         |         |      |  |  |

|-----------------------|-------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|------|--|--|

| Deremeter             | -5 Spee                                                                                   | d Grade | -6 Spee | d Grade | -7 Spee | d Grade | -8 Spee | d Grade | Unit |  |  |

| Parameter             | Min                                                                                       | Max     | Min     | Max     | Min     | Max     | Min     | Max     | Unit |  |  |

| t <sub>INSU</sub>     | 2.775                                                                                     |         | 2.990   |         | 3.407   |         | NA      |         | ns   |  |  |

| t <sub>INH</sub>      | 0.000                                                                                     |         | 0.000   |         | 0.000   |         | NA      |         | ns   |  |  |

| t <sub>OUTCO</sub>    | 2.867                                                                                     | 5.644   | 2.867   | 6.057   | 2.867   | 6.600   | NA      | NA      | ns   |  |  |

| t <sub>xz</sub>       | 2.894                                                                                     | 5.698   | 2.894   | 6.113   | 2.894   | 6.668   | NA      | NA      | ns   |  |  |

| t <sub>ZX</sub>       | 2.894                                                                                     | 5.698   | 2.894   | 6.113   | 2.894   | 6.668   | NA      | NA      | ns   |  |  |

| t <sub>INSUPLL</sub>  | 1.523                                                                                     |         | 1.577   |         | 1.791   |         | NA      |         | ns   |  |  |

| t <sub>INHPLL</sub>   | 0.000                                                                                     |         | 0.000   |         | 0.000   |         | NA      |         | ns   |  |  |

| t <sub>OUTCOPLL</sub> | 1.174                                                                                     | 2.507   | 1.174   | 2.643   | 1.174   | 2.664   | NA      | NA      | ns   |  |  |

| t <sub>XZPLL</sub>    | 1.201                                                                                     | 2.561   | 1.201   | 2.699   | 1.201   | 2.732   | NA      | NA      | ns   |  |  |

| t <sub>ZXPLL</sub>    | 1.201                                                                                     | 2.561   | 1.201   | 2.699   | 1.201   | 2.732   | NA      | NA      | ns   |  |  |

| Parameter             | -5 Spee | d Grade | -6 Spee | d Grade | -7 Spee | d Grade | -8 Spee | d Grade | 1    |

|-----------------------|---------|---------|---------|---------|---------|---------|---------|---------|------|

|                       | Min     | Max     | Min     | Max     | Min     | Max     | Min     | Max     | Unit |

| t <sub>INSU</sub>     | 2.232   |         | 2.393   |         | 2.721   |         | NA      |         | ns   |

| t <sub>INH</sub>      | 0.000   |         | 0.000   |         | 0.000   |         | NA      |         | ns   |

| t <sub>outco</sub>    | 3.182   | 6.187   | 3.182   | 6.654   | 3.182   | 7.286   | NA      | NA      | ns   |

| t <sub>XZ</sub>       | 3.209   | 6.241   | 3.209   | 6.710   | 3.209   | 7.354   | NA      | NA      | ns   |

| t <sub>ZX</sub>       | 3.209   | 6.241   | 3.209   | 6.710   | 3.209   | 7.354   | NA      | NA      | ns   |

| t <sub>INSUPLL</sub>  | 1.651   |         | 1.612   |         | 1.833   |         | NA      |         | ns   |

| t <sub>INHPLL</sub>   | 0.000   |         | 0.000   |         | 0.000   |         | NA      |         | ns   |

| t <sub>OUTCOPLL</sub> | 1.154   | 2.469   | 1.154   | 2.608   | 1.154   | 2.622   | NA      | NA      | ns   |

| t <sub>XZPLL</sub>    | 1.181   | 2.523   | 1.181   | 2.664   | 1.181   | 2.690   | NA      | NA      | ns   |

| t <sub>ZXPLL</sub>    | 1.181   | 2.523   | 1.181   | 2.664   | 1.181   | 2.690   | NA      | NA      | ns   |

*Note to Tables* 4–85 *to* 4–90:

(1) Only EP1S25, EP1S30, and EP1S40 devices have the -8 speed grade.

| Table 4–116. Stratix Ma<br>Flip-Chip Packages | nximum Inpu       | it Clock Rat      | e for CLK[1       | , 3, 8, 10] I     | Pins in |

|-----------------------------------------------|-------------------|-------------------|-------------------|-------------------|---------|

| I/O Standard                                  | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit    |

| LVTTL                                         | 422               | 422               | 390               | 390               | MHz     |

| 2.5 V                                         | 422               | 422               | 390               | 390               | MHz     |

| 1.8 V                                         | 422               | 422               | 390               | 390               | MHz     |

| 1.5 V                                         | 422               | 422               | 390               | 390               | MHz     |

| LVCMOS                                        | 422               | 422               | 390               | 390               | MHz     |

| GTL+                                          | 300               | 250               | 200               | 200               | MHz     |

| SSTL-3 Class I                                | 400               | 350               | 300               | 300               | MHz     |

| SSTL-3 Class II                               | 400               | 350               | 300               | 300               | MHz     |

| SSTL-2 Class I                                | 400               | 350               | 300               | 300               | MHz     |

| SSTL-2 Class II                               | 400               | 350               | 300               | 300               | MHz     |

| SSTL-18 Class I                               | 400               | 350               | 300               | 300               | MHz     |

| SSTL-18 Class II                              | 400               | 350               | 300               | 300               | MHz     |

| 1.5-V HSTL Class I                            | 400               | 350               | 300               | 300               | MHz     |

| 1.8-V HSTL Class I                            | 400               | 350               | 300               | 300               | MHz     |

| CTT                                           | 300               | 250               | 200               | 200               | MHz     |

| Differential 1.5-V HSTL<br>C1                 | 400               | 350               | 300               | 300               | MHz     |

| LVPECL (1)                                    | 645               | 645               | 640               | 640               | MHz     |

| PCML (1)                                      | 300               | 275               | 275               | 275               | MHz     |

| LVDS (1)                                      | 645               | 645               | 640               | 640               | MHz     |

| HyperTransport<br>technology (1)              | 500               | 500               | 450               | 450               | MHz     |

Table 4-116 Stratix Maximum Innut Clock Rate for CLK[1. 3. 8, 10] Pins in

Table 4–117. Stratix Maximum Input Clock Rate for CLK[7..4] & CLK[15..12]

Pins in Wire-Bond Packages (Part 1 of 2)

| I/O Standard | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|--------------|-------------------|-------------------|-------------------|------|

| LVTTL        | 422               | 390               | 390               | MHz  |

| 2.5 V        | 422               | 390               | 390               | MHz  |

| 1.8 V        | 422               | 390               | 390               | MHz  |

| 1.5 V        | 422               | 390               | 390               | MHz  |

| LVCMOS       | 422               | 390               | 390               | MHz  |

| GTL          | 250               | 200               | 200               | MHz  |

| Symbol Co         | Conditions                                                                   | -5 Speed Grade |     | -6 Speed Grade |      | -7 Speed Grade |      |      | -8 Speed Grade |      |      | 11  |      |      |

|-------------------|------------------------------------------------------------------------------|----------------|-----|----------------|------|----------------|------|------|----------------|------|------|-----|------|------|

|                   | Conditions                                                                   | Min            | Тур | Max            | Min  | Тур            | Max  | Min  | Тур            | Max  | Min  | Тур | Max  | Unit |

| t <sub>DUTY</sub> | LVDS ( $J = 2$<br>through 10)                                                | 47.5           | 50  | 52.5           | 47.5 | 50             | 52.5 | 47.5 | 50             | 52.5 | 47.5 | 50  | 52.5 | %    |

|                   | LVDS ( <i>J</i> = 1)<br>and LVPECL,<br>PCML,<br>HyperTransport<br>technology | 45             | 50  | 55             | 45   | 50             | 55   | 45   | 50             | 55   | 45   | 50  | 55   | %    |

| t <sub>LOCK</sub> | All                                                                          |                |     | 100            |      |                | 100  |      |                | 100  |      |     | 100  | μs   |

Notes to Table 4–125:

(1) When J = 4, 7, 8, and 10, the SERDES block is used.

(2) When J = 2 or J = 1, the SERDES is bypassed.