Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 3247                                                    |

| Number of Logic Elements/Cells | 32470                                                   |

| Total RAM Bits                 | 3317184                                                 |

| Number of I/O                  | 597                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                         |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 780-BBGA, FCBGA                                         |

| Supplier Device Package        | 780-FBGA (29x29)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s30f780c6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Chapter Revision Dates**

The chapters in this book, *Stratix Device Handbook*, *Volume 1*, were revised on the following dates. Where chapters or groups of chapters are available separately, part numbers are listed.

Chapter 1. Introduction

Revised: July 2005 Part number: S51001-3.2

Chapter 2. Stratix Architecture

Revised: July 2005 Part number: S51002-3.2

Chapter 3. Configuration & Testing

Revised: July 2005 Part number: S51003-1.3

Chapter 4. DC & Switching Characteristics

Revised: January 2006 Part number: S51004-3.4

Chapter 5. Reference & Ordering Information

Revised: September 2004 Part number: S51005-2.1

Altera Corporation vii

| Chapter | Date/Version         | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2       | July 2003, v2.0      | <ul> <li>Added reference on page 2-73 to Figures 2-50 and 2-51 for RCLK connections.</li> <li>Updated ranges for EPLL post-scale and pre-scale dividers on page 2-85.</li> <li>Updated PLL Reconfiguration frequency from 25 to 22 MHz on page 2-87.</li> <li>New requirement to assert are set signal each PLL when it has to reacquire lock on either a new clock after loss of lock (page 2-96).</li> <li>Updated max input frequency for CLK [1,3,8,10] from 462 to 500, Table 2-24.</li> <li>Renamed impedance matching to series termination throughout.</li> <li>Updated naming convention for DQS pins on page 2-112 to match pin tables.</li> <li>Added DDR SDRAM Performance Specification on page 2-117.</li> <li>Added external reference resistor values for terminator technology (page 2-136).</li> <li>Added Terminator Technology Specification on pages 2-137 and 2-138.</li> <li>Updated Tables 2-45 to 2-49 to reflect PLL cross-bank support for high speed differential channels at full speed.</li> <li>Wire bond package performance specification for "high" speed channels was increased to 624 Mbps from 462 Mbps throughout chapter.</li> </ul> |

| 3       | July 2005, v1.3      | <ul> <li>Updated "Operating Modes" section.</li> <li>Updated "Temperature Sensing Diode" section.</li> <li>Updated "IEEE Std. 1149.1 (JTAG) Boundary-Scan Support" section.</li> <li>Updated "Configuration" section.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | January 2005, v1.2   | Updated limits for JTAG chain of devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | September 2004, v1.1 | <ul> <li>Added new section, "Stratix Automated Single Event Upset (SEU)         Detection" on page 3–12.</li> <li>Updated description of "Custom-Built Circuitry" on page 3–13.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | April 2003, v1.0     | No new changes in Stratix Device Handbook v2.0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4       | January 2006, v3.4   | Added Table 4–135.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | July 2005, v3.3      | <ul> <li>Updated Tables 4–6 and 4–30.</li> <li>Updated Tables 4–103 through 4–108.</li> <li>Updated Tables 4–114 through 4–124.</li> <li>Updated Table 4–129.</li> <li>Added Table 4–130.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Altera Corporation Section I–3

The number of M512 RAM, M4K RAM, and DSP blocks varies by device along with row and column numbers and M-RAM blocks. Table 2–1 lists the resources available in Stratix devices.

| Table 2–1. Stratix Device Resources |                            |                           |                 |        |     |          |  |  |  |  |

|-------------------------------------|----------------------------|---------------------------|-----------------|--------|-----|----------|--|--|--|--|

| Device                              | M512 RAM<br>Columns/Blocks | M4K RAM<br>Columns/Blocks | M-RAM<br>Blocks |        |     | LAB Rows |  |  |  |  |

| EP1S10                              | 4 / 94                     | 2/60                      | 1               | 2/6    | 40  | 30       |  |  |  |  |

| EP1S20                              | 6 / 194                    | 2 / 82                    | 2               | 2/10   | 52  | 41       |  |  |  |  |

| EP1S25                              | 6 / 224                    | 3 / 138                   | 2               | 2/10   | 62  | 46       |  |  |  |  |

| EP1S30                              | 7 / 295                    | 3 / 171                   | 4               | 2 / 12 | 67  | 57       |  |  |  |  |

| EP1S40                              | 8 / 384                    | 3 / 183                   | 4               | 2 / 14 | 77  | 61       |  |  |  |  |

| EP1S60                              | 10 / 574                   | 4 / 292                   | 6               | 2 / 18 | 90  | 73       |  |  |  |  |

| EP1S80                              | 11 / 767                   | 4 / 364                   | 9               | 2 / 22 | 101 | 91       |  |  |  |  |

### Logic Array Blocks

Each LAB consists of 10 LEs, LE carry chains, LAB control signals, local interconnect, LUT chain, and register chain connection lines. The local interconnect transfers signals between LEs in the same LAB. LUT chain connections transfer the output of one LE's LUT to the adjacent LE for fast sequential LUT connections within the same LAB. Register chain connections transfer the output of one LE's register to the adjacent LE's register within an LAB. The Quartus® II Compiler places associated logic within an LAB or adjacent LABs, allowing the use of local, LUT chain, and register chain connections for performance and area efficiency. Figure 2–2 shows the Stratix LAB.

#### Dynamic Arithmetic Mode

The dynamic arithmetic mode is ideal for implementing adders, counters, accumulators, wide parity functions, and comparators. An LE in dynamic arithmetic mode uses four 2-input LUTs configurable as a dynamic adder/subtractor. The first two 2-input LUTs compute two summations based on a possible carry-in of 1 or 0; the other two LUTs generate carry outputs for the two chains of the carry select circuitry. As shown in Figure 2–7, the LAB carry-in signal selects either the carry-in0 or carry-in1 chain. The selected chain's logic level in turn determines which parallel sum is generated as a combinatorial or registered output. For example, when implementing an adder, the sum output is the selection of two possible calculated sums: data1 + data2 + carry-in0 or data1 + data2 + carry-in1. The other two LUTs use the data1 and data2 signals to generate two possible carry-out signals—one for a carry of 1 and the other for a carry of 0. The carry-in0 signal acts as the carry select for the carry-out 0 output and carry-in1 acts as the carry select for the carry-out1 output. LEs in arithmetic mode can drive out registered and unregistered versions of the LUT output.

The dynamic arithmetic mode also offers clock enable, counter enable, synchronous up/down control, synchronous clear, synchronous load, and dynamic adder/subtractor options. The LAB local interconnect data inputs generate the counter enable and synchronous up/down control signals. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. The Quartus II software automatically places any registers that are not used by the counter into other LABs. The addnsub LAB-wide signal controls whether the LE acts as an adder or subtractor.

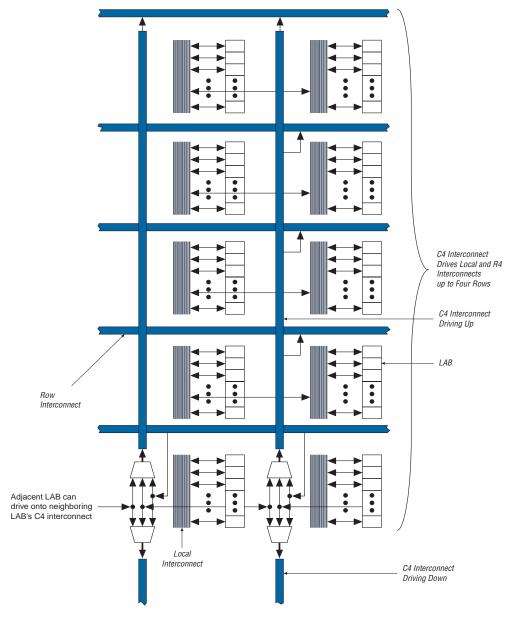

Figure 2–11. C4 Interconnect Connections Note (1)

Note to Figure 2–11:

(1) Each C4 interconnect can drive either up or down four rows.

#### M512 RAM Block

The M512 RAM block is a simple dual-port memory block and is useful for implementing small FIFO buffers, DSP, and clock domain transfer applications. Each block contains 576 RAM bits (including parity bits). M512 RAM blocks can be configured in the following modes:

- Simple dual-port RAM

- Single-port RAM

- FIFO

- ROM

- Shift register

When configured as RAM or ROM, you can use an initialization file to pre-load the memory contents.

The memory address depths and output widths can be configured as  $512 \times 1,256 \times 2,128 \times 4,64 \times 8$  ( $64 \times 9$  bits with parity), and  $32 \times 16$  ( $32 \times 18$  bits with parity). Mixed-width configurations are also possible, allowing different read and write widths. Table 2–4 summarizes the possible M512 RAM block configurations.

| Table 2–4. M512 RAM Block Configurations (Simple Dual-Port RAM) |            |          |          |          |          |          |          |  |  |  |  |

|-----------------------------------------------------------------|------------|----------|----------|----------|----------|----------|----------|--|--|--|--|

| Dood Dow                                                        | Write Port |          |          |          |          |          |          |  |  |  |  |

| Read Port                                                       | 512 × 1    | 256 × 2  | 128 × 4  | 64 × 8   | 32 × 16  | 64 × 9   | 32 × 18  |  |  |  |  |

| 512 × 1                                                         | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |  |  |  |  |

| 256 × 2                                                         | <b>✓</b>   | ~        | ~        | <b>✓</b> | ~        |          |          |  |  |  |  |

| 128 × 4                                                         | <b>✓</b>   | ~        | ~        |          | ~        |          |          |  |  |  |  |

| 64 × 8                                                          | <b>✓</b>   | ~        |          | <b>✓</b> |          |          |          |  |  |  |  |

| 32 × 16                                                         | <b>✓</b>   | ~        | ~        |          | ~        |          |          |  |  |  |  |

| 64 × 9                                                          |            |          |          |          |          | <b>✓</b> |          |  |  |  |  |

| 32 × 18                                                         |            |          |          |          |          |          | <b>✓</b> |  |  |  |  |

When the M512 RAM block is configured as a shift register block, a shift register of size up to 576 bits is possible.

The M512 RAM block can also be configured to support serializer and deserializer applications. By using the mixed-width support in combination with DDR I/O standards, the block can function as a SERDES to support low-speed serial I/O standards using global or regional clocks. See "I/O Structure" on page 2–104 for details on dedicated SERDES in Stratix devices.

M4K RAM blocks support byte writes when the write port has a data width of 16, 18, 32, or 36 bits. The byte enables allow the input data to be masked so the device can write to specific bytes. The unwritten bytes retain the previous written value. Table 2–7 summarizes the byte selection.

| Table 2–7. Byte Enable for M4K Blocks Notes (1), (2) |                            |        |  |  |  |  |  |  |

|------------------------------------------------------|----------------------------|--------|--|--|--|--|--|--|

| byteena[30]                                          | [30] datain ×18 datain ×36 |        |  |  |  |  |  |  |

| [0] = 1                                              | [80]                       | [80]   |  |  |  |  |  |  |

| [1] = 1                                              | [179]                      | [179]  |  |  |  |  |  |  |

| [2] = 1                                              | _                          | [2618] |  |  |  |  |  |  |

| [3] = 1                                              | _                          | [3527] |  |  |  |  |  |  |

*Notes to Table 2–7:*

- (1) Any combination of byte enables is possible.

- (2) Byte enables can be used in the same manner with 8-bit words, i.e., in  $\times$  16 and  $\times$  32 modes.

The M4K RAM blocks allow for different clocks on their inputs and outputs. Either of the two clocks feeding the block can clock M4K RAM block registers (renwe, address, byte enable, datain, and output registers). Only the output register can be bypassed. The eight labclk signals or local interconnects can drive the control signals for the A and B ports of the M4K RAM block. LEs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals, as shown in Figure 2–17.

The R4, R8, C4, C8, and direct link interconnects from adjacent LABs drive the M4K RAM block local interconnect. The M4K RAM blocks can communicate with LABs on either the left or right side through these row resources or with LAB columns on either the right or left with the column resources. Up to 10 direct link input connections to the M4K RAM Block are possible from the left adjacent LABs and another 10 possible from the right adjacent LAB. M4K RAM block outputs can also connect to left and right LABs through 10 direct link interconnects each. Figure 2–18 shows the M4K RAM block to logic array interface.

Table 2–12 shows the input and output data signal connections for the column units (B1 to B6 and A1 to A6). It also shows the address and control signal input connections to the row units (R1 to R11).

| Unit Interface Plack Input Clanale Output Cianale |                                              |                 |  |  |  |  |  |  |

|---------------------------------------------------|----------------------------------------------|-----------------|--|--|--|--|--|--|

| Unit Interface Block                              | Input Signals                                | Output Signals  |  |  |  |  |  |  |

| R1                                                | addressa[70]                                 |                 |  |  |  |  |  |  |

| R2                                                | addressa[158]                                |                 |  |  |  |  |  |  |

| R3                                                | byte_enable_a[70]<br>renwe_a                 |                 |  |  |  |  |  |  |

| R4                                                | -                                            |                 |  |  |  |  |  |  |

| R5                                                | -                                            |                 |  |  |  |  |  |  |

| R6                                                | clock_a<br>clocken_a<br>clock_b<br>clocken_b |                 |  |  |  |  |  |  |

| R7                                                | -                                            |                 |  |  |  |  |  |  |

| R8                                                | -                                            |                 |  |  |  |  |  |  |

| R9                                                | byte_enable_b[70]<br>renwe_b                 |                 |  |  |  |  |  |  |

| R10                                               | addressb[158]                                |                 |  |  |  |  |  |  |

| R11                                               | addressb[70]                                 |                 |  |  |  |  |  |  |

| B1                                                | datain_b[7160]                               | dataout_b[7160] |  |  |  |  |  |  |

| B2                                                | datain_b[5948]                               | dataout_b[5948] |  |  |  |  |  |  |

| B3                                                | datain_b[4736]                               | dataout_b[4736] |  |  |  |  |  |  |

| B4                                                | datain_b[3524]                               | dataout_b[3524] |  |  |  |  |  |  |

| B5                                                | datain_b[2312]                               | dataout_b[2312] |  |  |  |  |  |  |

| B6                                                | datain_b[110]                                | dataout_b[110]  |  |  |  |  |  |  |

| A1                                                | datain_a[7160]                               | dataout_a[7160] |  |  |  |  |  |  |

| A2                                                | datain_a[5948]                               | dataout_a[5948] |  |  |  |  |  |  |

| A3                                                | datain_a[4736]                               | dataout_a[4736] |  |  |  |  |  |  |

| A4                                                | datain_a[3524]                               | dataout_a[3524] |  |  |  |  |  |  |

| A5                                                | datain_a[2312]                               | dataout_a[2312] |  |  |  |  |  |  |

| A6                                                | datain_a[110]                                | dataout_a[110]  |  |  |  |  |  |  |

#### Adder/Subtractor/Accumulator

The adder/subtractor/accumulator is the first level of the adder/output block and can be used as an accumulator or as an adder/subtractor.

#### Adder/Subtractor

Each adder/subtractor/accumulator block can perform addition or subtraction using the addnsub independent control signal for each first-level adder in  $18 \times 18$ -bit mode. There are two addnsub [1..0] signals available in a DSP block for any configuration. For  $9 \times 9$ -bit mode, one addnsub [1..0] signal controls the top two one-level adders and another addnsub [1..0] signal controls the bottom two one-level adders. A high addnsub signal indicates addition, and a low signal indicates subtraction. The addnsub control signal can be unregistered or registered once or twice when feeding the adder blocks to match data path pipelines.

The signa and signb signals serve the same function as the multiplier block signa and signb signals. The only difference is that these signals can be registered up to two times. These signals are tied to the same signa and signb signals from the multiplier and must be connected to the same clocks and control signals.

#### Accumulator

When configured for accumulation, the adder/output block output feeds back to the accumulator as shown in Figure 2–34. The accum\_sload[1..0] signal synchronously loads the multiplier result to the accumulator output. This signal can be unregistered or registered once or twice. Additionally, the overflow signal indicates the accumulator has overflowed or underflowed in accumulation mode. This signal is always registered and must be externally latched in LEs if the design requires a latched overflow signal.

#### Summation

The output of the adder/subtractor/accumulator block feeds to an optional summation block. This block sums the outputs of the DSP block multipliers. In 9  $\times$  9-bit mode, there are two summation blocks providing the sums of two sets of four 9  $\times$  9-bit multipliers. In 18  $\times$  18-bit mode, there is one summation providing the sum of one set of four 18  $\times$  18-bit multipliers.

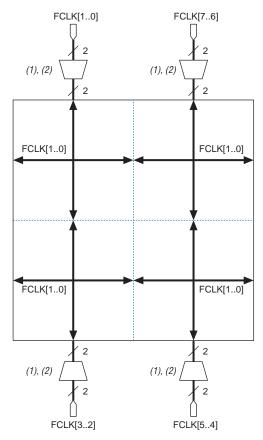

Figure 2–44. EP1S25, EP1S20 & EP1S10 Device Fast Clock Pin Connections to Fast Regional Clocks

#### Notes to Figure 2-44:

- (1) This is a set of two multiplexers.

- (2) In addition to the FCLK pin inputs, there is also an input from the I/O interconnect.

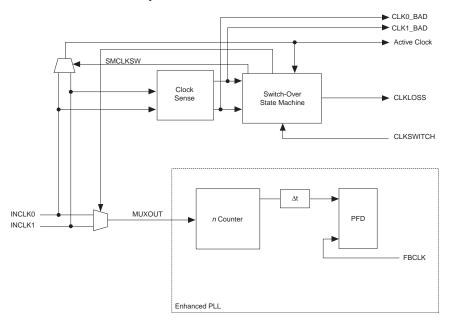

Figure 2-53. Clock Switchover Circuitry

There are two possible ways to use the clock switchover feature.

- Use automatic switchover circuitry for switching between inputs of the same frequency. For example, in applications that require a redundant clock with the same frequency as the primary clock, the switchover state machine generates a signal that controls the multiplexer select input on the bottom of Figure 2–53. In this case, the secondary clock becomes the reference clock for the PLL.

- Use the clkswitch input for user- or system-controlled switch conditions. This is possible for same-frequency switchover or to switch between inputs of different frequencies. For example, if inclk0 is 66 MHz and inclk1 is 100 MHz, you must control the switchover because the automatic clock-sense circuitry cannot monitor primary and secondary clock frequencies with a frequency difference of more than ±20%. This feature is useful when clock sources can originate from multiple cards on the backplane, requiring a system-controlled switchover between frequencies of operation. You can use clkswitch together with the lock signal to trigger the switch from a clock that is running but becomes unstable and cannot be locked onto.

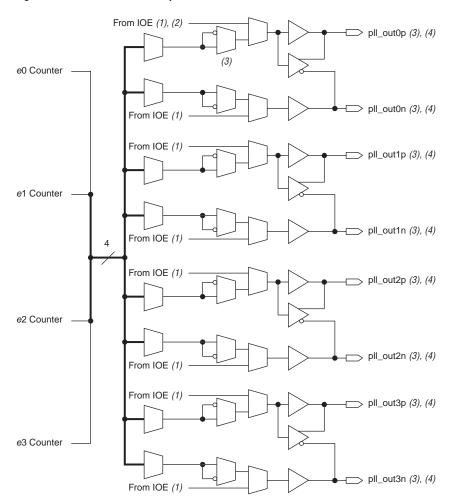

Figure 2-55. External Clock Outputs for PLLs 5 & 6

#### *Notes to Figure 2–55:*

- (1) The design can use each external clock output pin as a general-purpose output pin from the logic array. These pins are multiplexed with IOE outputs.

- (2) Two single-ended outputs are possible per output counter—either two outputs of the same frequency and phase or one shifted 180°.

- (3) EP1S10, EP1S20, and EP1S25 devices in 672-pin BGA and 484- and 672-pin FineLine BGA packages only have two pairs of external clocks (i.e., pll\_out0p, pll\_out0n, pll\_out1p, and pll\_out1n).

- (4) Differential SSTL and HSTL outputs are implemented using two single-ended output buffers, which are programmed to have opposite polarity.

| Table 4–9. Overshoot Input Voltage with Respect to Duty Cycle (Part 2 of 2) |    |  |  |  |  |  |

|-----------------------------------------------------------------------------|----|--|--|--|--|--|

| Vin (V) Maximum Duty Cycle (%)                                              |    |  |  |  |  |  |

| 4.3                                                                         | 30 |  |  |  |  |  |

| 4.4                                                                         | 17 |  |  |  |  |  |

| 4.5                                                                         | 10 |  |  |  |  |  |

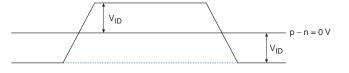

Figures 4–1 and 4–2 show receiver input and transmitter output waveforms, respectively, for all differential I/O standards (LVDS, 3.3-V PCML, LVPECL, and HyperTransport technology).

Figure 4-1. Receiver Input Waveforms for Differential I/O Standards

# Single-Ended Waveform Positive Channel (p) = $V_{IH}$ Negative Channel (n) = $V_{IL}$

#### **Differential Waveform**

| Table 4–33. Stratix Device Capacitance Note (5) |                                                                                                                             |         |         |         |      |  |  |  |  |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|------|--|--|--|--|

| Symbol                                          | Parameter                                                                                                                   | Minimum | Typical | Maximum | Unit |  |  |  |  |

| C <sub>IOTB</sub>                               | Input capacitance on I/O pins in I/O banks 3, 4, 7, and 8.                                                                  |         | 11.5    |         | pF   |  |  |  |  |

| C <sub>IOLR</sub>                               | Input capacitance on I/O pins in I/O banks 1, 2, 5, and 6, including high-speed differential receiver and transmitter pins. |         | 8.2     |         | pF   |  |  |  |  |

| C <sub>CLKTB</sub>                              | Input capacitance on top/bottom clock input pins: CLK [4:7] and CLK [12:15].                                                |         | 11.5    |         | pF   |  |  |  |  |

| C <sub>CLKLR</sub>                              | Input capacitance on left/right clock inputs: CLK1, CLK3, CLK8, CLK10.                                                      |         | 7.8     |         | pF   |  |  |  |  |

| C <sub>CLKLR+</sub>                             | Input capacitance on left/right clock inputs: CLK0, CLK2, CLK9, and CLK11.                                                  |         | 4.4     |         | pF   |  |  |  |  |

#### Notes to Tables 4–10 through 4–33:

- (1) When  $tx_outclock$  port of altlvds\_tx megafunction is 717 MHz,  $V_{OD(min)} = 235$  mV on the output clock pin.

- (2) Pin pull-up resistance values will lower if an external source drives the pin higher than V<sub>CCIO</sub>.

- (3) Drive strength is programmable according to the values shown in the *Stratix Architecture* chapter of the *Stratix Device Handbook, Volume 1*.

- (4) V<sub>REF</sub> specifies the center point of the switching range.

- (5) Capacitance is sample-tested only. Capacitance is measured using time-domain reflections (TDR). Measurement accuracy is within ±0.5 pF.

- (6)  $V_{IO}$  and  $V_{CM}$  have multiple ranges and values for J=1 through 10.

# Power Consumption

Altera® offers two ways to calculate power for a design: the Altera web power calculator and the PowerGauge<sup>TM</sup> feature in the Quartus® II software.

The interactive power calculator on the Altera web site is typically used prior to designing the FPGA in order to get a magnitude estimate of the device power. The Quartus II software PowerGauge feature allows you to apply test vectors against your design for more accurate power consumption modeling.

In both cases, these calculations should only be used as an estimation of power, not as a specification.

Stratix devices require a certain amount of power-up current to successfully power up because of the small process geometry on which they are fabricated.

Table 4–34 shows the maximum power-up current ( $I_{CCINT}$ ) required to power a Stratix device. This specification is for commercial operating conditions. Measurements were performed with an isolated Stratix device on the board to characterize the power-up current of an isolated

**Table 4–101.** Reporting Methodology For Maximum Timing For Single-Ended Output Pins (Part 2 of 2) Notes (1), (2), (3)

| 1/2.01                 |             | Measurement<br>Point |                |                           |                          |            |                        |                   |

|------------------------|-------------|----------------------|----------------|---------------------------|--------------------------|------------|------------------------|-------------------|

| I/O Standard           | $R_{UP}$    | $R_{DN}$             | R <sub>S</sub> | $\mathbf{R}_{T}$ $\Omega$ | V <sub>CCIO</sub><br>(V) | VTT<br>(V) | C <sub>L</sub><br>(pF) | V <sub>MEAS</sub> |

| 3.3-V SSTL-3 Class I   | -           | _                    | 25             | 50                        | 2.950                    | 1.250      | 30                     | 1.250             |

| 2.5-V SSTL-2 Class II  | -           | _                    | 25             | 25                        | 2.370                    | 1.110      | 30                     | 1.110             |

| 2.5-V SSTL-2 Class I   | -           | -                    | 25             | 50                        | 2.370                    | 1.110      | 30                     | 1.110             |

| 1.8-V SSTL-18 Class II | -           | -                    | 25             | 25                        | 1.650                    | 0.760      | 30                     | 0.760             |

| 1.8-V SSTL-18 Class I  | -           | -                    | 25             | 50                        | 1.650                    | 0.760      | 30                     | 0.760             |

| 1.5-V HSTL Class II    | -           | -                    | 0              | 25                        | 1.400                    | 0.700      | 20                     | 0.680             |

| 1.5-V HSTL Class I     | -           | -                    | 0              | 50                        | 1.400                    | 0.700      | 20                     | 0.680             |

| 1.8-V HSTL Class II    | -           | -                    | 0              | 25                        | 1.650                    | 0.700      | 20                     | 0.880             |

| 1.8-V HSTL Class I     | -           | -                    | 0              | 50                        | 1.650                    | 0.700      | 20                     | 0.880             |

| 3.3-V PCI (4)          | <b>-/25</b> | 25/–                 | 0              | -                         | 2.950                    | 2.950      | 10                     | 0.841/1.814       |

| 3.3-V PCI-X 1.0 (4)    | <b>-/25</b> | 25/–                 | 0              | _                         | 2.950                    | 2.950      | 10                     | 0.841/1.814       |

| 3.3-V Compact PCI (4)  | <b>-/25</b> | 25/–                 | 0              | -                         | 2.950                    | 2.950      | 10                     | 0.841/1.814       |

| 3.3-V AGP 1X (4)       | <b>-/25</b> | 25/–                 | 0              | _                         | 2.950                    | 2.950      | 10                     | 0.841/1.814       |

| 3.3-V CTT              | _           | -                    | 25             | 50                        | 2.050                    | 1.350      | 30                     | 1.350             |

#### *Notes to Table 4–101:*

- (1) Input measurement point at internal node is  $0.5 \times V_{CCINT}$ .

- (2) Output measuring point for data is V<sub>MEAS</sub>.

- (3) Input stimulus edge rate is 0 to  $V_{\rm CCINT}$  in 0.5 ns (internal signal) from the driver preceding the IO buffer.

- (4) The first value is for output rising edge and the second value is for output falling edge. The hyphen (-) indicates infinite resistance or disconnection.

| Table 4–102. Reporting Methodology For Minimum Timi | ing For Single-Ended Output Pins (Part 2 of 2) |

|-----------------------------------------------------|------------------------------------------------|

| Notes (1), (2), (3)                                 |                                                |

| I/O Standard |                   | Measurement<br>Point |                |                  |                          |            |                        |                   |

|--------------|-------------------|----------------------|----------------|------------------|--------------------------|------------|------------------------|-------------------|

|              | $\mathbf{R}_{UP}$ | $R_{DN}$             | R <sub>S</sub> | $\mathbf{R}_{T}$ | V <sub>CCIO</sub><br>(V) | VTT<br>(V) | C <sub>L</sub><br>(pF) | V <sub>MEAS</sub> |

| 3.3-V CTT    | _                 | =-                   | 25             | 50               | 3.600                    | 1.650      | 30                     | 1.650             |

#### Notes to Table 4–102:

- (1) Input measurement point at internal node is  $0.5 \times V_{CCINT}$ .

- (2) Output measuring point for data is V<sub>MEAS</sub>. When two values are given, the first is the measurement point on the rising edge and the other is for the falling edge.

- (3) Input stimulus edge rate is 0 to V<sub>CCINT</sub> in 0.5 ns (internal signal) from the driver preceding the I/O buffer.

- (4) The first value is for the output rising edge and the second value is for the output falling edge. The hyphen (-) indicates infinite resistance or disconnection.

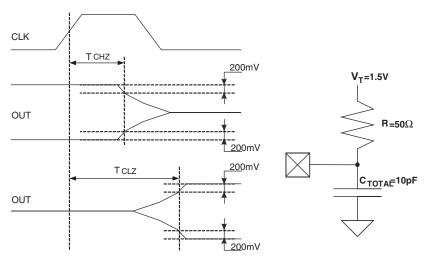

Figure 4–8 shows the measurement setup for output disable and output enable timing. The  $T_{CHZ}$  stands for clock to high Z time delay and is the same as  $T_{XZ}.$  The  $T_{CLZ}$  stands for clock to low Z (driving) time delay and is the same as  $T_{ZX}.$

Figure 4–8. Measurement Setup for  $T_{XZ}$  and  $T_{ZX}$

Tables 4–105 through 4–108 show the output adder delays associated with column and row I/O pins for both fast and slow slew rates. If an I/O standard is selected other than 3.3-V LVTTL 4mA or LVCMOS 2 mA with a fast slew rate, add the selected delay to the external  $t_{\rm OUTCO}$ ,  $t_{\rm OUTCOPLL}$ ,  $t_{\rm XZ}$ ,  $t_{\rm XZPLL}$ , and  $t_{\rm ZXPLL}$  I/O parameters shown in Table 4–55 on page 4–36 through Table 4–96 on page 4–56.

| Table 4–105. Stratix I/O Standard Output Delay Adders for Fast Slew Rate on Column Pins (Part 1 of 2) |       |                |       |         |         |         |                |     |          |      |

|-------------------------------------------------------------------------------------------------------|-------|----------------|-------|---------|---------|---------|----------------|-----|----------|------|

| Donomo                                                                                                |       | -5 Speed Grade |       | -6 Spee | d Grade | -7 Spee | -7 Speed Grade |     | ed Grade | 11:4 |

| Parameter                                                                                             |       | Min            | Max   | Min     | Max     | Min     | Max            | Min | Max      | Unit |

| LVCMOS                                                                                                | 2 mA  |                | 1,895 |         | 1,990   |         | 1,990          |     | 1,990    | ps   |

|                                                                                                       | 4 mA  |                | 956   |         | 1,004   |         | 1,004          |     | 1,004    | ps   |

|                                                                                                       | 8 mA  |                | 189   |         | 198     |         | 198            |     | 198      | ps   |

|                                                                                                       | 12 mA |                | 0     |         | 0       |         | 0              |     | 0        | ps   |

|                                                                                                       | 24 mA |                | -157  |         | -165    |         | -165           |     | -165     | ps   |

| 3.3-V LVTTL                                                                                           | 4 mA  |                | 1,895 |         | 1,990   |         | 1,990          |     | 1,990    | ps   |

|                                                                                                       | 8 mA  |                | 1,347 |         | 1,414   |         | 1,414          |     | 1,414    | ps   |

|                                                                                                       | 12 mA |                | 636   |         | 668     |         | 668            |     | 668      | ps   |

|                                                                                                       | 16 mA |                | 561   |         | 589     |         | 589            |     | 589      | ps   |

|                                                                                                       | 24 mA |                | 0     |         | 0       |         | 0              |     | 0        | ps   |

| 2.5-V LVTTL                                                                                           | 2 mA  |                | 2,517 |         | 2,643   |         | 2,643          |     | 2,643    | ps   |

|                                                                                                       | 8 mA  |                | 834   |         | 875     |         | 875            |     | 875      | ps   |

|                                                                                                       | 12 mA |                | 504   |         | 529     |         | 529            |     | 529      | ps   |

|                                                                                                       | 16 mA |                | 194   |         | 203     |         | 203            |     | 203      | ps   |

| 1.8-V LVTTL                                                                                           | 2 mA  |                | 1,304 |         | 1,369   |         | 1,369          |     | 1,369    | ps   |

|                                                                                                       | 8 mA  |                | 960   |         | 1,008   |         | 1,008          |     | 1,008    | ps   |

|                                                                                                       | 12 mA |                | 960   |         | 1,008   |         | 1,008          |     | 1,008    | ps   |

| 1.5-V LVTTL                                                                                           | 2 mA  |                | 6,680 |         | 7,014   |         | 7,014          |     | 7,014    | ps   |

|                                                                                                       | 4 mA  |                | 3,275 |         | 3,439   |         | 3,439          |     | 3,439    | ps   |

|                                                                                                       | 8 mA  |                | 1,589 |         | 1,668   |         | 1,668          |     | 1,668    | ps   |

| GTL                                                                                                   | •     |                | 16    |         | 17      |         | 17             |     | 17       | ps   |

| GTL+                                                                                                  |       |                | 9     |         | 9       |         | 9              |     | 9        | ps   |

| 3.3-V PCI                                                                                             |       |                | 50    |         | 52      |         | 52             |     | 52       | ps   |

| 3.3-V PCI-X 1.0                                                                                       |       |                | 50    |         | 52      |         | 52             |     | 52       | ps   |

| Compact PCI                                                                                           |       |                | 50    |         | 52      |         | 52             |     | 52       | ps   |

| AGP 1×                                                                                                |       |                | 50    |         | 52      |         | 52             |     | 52       | ps   |

| AGP 2×                                                                                                |       |                | 1,895 |         | 1,990   |         | 1,990          |     | 1,990    | ps   |

Table 4–118. Stratix Maximum Input Clock Rate for CLK[0, 2, 9, 11] Pins & FPLL[10..7]CLK Pins in Wire-Bond Packages (Part 2 of 2)

| I/O Standard                  | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------|-------------------|-------------------|-------------------|------|

| LVCMOS                        | 422               | 390               | 390               | MHz  |

| GTL+                          | 250               | 200               | 200               | MHz  |

| SSTL-3 Class I                | 350               | 300               | 300               | MHz  |

| SSTL-3 Class II               | 350               | 300               | 300               | MHz  |

| SSTL-2 Class I                | 350               | 300               | 300               | MHz  |

| SSTL-2 Class II               | 350               | 300               | 300               | MHz  |

| SSTL-18 Class I               | 350               | 300               | 300               | MHz  |

| SSTL-18 Class II              | 350               | 300               | 300               | MHz  |

| 1.5-V HSTL Class I            | 350               | 300               | 300               | MHz  |

| 1.8-V HSTL Class I            | 350               | 300               | 300               | MHz  |

| CTT                           | 250               | 200               | 200               | MHz  |

| Differential 1.5-V HSTL<br>C1 | 350               | 300               | 300               | MHz  |

| LVPECL (1)                    | 717               | 640               | 640               | MHz  |

| PCML (1)                      | 375               | 350               | 350               | MHz  |

| LVDS (1)                      | 717               | 640               | 640               | MHz  |

| HyperTransport technology (1) | 717               | 640               | 640               | MHz  |

Table 4–119. Stratix Maximum Input Clock Rate for CLK[1, 3, 8, 10] Pins in Wire-Bond Packages (Part 1 of 2)

| I/O Standard    | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-----------------|-------------------|-------------------|-------------------|------|

| LVTTL           | 422               | 390               | 390               | MHz  |

| 2.5 V           | 422               | 390               | 390               | MHz  |

| 1.8 V           | 422               | 390               | 390               | MHz  |

| 1.5 V           | 422               | 390               | 390               | MHz  |

| LVCMOS          | 422               | 390               | 390               | MHz  |

| GTL+            | 250               | 200               | 200               | MHz  |

| SSTL-3 Class I  | 350               | 300               | 300               | MHz  |

| SSTL-3 Class II | 350               | 300               | 300               | MHz  |

| SSTL-2 Class I  | 350               | 300               | 300               | MHz  |

| SSTL-2 Class II | 350               | 300               | 300               | MHz  |

Table 4–122. Stratix Maximum Output Clock Rate for PLL[5, 6, 11, 12] Pins in Wire-Bond Packages (Part 2 of 2)

| I/O Standard                  | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------|-------------------|-------------------|-------------------|------|

| LVDS (2)                      | 311               | 275               | 275               | MHz  |

| HyperTransport technology (2) | 311               | 275               | 275               | MHz  |

Table 4–123. Stratix Maximum Output Clock Rate (Using I/O Pins) for PLL[1, 2, 3, 4] Pins in Wire-Bond Packages (Part 1 of 2)

| I/O Standard        | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|---------------------|-------------------|-------------------|-------------------|------|

| LVTTL               | 200               | 175               | 175               | MHz  |

| 2.5 V               | 200               | 175               | 175               | MHz  |

| 1.8 V               | 200               | 175               | 175               | MHz  |

| 1.5 V               | 200               | 175               | 175               | MHz  |

| LVCMOS              | 200               | 175               | 175               | MHz  |

| GTL                 | 125               | 100               | 100               | MHz  |

| GTL+                | 125               | 100               | 100               | MHz  |

| SSTL-3 Class I      | 110               | 90                | 90                | MHz  |

| SSTL-3 Class II     | 150               | 133               | 133               | MHz  |

| SSTL-2 Class I      | 90                | 80                | 80                | MHz  |

| SSTL-2 Class II     | 110               | 100               | 100               | MHz  |

| SSTL-18 Class I     | 110               | 100               | 100               | MHz  |

| SSTL-18 Class II    | 110               | 100               | 100               | MHz  |

| 1.5-V HSTL Class I  | 225               | 200               | 200               | MHz  |

| 1.5-V HSTL Class II | 200               | 167               | 167               | MHz  |

| 1.8-V HSTL Class I  | 225               | 200               | 200               | MHz  |

| 1.8-V HSTL Class II | 200               | 167               | 167               | MHz  |

| 3.3-V PCI           | 200               | 175               | 175               | MHz  |

| 3.3-V PCI-X 1.0     | 200               | 175               | 175               | MHz  |

| Compact PCI         | 200               | 175               | 175               | MHz  |

| AGP 1×              | 200               | 175               | 175               | MHz  |

| AGP 2×              | 200               | 175               | 175               | MHz  |

| CTT                 | 125               | 100               | 100               | MHz  |

| LVPECL (2)          | 311               | 270               | 270               | MHz  |

| PCML (2)            | 400               | 311               | 311               | MHz  |

| Fast Regional Clock External I/O Timing            | I                                                           |

|----------------------------------------------------|-------------------------------------------------------------|

| Parameters 4–49                                    | I/O                                                         |

| Global Clock External I/O Timing                   | Standards                                                   |

| Parameters 4–50 Regional Clock External I/O Timing | 1.5-V 4-14, 4-15                                            |

| Parameters 4–50                                    | I/O Specifications 4–4                                      |

| EP1S60 Devices                                     | 1.8-V                                                       |

| Column Pin                                         | I/O Specifications 4–4                                      |

| Fast Regional Clock External I/O Timing            | 2.5-V                                                       |

| Parameters 4–51                                    | I/O Specifications 4–3                                      |

| Global Clock External I/O Timing                   | 3.3-V 4–13                                                  |

| Parameters 4–52                                    | LVDS I/O Specifications 4–6                                 |

| Regional Clock External I/O Timing                 | PCI Specifications 4–9                                      |

| Parameters 4–51                                    | PCML Specifications 4–8                                     |

| M-RAM                                              | Advanced I/O Standard Support 2–122                         |

| Interface Locations 2–38                           | Column I/O Block Connection to the                          |

| Row Pin                                            | Interconnect 2–107                                          |

| Fast Regional Clock External I/O Timing            | Column Pin                                                  |

| Parameters 4–52                                    | Input Delay Adders 4–66                                     |

| Global Clock External I/O Timing                   | Control Signal Selection per IOE 2–109                      |

| Parameters 4–53                                    | CTT I/O Specifications 4–16                                 |

| Regional Clock External I/O Timing                 | Differential LVDS Input On-Chip                             |

| Parameters 4–53                                    | Termination 2–128                                           |

| EP1S80 Devices                                     | External I/O Delay Parameters 4–66                          |

| Column Pin                                         | GTL+ I/O Specifications 4–10<br>High-Speed Differential I/O |

| Fast Regional Clock External I/O Timing            | Support 2–130                                               |

| Parameters 4–54                                    | HyperTransport Technology                                   |

| Global Clock External I/O Timing                   | Specifications 4–9                                          |

| Parameters 4–55                                    | I/O Banks 2–125                                             |

| Regional Clock External I/O Timing                 | I/O Structure 2–104                                         |

| Parameters 4–54                                    | I/O Support by Bank 2–126                                   |

| Global Clock External I/O Timing                   | IOE Structure 2–105                                         |

| Parameters 4–56                                    | LVCMOS Specifications 4–3                                   |

| Row Pin                                            | LVDS Performance on Fast PLL                                |

| Fast Regional Clock External I/O Timing            | Input 2–103                                                 |

| Parameters 4–55                                    | LVPECL Specifications 4–8                                   |

| Regional Clock External I/O Timing                 | LVTTL Specifications 4–3                                    |

| Parameters 4–56                                    | MultiVolt I/O Interface 2–129                               |

|                                                    | MultiVolt I/O Support 2–130                                 |

| H                                                  | Output Delay Adders for Fast Slew Rate                      |

| HSTL                                               | on Column Pins 4–68                                         |

| Class I Specifications 4–14, 4–15                  | Output Delay Adders for Fast Slew Rate                      |

| Class II Specifications 4–14, 4–15                 | on Row Pins 4–69                                            |

| Ciass II Specifications 4-14, 4-15                 | Output Delay Adders for Slow Slew Rate                      |

|                                                    | on Column Pins 4–70                                         |

|                                                    | Package Options & I/O Pin Counts 1–4                        |

|                                                    | Receiver Input Waveforms for Differential                   |

Index-4 Altera Corporation