Welcome to E-XFL.COM

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 3247                                                     |

| Number of Logic Elements/Cells | 32470                                                    |

| Total RAM Bits                 | 3317184                                                  |

| Number of I/O                  | 597                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 780-BBGA, FCBGA                                          |

| Supplier Device Package        | 780-FBGA (29x29)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s30f780c7n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### M512 RAM Block

The M512 RAM block is a simple dual-port memory block and is useful for implementing small FIFO buffers, DSP, and clock domain transfer applications. Each block contains 576 RAM bits (including parity bits). M512 RAM blocks can be configured in the following modes:

- Simple dual-port RAM

- Single-port RAM

- FIFO

- ROM

- Shift register

When configured as RAM or ROM, you can use an initialization file to pre-load the memory contents.

The memory address depths and output widths can be configured as  $512 \times 1,256 \times 2,128 \times 4,64 \times 8$  ( $64 \times 9$  bits with parity), and  $32 \times 16$  ( $32 \times 18$  bits with parity). Mixed-width configurations are also possible, allowing different read and write widths. Table 2–4 summarizes the possible M512 RAM block configurations.

| Table 2-4 | Table 2–4. M512 RAM Block Configurations (Simple Dual-Port RAM) |          |          |          |          |          |          |

|-----------|-----------------------------------------------------------------|----------|----------|----------|----------|----------|----------|

| Dood Dow  | Write Port                                                      |          |          |          |          |          |          |

| Read Port | 512 × 1                                                         | 256 × 2  | 128 × 4  | 64 × 8   | 32 × 16  | 64 × 9   | 32 × 18  |

| 512 × 1   | <b>✓</b>                                                        | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |

| 256 × 2   | <b>✓</b>                                                        | ~        | ~        | <b>✓</b> | ~        |          |          |

| 128 × 4   | <b>✓</b>                                                        | ~        | ~        |          | ~        |          |          |

| 64 × 8    | <b>✓</b>                                                        | ~        |          | <b>✓</b> |          |          |          |

| 32 × 16   | <b>✓</b>                                                        | ~        | ~        |          | ~        |          |          |

| 64 × 9    |                                                                 |          |          |          |          | <b>✓</b> |          |

| 32 × 18   |                                                                 |          |          |          |          |          | <b>✓</b> |

When the M512 RAM block is configured as a shift register block, a shift register of size up to 576 bits is possible.

The M512 RAM block can also be configured to support serializer and deserializer applications. By using the mixed-width support in combination with DDR I/O standards, the block can function as a SERDES to support low-speed serial I/O standards using global or regional clocks. See "I/O Structure" on page 2–104 for details on dedicated SERDES in Stratix devices.

| Table 2–9. M-RAM Block Configurations (True Dual-Port) |          |          |          |          |  |

|--------------------------------------------------------|----------|----------|----------|----------|--|

| Dovt A                                                 | Port B   |          |          |          |  |

| Port A                                                 | 64K × 9  | 32K × 18 | 16K × 36 | 8K × 72  |  |

| 64K × 9                                                | <b>✓</b> | ✓        | ✓        | <b>✓</b> |  |

| 32K × 18                                               | ✓        | ✓        | ✓        | <b>✓</b> |  |

| 16K × 36                                               | <b>✓</b> | ✓        | ✓        | ✓        |  |

| 8K × 72                                                | ✓        | ✓        | ✓        | <b>✓</b> |  |

The read and write operation of the memory is controlled by the WREN signal, which sets the ports into either read or write modes. There is no separate read enable (RE) signal.

Writing into RAM is controlled by both the WREN and byte enable (byteena) signals for each port. The default value for the byteena signal is high, in which case writing is controlled only by the WREN signal. The byte enables are available for the ×18, ×36, and ×72 modes. In the ×144 simple dual-port mode, the two sets of byteena signals (byteena\_a and byteena\_b) are combined to form the necessary 16 byte enables. Tables 2–10 and 2–11 summarize the byte selection.

| Table 2–10. Byte Enable for M-RAM Blocks Notes (1), (2) |            |            |            |

|---------------------------------------------------------|------------|------------|------------|

| byteena[30]                                             | datain ×18 | datain ×36 | datain ×72 |

| [0] = 1                                                 | [80]       | [80]       | [80]       |

| [1] = 1                                                 | [179]      | [179]      | [179]      |

| [2] = 1                                                 | _          | [2618]     | [2618]     |

| [3] = 1                                                 | -          | [3527]     | [3527]     |

| [4] = 1                                                 | _          | _          | [4436]     |

| [5] = 1                                                 | _          | _          | [5345]     |

| [6] = 1                                                 | _          | _          | [6254]     |

| [7] = 1                                                 | _          | _          | [7163]     |

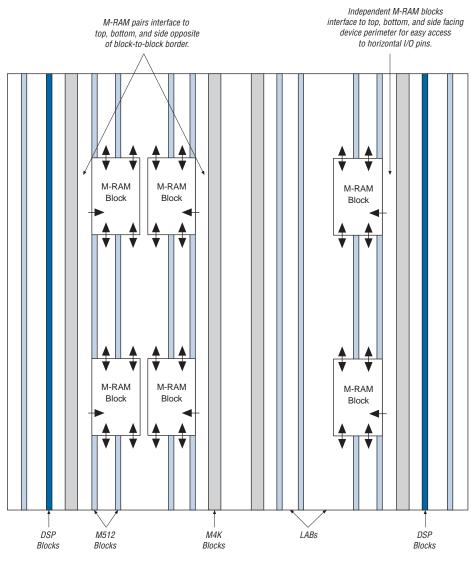

Figure 2–20. EP1S60 Device with M-RAM Interface Locations Note (1)

*Note to Figure 2–20:*

(1) Device shown is an EP1S60 device. The number and position of M-RAM blocks varies in other devices.

The M-RAM block local interconnect is driven by the R4, R8, C4, C8, and direct link interconnects from adjacent LABs. For independent M-RAM blocks, up to 10 direct link address and control signal input connections to the M-RAM block are possible from the left adjacent LABs for M-RAM

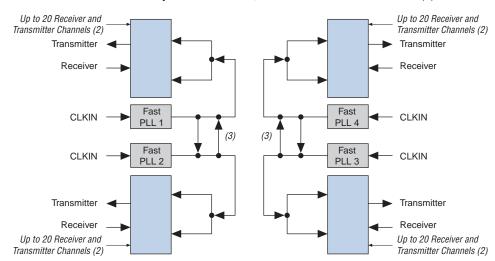

*Note to Figure 2–42:*

(1) The corner fast PLLs can also be driven through the global or regional clock networks. The global or regional clock input to the fast PLL can be driven by an output from another PLL, a pin-driven global or regional clock, or internallygenerated global signals.

## Regional Clock Network

There are four regional clock networks within each quadrant of the Stratix device that are driven by the same dedicated CLK[15..0] input pins or from PLL outputs. From a top view of the silicon, RCLK [0..3] are in the top left quadrant, RCLK[8..11] are in the top-right quadrant, RCLK[4..7] are in the bottom-left quadrant, and RCLK[12..15] are in the bottom-right quadrant. The regional clock networks only pertain to the quadrant they drive into. The regional clock networks provide the lowest clock delay and skew for logic contained within a single quadrant. RCLK cannot be driven by internal logic. The CLK clock pins symmetrically drive the RCLK networks within a particular quadrant, as shown in Figure 2–43. See Figures 2–50 and 2–51 for RCLK connections from PLLs and CLK pins.

Post-Scale Counters → diffioclk1 (2) Global or ÷/0 regional clock txload\_en (3) VCO Phase Selection Selectable at each PLL Output Port Phase rxload\_en (3) Frequency ÷/1 Global or Detector Global or regional clock regional clock (1) ► diffioclk2 (2) Charge Loop Global or PFD VCO ÷ g0 Clock □ Pump Filter regional clock Input [  $\pm m$

Figure 2-58. Stratix Device Fast PLL

#### *Notes to Figure 2–58:*

- The global or regional clock input can be driven by an output from another PLL or any dedicated CLK or FCLK pin.

It cannot be driven by internally-generated global signals.

- (2) In high-speed differential I/O support mode, this high-speed PLL clock feeds the SERDES. Stratix devices only support one rate of data transfer per fast PLL in high-speed differential I/O support mode.

- (3) This signal is a high-speed differential I/O support SERDES control signal.

### Clock Multiplication & Division

Stratix device fast PLLs provide clock synthesis for PLL output ports using m/(post scaler) scaling factors. The input clock is multiplied by the m feedback factor. Each output port has a unique post scale counter to divide down the high-frequency VCO. There is one multiply divider, m, per fast PLL with a range of 1 to 32. There are two post scale L dividers for regional and/or LVDS interface clocks, and g0 counter for global clock output port; all range from 1 to 32.

In the case of a high-speed differential interface, set the output counter to 1 to allow the high-speed VCO frequency to drive the SERDES. When used for clocking the SERDES, the m counter can range from 1 to 30. The VCO frequency is equal to  $f_{\rm IN}\times m$ , where VCO frequency must be between 300 and 1000 MHz.

| Table 2–32. I/O Support by Bank (Part 2 of 2) |                                     |                                     |                                                                 |  |

|-----------------------------------------------|-------------------------------------|-------------------------------------|-----------------------------------------------------------------|--|

| I/O Standard                                  | Top & Bottom Banks<br>(3, 4, 7 & 8) | Left & Right Banks<br>(1, 2, 5 & 6) | Enhanced PLL External<br>Clock Output Banks<br>(9, 10, 11 & 12) |  |

| SSTL-3 Class II                               | ✓                                   | ✓                                   | ✓                                                               |  |

| AGP (1× and 2×)                               | ✓                                   |                                     | ✓                                                               |  |

| CTT                                           | ✓                                   | ✓                                   | ✓                                                               |  |

Each I/O bank has its own VCCIO pins. A single device can support 1.5-, 1.8-, 2.5-, and 3.3-V interfaces; each bank can support a different standard independently. Each bank also has dedicated VREF pins to support any one of the voltage-referenced standards (such as SSTL-3) independently.

Each I/O bank can support multiple standards with the same  $V_{\rm CCIO}$  for input and output pins. Each bank can support one voltage-referenced I/O standard. For example, when  $V_{\rm CCIO}$  is 3.3 V, a bank can support LVTTL, LVCMOS, 3.3-V PCI, and SSTL-3 for inputs and outputs.

### **Differential On-Chip Termination**

Stratix devices provide differential on-chip termination (LVDS I/O standard) to reduce reflections and maintain signal integrity. Differential on-chip termination simplifies board design by minimizing the number of external termination resistors required. Termination can be placed inside the package, eliminating small stubs that can still lead to reflections. The internal termination is designed using transistors in the linear region of operation.

Stratix devices support internal differential termination with a nominal resistance value of 137.5  $\Omega$  for LVDS input receiver buffers. LVPECL signals require an external termination resistor. Figure 2–71 shows the device with differential termination.

The Quartus II MegaWizard® Plug-In Manager only allows the implementation of up to 20 receiver or 20 transmitter channels for each fast PLL. These channels operate at up to 840 Mbps. The receiver and transmitter channels are interleaved such that each I/O bank on the left and right side of the device has one receiver channel and one transmitter channel per LAB row. Figure 2–74 shows the fast PLL and channel layout in EP1S10, EP1S20, and EP1S25 devices. Figure 2–75 shows the fast PLL and channel layout in the EP1S30 to EP1S80 devices.

Figure 2-74. Fast PLL & Channel Layout in the EP1S10, EP1S20 or EP1S25 Devices Note (1)

#### Notes to Figure 2-74:

- Wire-bond packages support up to 624 Mbps.

- (2) See Table 2–41 for the number of channels each device supports.

- (3) There is a multiplexer here to select the PLL clock source. If a PLL uses this multiplexer to clock channels outside of its bank quadrant, those clocked channels support up to 840 Mbps for "high" speed channels and 462 Mbps for "low" speed channels, as labeled in the device pin-outs at www.altera.com.

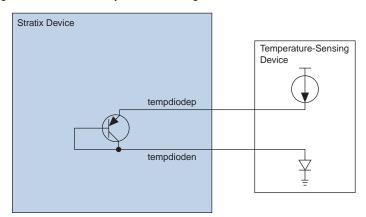

Figure 3-5. External Temperature-Sensing Diode

Table 3–6 shows the specifications for bias voltage and current of the Stratix temperature sensing diode.

| Table 3–6. Temperature-Sensing Diode Electrical Characteristics |         |         |         |      |  |

|-----------------------------------------------------------------|---------|---------|---------|------|--|

| Parameter                                                       | Minimum | Typical | Maximum | Unit |  |

| I <sub>BIAS</sub> high                                          | 80      | 100     | 120     | μΑ   |  |

| I <sub>BIAS</sub> low                                           | 8       | 10      | 12      | μΑ   |  |

| $V_{BP} - V_{BN}$                                               | 0.3     |         | 0.9     | V    |  |

| V <sub>BN</sub>                                                 |         | 0.7     |         | V    |  |

| Series resistance                                               |         |         | 3       | W    |  |

# 4. DC & Switching Characteristics

\$51004-3.4

# Operating Conditions

Stratix® devices are offered in both commercial and industrial grades. Industrial devices are offered in -6 and -7 speed grades and commercial devices are offered in -5 (fastest), -6, -7, and -8 speed grades. This section specifies the operation conditions for operating junction temperature,  $V_{\text{CCINT}}$  and  $V_{\text{CCIO}}$  voltage levels, and input voltage requirements. The voltage specifications in this section are specified at the pins of the device (and not the power supply). If the device operates outside these ranges, then all DC and AC specifications are not guaranteed. Furthermore, the reliability of the device may be affected. The timing parameters in this chapter apply to both commercial and industrial temperature ranges unless otherwise stated.

Tables 4–1 through 4–8 provide information on absolute maximum ratings.

| Table 4-1          | Table 4–1. Stratix Device Absolute Maximum Ratings Notes (1), (2) |                         |         |         |      |  |  |

|--------------------|-------------------------------------------------------------------|-------------------------|---------|---------|------|--|--|

| Symbol             | Parameter                                                         | Conditions              | Minimum | Maximum | Unit |  |  |

| V <sub>CCINT</sub> | Supply voltage                                                    | With respect to ground  | -0.5    | 2.4     | V    |  |  |

| V <sub>CCIO</sub>  |                                                                   |                         | -0.5    | 4.6     | V    |  |  |

| Vı                 | DC input voltage (3)                                              |                         | -0.5    | 4.6     | V    |  |  |

| I <sub>OUT</sub>   | DC output current, per pin                                        |                         | -25     | 40      | mA   |  |  |

| T <sub>STG</sub>   | Storage temperature                                               | No bias                 | -65     | 150     | °C   |  |  |

| T <sub>J</sub>     | Junction temperature                                              | BGA packages under bias |         | 135     | °C   |  |  |

| Table 4–2. Stratix Device Recommended Operating Conditions (Part 1 of 2) |                                                     |            |         |         |      |

|--------------------------------------------------------------------------|-----------------------------------------------------|------------|---------|---------|------|

| Symbol                                                                   | Parameter                                           | Conditions | Minimum | Maximum | Unit |

| V <sub>CCINT</sub>                                                       | Supply voltage for internal logic and input buffers | (4)        | 1.425   | 1.575   | V    |

| Symbol            | Parameter                                          | Conditions         | Minimum      | Maximum           | Unit |

|-------------------|----------------------------------------------------|--------------------|--------------|-------------------|------|

| V <sub>CCIO</sub> | Supply voltage for output buffers, 3.3-V operation | (4), (5)           | 3.00 (3.135) | 3.60 (3.465)      | V    |

|                   | Supply voltage for output buffers, 2.5-V operation | (4)                | 2.375        | 2.625             | ٧    |

|                   | Supply voltage for output buffers, 1.8-V operation | (4)                | 1.71         | 1.89              | ٧    |

|                   | Supply voltage for output buffers, 1.5-V operation | (4)                | 1.4          | 1.6               | ٧    |

| VI                | Input voltage                                      | (3), (6)           | -0.5         | 4.0               | V    |

| V <sub>O</sub>    | Output voltage                                     |                    | 0            | V <sub>CCIO</sub> | V    |

| TJ                | Operating junction                                 | For commercial use | 0            | 85                | °C   |

|                   | temperature                                        | For industrial use | -40          | 100               | °C   |

| Table 4–3. Stratix Device DC Operating Conditions Note (7) (Part 1 of 2) |                                               |                                                              |         |         |         |      |

|--------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------|---------|---------|---------|------|

| Symbol                                                                   | Parameter                                     | Conditions                                                   | Minimum | Typical | Maximum | Unit |

| I <sub>I</sub>                                                           | Input pin leakage current                     | $V_I = V_{CCIOmax}$ to 0 V (8)                               | -10     |         | 10      | μА   |

| I <sub>OZ</sub>                                                          | Tri-stated I/O pin leakage current            | V <sub>O</sub> = V <sub>CCIOmax</sub> to 0 V (8)             | -10     |         | 10      | μА   |

| I <sub>CC0</sub>                                                         | V <sub>CC</sub> supply current (standby) (All | V <sub>I</sub> = ground, no load, no toggling inputs         |         |         |         | mA   |

|                                                                          | memory blocks in power-down mode)             | EP1S10. V <sub>I</sub> = ground, no load, no toggling inputs |         | 37      |         | mA   |

|                                                                          |                                               | EP1S20. V <sub>I</sub> = ground, no load, no toggling inputs |         | 65      |         | mA   |

|                                                                          |                                               | EP1S25. V <sub>I</sub> = ground, no load, no toggling inputs |         | 90      |         | mA   |

|                                                                          |                                               | EP1S30. V <sub>I</sub> = ground, no load, no toggling inputs |         | 114     |         | mA   |

|                                                                          |                                               | EP1S40. V <sub>I</sub> = ground, no load, no toggling inputs |         | 145     |         | mA   |

|                                                                          |                                               | EP1S60. V <sub>I</sub> = ground, no load, no toggling inputs |         | 200     |         | mA   |

|                                                                          |                                               | EP1S80. V <sub>I</sub> = ground, no load, no toggling inputs |         | 277     |         | mA   |

| Table 4–33. Stratix Device Capacitance Note (5) |                                                                                                                             |         |         |         |      |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|------|

| Symbol                                          | Parameter                                                                                                                   | Minimum | Typical | Maximum | Unit |

| C <sub>IOTB</sub>                               | Input capacitance on I/O pins in I/O banks 3, 4, 7, and 8.                                                                  |         | 11.5    |         | pF   |

| C <sub>IOLR</sub>                               | Input capacitance on I/O pins in I/O banks 1, 2, 5, and 6, including high-speed differential receiver and transmitter pins. |         | 8.2     |         | pF   |

| C <sub>CLKTB</sub>                              | Input capacitance on top/bottom clock input pins: CLK [4:7] and CLK [12:15].                                                |         | 11.5    |         | pF   |

| C <sub>CLKLR</sub>                              | Input capacitance on left/right clock inputs: CLK1, CLK3, CLK8, CLK10.                                                      |         | 7.8     |         | pF   |

| C <sub>CLKLR+</sub>                             | Input capacitance on left/right clock inputs: CLK0, CLK2, CLK9, and CLK11.                                                  |         | 4.4     |         | pF   |

#### Notes to Tables 4–10 through 4–33:

- (1) When  $tx_outclock$  port of altlvds\_tx megafunction is 717 MHz,  $V_{OD(min)} = 235$  mV on the output clock pin.

- (2) Pin pull-up resistance values will lower if an external source drives the pin higher than V<sub>CCIO</sub>.

- (3) Drive strength is programmable according to the values shown in the *Stratix Architecture* chapter of the *Stratix Device Handbook, Volume 1*.

- (4) V<sub>REF</sub> specifies the center point of the switching range.

- (5) Capacitance is sample-tested only. Capacitance is measured using time-domain reflections (TDR). Measurement accuracy is within ±0.5 pF.

- (6)  $V_{IO}$  and  $V_{CM}$  have multiple ranges and values for J=1 through 10.

# Power Consumption

Altera® offers two ways to calculate power for a design: the Altera web power calculator and the PowerGauge<sup>TM</sup> feature in the Quartus® II software.

The interactive power calculator on the Altera web site is typically used prior to designing the FPGA in order to get a magnitude estimate of the device power. The Quartus II software PowerGauge feature allows you to apply test vectors against your design for more accurate power consumption modeling.

In both cases, these calculations should only be used as an estimation of power, not as a specification.

Stratix devices require a certain amount of power-up current to successfully power up because of the small process geometry on which they are fabricated.

Table 4–34 shows the maximum power-up current ( $I_{CCINT}$ ) required to power a Stratix device. This specification is for commercial operating conditions. Measurements were performed with an isolated Stratix device on the board to characterize the power-up current of an isolated

| Table 4–39. DSP              | Block Internal Timing Microparameter Descriptions                                                                                                                                                                                                                                                                                                         |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                       | Parameter                                                                                                                                                                                                                                                                                                                                                 |

| t <sub>SU</sub>              | Input, pipeline, and output register setup time before clock                                                                                                                                                                                                                                                                                              |

| t <sub>H</sub>               | Input, pipeline, and output register hold time after clock                                                                                                                                                                                                                                                                                                |

| t <sub>co</sub>              | Input, pipeline, and output register clock-to-output delay                                                                                                                                                                                                                                                                                                |

| t <sub>INREG2PIPE9</sub>     | Input Register to DSP Block pipeline register in $9\times9$ -bit mode                                                                                                                                                                                                                                                                                     |

| t <sub>INREG2PIPE18</sub>    | Input Register to DSP Block pipeline register in 18 $\times$ 18-bit mode                                                                                                                                                                                                                                                                                  |

| t <sub>PIPE2OUTREG2ADD</sub> | DSP Block Pipeline Register to output register delay in Two-Multipliers Adder mode                                                                                                                                                                                                                                                                        |

| t <sub>PIPE2OUTREG4ADD</sub> | DSP Block Pipeline Register to output register delay in Four-Multipliers Adder mode                                                                                                                                                                                                                                                                       |

| t <sub>PD9</sub>             | Combinatorial input to output delay for $9 \times 9$                                                                                                                                                                                                                                                                                                      |

| t <sub>PD18</sub>            | Combinatorial input to output delay for 18 × 18                                                                                                                                                                                                                                                                                                           |

| t <sub>PD36</sub>            | Combinatorial input to output delay for $36 \times 36$                                                                                                                                                                                                                                                                                                    |

| t <sub>CLR</sub>             | Minimum clear pulse width                                                                                                                                                                                                                                                                                                                                 |

| t <sub>CLKHL</sub>           | Register minimum clock high or low time. This is a limit on the min time for the clock on the registers in these blocks. The actual performance is dependent upon the internal point-to-point delays in the blocks and may give slower performance as shown in Table 4–36 on page 4–20 and as reported by the timing analyzer in the Quartus II software. |

| Doromotor            | -5 Spee | d Grade | -6 Spee | d Grade | -7 Speed Grade |       | -8 Speed Grade |       | llm:4 |

|----------------------|---------|---------|---------|---------|----------------|-------|----------------|-------|-------|

| Parameter            | Min     | Max     | Min     | Max     | Min            | Max   | Min            | Max   | Unit  |

| t <sub>XZ</sub>      | 2.754   | 5.406   | 2.754   | 5.848   | 2.754          | 6.412 | 2.754          | 7.159 | ns    |

| t <sub>ZX</sub>      | 2.754   | 5.406   | 2.754   | 5.848   | 2.754          | 6.412 | 2.754          | 7.159 | ns    |

| t <sub>INSUPLL</sub> | 1.265   |         | 1.236   |         | 1.403          |       | 1.756          |       | ns    |

| t <sub>INHPLL</sub>  | 0.000   |         | 0.000   |         | 0.000          |       | 0.000          |       | ns    |

| toutcopll            | 1.068   | 2.302   | 1.068   | 2.483   | 1.068          | 2.510 | 1.068          | 2.423 | ns    |

| t <sub>XZPLL</sub>   | 1.008   | 2.176   | 1.008   | 2.351   | 1.008          | 2.386 | 1.008          | 2.308 | ns    |

| t <sub>ZXPLL</sub>   | 1.008   | 2.176   | 1.008   | 2.351   | 1.008          | 2.386 | 1.008          | 2.308 | ns    |

| Table 4-76. L      | Table 4–76. EP1S30 External I/O Timing on Row Pins Using Fast Regional Clock Networks |                |       |                                |       |                |       |                   |      |      |

|--------------------|---------------------------------------------------------------------------------------|----------------|-------|--------------------------------|-------|----------------|-------|-------------------|------|------|

| Davamatava         | -5 Spee                                                                               | -5 Speed Grade |       | ed Grade -7 Speed Grade -8 Spe |       | -6 Speed Grade |       | de -8 Speed Grade |      | Hait |

| Parameters         | Min                                                                                   | Max            | Min   | Max                            | Min   | Max            | Min   | Max               | Unit |      |

| t <sub>INSU</sub>  | 2.616                                                                                 |                | 2.808 |                                | 3.223 |                | 3.797 |                   | ns   |      |

| t <sub>INH</sub>   | 0.000                                                                                 |                | 0.000 |                                | 0.000 |                | 0.000 |                   | ns   |      |

| t <sub>outco</sub> | 2.542                                                                                 | 5.114          | 2.542 | 5.502                          | 2.542 | 5.965          | 2.542 | 6.581             | ns   |      |

| t <sub>XZ</sub>    | 2.569                                                                                 | 5.168          | 2.569 | 5.558                          | 2.569 | 6.033          | 2.569 | 6.663             | ns   |      |

| t <sub>ZX</sub>    | 2.569                                                                                 | 5.168          | 2.569 | 5.558                          | 2.569 | 6.033          | 2.569 | 6.663             | ns   |      |

| Table 4-81. I         | EP1S40 Ext     | ternal I/O T | iming on C | Column Pin     | s Using Glo | obal Clock     | Networks |                |      |

|-----------------------|----------------|--------------|------------|----------------|-------------|----------------|----------|----------------|------|

| Davamatav             | -5 Speed Grade |              | -6 Spee    | -6 Speed Grade |             | -7 Speed Grade |          | -8 Speed Grade |      |

| Parameter             | Min            | Max          | Min        | Max            | Min         | Max            | Min      | Max            | Unit |

| t <sub>INSU</sub>     | 2.126          |              | 2.268      |                | 2.558       |                | 2.930    |                | ns   |

| t <sub>INH</sub>      | 0.000          |              | 0.000      |                | 0.000       |                | 0.000    |                | ns   |

| t <sub>OUTCO</sub>    | 2.856          | 5.585        | 2.856      | 5.987          | 2.856       | 6.541          | 2.847    | 7.253          | ns   |

| t <sub>XZ</sub>       | 2.796          | 5.459        | 2.796      | 5.855          | 2.796       | 6.417          | 2.787    | 7.138          | ns   |

| t <sub>ZX</sub>       | 2.796          | 5.459        | 2.796      | 5.855          | 2.796       | 6.417          | 2.787    | 7.138          | ns   |

| t <sub>INSUPLL</sub>  | 1.466          |              | 1.455      |                | 1.711       |                | 1.906    |                | ns   |

| t <sub>INHPLL</sub>   | 0.000          |              | 0.000      |                | 0.000       |                | 0.000    |                | ns   |

| t <sub>OUTCOPLL</sub> | 1.092          | 2.345        | 1.092      | 2.510          | 1.092       | 2.455          | 1.089    | 2.473          | ns   |

| t <sub>XZPLL</sub>    | 1.032          | 2.219        | 1.032      | 2.378          | 1.032       | 2.331          | 1.029    | 2.358          | ns   |

| t <sub>ZXPLL</sub>    | 1.032          | 2.219        | 1.032      | 2.378          | 1.032       | 2.331          | 1.029    | 2.358          | ns   |

| Table 4–82. I      | Table 4–82. EP1S40 External I/O Timing on Row Pins Using Fast Regional Clock Networks |                |       |                |       |         |               |       |      |  |

|--------------------|---------------------------------------------------------------------------------------|----------------|-------|----------------|-------|---------|---------------|-------|------|--|

| Daramatar          | -5 Spee                                                                               | -5 Speed Grade |       | -6 Speed Grade |       | d Grade | -8 Speed Grad |       | Unit |  |

| Parameter          | Min                                                                                   | Max            | Min   | Max            | Min   | Max     | Min           | Max   | Unit |  |

| t <sub>INSU</sub>  | 2.472                                                                                 |                | 2.685 |                | 3.083 |         | 3.056         |       | ns   |  |

| t <sub>INH</sub>   | 0.000                                                                                 |                | 0.000 |                | 0.000 |         | 0.000         |       | ns   |  |

| t <sub>OUTCO</sub> | 2.631                                                                                 | 5.258          | 2.631 | 5.625          | 2.631 | 6.105   | 2.745         | 7.324 | ns   |  |

| t <sub>XZ</sub>    | 2.658                                                                                 | 5.312          | 2.658 | 5.681          | 2.658 | 6.173   | 2.772         | 7.406 | ns   |  |

| t <sub>ZX</sub>    | 2.658                                                                                 | 5.312          | 2.658 | 5.681          | 2.658 | 6.173   | 2.772         | 7.406 | ns   |  |

| Davamatav            | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |     | l lmi4 |

|----------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-----|--------|

| Parameter            | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max | Unit   |

| t <sub>INSU</sub>    | 0.884          |       | 0.976          |       | 1.118          |       | NA             |     | ns     |

| t <sub>INH</sub>     | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns     |

| t <sub>outco</sub>   | 3.267          | 6.274 | 3.267          | 6.721 | 3.267          | 7.415 | NA             | NA  | ns     |

| t <sub>XZ</sub>      | 3.207          | 6.148 | 3.207          | 6.589 | 3.207          | 7.291 | NA             | NA  | ns     |

| t <sub>ZX</sub>      | 3.207          | 6.148 | 3.207          | 6.589 | 3.207          | 7.291 | NA             | NA  | ns     |

| t <sub>INSUPLL</sub> | 0.506          |       | 0.656          |       | 0.838          |       | NA             |     | ns     |

| t <sub>INHPLL</sub>  | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns     |

| toutcopll            | 1.635          | 2.805 | 1.635          | 2.809 | 1.635          | 2.828 | NA             | NA  | ns     |

| t <sub>XZPLL</sub>   | 1.575          | 2.679 | 1.575          | 2.677 | 1.575          | 2.704 | NA             | NA  | ns     |

| t <sub>ZXPLL</sub>   | 1.575          | 2.679 | 1.575          | 2.677 | 1.575          | 2.704 | NA             | NA  | ns     |

| Table 4–94. l      | Table 4–94. EP1S80 External I/O Timing on Row Pins Using Fast Regional Clock Networks Note (1) |                |       |                |       |                               |     |         |      |  |

|--------------------|------------------------------------------------------------------------------------------------|----------------|-------|----------------|-------|-------------------------------|-----|---------|------|--|

| Parameter          | -5 Spee                                                                                        | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade -8 Speed Grade |     | d Grade | Unit |  |

|                    | Min                                                                                            | Max            | Min   | Max            | Min   | Max                           | Min | Max     |      |  |

| t <sub>INSU</sub>  | 2.792                                                                                          |                | 2.993 |                | 3.386 |                               | NA  |         | ns   |  |

| t <sub>INH</sub>   | 0.000                                                                                          |                | 0.000 |                | 0.000 |                               | NA  |         | ns   |  |

| t <sub>outco</sub> | 2.619                                                                                          | 5.235          | 2.619 | 5.609          | 2.619 | 6.086                         | NA  | NA      | ns   |  |

| t <sub>XZ</sub>    | 2.646                                                                                          | 5.289          | 2.646 | 5.665          | 2.646 | 6.154                         | NA  | NA      | ns   |  |

| t <sub>ZX</sub>    | 2.646                                                                                          | 5.289          | 2.646 | 5.665          | 2.646 | 6.154                         | NA  | NA      | ns   |  |

| Table 4-95. E         | P1S80 Ext | ernal I/O T | iming on R     | ow Pins Us | sing Regio     | nal Clock N | letworks N             | ote (1) |      |

|-----------------------|-----------|-------------|----------------|------------|----------------|-------------|------------------------|---------|------|

| Parameter             | -5 Spee   | d Grade     | -6 Speed Grade |            | -7 Speed Grade |             | d Grade -8 Speed Grade |         | Unit |

|                       | Min       | Max         | Min            | Max        | Min            | Max         | Min                    | Max     |      |

| t <sub>INSU</sub>     | 2.295     |             | 2.454          |            | 2.767          |             | NA                     |         | ns   |

| t <sub>INH</sub>      | 0.000     |             | 0.000          |            | 0.000          |             | NA                     |         | ns   |

| t <sub>оитсо</sub>    | 2.917     | 5.732       | 2.917          | 6.148      | 2.917          | 6.705       | NA                     | NA      | ns   |

| t <sub>XZ</sub>       | 2.944     | 5.786       | 2.944          | 6.204      | 2.944          | 6.773       | NA                     | NA      | ns   |

| t <sub>ZX</sub>       | 2.944     | 5.786       | 2.944          | 6.204      | 2.944          | 6.773       | NA                     | NA      | ns   |

| t <sub>INSUPLL</sub>  | 1.011     |             | 1.161          |            | 1.372          |             | NA                     |         | ns   |

| t <sub>INHPLL</sub>   | 0.000     |             | 0.000          |            | 0.000          |             | NA                     |         | ns   |

| t <sub>OUTCOPLL</sub> | 1.808     | 3.169       | 1.808          | 3.209      | 1.808          | 3.233       | NA                     | NA      | ns   |

| t <sub>XZPLL</sub>    | 1.835     | 3.223       | 1.835          | 3.265      | 1.835          | 3.301       | NA                     | NA      | ns   |

| t <sub>ZXPLL</sub>    | 1.835     | 3.223       | 1.835          | 3.265      | 1.835          | 3.301       | NA                     | NA      | ns   |

| Table 4-96.           | Table 4–96. EP1S80 External I/O Timing on Rows Using Pin Global Clock Networks Note (1) |                   |       |                |       |         |         |         |      |  |  |

|-----------------------|-----------------------------------------------------------------------------------------|-------------------|-------|----------------|-------|---------|---------|---------|------|--|--|

| Cumbal                | -5 Spee                                                                                 | -5 Speed Grade -6 |       | -6 Speed Grade |       | d Grade | -8 Spee | d Grade | Heit |  |  |

| Symbol                | Min                                                                                     | Max               | Min   | Max            | Min   | Max     | Min     | Max     | Unit |  |  |

| t <sub>INSU</sub>     | 1.362                                                                                   |                   | 1.451 |                | 1.613 |         | NA      |         | ns   |  |  |

| t <sub>INH</sub>      | 0.000                                                                                   |                   | 0.000 |                | 0.000 |         | NA      |         | ns   |  |  |

| t <sub>outco</sub>    | 3.457                                                                                   | 6.665             | 3.457 | 7.151          | 3.457 | 7.859   | NA      | NA      | ns   |  |  |

| t <sub>XZ</sub>       | 3.484                                                                                   | 6.719             | 3.484 | 7.207          | 3.484 | 7.927   | NA      | NA      | ns   |  |  |

| t <sub>ZX</sub>       | 3.484                                                                                   | 6.719             | 3.484 | 7.207          | 3.484 | 7.927   | NA      | NA      | ns   |  |  |

| t <sub>INSUPLL</sub>  | 0.994                                                                                   |                   | 1.143 |                | 1.351 |         | NA      |         | ns   |  |  |

| t <sub>INHPLL</sub>   | 0.000                                                                                   |                   | 0.000 |                | 0.000 |         | NA      |         | ns   |  |  |

| t <sub>OUTCOPLL</sub> | 1.821                                                                                   | 3.186             | 1.821 | 3.227          | 1.821 | 3.254   | NA      | NA      | ns   |  |  |

| t <sub>XZPLL</sub>    | 1.848                                                                                   | 3.240             | 1.848 | 3.283          | 1.848 | 3.322   | NA      | NA      | ns   |  |  |

| t <sub>ZXPLL</sub>    | 1.848                                                                                   | 3.240             | 1.848 | 3.283          | 1.848 | 3.322   | NA      | NA      | ns   |  |  |

*Note to Tables 4–91 to 4–96:*

<sup>(1)</sup> Only EP1S25, EP1S30, and EP1S40 devices have the -8 speed grade.

Table 4–116. Stratix Maximum Input Clock Rate for CLK[1, 3, 8, 10] Pins in Flip-Chip Packages

| I/O Standard                  | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------|-------------------|-------------------|-------------------|-------------------|------|

| LVTTL                         | 422               | 422               | 390               | 390               | MHz  |

| 2.5 V                         | 422               | 422               | 390               | 390               | MHz  |

| 1.8 V                         | 422               | 422               | 390               | 390               | MHz  |

| 1.5 V                         | 422               | 422               | 390               | 390               | MHz  |

| LVCMOS                        | 422               | 422               | 390               | 390               | MHz  |

| GTL+                          | 300               | 250               | 200               | 200               | MHz  |

| SSTL-3 Class I                | 400               | 350               | 300               | 300               | MHz  |

| SSTL-3 Class II               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-2 Class I                | 400               | 350               | 300               | 300               | MHz  |

| SSTL-2 Class II               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-18 Class I               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-18 Class II              | 400               | 350               | 300               | 300               | MHz  |

| 1.5-V HSTL Class I            | 400               | 350               | 300               | 300               | MHz  |

| 1.8-V HSTL Class I            | 400               | 350               | 300               | 300               | MHz  |

| СТТ                           | 300               | 250               | 200               | 200               | MHz  |

| Differential 1.5-V HSTL<br>C1 | 400               | 350               | 300               | 300               | MHz  |

| LVPECL (1)                    | 645               | 645               | 640               | 640               | MHz  |

| PCML (1)                      | 300               | 275               | 275               | 275               | MHz  |

| LVDS (1)                      | 645               | 645               | 640               | 640               | MHz  |

| HyperTransport technology (1) | 500               | 500               | 450               | 450               | MHz  |

Table 4–117. Stratix Maximum Input Clock Rate for CLK[7..4] & CLK[15..12] Pins in Wire-Bond Packages (Part 1 of 2)

| I/O Standard | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|--------------|-------------------|-------------------|-------------------|------|

| LVTTL        | 422               | 390               | 390               | MHz  |

| 2.5 V        | 422               | 390               | 390               | MHz  |

| 1.8 V        | 422               | 390               | 390               | MHz  |

| 1.5 V        | 422               | 390               | 390               | MHz  |

| LVCMOS       | 422               | 390               | 390               | MHz  |

| GTL          | 250               | 200               | 200               | MHz  |

Table 4–121. Stratix Maximum Output Clock Rate (Using I/O Pins) for PLL[1, 2, 3, 4] Pins in Flip-Chip Packages

| I/O Standard                  | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------|-------------------|-------------------|-------------------|-------------------|------|

| LVTTL                         | 400               | 350               | 300               | 300               | MHz  |

| 2.5 V                         | 400               | 350               | 300               | 300               | MHz  |

| 1.8 V                         | 400               | 350               | 300               | 300               | MHz  |

| 1.5 V                         | 350               | 300               | 300               | 300               | MHz  |

| LVCMOS                        | 400               | 350               | 300               | 300               | MHz  |

| GTL                           | 200               | 167               | 125               | 125               | MHz  |

| GTL+                          | 200               | 167               | 125               | 125               | MHz  |

| SSTL-3 Class I                | 167               | 150               | 133               | 133               | MHz  |

| SSTL-3 Class II               | 167               | 150               | 133               | 133               | MHz  |

| SSTL-2 Class I                | 150               | 133               | 133               | 133               | MHz  |

| SSTL-2 Class II               | 150               | 133               | 133               | 133               | MHz  |

| SSTL-18 Class I               | 150               | 133               | 133               | 133               | MHz  |

| SSTL-18 Class II              | 150               | 133               | 133               | 133               | MHz  |

| 1.5-V HSTL Class I            | 250               | 225               | 200               | 200               | MHz  |

| 1.5-V HSTL Class II           | 225               | 225               | 200               | 200               | MHz  |

| 1.8-V HSTL Class I            | 250               | 225               | 200               | 200               | MHz  |

| 1.8-V HSTL Class II           | 225               | 225               | 200               | 200               | MHz  |

| 3.3-V PCI                     | 250               | 225               | 200               | 200               | MHz  |

| 3.3-V PCI-X 1.0               | 225               | 225               | 200               | 200               | MHz  |

| Compact PCI                   | 400               | 350               | 300               | 300               | MHz  |

| AGP 1×                        | 400               | 350               | 300               | 300               | MHz  |

| AGP 2×                        | 400               | 350               | 300               | 300               | MHz  |

| CTT                           | 300               | 250               | 200               | 200               | MHz  |

| LVPECL (2)                    | 717               | 717               | 500               | 500               | MHz  |

| PCML (2)                      | 420               | 420               | 420               | 420               | MHz  |

| LVDS (2)                      | 717               | 717               | 500               | 500               | MHz  |

| HyperTransport technology (2) | 420               | 420               | 420               | 420               | MHz  |

Table 4–122. Stratix Maximum Output Clock Rate for PLL[5, 6, 11, 12] Pins in Wire-Bond Packages (Part 2 of 2)

| I/O Standard                  | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------|-------------------|-------------------|-------------------|------|

| LVDS (2)                      | 311               | 275               | 275               | MHz  |

| HyperTransport technology (2) | 311               | 275               | 275               | MHz  |

Table 4–123. Stratix Maximum Output Clock Rate (Using I/O Pins) for PLL[1, 2, 3, 4] Pins in Wire-Bond Packages (Part 1 of 2)

| I/O Standard        | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |  |  |

|---------------------|-------------------|-------------------|-------------------|------|--|--|

| LVTTL               | 200               | 175               | 175               | MHz  |  |  |

| 2.5 V               | 200               | 175               | 175               | MHz  |  |  |

| 1.8 V               | 200               | 175               | 175               | MHz  |  |  |

| 1.5 V               | 200               | 175               | 175               | MHz  |  |  |

| LVCMOS              | 200               | 175               | 175               | MHz  |  |  |

| GTL                 | 125               | 100               | 100               | MHz  |  |  |

| GTL+                | 125               | 100               | 100               | MHz  |  |  |

| SSTL-3 Class I      | 110               | 90                | 90                | MHz  |  |  |

| SSTL-3 Class II     | 150               | 133               | 133               | MHz  |  |  |

| SSTL-2 Class I      | 90                | 80                | 80                | MHz  |  |  |

| SSTL-2 Class II     | 110               | 100               | 100               | MHz  |  |  |

| SSTL-18 Class I     | 110               | 100               | 100               | MHz  |  |  |

| SSTL-18 Class II    | 110               | 100               | 100               | MHz  |  |  |

| 1.5-V HSTL Class I  | 225               | 200               | 200               | MHz  |  |  |

| 1.5-V HSTL Class II | 200               | 167               | 167               | MHz  |  |  |

| 1.8-V HSTL Class I  | 225               | 200               | 200               | MHz  |  |  |

| 1.8-V HSTL Class II | 200               | 167               | 167               | MHz  |  |  |

| 3.3-V PCI           | 200               | 175               | 175               | MHz  |  |  |

| 3.3-V PCI-X 1.0     | 200               | 175               | 175               | MHz  |  |  |

| Compact PCI         | 200               | 175               | 175               | MHz  |  |  |

| AGP 1×              | 200               | 175               | 175               | MHz  |  |  |

| AGP 2×              | 200               | 175               | 175               | MHz  |  |  |

| CTT                 | 125               | 100               | 100               | MHz  |  |  |

| LVPECL (2)          | 311               | 270               | 270               | MHz  |  |  |

| PCML (2)            | 400               | 311               | 311               | MHz  |  |  |

| Symbol                                | Conditions                                                            | -6 Speed Grade |     | -7 Speed Grade |       |     | -8 Speed Grade |       |     |      |      |

|---------------------------------------|-----------------------------------------------------------------------|----------------|-----|----------------|-------|-----|----------------|-------|-----|------|------|

|                                       |                                                                       | Min            | Тур | Max            | Min   | Тур | Max            | Min   | Тур | Max  | Unit |

| SW                                    | PCML (J = 4, 7, 8, 10) only                                           | 800            |     |                | 800   |     |                | 800   |     |      | ps   |

|                                       | PCML (J = 2) only                                                     | 1,200          |     |                | 1,200 |     |                | 1,200 |     |      | ps   |

|                                       | PCML (J = 1) only                                                     | 1,700          |     |                | 1,700 |     |                | 1,700 |     |      | ps   |

|                                       | LVDS and LVPECL (J = 1) only                                          | 550            |     |                | 550   |     |                | 550   |     |      | ps   |

|                                       | LVDS, LVPECL,<br>HyperTransport technology<br>(J = 2 through 10) only | 500            |     |                | 500   |     |                | 500   |     |      | ps   |

| Input jitter tolerance (peak-to-peak) | All                                                                   |                |     | 250            |       |     | 250            |       |     | 250  | ps   |

| Output jitter (peak-to-<br>peak)      | All                                                                   |                |     | 200            |       |     | 200            |       |     | 200  | ps   |

| Output t <sub>RISE</sub>              | LVDS                                                                  | 80             | 110 | 120            | 80    | 110 | 120            | 80    | 110 | 120  | ps   |

|                                       | HyperTransport technology                                             | 120            | 170 | 200            | 120   | 170 | 200            | 120   | 170 | 200  | ps   |

|                                       | LVPECL                                                                | 100            | 135 | 150            | 100   | 135 | 150            | 100   | 135 | 150  | ps   |

|                                       | PCML                                                                  | 80             | 110 | 135            | 80    | 110 | 135            | 80    | 110 | 135  | ps   |

| Output t <sub>FALL</sub>              | LVDS                                                                  | 80             | 110 | 120            | 80    | 110 | 120            | 80    | 110 | 120  | ps   |

|                                       | HyperTransport                                                        | 110            | 170 | 200            | 110   | 170 | 200            | 110   | 170 | 200  | ps   |

|                                       | LVPECL                                                                | 100            | 135 | 160            | 100   | 135 | 160            | 100   | 135 | 160  | ps   |

|                                       | PCML                                                                  | 110            | 145 | 175            | 110   | 145 | 175            | 110   | 145 | 175  | ps   |

| touty                                 | LVDS (J = 2 through10) only                                           | 47.5           | 50  | 52.5           | 47.5  | 50  | 52.5           | 47.5  | 50  | 52.5 | %    |

|                                       | LVDS (J =1) and LVPECL,<br>PCML, HyperTransport<br>technology         | 45             | 50  | 55             | 45    | 50  | 55             | 45    | 50  | 55   | %    |

| t <sub>LOCK</sub>                     | All                                                                   |                |     | 100            |       |     | 100            |       |     | 100  | μs   |

Table 4–126. High-Speed I/O Specifications for Wire-Bond Packages (Part 2 of 2)