Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 3247                                                    |

| Number of Logic Elements/Cells | 32470                                                   |

| Total RAM Bits                 | 3317184                                                 |

| Number of I/O                  | 597                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                         |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 780-BBGA, FCBGA                                         |

| Supplier Device Package        | 780-FBGA (29x29)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s30f780c8 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Chapter | Date/Version        | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4       |                     | <ul> <li>Updated Table 4–123 on page 4–85 through Table 4–126 on page 4–92.</li> <li>Updated Note 3 in Table 4–123 on page 4–85.</li> <li>Table 4–125 on page 4–88: moved to correct order in chapter, and updated table.</li> <li>Updated Table 4–126 on page 4–92.</li> <li>Updated Table 4–127 on page 4–94.</li> <li>Updated Table 4–128 on page 4–95.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | April 2004, v3.0    | <ul> <li>Table 4–129 on page 4–96: updated table and added Note 10.</li> <li>Updated Table 4–131 and Table 4–132 on page 4–100.</li> <li>Updated Table 4–110 on page 4–74.</li> <li>Updated Table 4–123 on page 4–85.</li> <li>Updated Table 4–124 on page 4–87. through Table 4–126 on page 4–92.</li> <li>Added Note 10 to Table 4–129 on page 4–96.</li> <li>Moved Table 4–127 on page 4–94 to correct order in the chapter.</li> <li>Updated Table 4–131 on page 4–100 through Table 4–132 on page 4–100.</li> <li>Deleted t<sub>XZ</sub> and t<sub>ZX</sub> from Figure 4–4.</li> <li>Waveform was added to Figure 4–6.</li> <li>The minimum and maximum duty cycle values in Note 3 of Table 4–8 were moved to a new Table 4–9.</li> <li>Changes were made to values in SSTL-3 Class I and II rows in Table 4–17.</li> <li>Note 1 was added to Table 4–34.</li> <li>Added t<sub>SU_R</sub> and t<sub>SU_C</sub> rows in Table 4–38.</li> <li>Changed Table 4–55 title from "EP1S10 Column Pin Fast Regional Clock External I/O Timing Parameters" to "EP1S10 External I/O Timing on Column Pins Using Fast Regional Clock Networks."</li> <li>Changed values in Tables 4–46, 4–48 to 4–51, 4–128, and 4–131.</li> <li>Added t<sub>ARESET</sub> row in Tables 4–127 to 4–132.</li> <li>Deleted -5 Speed Grade column in Tables 4–117 to 4–119 and 4–122 to 4–123.</li> <li>Fixed differential waveform in Figure 4–1.</li> <li>Added "Definition of I/O Skew" section.</li> <li>Added d'Definition of I/O Skew" section.</li> <li>Added table 4–46.</li> <li>Values changed in the t<sub>MAKCLKHL</sub> row in Table 4–47.</li> <li>Values changed in the t<sub>MAKCLKHL</sub> row in Table 4–50.</li> <li>Added Table 4–51 to "Internal Timing Parameters" section.</li> <li>The timing information is preliminary in Tables 4–55 through 4–96.</li> <li>Table 4–111 was separated into 3 tables: Tables 4–111 to 4–113.</li> </ul> |

|         | November 2003, v2.2 | Updated Tables 4–127 through 4–129.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Section I–6 Altera Corporation

With the LAB-wide addnsub control signal, a single LE can implement a one-bit adder and subtractor. This saves LE resources and improves performance for logic functions such as DSP correlators and signed multipliers that alternate between addition and subtraction depending on data.

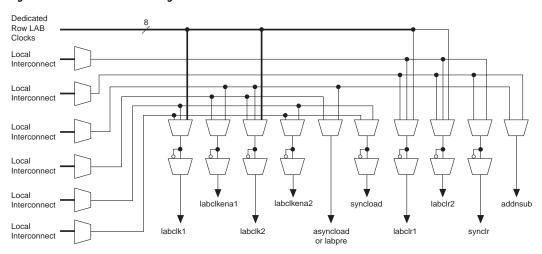

The LAB row clocks [7..0] and LAB local interconnect generate the LAB-wide control signals. The MultiTrack $^{\text{IM}}$  interconnect's inherent low skew allows clock and control signal distribution in addition to data. Figure 2–4 shows the LAB control signal generation circuit.

Figure 2-4. LAB-Wide Control Signals

# **Logic Elements**

The smallest unit of logic in the Stratix architecture, the LE, is compact and provides advanced features with efficient logic utilization. Each LE contains a four-input LUT, which is a function generator that can implement any function of four variables. In addition, each LE contains a programmable register and carry chain with carry select capability. A single LE also supports dynamic single bit addition or subtraction mode selectable by an LAB-wide control signal. Each LE drives all types of interconnects: local, row, column, LUT chain, register chain, and direct link interconnects. See Figure 2–5.

### **Shift Register Support**

You can configure embedded memory blocks to implement shift registers for DSP applications such as pseudo-random number generators, multichannel filtering, auto-correlation, and cross-correlation functions. These and other DSP applications require local data storage, traditionally implemented with standard flip-flops, which can quickly consume many logic cells and routing resources for large shift registers. A more efficient alternative is to use embedded memory as a shift register block, which saves logic cell and routing resources and provides a more efficient implementation with the dedicated circuitry.

The size of a  $w \times m \times n$  shift register is determined by the input data width (w), the length of the taps (m), and the number of taps (n). The size of a  $w \times m \times n$  shift register must be less than or equal to the maximum number of memory bits in the respective block: 576 bits for the M512 RAM block and 4,608 bits for the M4K RAM block. The total number of shift register outputs (number of taps  $n \times$  width w) must be less than the maximum data width of the RAM block (18 for M512 blocks, 36 for M4K blocks). To create larger shift registers, the memory blocks are cascaded together.

Data is written into each address location at the falling edge of the clock and read from the address at the rising edge of the clock. The shift register mode logic automatically controls the positive and negative edge clocking to shift the data in one clock cycle. Figure 2–14 shows the TriMatrix memory block in the shift register mode.

#### M-RAM Block

The largest TriMatrix memory block, the M-RAM block, is useful for applications where a large volume of data must be stored on-chip. Each block contains 589,824 RAM bits (including parity bits). The M-RAM block can be configured in the following modes:

- True dual-port RAM

- Simple dual-port RAM

- Single-port RAM

- FIFO RAM

You cannot use an initialization file to initialize the contents of a M-RAM block. All M-RAM block contents power up to an undefined value. Only synchronous operation is supported in the M-RAM block, so all inputs are registered. Output registers can be bypassed. The memory address and output width can be configured as  $64 \text{K} \times 8$  (or  $64 \text{K} \times 9$  bits),  $32 \text{K} \times 16$  (or  $32 \text{K} \times 18$  bits),  $16 \text{K} \times 32$  (or  $16 \text{K} \times 36$  bits),  $8 \text{K} \times 64$  (or  $8 \text{K} \times 72$  bits), and  $4 \text{K} \times 128$  (or  $4 \text{K} \times 144$  bits). The  $4 \text{K} \times 128$  configuration is unavailable in true dual-port mode because there are a total of 144 data output drivers in the block. Mixed-width configurations are also possible, allowing different read and write widths. Tables 2–8 and 2–9 summarize the possible M-RAM block configurations:

| Table 2–8. M-RAM Block Configurations (Simple Dual-Port) |            |          |          |          |          |  |  |  |  |

|----------------------------------------------------------|------------|----------|----------|----------|----------|--|--|--|--|

| Bood Bort                                                | Write Port |          |          |          |          |  |  |  |  |

| Read Port                                                | 64K × 9    | 32K × 18 | 16K × 36 | 8K × 72  | 4K × 144 |  |  |  |  |

| 64K × 9                                                  | <b>✓</b>   | <b>✓</b> | ✓        | <b>✓</b> |          |  |  |  |  |

| 32K × 18                                                 | ✓          | ✓        | ✓        | ✓        |          |  |  |  |  |

| 16K × 36                                                 | ✓          | ✓        | ✓        | ✓        |          |  |  |  |  |

| 8K × 72                                                  | <b>✓</b>   | <b>✓</b> | ✓        | <b>✓</b> |          |  |  |  |  |

| 4K × 144                                                 |            |          |          |          | ✓        |  |  |  |  |

Table 2–13 shows the number of DSP blocks in each Stratix device.

| Table 2–13. DSP Blocks in Stratix Devices Notes (1), (2) |            |                            |                              |                              |  |  |  |  |

|----------------------------------------------------------|------------|----------------------------|------------------------------|------------------------------|--|--|--|--|

| Device                                                   | DSP Blocks | Total 9 × 9<br>Multipliers | Total 18 × 18<br>Multipliers | Total 36 × 36<br>Multipliers |  |  |  |  |

| EP1S10                                                   | 6          | 48                         | 24                           | 6                            |  |  |  |  |

| EP1S20                                                   | 10         | 80                         | 40                           | 10                           |  |  |  |  |

| EP1S25                                                   | 10         | 80                         | 40                           | 10                           |  |  |  |  |

| EP1S30                                                   | 12         | 96                         | 48                           | 12                           |  |  |  |  |

| EP1S40                                                   | 14         | 112                        | 56                           | 14                           |  |  |  |  |

| EP1S60                                                   | 18         | 144                        | 72                           | 18                           |  |  |  |  |

| EP1S80                                                   | 22         | 176                        | 88                           | 22                           |  |  |  |  |

#### *Notes to Table 2–13:*

- (1) Each device has either the number of  $9 \times 9$ -,  $18 \times 18$ -, or  $36 \times 36$ -bit multipliers shown. The total number of multipliers for each device is not the sum of all the multipliers.

- (2) The number of supported multiply functions shown is based on signed/signed or unsigned/unsigned implementations.

DSP block multipliers can optionally feed an adder/subtractor or accumulator within the block depending on the configuration. This makes routing to LEs easier, saves LE routing resources, and increases performance, because all connections and blocks are within the DSP block. Additionally, the DSP block input registers can efficiently implement shift registers for FIR filter applications.

Figure 2–30 shows the top-level diagram of the DSP block configured for  $18 \times 18$ -bit multiplier mode. Figure 2–31 shows the  $9 \times 9$ -bit multiplier configuration of the DSP block.

There are 16 dedicated clock pins (CLK [15..0]) to drive either the global or regional clock networks. Four clock pins drive each side of the device, as shown in Figure 2–42. Enhanced and fast PLL outputs can also drive the global and regional clock networks.

#### Global Clock Network

These clocks drive throughout the entire device, feeding all device quadrants. The global clock networks can be used as clock sources for all resources within the device—IOEs, LEs, DSP blocks, and all memory blocks. These resources can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin. The global clock networks can also be driven by internal logic for internally generated global clocks and asynchronous clears, clock enables, or other control signals with large fanout. Figure 2–42 shows the 16 dedicated CLK pins driving global clock networks.

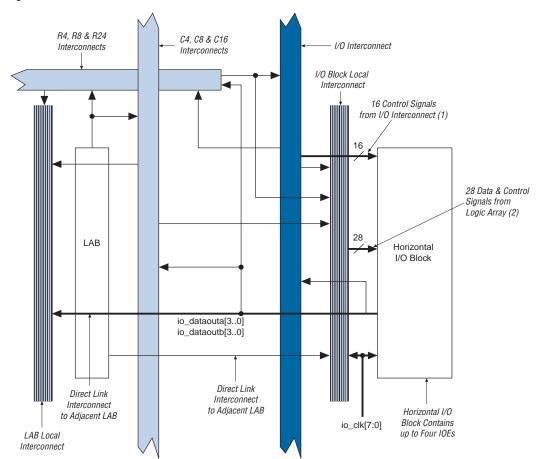

Figure 2-60. Row I/O Block Connection to the Interconnect

#### *Notes to Figure 2–60:*

- (1) The 16 control signals are composed of four output enables io\_boe[3..0], four clock enables io\_boe[3..0], four clocks io\_clk[3..0], and four clear signals io\_bclr[3..0].

- (2) The 28 data and control signals consist of eight data out lines: four lines each for DDR applications io\_dataouta[3..0] and io\_dataoutb[3..0], four output enables io\_coe[3..0], four input clock enables io\_cce\_in[3..0], four output clock enables io\_cce\_out[3..0], four clocks io\_cclk[3..0], and four clear signals io\_cclr[3..0].

Stratix devices have an I/O interconnect similar to the R4 and C4 interconnect to drive high-fanout signals to and from the I/O blocks. There are 16 signals that drive into the I/O blocks composed of four output enables <code>io\_boe[3..0]</code>, four clock enables <code>io\_bce[3..0]</code>, four clocks <code>io\_bclk[3..0]</code>, and four clear signals <code>io\_bclr[3..0]</code>. The pin's <code>datain</code> signals can drive the IO interconnect, which in turn drives the logic array or other I/O blocks. In addition, the control and data signals can be driven from the logic array, providing a slower but more flexible routing resource. The row or column IOE clocks, <code>io\_clk[7..0]</code>, provide a dedicated routing resource for low-skew, high-speed clocks. I/O clocks are generated from regional, global, or fast regional clocks (see "PLLs & Clock Networks" on page 2–73). Figure 2–62 illustrates the signal paths through the I/O block.

Row or Column io\_clk[7..0] io\_boe[3..0] To Other io\_bce[3..0] 10Es From I/O Interconnect io\_bclk[3..0] io\_bclr[3..0] io\_datain0 To Logic Array io datain1 ◀ oe ce\_in ce\_out io coe Control IOE aclr/apreset io cce in Signal Selection sclr/spreset io cce out clk in From Logic io\_cclr Array clk out io\_cclk io\_dataout0 io\_dataout1

Figure 2-62. Signal Path through the I/O Block

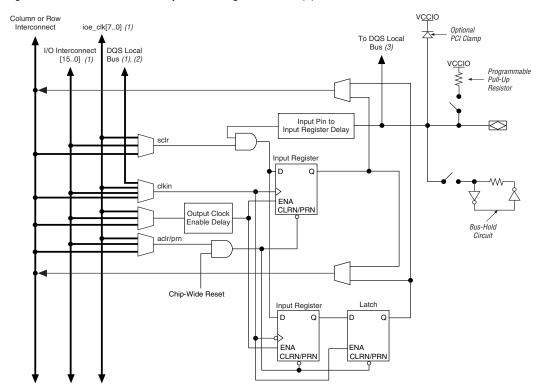

Figure 2–65. Stratix IOE in DDR Input I/O Configuration Note (1)

*Notes to Figure 2–65:*

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) This signal connection is only allowed on dedicated DQ function pins.

- (3) This signal is for dedicated DQS function pins only.

- 1.8-V HSTL Class I and II

- SSTL-3 Class I and II

- SSTL-2 Class I and II

- SSTL-18 Class I and II

- CTT

Table 2–31 describes the I/O standards supported by Stratix devices.

| Table 2–31. Stratix Supported I/O Standards |                    |                                                       |                                                      |                                                           |  |  |  |  |

|---------------------------------------------|--------------------|-------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------|--|--|--|--|

| I/O Standard                                | Туре               | Input Reference<br>Voltage (V <sub>REF</sub> )<br>(V) | Output Supply<br>Voltage (V <sub>CCIO</sub> )<br>(V) | Board<br>Termination<br>Voltage (V <sub>TT</sub> )<br>(V) |  |  |  |  |

| LVTTL                                       | Single-ended       | N/A                                                   | 3.3                                                  | N/A                                                       |  |  |  |  |

| LVCMOS                                      | Single-ended       | N/A                                                   | 3.3                                                  | N/A                                                       |  |  |  |  |

| 2.5 V                                       | Single-ended       | N/A                                                   | 2.5                                                  | N/A                                                       |  |  |  |  |

| 1.8 V                                       | Single-ended       | N/A                                                   | 1.8                                                  | N/A                                                       |  |  |  |  |

| 1.5 V                                       | Single-ended       | N/A                                                   | 1.5                                                  | N/A                                                       |  |  |  |  |

| 3.3-V PCI                                   | Single-ended       | N/A                                                   | 3.3                                                  | N/A                                                       |  |  |  |  |

| 3.3-V PCI-X 1.0                             | Single-ended       | N/A                                                   | 3.3                                                  | N/A                                                       |  |  |  |  |

| LVDS                                        | Differential       | N/A                                                   | 3.3                                                  | N/A                                                       |  |  |  |  |

| LVPECL                                      | Differential       | N/A                                                   | 3.3                                                  | N/A                                                       |  |  |  |  |

| 3.3-V PCML                                  | Differential       | N/A                                                   | 3.3                                                  | N/A                                                       |  |  |  |  |

| HyperTransport                              | Differential       | N/A                                                   | 2.5                                                  | N/A                                                       |  |  |  |  |

| Differential HSTL (1)                       | Differential       | 0.75                                                  | 1.5                                                  | 0.75                                                      |  |  |  |  |

| Differential SSTL (2)                       | Differential       | 1.25                                                  | 2.5                                                  | 1.25                                                      |  |  |  |  |

| GTL                                         | Voltage-referenced | 0.8                                                   | N/A                                                  | 1.20                                                      |  |  |  |  |

| GTL+                                        | Voltage-referenced | 1.0                                                   | N/A                                                  | 1.5                                                       |  |  |  |  |

| 1.5-V HSTL Class I and II                   | Voltage-referenced | 0.75                                                  | 1.5                                                  | 0.75                                                      |  |  |  |  |

| 1.8-V HSTL Class I and II                   | Voltage-referenced | 0.9                                                   | 1.8                                                  | 0.9                                                       |  |  |  |  |

| SSTL-18 Class I and II                      | Voltage-referenced | 0.90                                                  | 1.8                                                  | 0.90                                                      |  |  |  |  |

| SSTL-2 Class I and II                       | Voltage-referenced | 1.25                                                  | 2.5                                                  | 1.25                                                      |  |  |  |  |

| SSTL-3 Class I and II                       | Voltage-referenced | 1.5                                                   | 3.3                                                  | 1.5                                                       |  |  |  |  |

| AGP (1× and 2°)                             | Voltage-referenced | 1.32                                                  | 3.3                                                  | N/A                                                       |  |  |  |  |

| CTT                                         | Voltage-referenced | 1.5                                                   | 3.3                                                  | 1.5                                                       |  |  |  |  |

#### Notes to Table 2–31:

- (1) This I/O standard is only available on input and output clock pins.

- (2) This I/O standard is only available on output column clock pins.

| Table 4–13                         | Table 4–13. HyperTransport Technology Specifications |                    |         |         |         |      |  |  |  |  |

|------------------------------------|------------------------------------------------------|--------------------|---------|---------|---------|------|--|--|--|--|

| Symbol                             | Parameter                                            | Conditions         | Minimum | Typical | Maximum | Unit |  |  |  |  |

| V <sub>CCIO</sub>                  | I/O supply voltage                                   |                    | 2.375   | 2.5     | 2.625   | ٧    |  |  |  |  |

| V <sub>ID</sub> (peak-<br>to-peak) | Input differential voltage swing (single-ended)      |                    | 300     |         | 900     | mV   |  |  |  |  |

| V <sub>ICM</sub>                   | Input common mode voltage                            |                    | 300     |         | 900     | mV   |  |  |  |  |

| V <sub>OD</sub>                    | Output differential voltage (single-ended)           | $R_L = 100 \Omega$ | 380     | 485     | 820     | mV   |  |  |  |  |

| $\Delta$ V <sub>OD</sub>           | Change in V <sub>OD</sub> between high and low       | $R_L = 100 \Omega$ |         |         | 50      | mV   |  |  |  |  |

| V <sub>OCM</sub>                   | Output common mode voltage                           | $R_L = 100 \Omega$ | 440     | 650     | 780     | mV   |  |  |  |  |

| Δ V <sub>OCM</sub>                 | Change in V <sub>OCM</sub> between high and low      | $R_L = 100 \Omega$ |         |         | 50      | mV   |  |  |  |  |

| R <sub>L</sub>                     | Receiver differential input resistor                 |                    | 90      | 100     | 110     | Ω    |  |  |  |  |

| Table 4–14        | Table 4–14. 3.3-V PCI Specifications |                             |                            |         |                            |      |  |  |  |  |  |

|-------------------|--------------------------------------|-----------------------------|----------------------------|---------|----------------------------|------|--|--|--|--|--|

| Symbol            | Parameter                            | Conditions                  | Minimum                    | Typical | Maximum                    | Unit |  |  |  |  |  |

| V <sub>CCIO</sub> | Output supply voltage                |                             | 3.0                        | 3.3     | 3.6                        | V    |  |  |  |  |  |

| V <sub>IH</sub>   | High-level input voltage             |                             | 0.5 ×<br>V <sub>CCIO</sub> |         | V <sub>CCIO</sub> + 0.5    | V    |  |  |  |  |  |

| V <sub>IL</sub>   | Low-level input voltage              |                             | -0.5                       |         | 0.3 ×<br>V <sub>CCIO</sub> | V    |  |  |  |  |  |

| V <sub>OH</sub>   | High-level output voltage            | I <sub>OUT</sub> = -500 μA  | 0.9 ×<br>V <sub>CCIO</sub> |         |                            | V    |  |  |  |  |  |

| V <sub>OL</sub>   | Low-level output voltage             | I <sub>OUT</sub> = 1,500 μA |                            |         | 0.1 ×<br>V <sub>CCIO</sub> | V    |  |  |  |  |  |

# **Timing Model**

The DirectDrive<sup>TM</sup> technology and MultiTrack<sup>TM</sup> interconnect ensure predictable performance, accurate simulation, and accurate timing analysis across all Stratix device densities and speed grades. This section describes and specifies the performance, internal, external, and PLL timing specifications.

All specifications are representative of worst-case supply voltage and junction temperature conditions.

## **Preliminary & Final Timing**

Timing models can have either preliminary or final status. The Quartus II software issues an informational message during the design compilation if the timing models are preliminary. Table 4–35 shows the status of the Stratix device timing models.

Preliminary status means the timing model is subject to change. Initially, timing numbers are created using simulation results, process data, and other known parameters. These tests are used to make the preliminary numbers as close to the actual timing parameters as possible.

Final timing numbers are based on actual device operation and testing. These numbers reflect the actual performance of the device under worst-case voltage and junction temperature conditions.

| able 4–35. Stratix Device Timing Model Status |             |          |  |  |  |  |

|-----------------------------------------------|-------------|----------|--|--|--|--|

| Device                                        | Preliminary | Final    |  |  |  |  |

| EP1S10                                        |             | ✓        |  |  |  |  |

| EP1S20                                        |             | ✓        |  |  |  |  |

| EP1S25                                        |             | ✓        |  |  |  |  |

| EP1S30                                        |             | ✓        |  |  |  |  |

| EP1S40                                        |             | ✓        |  |  |  |  |

| EP1S60                                        |             | ✓        |  |  |  |  |

| EP1S80                                        |             | <b>✓</b> |  |  |  |  |

| Table 4–53. Stratix Regional Clock External I/O Ti | iming Parameters (Part 2 |

|----------------------------------------------------|--------------------------|

| <b>of 2)</b> Notes (1), (2)                        |                          |

|                                                    |                          |

| Symbol             | Parameter                                                                                                                              |  |  |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| t <sub>XZPLL</sub> | Synchronous IOE output enable register to output pin disable delay using regional clock fed by Enhanced PLL with default phase setting |  |  |  |  |  |  |

| t <sub>ZXPLL</sub> | Synchronous IOE output enable register to output pin enable delay using regional clock fed by Enhanced PLL with default phase setting  |  |  |  |  |  |  |

#### *Notes to Table 4–53:*

- (1) These timing parameters are sample-tested only.

- (2) These timing parameters are for column and row IOE pins. You should use the Quartus II software to verify the external timing for any pin.

Table 4–54 shows the external I/O timing parameters when using global clock networks.

| <b>Table 4–3</b> (2)  | 54. Stratix Global Clock External I/O Timing Parameters Notes (1),                                                                    |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                | Parameter                                                                                                                             |

| t <sub>INSU</sub>     | Setup time for input or bidirectional pin using IOE input register with global clock fed by ${\tt CLK}$ pin                           |

| t <sub>INH</sub>      | Hold time for input or bidirectional pin using IOE input register with global clock fed by CLK pin                                    |

| t <sub>OUTCO</sub>    | Clock-to-output delay output or bidirectional pin using IOE output register with global clock fed by CLK pin                          |

| t <sub>INSUPLL</sub>  | Setup time for input or bidirectional pin using IOE input register with global clock fed by Enhanced PLL with default phase setting   |

| t <sub>INHPLL</sub>   | Hold time for input or bidirectional pin using IOE input register with global clock fed by Enhanced PLL with default phase setting    |

| t <sub>OUTCOPLL</sub> | Clock-to-output delay output or bidirectional pin using IOE output register with global clock Enhanced PLL with default phase setting |

| t <sub>XZPLL</sub>    | Synchronous IOE output enable register to output pin disable delay using global clock fed by Enhanced PLL with default phase setting  |

| t <sub>ZXPLL</sub>    | Synchronous IOE output enable register to output pin enable delay using global clock fed by Enhanced PLL with default phase setting   |

#### Notes to Table 4-54:

- (1) These timing parameters are sample-tested only.

- (2) These timing parameters are for column and row IOE pins. You should use the Quartus II software to verify the external timing for any pin.

Tables 4–67 through 4–72 show the external timing parameters on column and row pins for EP1S25 devices.

| Table 4–67. EP1S25 External I/O Timing on Column Pins Using Fast Regional Clock Networks |         |         |         |         |         |         |         |         |      |

|------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|------|

| Doromotor                                                                                | -5 Spee | d Grade | -6 Spee | d Grade | -7 Spee | d Grade | -8 Spee | d Grade | Heit |

| Parameter                                                                                | Min     | Max     | Min     | Max     | Min     | Max     | Min     | Max     | Unit |

| t <sub>INSU</sub>                                                                        | 2.412   |         | 2.613   |         | 2.968   |         | 3.468   |         | ns   |

| t <sub>INH</sub>                                                                         | 0.000   |         | 0.000   |         | 0.000   |         | 0.000   |         | ns   |

| t <sub>OUTCO</sub>                                                                       | 2.196   | 4.475   | 2.196   | 4.748   | 2.196   | 5.118   | 2.196   | 5.603   | ns   |

| t <sub>XZ</sub>                                                                          | 2.136   | 4.349   | 2.136   | 4.616   | 2.136   | 4.994   | 2.136   | 5.488   | ns   |

| t <sub>ZX</sub>                                                                          | 2.136   | 4.349   | 2.136   | 4.616   | 2.136   | 4.994   | 2.136   | 5.488   | ns   |

| Table 4–68. I        | Table 4–68. EP1S25 External I/O Timing on Column Pins Using Regional Clock Networks |         |         |         |         |         |                |       |      |  |

|----------------------|-------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|----------------|-------|------|--|

| Parameter            | -5 Spee                                                                             | d Grade | -6 Spee | d Grade | -7 Spee | d Grade | -8 Speed Grade |       | Unit |  |

| rarameter            | Min                                                                                 | Max     | Min     | Max     | Min     | Max     | Min            | Max   | Unit |  |

| t <sub>INSU</sub>    | 1.535                                                                               |         | 1.661   |         | 1.877   |         | 2.125          |       | ns   |  |

| t <sub>INH</sub>     | 0.000                                                                               |         | 0.000   |         | 0.000   |         | 0.000          |       | ns   |  |

| t <sub>оитсо</sub>   | 2.739                                                                               | 5.396   | 2.739   | 5.746   | 2.739   | 6.262   | 2.739          | 6.946 | ns   |  |

| t <sub>XZ</sub>      | 2.679                                                                               | 5.270   | 2.679   | 5.614   | 2.679   | 6.138   | 2.679          | 6.831 | ns   |  |

| t <sub>ZX</sub>      | 2.679                                                                               | 5.270   | 2.679   | 5.614   | 2.679   | 6.138   | 2.679          | 6.831 | ns   |  |

| t <sub>INSUPLL</sub> | 0.934                                                                               |         | 0.980   |         | 1.092   |         | 1.231          |       | ns   |  |

| t <sub>INHPLL</sub>  | 0.000                                                                               |         | 0.000   |         | 0.000   |         | 0.000          |       | ns   |  |

| toutcopll            | 1.316                                                                               | 2.733   | 1.316   | 2.839   | 1.316   | 2.921   | 1.316          | 3.110 | ns   |  |

| t <sup>XZPLL</sup>   | 1.256                                                                               | 2.607   | 1.256   | 2.707   | 1.256   | 2.797   | 1.256          | 2.995 | ns   |  |

| t <sub>ZXPLL</sub>   | 1.256                                                                               | 2.607   | 1.256   | 2.707   | 1.256   | 2.797   | 1.256          | 2.995 | ns   |  |

| Table 4-77. L         | EP1S30 Ext | ernal I/O T | iming on R | ow Pins U | sing Regio | nal Clock N | letworks       |       |         |

|-----------------------|------------|-------------|------------|-----------|------------|-------------|----------------|-------|---------|

| Davamatav             | -5 Spee    | d Grade     | -6 Spee    | d Grade   | -7 Spee    | d Grade     | -8 Speed Grade |       | II.a.iA |

| Parameter             | Min        | Max         | Min        | Max       | Min        | Max         | Min            | Max   | Unit    |

| t <sub>INSU</sub>     | 2.322      |             | 2.467      |           | 2.828      |             | 3.342          |       | ns      |

| t <sub>INH</sub>      | 0.000      |             | 0.000      |           | 0.000      |             | 0.000          |       | ns      |

| t <sub>OUTCO</sub>    | 2.731      | 5.408       | 2.731      | 5.843     | 2.731      | 6.360       | 2.731          | 7.036 | ns      |

| t <sub>XZ</sub>       | 2.758      | 5.462       | 2.758      | 5.899     | 2.758      | 6.428       | 2.758          | 7.118 | ns      |

| t <sub>ZX</sub>       | 2.758      | 5.462       | 2.758      | 5.899     | 2.758      | 6.428       | 2.758          | 7.118 | ns      |

| t <sub>INSUPLL</sub>  | 1.291      |             | 1.283      |           | 1.469      |             | 1.832          |       | ns      |

| t <sub>INHPLL</sub>   | 0.000      |             | 0.000      |           | 0.000      |             | 0.000          |       | ns      |

| t <sub>OUTCOPLL</sub> | 1.192      | 2.539       | 1.192      | 2.737     | 1.192      | 2.786       | 1.192          | 2.742 | ns      |

| t <sub>XZPLL</sub>    | 1.219      | 2.539       | 1.219      | 2.793     | 1.219      | 2.854       | 1.219          | 2.824 | ns      |

| t <sub>ZXPLL</sub>    | 1.219      | 2.539       | 1.219      | 2.793     | 1.219      | 2.854       | 1.219          | 2.824 | ns      |

| Table 4-78. I        | Table 4–78. EP1S30 External I/O Timing on Row Pins Using Global Clock Networks |         |         |         |         |         |                |       |      |  |

|----------------------|--------------------------------------------------------------------------------|---------|---------|---------|---------|---------|----------------|-------|------|--|

| Davamatav            | -5 Spee                                                                        | d Grade | -6 Spee | d Grade | -7 Spee | d Grade | -8 Speed Grade |       | Hait |  |

| Parameter            | Min                                                                            | Max     | Min     | Max     | Min     | Max     | Min            | Max   | Unit |  |

| t <sub>INSU</sub>    | 1.995                                                                          |         | 2.089   |         | 2.398   |         | 2.830          |       | ns   |  |

| t <sub>INH</sub>     | 0.000                                                                          |         | 0.000   |         | 0.000   |         | 0.000          |       | ns   |  |

| t <sub>OUTCO</sub>   | 2.917                                                                          | 5.735   | 2.917   | 6.221   | 2.917   | 6.790   | 2.917          | 7.548 | ns   |  |

| t <sub>XZ</sub>      | 2.944                                                                          | 5.789   | 2.944   | 6.277   | 2.944   | 6.858   | 2.944          | 7.630 | ns   |  |

| t <sub>ZX</sub>      | 2.944                                                                          | 5.789   | 2.944   | 6.277   | 2.944   | 6.858   | 2.944          | 7.630 | ns   |  |

| t <sub>INSUPLL</sub> | 1.337                                                                          |         | 1.312   |         | 1.508   |         | 1.902          |       | ns   |  |

| t <sub>INHPLL</sub>  | 0.000                                                                          |         | 0.000   |         | 0.000   |         | 0.000          |       | ns   |  |

| toutcopll            | 1.164                                                                          | 2.493   | 1.164   | 2.708   | 1.164   | 2.747   | 1.164          | 2.672 | ns   |  |

| t <sub>XZPLL</sub>   | 1.191                                                                          | 2.547   | 1.191   | 2.764   | 1.191   | 2.815   | 1.191          | 2.754 | ns   |  |

| t <sub>ZXPLL</sub>   | 1.191                                                                          | 2.547   | 1.191   | 2.764   | 1.191   | 2.815   | 1.191          | 2.754 | ns   |  |

| Table 4-89. I         | EP1S60 Ext | ernal I/O T | iming on R | ow Pins U | sing Regio | nal Clock N | letworks N     | ote (1) |      |

|-----------------------|------------|-------------|------------|-----------|------------|-------------|----------------|---------|------|

| Davamatav             | -5 Spee    | d Grade     | -6 Spee    | d Grade   | -7 Spee    | d Grade     | -8 Speed Grade |         | IIiA |

| Parameter             | Min        | Max         | Min        | Max       | Min        | Max         | Min            | Max     | Unit |

| t <sub>INSU</sub>     | 2.775      |             | 2.990      |           | 3.407      |             | NA             |         | ns   |

| t <sub>INH</sub>      | 0.000      |             | 0.000      |           | 0.000      |             | NA             |         | ns   |

| t <sub>OUTCO</sub>    | 2.867      | 5.644       | 2.867      | 6.057     | 2.867      | 6.600       | NA             | NA      | ns   |

| t <sub>XZ</sub>       | 2.894      | 5.698       | 2.894      | 6.113     | 2.894      | 6.668       | NA             | NA      | ns   |

| t <sub>ZX</sub>       | 2.894      | 5.698       | 2.894      | 6.113     | 2.894      | 6.668       | NA             | NA      | ns   |

| t <sub>INSUPLL</sub>  | 1.523      |             | 1.577      |           | 1.791      |             | NA             |         | ns   |

| t <sub>INHPLL</sub>   | 0.000      |             | 0.000      |           | 0.000      |             | NA             |         | ns   |

| t <sub>OUTCOPLL</sub> | 1.174      | 2.507       | 1.174      | 2.643     | 1.174      | 2.664       | NA             | NA      | ns   |

| t <sub>XZPLL</sub>    | 1.201      | 2.561       | 1.201      | 2.699     | 1.201      | 2.732       | NA             | NA      | ns   |

| t <sub>ZXPLL</sub>    | 1.201      | 2.561       | 1.201      | 2.699     | 1.201      | 2.732       | NA             | NA      | ns   |

| Table 4-90. I         | EP1S60 Ext | ernal I/O T | iming on R | ow Pins Us | sing Globa     | l Clock Net | <b>works</b> Note | ? (1) |      |

|-----------------------|------------|-------------|------------|------------|----------------|-------------|-------------------|-------|------|

| Davamatav             | -5 Spee    | d Grade     | -6 Spee    | d Grade    | -7 Speed Grade |             | -8 Speed Grade    |       | 11   |

| Parameter             | Min        | Max         | Min        | Max        | Min            | Max         | Min               | Max   | Unit |

| t <sub>INSU</sub>     | 2.232      |             | 2.393      |            | 2.721          |             | NA                |       | ns   |

| t <sub>INH</sub>      | 0.000      |             | 0.000      |            | 0.000          |             | NA                |       | ns   |

| t <sub>outco</sub>    | 3.182      | 6.187       | 3.182      | 6.654      | 3.182          | 7.286       | NA                | NA    | ns   |

| t <sub>XZ</sub>       | 3.209      | 6.241       | 3.209      | 6.710      | 3.209          | 7.354       | NA                | NA    | ns   |

| t <sub>ZX</sub>       | 3.209      | 6.241       | 3.209      | 6.710      | 3.209          | 7.354       | NA                | NA    | ns   |

| t <sub>INSUPLL</sub>  | 1.651      |             | 1.612      |            | 1.833          |             | NA                |       | ns   |

| t <sub>INHPLL</sub>   | 0.000      |             | 0.000      |            | 0.000          |             | NA                |       | ns   |

| t <sub>OUTCOPLL</sub> | 1.154      | 2.469       | 1.154      | 2.608      | 1.154          | 2.622       | NA                | NA    | ns   |

| t <sub>XZPLL</sub>    | 1.181      | 2.523       | 1.181      | 2.664      | 1.181          | 2.690       | NA                | NA    | ns   |

| t <sub>ZXPLL</sub>    | 1.181      | 2.523       | 1.181      | 2.664      | 1.181          | 2.690       | NA                | NA    | ns   |

*Note to Tables 4–85 to 4–90:*

<sup>(1)</sup> Only EP1S25, EP1S30, and EP1S40 devices have the -8 speed grade.

| Table 4–102. Reporting Methodology For Minimum Timi | ng For Single-Ended Output Pins (Part 2 of 2) |

|-----------------------------------------------------|-----------------------------------------------|

| Notes (1), (2), (3)                                 |                                               |

| 1/0 0111     |                   |          | Loadi          | ng and T         | ermination               |            |                        | Measurement<br>Point |

|--------------|-------------------|----------|----------------|------------------|--------------------------|------------|------------------------|----------------------|

| I/O Standard | $\mathbf{R}_{UP}$ | $R_{DN}$ | R <sub>S</sub> | $\mathbf{R}_{T}$ | V <sub>CCIO</sub><br>(V) | VTT<br>(V) | C <sub>L</sub><br>(pF) | V <sub>MEAS</sub>    |

| 3.3-V CTT    | _                 | =-       | 25             | 50               | 3.600                    | 1.650      | 30                     | 1.650                |

#### Notes to Table 4–102:

- (1) Input measurement point at internal node is  $0.5 \times V_{CCINT}$ .

- (2) Output measuring point for data is V<sub>MEAS</sub>. When two values are given, the first is the measurement point on the rising edge and the other is for the falling edge.

- (3) Input stimulus edge rate is 0 to V<sub>CCINT</sub> in 0.5 ns (internal signal) from the driver preceding the I/O buffer.

- (4) The first value is for the output rising edge and the second value is for the output falling edge. The hyphen (-) indicates infinite resistance or disconnection.

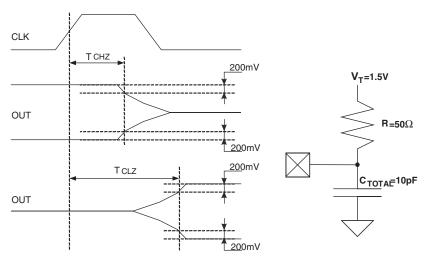

Figure 4–8 shows the measurement setup for output disable and output enable timing. The  $T_{CHZ}$  stands for clock to high Z time delay and is the same as  $T_{XZ}.$  The  $T_{CLZ}$  stands for clock to low Z (driving) time delay and is the same as  $T_{ZX}.$

Figure 4–8. Measurement Setup for  $T_{XZ}$  and  $T_{ZX}$

Table 4–116. Stratix Maximum Input Clock Rate for CLK[1, 3, 8, 10] Pins in Flip-Chip Packages

| I/O Standard                  | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------|-------------------|-------------------|-------------------|-------------------|------|

| LVTTL                         | 422               | 422               | 390               | 390               | MHz  |

| 2.5 V                         | 422               | 422               | 390               | 390               | MHz  |

| 1.8 V                         | 422               | 422               | 390               | 390               | MHz  |

| 1.5 V                         | 422               | 422               | 390               | 390               | MHz  |

| LVCMOS                        | 422               | 422               | 390               | 390               | MHz  |

| GTL+                          | 300               | 250               | 200               | 200               | MHz  |

| SSTL-3 Class I                | 400               | 350               | 300               | 300               | MHz  |

| SSTL-3 Class II               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-2 Class I                | 400               | 350               | 300               | 300               | MHz  |

| SSTL-2 Class II               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-18 Class I               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-18 Class II              | 400               | 350               | 300               | 300               | MHz  |

| 1.5-V HSTL Class I            | 400               | 350               | 300               | 300               | MHz  |

| 1.8-V HSTL Class I            | 400               | 350               | 300               | 300               | MHz  |

| СТТ                           | 300               | 250               | 200               | 200               | MHz  |

| Differential 1.5-V HSTL<br>C1 | 400               | 350               | 300               | 300               | MHz  |

| LVPECL (1)                    | 645               | 645               | 640               | 640               | MHz  |

| PCML (1)                      | 300               | 275               | 275               | 275               | MHz  |

| LVDS (1)                      | 645               | 645               | 640               | 640               | MHz  |

| HyperTransport technology (1) | 500               | 500               | 450               | 450               | MHz  |

Table 4–117. Stratix Maximum Input Clock Rate for CLK[7..4] & CLK[15..12] Pins in Wire-Bond Packages (Part 1 of 2)

| I/O Standard | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|--------------|-------------------|-------------------|-------------------|------|

| LVTTL        | 422               | 390               | 390               | MHz  |

| 2.5 V        | 422               | 390               | 390               | MHz  |

| 1.8 V        | 422               | 390               | 390               | MHz  |

| 1.5 V        | 422               | 390               | 390               | MHz  |

| LVCMOS       | 422               | 390               | 390               | MHz  |

| GTL          | 250               | 200               | 200               | MHz  |

Table 4–122. Stratix Maximum Output Clock Rate for PLL[5, 6, 11, 12] Pins in Wire-Bond Packages (Part 1 of 2)

| I/O Standard                        | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------------|-------------------|-------------------|-------------------|------|

| LVTTL                               | 175               | 150               | 150               | MHz  |

| 2.5 V                               | 175               | 150               | 150               | MHz  |

| 1.8 V                               | 175               | 150               | 150               | MHz  |

| 1.5 V                               | 175               | 150               | 150               | MHz  |

| LVCMOS                              | 175               | 150               | 150               | MHz  |

| GTL                                 | 125               | 100               | 100               | MHz  |

| GTL+                                | 125               | 100               | 100               | MHz  |

| SSTL-3 Class I                      | 110               | 90                | 90                | MHz  |

| SSTL-3 Class II                     | 133               | 125               | 125               | MHz  |

| SSTL-2 Class I                      | 166               | 133               | 133               | MHz  |

| SSTL-2 Class II                     | 133               | 100               | 100               | MHz  |

| SSTL-18 Class I                     | 110               | 100               | 100               | MHz  |

| SSTL-18 Class II                    | 110               | 100               | 100               | MHz  |

| 1.5-V HSTL Class I                  | 167               | 167               | 167               | MHz  |

| 1.5-V HSTL Class II                 | 167               | 133               | 133               | MHz  |

| 1.8-V HSTL Class I                  | 167               | 167               | 167               | MHz  |

| 1.8-V HSTL Class II                 | 167               | 133               | 133               | MHz  |

| 3.3-V PCI                           | 167               | 167               | 167               | MHz  |

| 3.3-V PCI-X 1.0                     | 167               | 133               | 133               | MHz  |

| Compact PCI                         | 175               | 150               | 150               | MHz  |

| AGP 1×                              | 175               | 150               | 150               | MHz  |

| AGP 2×                              | 175               | 150               | 150               | MHz  |

| СТТ                                 | 125               | 100               | 100               | MHz  |

| Differential 1.5-V HSTL<br>C1       | 167               | 133               | 133               | MHz  |

| Differential 1.8-V HSTL<br>Class I  | 167               | 167               | 167               | MHz  |

| Differential 1.8-V HSTL<br>Class II | 167               | 133               | 133               | MHz  |

| Differential SSTL-2 (1)             | 110               | 100               | 100               | MHz  |

| LVPECL (2)                          | 311               | 275               | 275               | MHz  |

| PCML (2)                            | 250               | 200               | 200               | MHz  |

| Symbol              | Parameter                                                                                             | Min | Тур | Max | Unit |

|---------------------|-------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>LSKEW</sub>  | Clock skew between two external clock outputs driven by the same counter                              |     | ±50 |     | ps   |

| t <sub>SKEW</sub>   | Clock skew between two external clock outputs driven by the different counters with the same settings |     | ±75 |     | ps   |

| f <sub>SS</sub>     | Spread spectrum modulation frequency                                                                  | 30  |     | 150 | kHz  |

| % spread            | Percentage spread for spread spectrum frequency (10)                                                  | 0.5 |     | 0.6 | %    |

| t <sub>ARESET</sub> | Minimum pulse width on areset signal                                                                  | 10  |     |     | ns   |

#### *Notes to Tables 4–127 through 4–130:*

- (1) The minimum input clock frequency to the PFD ( $f_{\rm IN}/N$ ) must be at least 3 MHz for Stratix device enhanced PLLs.

- (2) Use this equation  $(f_{OUT} = f_{IN} * ml(n \times post\text{-scale counter}))$  in conjunction with the specified  $f_{INPFD}$  and  $f_{VCO}$  ranges to determine the allowed PLL settings.

- (3) See "Maximum Input & Output Clock Rates" on page 4–76.

- (4) t<sub>PCOMP</sub> can also equal 50% of the input clock period multiplied by the pre-scale divider *n* (whichever is less).

- (5) This parameter is timing analyzed by the Quartus II software because the scanclk and scandata ports can be driven by the logic array.

- (6) Actual jitter performance may vary based on the system configuration.

- (7) Total required time to reconfigure and lock is equal to t<sub>DLOCK</sub> + t<sub>CONFIG</sub>. If only post-scale counters and delays are changed, then t<sub>DLOCK</sub> is equal to 0.

- (8) When using the spread-spectrum feature, the minimum VCO frequency is 500 MHz. The maximum VCO frequency is determined by the speed grade selected.

- (9) Lock time is a function of PLL configuration and may be significantly faster depending on bandwidth settings or feedback counter change increment.

- (10) Exact, user-controllable value depends on the PLL settings.

- (11) The LOCK circuit on Stratix PLLs does not work for industrial devices below -20C unless the PFD frequency > 200 MHz. See the *Stratix FPGA Errata Sheet* for more information on the PLL.