Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Obsolete                                                  |

| Number of LABs/CLBs            | 4125                                                      |

| Number of Logic Elements/Cells | 41250                                                     |

| Total RAM Bits                 | 3423744                                                   |

| Number of I/O                  | 773                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.425V ~ 1.575V                                           |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 1020-BBGA                                                 |

| Supplier Device Package        | 1020-FBGA (33x33)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s40f1020c5n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1. Introduction

\$51001-3.2

#### Introduction

The Stratix® family of FPGAs is based on a 1.5-V, 0.13- $\mu$ m, all-layer copper SRAM process, with densities of up to 79,040 logic elements (LEs) and up to 7.5 Mbits of RAM. Stratix devices offer up to 22 digital signal processing (DSP) blocks with up to 176 (9-bit × 9-bit) embedded multipliers, optimized for DSP applications that enable efficient implementation of high-performance filters and multipliers. Stratix devices support various I/O standards and also offer a complete clock management solution with its hierarchical clock structure with up to 420-MHz performance and up to 12 phase-locked loops (PLLs).

The following shows the main sections in the Stratix Device Family Data Sheet:

| Section                                       | Page  |

|-----------------------------------------------|-------|

| Features                                      | 1–2   |

| Functional Description                        | 2–1   |

| Logic Array Blocks                            |       |

| Logic Elements                                |       |

| MultiTrack Interconnect                       |       |

| TriMatrix Memory                              |       |

| Digital Signal Processing Block               |       |

| PLLs & Clock Networks                         |       |

| I/O Structure                                 |       |

| High-Speed Differential I/O Support           |       |

| Power Sequencing & Hot Socketing              | 2–140 |

| IEEE Std. 1149.1 (JTAG) Boundary-Scan Support | 3–1   |

| SignalTap II Embedded Logic Analyzer          |       |

| Configuration                                 |       |

| Temperature Sensing Diode                     |       |

| Operating Conditions                          | 4_1   |

| Power Consumption                             |       |

| Timing Model                                  |       |

| Software                                      | 5–1   |

| Device Pin-Outs                               |       |

| Ordering Information                          |       |

#### Dynamic Arithmetic Mode

The dynamic arithmetic mode is ideal for implementing adders, counters, accumulators, wide parity functions, and comparators. An LE in dynamic arithmetic mode uses four 2-input LUTs configurable as a dynamic adder/subtractor. The first two 2-input LUTs compute two summations based on a possible carry-in of 1 or 0; the other two LUTs generate carry outputs for the two chains of the carry select circuitry. As shown in Figure 2–7, the LAB carry-in signal selects either the carry-in0 or carry-in1 chain. The selected chain's logic level in turn determines which parallel sum is generated as a combinatorial or registered output. For example, when implementing an adder, the sum output is the selection of two possible calculated sums: data1 + data2 + carry-in0 or data1 + data2 + carry-in1. The other two LUTs use the data1 and data2 signals to generate two possible carry-out signals—one for a carry of 1 and the other for a carry of 0. The carry-in0 signal acts as the carry select for the carry-out 0 output and carry-in1 acts as the carry select for the carry-out1 output. LEs in arithmetic mode can drive out registered and unregistered versions of the LUT output.

The dynamic arithmetic mode also offers clock enable, counter enable, synchronous up/down control, synchronous clear, synchronous load, and dynamic adder/subtractor options. The LAB local interconnect data inputs generate the counter enable and synchronous up/down control signals. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. The Quartus II software automatically places any registers that are not used by the counter into other LABs. The addnsub LAB-wide signal controls whether the LE acts as an adder or subtractor.

LAB Carry-In LAB Carry-In Sum1 A1 B1 LE1 Carry-In0 Carry-In1 Sum2 LE2 LUT B2 data1 Sum data2 Sum3 LUT LE3 A4 B4 Sum4 LUT LE4 LUT A5 B5 Sum5 LE5 Carry-Out0 Carry-Out1 Sum6 A6 B6 LE6 A7 B7 Sum7 LE7 \_<u>A8</u> \_B8 Sum8 LE8 <u>A9</u> B9 Sum9 LE9 Sum10 A10 B10 LE10 LAB Carry-Out

Figure 2-8. Carry Select Chain

### **Clear & Preset Logic Control**

LAB-wide signals control the logic for the register's clear and preset signals. The LE directly supports an asynchronous clear and preset function. The register preset is achieved through the asynchronous load of a logic high. The direct asynchronous preset does not require a NOT-gate push-back technique. Stratix devices support simultaneous preset/

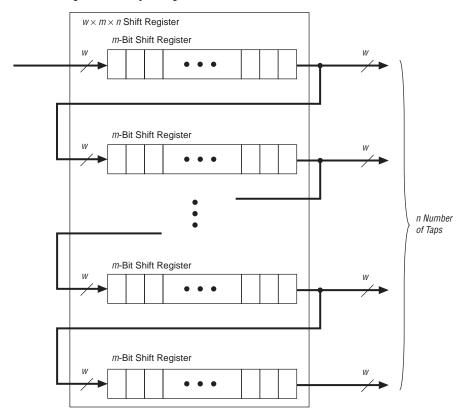

Figure 2-14. Shift Register Memory Configuration

## **Memory Block Size**

TriMatrix memory provides three different memory sizes for efficient application support. The large number of M512 blocks are ideal for designs with many shallow first-in first-out (FIFO) buffers. M4K blocks provide additional resources for channelized functions that do not require large amounts of storage. The M-RAM blocks provide a large single block of RAM ideal for data packet storage. The different-sized blocks allow Stratix devices to efficiently support variable-sized memory in designs.

The Quartus II software automatically partitions the user-defined memory into the embedded memory blocks using the most efficient size combinations. You can also manually assign the memory to a specific block size or a mixture of block sizes.

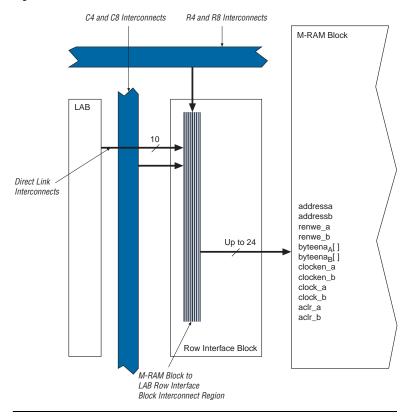

blocks facing to the left, and another 10 possible from the right adjacent LABs for M-RAM blocks facing to the right. For column interfacing, every M-RAM column unit connects to the right and left column lines, allowing each M-RAM column unit to communicate directly with three columns of LABs. Figures 2–21 through 2–23 show the interface between the M-RAM block and the logic array.

Figure 2–22. M-RAM Row Unit Interface to Interconnect

Table 2–12 shows the input and output data signal connections for the column units (B1 to B6 and A1 to A6). It also shows the address and control signal input connections to the row units (R1 to R11).

| Huit Interfese Block Innut Clausia Control Circuit |                                              |                 |  |  |  |  |  |  |  |

|----------------------------------------------------|----------------------------------------------|-----------------|--|--|--|--|--|--|--|

| Unit Interface Block                               | Input Signals                                | Output Signals  |  |  |  |  |  |  |  |

| R1                                                 | addressa[70]                                 |                 |  |  |  |  |  |  |  |

| R2                                                 | addressa[158]                                |                 |  |  |  |  |  |  |  |

| R3                                                 | byte_enable_a[70]<br>renwe_a                 |                 |  |  |  |  |  |  |  |

| R4                                                 | -                                            |                 |  |  |  |  |  |  |  |

| R5                                                 | -                                            |                 |  |  |  |  |  |  |  |

| R6                                                 | clock_a<br>clocken_a<br>clock_b<br>clocken_b |                 |  |  |  |  |  |  |  |

| R7                                                 | -                                            |                 |  |  |  |  |  |  |  |

| R8                                                 | -                                            |                 |  |  |  |  |  |  |  |

| R9                                                 | byte_enable_b[70]<br>renwe_b                 |                 |  |  |  |  |  |  |  |

| R10                                                | addressb[158]                                |                 |  |  |  |  |  |  |  |

| R11                                                | addressb[70]                                 |                 |  |  |  |  |  |  |  |

| B1                                                 | datain_b[7160]                               | dataout_b[7160] |  |  |  |  |  |  |  |

| B2                                                 | datain_b[5948]                               | dataout_b[5948] |  |  |  |  |  |  |  |

| B3                                                 | datain_b[4736]                               | dataout_b[4736] |  |  |  |  |  |  |  |

| B4                                                 | datain_b[3524]                               | dataout_b[3524] |  |  |  |  |  |  |  |

| B5                                                 | datain_b[2312]                               | dataout_b[2312] |  |  |  |  |  |  |  |

| B6                                                 | datain_b[110]                                | dataout_b[110]  |  |  |  |  |  |  |  |

| A1                                                 | datain_a[7160]                               | dataout_a[7160] |  |  |  |  |  |  |  |

| A2                                                 | datain_a[5948]                               | dataout_a[5948] |  |  |  |  |  |  |  |

| A3                                                 | datain_a[4736]                               | dataout_a[4736] |  |  |  |  |  |  |  |

| A4                                                 | datain_a[3524]                               | dataout_a[3524] |  |  |  |  |  |  |  |

| A5                                                 | datain_a[2312]                               | dataout_a[2312] |  |  |  |  |  |  |  |

| A6                                                 | datain_a[110]                                | dataout_a[110]  |  |  |  |  |  |  |  |

Accumulator Feedback accum\_sload0 (2) Result A ■ overflow0 Adder/ Subtractor/ addnsub1 (2) Accumulator1 Output Selection Multiplexer Result B signa (2) Summation Output signb (2) Register Block Result C Adder/ addnsub3 (2) Subtractor/ Accumulator2 overflow1 Result D accum\_sload1 (2) Accumulator Feedback

Figure 2–34. Adder/Output Blocks Note (1)

#### Notes to Figure 2–34:

- (1) Adder/output block shown in Figure 2–34 is in 18 × 18-bit mode. In 9 × 9-bit mode, there are four adder/subtractor blocks and two summation blocks.

- (2) These signals are either not registered, registered once, or registered twice to match the data path pipeline.

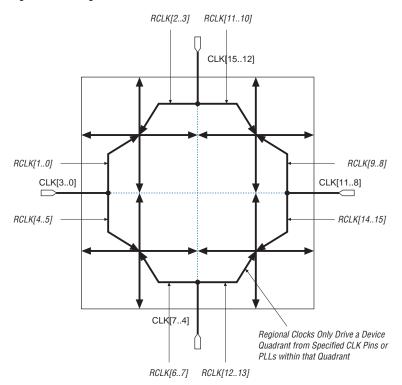

Figure 2-43. Regional Clocks

#### Fast Regional Clock Network

In EP1S25, EP1S20, and EP1S10 devices, there are two fast regional clock networks, FCLK [1..0], within each quadrant, fed by input pins that can connect to fast regional clock networks (see Figure 2–44). In EP1S30 and larger devices, there are two fast regional clock networks within each half-quadrant (see Figure 2–45). Dual-purpose FCLK pins drive the fast clock networks. All devices have eight FCLK pins to drive fast regional clock networks. Any I/O pin can drive a clock or control signal onto any fast regional clock network with the addition of a delay. This signal is driven via the I/O interconnect. The fast regional clock networks can also be driven from internal logic elements.

VCO period from up to eight taps for individual fine step selection. Also, each clock output counter can use a unique initial count setting to achieve individual coarse shift selection in steps of one VCO period. The combination of coarse and fine shifts allows phase shifting for the entire input clock period.

The equation to determine the precision of the phase shifting in degrees is:  $45^{\circ}$  ÷ post-scale counter value. Therefore, the maximum step size is  $45^{\circ}$ , and smaller steps are possible depending on the multiplication and division ratio necessary on the output counter port.

This type of phase shift provides the highest precision since it is the least sensitive to process, supply, and temperature variation.

#### **Clock Delay**

In addition to the phase shift feature, the ability to fine tune the  $\Delta t$  clock delay provides advanced time delay shift control on each of the four PLL outputs. There are time delays for each post-scale counter (e, g, or l) from the PLL, the n counter, and m counter. Each of these can shift in 250-ps increments for a range of 3.0 ns. The m delay shifts all outputs earlier in time, while n delay shifts all outputs later in time. Individual delays on post-scale counters (e, g, and l) provide positive delay for each output. Table 2–21 shows the combined delay for each output for normal or zero delay buffer mode where  $\Delta t_e$ ,  $\Delta t_o$ , or  $\Delta t_l$  is unique for each PLL output.

The  $t_{OUTPUT}$  for a single output can range from -3 ns to +6 ns. The total delay shift difference between any two PLL outputs, however, must be less than  $\pm 3$  ns. For example, shifts on two outputs of -1 and +2 ns is allowed, but not -1 and +2.5 ns because these shifts would result in a difference of 3.5 ns. If the design uses external feedback, the  $\Delta t_e$  delay will remove delay from outputs, represented by a negative sign (see Table 2–21). This effect occurs because the  $\Delta t_e$  delay is then part of the feedback loop.

| Table 2–21. Output Clock Delay for Enhanced PLLs                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Normal or Zero Delay Buffer Mode External Feedback Mode                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| $\begin{split} \Delta t_{e \text{OUTPUT}} &= \Delta t_n - \!\!\! \Delta t_m + \Delta t_e \\ \Delta t_{g \text{OUTPUT}} &= \Delta t_n - \!\!\! \Delta t_m + \Delta t_g \\ \Delta t_{l \text{OUTPUT}} &= \Delta t_n - \!\!\! \Delta t_m + \Delta t_l \end{split}$ | $\begin{split} \Delta \mathbf{t}_{\text{OUTPUT}} &= \Delta \mathbf{t}_{n} - \Delta \mathbf{t}_{m} - \Delta \mathbf{t}_{e} \ (1) \\ \Delta \mathbf{t}_{\text{gOUTPUT}} &= \Delta \mathbf{t}_{n} - \Delta \mathbf{t}_{m} + \Delta \mathbf{t}_{g} \\ \Delta \mathbf{t}_{\text{DUTPUT}} &= \Delta \mathbf{t}_{n} - \Delta \mathbf{t}_{m} + \Delta \mathbf{t}_{l} \end{split}$ |  |  |  |  |  |  |  |  |

Note to Table 2-21:

(1)  $\Delta t_e$  removes delay from outputs in external feedback mode.

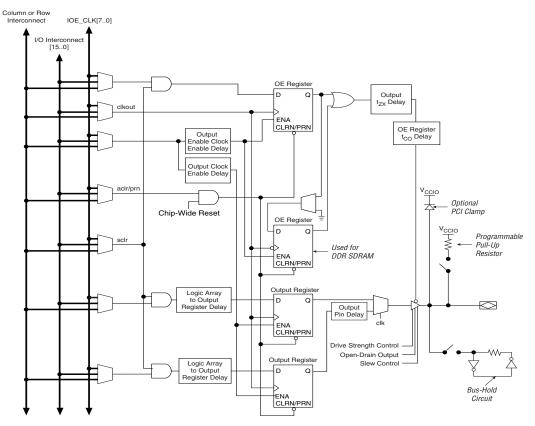

Figure 2–67. Stratix IOE in DDR Output I/O Configuration Notes (1), (2)

*Notes to Figure 2–67:*

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) The tristate is by default active high. It can, however, be designed to be active low.

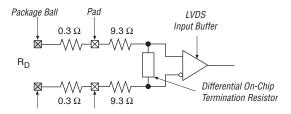

However, there is additional resistance present between the device ball and the input of the receiver buffer, as shown in Figure 2–72. This resistance is because of package trace resistance (which can be calculated as the resistance from the package ball to the pad) and the parasitic layout metal routing resistance (which is shown between the pad and the intersection of the on-chip termination and input buffer).

Figure 2-72. Differential Resistance of LVDS Differential Pin Pair (Rp)

Table 2–35 defines the specification for internal termination resistance for commercial devices.

| Table 2-3             | Table 2–35. Differential On-Chip Termination |                     |     |     |     |      |  |  |  |  |  |  |

|-----------------------|----------------------------------------------|---------------------|-----|-----|-----|------|--|--|--|--|--|--|

| Resistance Conditions |                                              |                     |     |     |     |      |  |  |  |  |  |  |

| Symbol                | Description                                  | Conditions          | Min | Тур | Max | Unit |  |  |  |  |  |  |

| R <sub>D</sub> (2)    | Internal differential termination for LVDS   | Commercial (1), (3) | 110 | 135 | 165 | W    |  |  |  |  |  |  |

|                       |                                              | Industrial (2), (3) | 100 | 135 | 170 | W    |  |  |  |  |  |  |

Notes to Table 2-35:

- (1) Data measured over minimum conditions ( $T_j = 0 \text{ C}$ ,  $V_{\text{CCIO}} + 5\%$ ) and maximum conditions ( $T_j = 85 \text{ C}$ ,  $V_{\text{CCIO}} = -5\%$ ).

- (2) Data measured over minimum conditions ( $T_j = -40$  C,  $V_{CCIO} + 5\%$ ) and maximum conditions ( $T_j = 100$  C,  $V_{CCIO} = -5\%$ ).

- (3) LVDS data rate is supported for 840 Mbps using internal differential termination.

#### MultiVolt I/O Interface

The Stratix architecture supports the MultiVolt I/O interface feature, which allows Stratix devices in all packages to interface with systems of different supply voltages.

The Stratix VCCINT pins must always be connected to a 1.5-V power supply. With a 1.5-V  $V_{CCINT}$  level, input pins are 1.5-V, 1.8-V, 2.5-V, and 3.3-V tolerant. The VCCIO pins can be connected to either a 1.5-V, 1.8-V, 2.5-V, or 3.3-V power supply, depending on the output requirements.

| Table 2-40.           | Table 2–40. EP1S60 Differential Channels (Part 2 of 2) Note (1) |                       |                 |            |                  |            |            |           |                           |            |        |  |

|-----------------------|-----------------------------------------------------------------|-----------------------|-----------------|------------|------------------|------------|------------|-----------|---------------------------|------------|--------|--|

|                       | Transmitter/                                                    | Total                 | Maximum         | C          | Center Fast PLLs |            |            |           | Corner Fast PLLs (2), (3) |            |        |  |

| Package               | Receiver                                                        | Channels              | Speed<br>(Mbps) | PLL1       | PLL2             | PLL3       | PLL4       | PLL7      | PLL8                      | PLL9       | PLL10  |  |

| 1,020-pin<br>FineLine | Transmitter (4)                                                 | 80 (12)<br><i>(7)</i> | 840             | 12<br>(2)  | 10<br>(4)        | 10<br>(4)  | 12<br>(2)  | 20        | 20                        | 20         | 20     |  |

| BGA                   |                                                                 |                       | 840 (5), (8)    | 22<br>(6)  | 22<br>(6)        | 22<br>(6)  | 22<br>(6)  | 20        | 20                        | 20         | 20     |  |

|                       | Receiver                                                        | 80 (10)<br><i>(7)</i> | 840             | 20         | 20               | 20         | 20         | 12<br>(8) | 10<br>(10)                | 10<br>(10) | 12 (8) |  |

|                       |                                                                 |                       | 840 (5), (8)    | 40         | 40               | 40         | 40         | 12<br>(8) | 10<br>(10)                | 10<br>(10) | 12 (8) |  |

| 1,508-pin<br>FineLine | Transmitter (4)                                                 | 80 (36)<br><i>(7)</i> | 840             | 12<br>(8)  | 10<br>(10)       | 10<br>(10) | 12<br>(8)  | 20        | 20                        | 20         | 20     |  |

| BGA                   |                                                                 |                       | 840 (5),(8)     | 22<br>(18) | 22<br>(18)       | 22<br>(18) | 22<br>(18) | 20        | 20                        | 20         | 20     |  |

|                       | Receiver                                                        | 80 (36)<br>(7)        | 840             | 20         | 20               | 20         | 20         | 12<br>(8) | 10<br>(10)                | 10<br>(10) | 12 (8) |  |

|                       |                                                                 |                       | 840 (5),(8)     | 40         | 40               | 40         | 40         | 12<br>(8) | 10<br>(10)                | 10<br>(10) | 12 (8) |  |

| Table 2-41.           | Table 2–41. EP1S80 Differential Channels (Part 1 of 2) Note (1) |                       |                 |           |           |           |           |                           |           |        |        |  |

|-----------------------|-----------------------------------------------------------------|-----------------------|-----------------|-----------|-----------|-----------|-----------|---------------------------|-----------|--------|--------|--|

|                       | Transmitter/                                                    | Total                 | Maximum         | C         | enter F   | ast PLI   | _S        | Corner Fast PLLs (2), (3) |           |        |        |  |

| Package               | Receiver                                                        | Channels              | Speed<br>(Mbps) | PLL1      | PLL2      | PLL3      | PLL4      | PLL7                      | PLL8      | PLL9   | PLL10  |  |

| 956-pin               | Transmitter                                                     | 80 (40)               | 840             | 10        | 10        | 10        | 10        | 20                        | 20        | 20     | 20     |  |

| BGA                   | (4)                                                             | (7)                   | 840 (5),(8)     | 20        | 20        | 20        | 20        | 20                        | 20        | 20     | 20     |  |

|                       | Receiver                                                        | 80                    | 840             | 20        | 20        | 20        | 20        | 10                        | 10        | 10     | 10     |  |

|                       |                                                                 |                       | 840 (5),(8)     | 40        | 40        | 40        | 40        | 10                        | 10        | 10     | 10     |  |

| 1,020-pin<br>FineLine | Transmitter (4)                                                 | 92 (12)<br><i>(7)</i> | 840             | 10<br>(2) | 10<br>(4) | 10<br>(4) | 10<br>(2) | 20                        | 20        | 20     | 20     |  |

| BGA                   |                                                                 |                       | 840 (5),(8)     | 20<br>(6) | 20<br>(6) | 20<br>(6) | 20<br>(6) | 20                        | 20        | 20     | 20     |  |

|                       | Receiver                                                        | 90 (10)<br>(7)        | 840             | 20        | 20        | 20        | 20        | 10<br>(2)                 | 10<br>(3) | 10 (3) | 10 (2) |  |

|                       |                                                                 |                       | 840 (5),(8)     | 40        | 40        | 40        | 40        | 10<br>(2)                 | 10<br>(3) | 10 (3) | 10 (2) |  |

## 3. Configuration & Testing

\$51003-1.3

## IEEE Std. 1149.1 (JTAG) Boundary-Scan Support

All Stratix® devices provide JTAG BST circuitry that complies with the IEEE Std. 1149.1a-1990 specification. JTAG boundary-scan testing can be performed either before or after, but not during configuration. Stratix devices can also use the JTAG port for configuration together with either the Quartus® II software or hardware using either Jam Files (.jam) or Jam Byte-Code Files (.jbc).

Stratix devices support IOE I/O standard setting reconfiguration through the JTAG BST chain. The JTAG chain can update the I/O standard for all input and output pins any time before or during user mode through the CONFIG\_IO instruction. You can use this ability for JTAG testing before configuration when some of the Stratix pins drive or receive from other devices on the board using voltage-referenced standards. Since the Stratix device may not be configured before JTAG testing, the I/O pins may not be configured for appropriate electrical standards for chip-to-chip communication. Programming those I/O standards via JTAG allows you to fully test the I/O connection to other devices.

The enhanced PLL reconfiguration bits are part of the JTAG chain before configuration and after power-up. After device configuration, the PLL reconfiguration bits are not part of the JTAG chain.

The JTAG pins support 1.5-V/1.8-V or 2.5-V/3.3-V I/O standards. The TDO pin voltage is determined by the  $V_{\rm CCIO}$  of the bank where it resides. The VCCSEL pin selects whether the JTAG inputs are 1.5-V, 1.8-V, 2.5-V, or 3.3-V compatible.

Stratix devices also use the JTAG port to monitor the logic operation of the device with the SignalTap<sup>®</sup> II embedded logic analyzer. Stratix devices support the JTAG instructions shown in Table 3–1.

The Quartus II software has an Auto Usercode feature where you can choose to use the checksum value of a programming file as the JTAG user code. If selected, the checksum is automatically loaded to the USERCODE register. In the Settings dialog box in the Assignments menu, click **Device & Pin Options**, then **General**, and then turn on the **Auto Usercode** option.

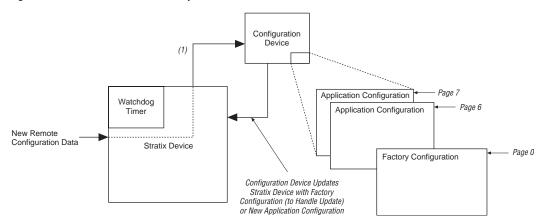

Figure 3-2. Stratix Device Remote Update

#### Note to Figure 3-2:

(1) When the Stratix device is configured with the factory configuration, it can handle update data from EPC16, EPC8, or EPC4 configuration device pages and point to the next page in the configuration device.

| Symbol                  | Parameter                                                                   | Conditions                                                                                 | Minimum | Typical | Maximum | Unit |  |

|-------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------|---------|---------|------|--|

| V <sub>ICM</sub>        | Input common mode voltage (6)                                               | LVDS<br>$0.3 \text{ V} \leq \text{V}_{\text{ID}} \leq 1.0 \text{ V}$<br>W = 1  through  10 | 100     |         | 1,100   | mV   |  |

|                         |                                                                             | LVDS<br>$0.3 \text{ V} \leq V_{\text{ID}} \leq 1.0 \text{ V}$<br>W = 1  through  10        | 1,600   |         | 1,800   | mV   |  |

|                         |                                                                             | LVDS<br>0.2 V ≤V <sub>ID</sub> ≤1.0 V<br>W = 1                                             | 1,100   |         | 1,600   | mV   |  |

|                         |                                                                             | LVDS<br>$0.1 \text{ V} \leq V_{\text{ID}} \leq 1.0 \text{ V}$<br>W = 2  through  10        | 1,100   |         | 1,600   | mV   |  |

| V <sub>OD</sub> (1)     | Output differential voltage (single-ended)                                  | R <sub>L</sub> = 100 Ω                                                                     | 250     | 375     | 550     | mV   |  |

| Δ V <sub>OD</sub>       | Change in V <sub>OD</sub> between high and low                              | R <sub>L</sub> = 100 Ω                                                                     |         |         | 50      | mV   |  |

| V <sub>OCM</sub>        | Output common mode voltage                                                  | $R_L = 100 \Omega$                                                                         | 1,125   | 1,200   | 1,375   | mV   |  |

| $\Delta V_{\text{OCM}}$ | Change in V <sub>OCM</sub> between high and low                             | $R_L = 100 \Omega$                                                                         |         |         | 50      | mV   |  |

| R <sub>L</sub>          | Receiver differential input discrete resistor (external to Stratix devices) |                                                                                            | 90      | 100     | 110     | Ω    |  |

| Table 4–39. DSP              | Block Internal Timing Microparameter Descriptions                                                                                                                                                                                                                                                                                                         |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                       | Parameter                                                                                                                                                                                                                                                                                                                                                 |

| t <sub>SU</sub>              | Input, pipeline, and output register setup time before clock                                                                                                                                                                                                                                                                                              |

| t <sub>H</sub>               | Input, pipeline, and output register hold time after clock                                                                                                                                                                                                                                                                                                |

| t <sub>co</sub>              | Input, pipeline, and output register clock-to-output delay                                                                                                                                                                                                                                                                                                |

| t <sub>INREG2PIPE9</sub>     | Input Register to DSP Block pipeline register in $9\times9$ -bit mode                                                                                                                                                                                                                                                                                     |

| t <sub>INREG2PIPE18</sub>    | Input Register to DSP Block pipeline register in 18 $\times$ 18-bit mode                                                                                                                                                                                                                                                                                  |

| t <sub>PIPE2OUTREG2ADD</sub> | DSP Block Pipeline Register to output register delay in Two-Multipliers Adder mode                                                                                                                                                                                                                                                                        |

| t <sub>PIPE2OUTREG4ADD</sub> | DSP Block Pipeline Register to output register delay in Four-Multipliers Adder mode                                                                                                                                                                                                                                                                       |

| t <sub>PD9</sub>             | Combinatorial input to output delay for $9 \times 9$                                                                                                                                                                                                                                                                                                      |

| t <sub>PD18</sub>            | Combinatorial input to output delay for 18 × 18                                                                                                                                                                                                                                                                                                           |

| t <sub>PD36</sub>            | Combinatorial input to output delay for $36 \times 36$                                                                                                                                                                                                                                                                                                    |

| t <sub>CLR</sub>             | Minimum clear pulse width                                                                                                                                                                                                                                                                                                                                 |

| t <sub>CLKHL</sub>           | Register minimum clock high or low time. This is a limit on the min time for the clock on the registers in these blocks. The actual performance is dependent upon the internal point-to-point delays in the blocks and may give slower performance as shown in Table 4–36 on page 4–20 and as reported by the timing analyzer in the Quartus II software. |

|                       | -5 Speed Grade |       | -6 Speed Grade |       | -7 Spee | d Grade | -8 Spee |     |      |

|-----------------------|----------------|-------|----------------|-------|---------|---------|---------|-----|------|

| Parameter             | Min            | Max   | Min            | Max   | Min     | Max     | Min     | Max | Unit |

| t <sub>INSU</sub>     | 1.351          |       | 1.479          |       | 1.699   |         | NA      |     | ns   |

| t <sub>INH</sub>      | 0.000          |       | 0.000          |       | 0.000   |         | NA      |     | ns   |

| t <sub>outco</sub>    | 2.732          | 5.380 | 2.732          | 5.728 | 2.732   | 6.240   | NA      | NA  | ns   |

| t <sub>XZ</sub>       | 2.672          | 5.254 | 2.672          | 5.596 | 2.672   | 6.116   | NA      | NA  | ns   |

| t <sub>ZX</sub>       | 2.672          | 5.254 | 2.672          | 5.596 | 2.672   | 6.116   | NA      | NA  | ns   |

| t <sub>INSUPLL</sub>  | 0.923          |       | 0.971          |       | 1.098   |         | NA      |     | ns   |

| t <sub>INHPLL</sub>   | 0.000          |       | 0.000          |       | 0.000   |         | NA      |     | ns   |

| t <sub>OUTCOPLL</sub> | 1.210          | 2.544 | 1.210          | 2.648 | 1.210   | 2.715   | NA      | NA  | ns   |

| t <sub>XZPLL</sub>    | 1.150          | 2.418 | 1.150          | 2.516 | 1.150   | 2.591   | NA      | NA  | ns   |

| t <sub>ZXPLL</sub>    | 1.150          | 2.418 | 1.150          | 2.516 | 1.150   | 2.591   | NA      | NA  | ns   |

| Table 4–64. l      | Table 4–64. EP1S20 External I/O Timing on Row Pins Using Fast Regional Clock Networks Note (1) |       |                |       |                |       |                |     |      |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------|-------|----------------|-------|----------------|-------|----------------|-----|------|--|--|--|--|

| Dougmotou          | -5 Speed Grade                                                                                 |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |     | 11   |  |  |  |  |

| Parameter          | Min                                                                                            | Max   | Min            | Max   | Min            | Max   | Min            | Max | Unit |  |  |  |  |

| t <sub>INSU</sub>  | 2.032                                                                                          |       | 2.207          |       | 2.535          |       | NA             |     | ns   |  |  |  |  |

| t <sub>INH</sub>   | 0.000                                                                                          |       | 0.000          |       | 0.000          |       | NA             |     | ns   |  |  |  |  |

| t <sub>OUTCO</sub> | 2.492                                                                                          | 5.018 | 2.492          | 5.355 | 2.492          | 5.793 | NA             | NA  | ns   |  |  |  |  |

| t <sub>XZ</sub>    | 2.519                                                                                          | 5.072 | 2.519          | 5.411 | 2.519          | 5.861 | NA             | NA  | ns   |  |  |  |  |

| t <sub>ZX</sub>    | 2.519                                                                                          | 5.072 | 2.519          | 5.411 | 2.519          | 5.861 | NA             | NA  | ns   |  |  |  |  |

Table 4–119. Stratix Maximum Input Clock Rate for CLK[1, 3, 8, 10] Pins in Wire-Bond Packages (Part 2 of 2)

| I/O Standard                  | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------|-------------------|-------------------|-------------------|------|

| SSTL-18 Class I               | 350               | 300               | 300               | MHz  |

| SSTL-18 Class II              | 350               | 300               | 300               | MHz  |

| 1.5-V HSTL Class I            | 350               | 300               | 300               | MHz  |

| 1.8-V HSTL Class I            | 350               | 300               | 300               | MHz  |

| CTT                           | 250               | 200               | 200               | MHz  |

| Differential 1.5-V HSTL<br>C1 | 350               | 300               | 300               | MHz  |

| LVPECL (1)                    | 645               | 622               | 622               | MHz  |

| PCML (1)                      | 275               | 275               | 275               | MHz  |

| LVDS (1)                      | 645               | 622               | 622               | MHz  |

| HyperTransport technology (1) | 500               | 450               | 450               | MHz  |

Note to Tables 4–114 through 4–119:

Tables 4–120 through 4–123 show the maximum output clock rate for column and row pins in Stratix devices.

Table 4–120. Stratix Maximum Output Clock Rate for PLL[5, 6, 11, 12] Pins in Flip-Chip Packages (Part 1 of 2)

| I/O Standard       | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |  |

|--------------------|-------------------|-------------------|-------------------|-------------------|------|--|

| LVTTL              | 350               | 300               | 250               | 250               | MHz  |  |

| 2.5 V              | 350               | 300               | 300               | 300               | MHz  |  |

| 1.8 V              | 250               | 250               | 250               | 250               | MHz  |  |

| 1.5 V              | 225               | 200               | 200               | 200               | MHz  |  |

| LVCMOS             | 350               | 300               | 250               | 250               | MHz  |  |

| GTL                | 200               | 167               | 125               | 125               | MHz  |  |

| GTL+               | 200               | 167               | 125               | 125               | MHz  |  |

| SSTL-3 Class I     | 200               | 167               | 167               | 133               | MHz  |  |

| SSTL-3 Class II    | 200               | 167               | 167               | 133               | MHz  |  |

| SSTL-2 Class I (3) | 200               | 200               | 167               | 167               | MHz  |  |

| SSTL-2 Class I (4) | 200               | 200               | 167               | 167               | MHz  |  |

| SSTL-2 Class I (5) | 150               | 134               | 134               | 134               | MHz  |  |

<sup>(1)</sup> These parameters are only available on row I/O pins.

# High-Speed I/O Specification

${\it Table 4-124 provides high-speed timing specifications definitions.}$

| Table 4–124. High-Speed Timing Specifications & Terminology |                                                                                                                                                                                                                                   |  |  |  |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| High-Speed Timing Specification                             | Terminology                                                                                                                                                                                                                       |  |  |  |

| tc                                                          | High-speed receiver/transmitter input and output clock period.                                                                                                                                                                    |  |  |  |

| f <sub>HSCLK</sub>                                          | High-speed receiver/transmitter input and output clock frequency.                                                                                                                                                                 |  |  |  |

| t <sub>RISE</sub>                                           | Low-to-high transmission time.                                                                                                                                                                                                    |  |  |  |

| t <sub>FALL</sub>                                           | High-to-low transmission time.                                                                                                                                                                                                    |  |  |  |

| Timing unit interval (TUI)                                  | The timing budget allowed for skew, propagation delays, and data sampling window. (TUI = $1/(Receiver\ Input\ Clock\ Frequency \times Multiplication\ Factor) = t_C/w)$ .                                                         |  |  |  |

| f <sub>HSDR</sub>                                           | Maximum LVDS data transfer rate (f <sub>HSDR</sub> = 1/TUI).                                                                                                                                                                      |  |  |  |

| Channel-to-channel skew (TCCS)                              | The timing difference between the fastest and slowest output edges, including $t_{\text{CO}}$ variation and clock skew. The clock is included in the TCCS measurement.                                                            |  |  |  |

| Sampling window (SW)                                        | The period of time during which the data must be valid to be captured correctly. The setup and hold times determine the ideal strobe position within the sampling window. $SW = t_{SW} \; (\text{max}) - t_{SW} \; (\text{min}).$ |  |  |  |

| Input jitter (peak-to-peak)                                 | Peak-to-peak input jitter on high-speed PLLs.                                                                                                                                                                                     |  |  |  |

| Output jitter (peak-to-peak)                                | Peak-to-peak output jitter on high-speed PLLs.                                                                                                                                                                                    |  |  |  |

| t <sub>DUTY</sub>                                           | Duty cycle on high-speed transmitter output clock.                                                                                                                                                                                |  |  |  |

| t <sub>LOCK</sub>                                           | Lock time for high-speed transmitter and receiver PLLs.                                                                                                                                                                           |  |  |  |

| J                                                           | Deserialization factor (width of internal data bus).                                                                                                                                                                              |  |  |  |

| W                                                           | PLL multiplication factor.                                                                                                                                                                                                        |  |  |  |