Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Obsolete                                                  |

| Number of LABs/CLBs            | 4125                                                      |

| Number of Logic Elements/Cells | 41250                                                     |

| Total RAM Bits                 | 3423744                                                   |

| Number of I/O                  | 773                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.425V ~ 1.575V                                           |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 1020-BBGA                                                 |

| Supplier Device Package        | 1020-FBGA (33x33)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s40f1020c7n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Typographic Conventions

This document uses the typographic conventions shown below.

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial<br>Capital Letters   | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                                                                                              |

| bold type                                   | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: f <sub>MAX</sub> , \qdesigns directory, d: drive, chiptrip.gdf file.                                                                         |

| Italic Type with Initial Capital<br>Letters | Document titles are shown in italic type with initial capital letters. Example: AN 75: High-Speed Board Designs.                                                                                                                                                                                                        |

| Italic type                                 | Internal timing parameters and variables are shown in italic type. Examples: $t_{PlA}$ , $n+1$ .                                                                                                                                                                                                                        |

|                                             | Variable names are enclosed in angle brackets (< >) and shown in italic type. Example: <file name="">, <pre><pre><pre><pre><pre><pre><pre><pre></pre></pre></pre></pre></pre></pre></pre></pre></file>                                                                                                                  |

| Initial Capital Letters                     | Keyboard keys and menu names are shown with initial capital letters. Examples: Delete key, the Options menu.                                                                                                                                                                                                            |

| "Subheading Title"                          | References to sections within a document and titles of on-line help topics are shown in quotation marks. Example: "Typographic Conventions."                                                                                                                                                                            |

| Courier type                                | Signal and port names are shown in lowercase Courier type. Examples: $\mathtt{data1}$ , $\mathtt{tdi}$ , $\mathtt{input}$ . Active-low signals are denoted by suffix $\mathtt{n}$ , $\mathtt{e.g.}$ , $\mathtt{resetn}$ .                                                                                               |

|                                             | Anything that must be typed exactly as it appears is shown in Courier type. For example: c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an actual file, such as a Report File, references to parts of files (e.g., the AHDL keyword SUBDESIGN), as well as logic function names (e.g., TRI) are shown in Courier. |

| 1., 2., 3., and<br>a., b., c., etc.         | Numbered steps are used in a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                                                                                                                                                        |

| • •                                         | Bullets are used in a list of items when the sequence of the items is not important.                                                                                                                                                                                                                                    |

| ✓                                           | The checkmark indicates a procedure that consists of one step only.                                                                                                                                                                                                                                                     |

|                                             | The hand points to information that requires special attention.                                                                                                                                                                                                                                                         |

| 4                                           | The angled arrow indicates you should press the Enter key.                                                                                                                                                                                                                                                              |

|                                             | The feet direct you to more information on a particular topic.                                                                                                                                                                                                                                                          |

x Altera Corporation

# **Features**

The Stratix family offers the following features:

- 10,570 to 79,040 LEs; see Table 1–1

- Up to 7,427,520 RAM bits (928,440 bytes) available without reducing logic resources

- TriMatrix<sup>™</sup> memory consisting of three RAM block sizes to implement true dual-port memory and first-in first-out (FIFO) buffers

- High-speed DSP blocks provide dedicated implementation of multipliers (faster than 300 MHz), multiply-accumulate functions, and finite impulse response (FIR) filters

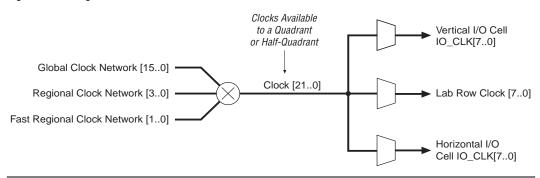

- Up to 16 global clocks with 22 clocking resources per device region

- Up to 12 PLLs (four enhanced PLLs and eight fast PLLs) per device provide spread spectrum, programmable bandwidth, clock switchover, real-time PLL reconfiguration, and advanced multiplication and phase shifting

- Support for numerous single-ended and differential I/O standards

- High-speed differential I/O support on up to 116 channels with up to 80 channels optimized for 840 megabits per second (Mbps)

- Support for high-speed networking and communications bus standards including RapidIO, UTOPIA IV, CSIX, HyperTransport™ technology, 10G Ethernet XSBI, SPI-4 Phase 2 (POS-PHY Level 4), and SFI-4

- Differential on-chip termination support for LVDS

- Support for high-speed external memory, including zero bus turnaround (ZBT) SRAM, quad data rate (QDR and QDRII) SRAM, double data rate (DDR) SDRAM, DDR fast cycle RAM (FCRAM), and single data rate (SDR) SDRAM

- Support for 66-MHz PCI (64 and 32 bit) in -6 and faster speed-grade devices, support for 33-MHz PCI (64 and 32 bit) in -8 and faster speed-grade devices

- Support for 133-MHz PCI-X 1.0 in -5 speed-grade devices

- Support for 100-MHz PCI-X 1.0 in -6 and faster speed-grade devices

- Support for 66-MHz PCI-X 1.0 in -7 speed-grade devices

- Support for multiple intellectual property megafunctions from Altera MegaCore<sup>®</sup> functions and Altera Megafunction Partners Program (AMPP<sup>SM</sup>) megafunctions

- Support for remote configuration updates

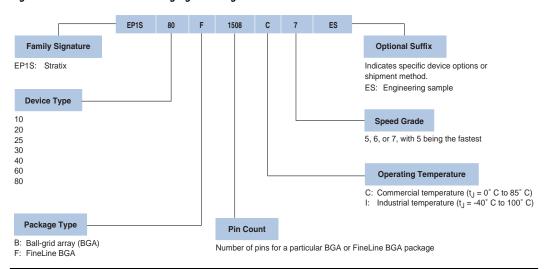

Stratix devices are available in space-saving FineLine BGA® and ball-grid array (BGA) packages (see Tables 1–3 through 1–5). All Stratix devices support vertical migration within the same package (for example, you can migrate between the EP1S10, EP1S20, and EP1S25 devices in the 672-pin BGA package). Vertical migration means that you can migrate to devices whose dedicated pins, configuration pins, and power pins are the same for a given package across device densities. For I/O pin migration across densities, you must cross-reference the available I/O pins using the device pin-outs for all planned densities of a given package type to identify which I/O pins are migrational. The Quartus® II software can automatically cross reference and place all pins except differential pins for migration when given a device migration list. You must use the pin-outs for each device to verify the differential placement migration. A future version of the Quartus II software will support differential pin migration.

| Table 1-3. | Table 1–3. Stratix Package Options & I/O Pin Counts |                |                            |                            |                            |                              |                              |  |  |  |  |

|------------|-----------------------------------------------------|----------------|----------------------------|----------------------------|----------------------------|------------------------------|------------------------------|--|--|--|--|

| Device     | 672-Pin<br>BGA                                      | 956-Pin<br>BGA | 484-Pin<br>FineLine<br>BGA | 672-Pin<br>FineLine<br>BGA | 780-Pin<br>FineLine<br>BGA | 1,020-Pin<br>FineLine<br>BGA | 1,508-Pin<br>FineLine<br>BGA |  |  |  |  |

| EP1S10     | 345                                                 |                | 335                        | 345                        | 426                        |                              |                              |  |  |  |  |

| EP1S20     | 426                                                 |                | 361                        | 426                        | 586                        |                              |                              |  |  |  |  |

| EP1S25     | 473                                                 |                |                            | 473                        | 597                        | 706                          |                              |  |  |  |  |

| EP1S30     |                                                     | 683            |                            |                            | 597                        | 726                          |                              |  |  |  |  |

| EP1S40     |                                                     | 683            |                            |                            | 615                        | 773                          | 822                          |  |  |  |  |

| EP1S60     |                                                     | 683            |                            |                            |                            | 773                          | 1,022                        |  |  |  |  |

| EP1S80     |                                                     | 683            |                            |                            |                            | 773                          | 1,203                        |  |  |  |  |

#### Note to Table 1-3:

<sup>(1)</sup> All I/O pin counts include 20 dedicated clock input pins (clk [15..0] p, clk0n, clk2n, clk9n, and clk11n) that can be used for data inputs.

| Table 1–4. Stratix BGA Package Sizes |                                                                      |  |  |  |  |  |  |  |  |

|--------------------------------------|----------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Dimension 672 Pin 956 Pin            |                                                                      |  |  |  |  |  |  |  |  |

| Pitch (mm)                           | Pitch (mm) 1.27 1.27                                                 |  |  |  |  |  |  |  |  |

| Area (mm²) 1,225 1,600               |                                                                      |  |  |  |  |  |  |  |  |

| Length × width (mm × mm)             | Length $\times$ width (mm $\times$ mm) 35 $\times$ 35 40 $\times$ 40 |  |  |  |  |  |  |  |  |

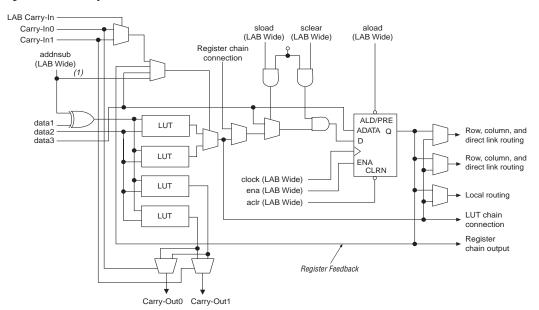

Figure 2-7. LE in Dynamic Arithmetic Mode

*Note to Figure 2–7:*

(1) The addnsub signal is tied to the carry input for the first LE of a carry chain only.

### Carry-Select Chain

The carry-select chain provides a very fast carry-select function between LEs in arithmetic mode. The carry-select chain uses the redundant carry calculation to increase the speed of carry functions. The LE is configured to calculate outputs for a possible carry-in of 1 and carry-in of 0 in parallel. The carry-in0 and carry-in1 signals from a lower-order bit feed forward into the higher-order bit via the parallel carry chain and feed into both the LUT and the next portion of the carry chain. Carry-select chains can begin in any LE within an LAB.

The speed advantage of the carry-select chain is in the parallel precomputation of carry chains. Since the LAB carry-in selects the precomputed carry chain, not every LE is in the critical path. Only the propagation delay between LAB carry-in generation (LE 5 and LE 10) are now part of the critical path. This feature allows the Stratix architecture to implement high-speed counters, adders, multipliers, parity functions, and comparators of arbitrary width.

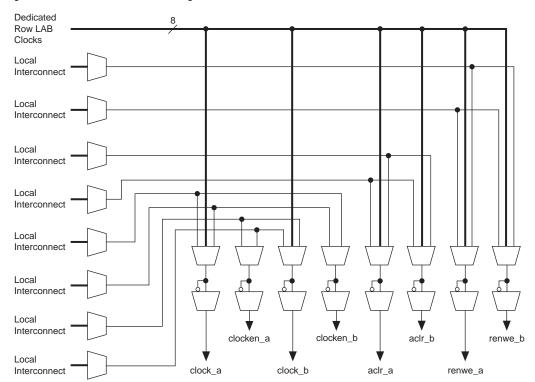

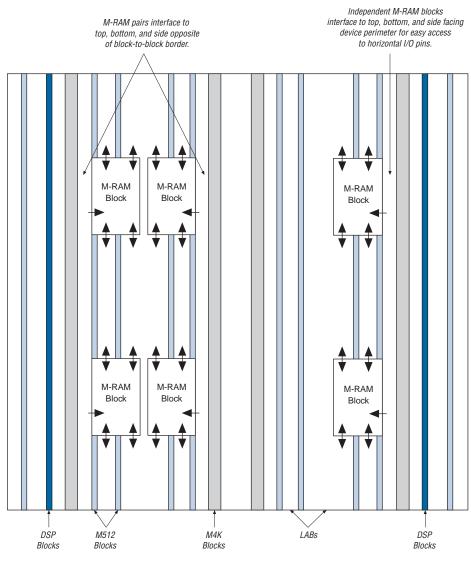

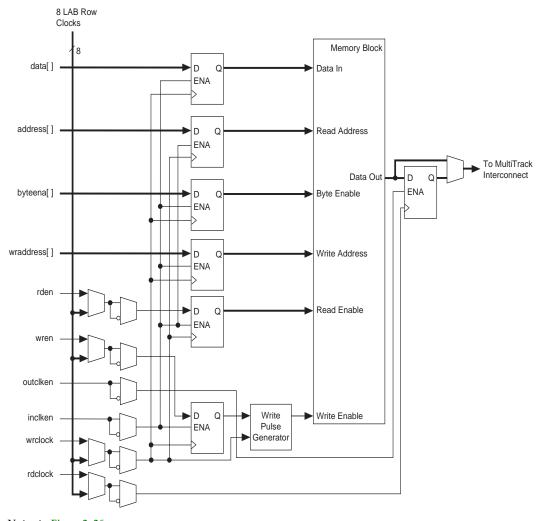

Figure 2-19. M-RAM Block Control Signals

One of the M-RAM block's horizontal sides drive the address and control signal (clock, renwe, byteena, etc.) inputs. Typically, the horizontal side closest to the device perimeter contains the interfaces. The one exception is when two M-RAM blocks are paired next to each other. In this case, the side of the M-RAM block opposite the common side of the two blocks contains the input interface. The top and bottom sides of any M-RAM block contain data input and output interfaces to the logic array. The top side has 72 data inputs and 72 data outputs for port B, and the bottom side has another 72 data inputs and 72 data outputs for port A. Figure 2–20 shows an example floorplan for the EP1S60 device and the location of the M-RAM interfaces.

Figure 2–20. EP1S60 Device with M-RAM Interface Locations Note (1)

*Note to Figure 2–20:*

(1) Device shown is an EP1S60 device. The number and position of M-RAM blocks varies in other devices.

The M-RAM block local interconnect is driven by the R4, R8, C4, C8, and direct link interconnects from adjacent LABs. For independent M-RAM blocks, up to 10 direct link address and control signal input connections to the M-RAM block are possible from the left adjacent LABs for M-RAM

# **Independent Clock Mode**

The memory blocks implement independent clock mode for true dual-port memory. In this mode, a separate clock is available for each port (ports A and B). Clock A controls all registers on the port A side, while clock B controls all registers on the port B side. Each port, A and B, also supports independent clock enables and asynchronous clear signals for port A and B registers. Figure 2–24 shows a TriMatrix memory block in independent clock mode.

Figure 2–26. Input/Output Clock Mode in Simple Dual-Port Mode Notes (1), (2)

#### Notes to Figure 2–26:

- (1) All registers shown except the rden register have asynchronous clear ports.

- (2) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

Figure 2-46. Regional Clock Bus

IOE clocks have horizontal and vertical block regions that are clocked by eight I/O clock signals chosen from the 22 quadrant or half-quadrant clock resources. Figures 2–47 and 2–48 show the quadrant and half-quadrant relationship to the I/O clock regions, respectively. The vertical regions (column pins) have less clock delay than the horizontal regions (row pins).

provide general purpose clocking with multiplication and phase shifting as well as high-speed outputs for high-speed differential I/O support. Enhanced and fast PLLs work together with the Stratix high-speed I/O and advanced clock architecture to provide significant improvements in system performance and bandwidth.

The Quartus II software enables the PLLs and their features without requiring any external devices. Table 2–18 shows the PLLs available for each Stratix device.

| Table 2-18 | 3. Stratix | . Device | PLL Ava  | ailabilit     | y            |              |              |              |          |          |               |               |

|------------|------------|----------|----------|---------------|--------------|--------------|--------------|--------------|----------|----------|---------------|---------------|

| Davisa     |            |          |          | Enhanced PLLs |              |              |              |              |          |          |               |               |

| Device     | 1          | 2        | 3        | 4             | 7            | 8            | 9            | 10           | 5(1)     | 6(1)     | <b>11</b> (2) | <b>12</b> (2) |

| EP1S10     | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b>      |              |              |              |              | <b>✓</b> | <b>✓</b> |               |               |

| EP1S20     | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b>      |              |              |              |              | <b>✓</b> | <b>✓</b> |               |               |

| EP1S25     | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b>      |              |              |              |              | <b>✓</b> | <b>✓</b> |               |               |

| EP1S30     | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b>      | <b>√</b> (3) | <b>√</b> (3) | <b>√</b> (3) | <b>√</b> (3) | <b>✓</b> | <b>✓</b> |               |               |

| EP1S40     | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b>      | <b>√</b> (3) | <b>√</b> (3) | <b>√</b> (3) | <b>√</b> (3) | <b>✓</b> | <b>✓</b> | <b>√</b> (3)  | <b>√</b> (3)  |

| EP1S60     | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b>      | <b>✓</b>     | <b>✓</b>     | <b>✓</b>     | <b>✓</b>     | <b>✓</b> | <b>✓</b> | <b>✓</b>      | <b>✓</b>      |

| EP1S80     | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b>      | <b>✓</b>     | <b>✓</b>     | <b>✓</b>     | <b>✓</b>     | <b>✓</b> | <b>✓</b> | <b>✓</b>      | <b>✓</b>      |

#### Notes to Table 2–18:

- (1) PLLs 5 and 6 each have eight single-ended outputs or four differential outputs.

- (2) PLLs 11 and 12 each have one single-ended output.

- (3) EP1S30 and EP1S40 devices do not support these PLLs in the 780-pin FineLine BGA® package.

Post-Scale Counters → diffioclk1 (2) Global or ÷/0 regional clock txload\_en (3) VCO Phase Selection Selectable at each PLL Output Port Phase rxload\_en (3) Frequency ÷/1 Global or Detector Global or regional clock regional clock (1) ► diffioclk2 (2) Charge Loop Global or PFD VCO ÷ g0 Clock □ Pump Filter regional clock Input [  $\pm m$

Figure 2-58. Stratix Device Fast PLL

#### *Notes to Figure 2–58:*

- The global or regional clock input can be driven by an output from another PLL or any dedicated CLK or FCLK pin.

It cannot be driven by internally-generated global signals.

- (2) In high-speed differential I/O support mode, this high-speed PLL clock feeds the SERDES. Stratix devices only support one rate of data transfer per fast PLL in high-speed differential I/O support mode.

- (3) This signal is a high-speed differential I/O support SERDES control signal.

#### Clock Multiplication & Division

Stratix device fast PLLs provide clock synthesis for PLL output ports using m/(post scaler) scaling factors. The input clock is multiplied by the m feedback factor. Each output port has a unique post scale counter to divide down the high-frequency VCO. There is one multiply divider, m, per fast PLL with a range of 1 to 32. There are two post scale L dividers for regional and/or LVDS interface clocks, and g0 counter for global clock output port; all range from 1 to 32.

In the case of a high-speed differential interface, set the output counter to 1 to allow the high-speed VCO frequency to drive the SERDES. When used for clocking the SERDES, the m counter can range from 1 to 30. The VCO frequency is equal to  $f_{\rm IN}\times m$ , where VCO frequency must be between 300 and 1000 MHz.

- 1.8-V HSTL Class I and II

- SSTL-3 Class I and II

- SSTL-2 Class I and II

- SSTL-18 Class I and II

- CTT

Table 2–31 describes the I/O standards supported by Stratix devices.

| Table 2–31. Stratix Supp  | orted I/O Standards |                                                       |                                                      |                                                           |

|---------------------------|---------------------|-------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------|

| I/O Standard              | Туре                | Input Reference<br>Voltage (V <sub>REF</sub> )<br>(V) | Output Supply<br>Voltage (V <sub>CCIO</sub> )<br>(V) | Board<br>Termination<br>Voltage (V <sub>TT</sub> )<br>(V) |

| LVTTL                     | Single-ended        | N/A                                                   | 3.3                                                  | N/A                                                       |

| LVCMOS                    | Single-ended        | N/A                                                   | 3.3                                                  | N/A                                                       |

| 2.5 V                     | Single-ended        | N/A                                                   | 2.5                                                  | N/A                                                       |

| 1.8 V                     | Single-ended        | N/A                                                   | 1.8                                                  | N/A                                                       |

| 1.5 V                     | Single-ended        | N/A                                                   | 1.5                                                  | N/A                                                       |

| 3.3-V PCI                 | Single-ended        | N/A                                                   | 3.3                                                  | N/A                                                       |

| 3.3-V PCI-X 1.0           | Single-ended        | N/A                                                   | 3.3                                                  | N/A                                                       |

| LVDS                      | Differential        | N/A                                                   | 3.3                                                  | N/A                                                       |

| LVPECL                    | Differential        | N/A                                                   | 3.3                                                  | N/A                                                       |

| 3.3-V PCML                | Differential        | N/A                                                   | 3.3                                                  | N/A                                                       |

| HyperTransport            | Differential        | N/A                                                   | 2.5                                                  | N/A                                                       |

| Differential HSTL (1)     | Differential        | 0.75                                                  | 1.5                                                  | 0.75                                                      |

| Differential SSTL (2)     | Differential        | 1.25                                                  | 2.5                                                  | 1.25                                                      |

| GTL                       | Voltage-referenced  | 0.8                                                   | N/A                                                  | 1.20                                                      |

| GTL+                      | Voltage-referenced  | 1.0                                                   | N/A                                                  | 1.5                                                       |

| 1.5-V HSTL Class I and II | Voltage-referenced  | 0.75                                                  | 1.5                                                  | 0.75                                                      |

| 1.8-V HSTL Class I and II | Voltage-referenced  | 0.9                                                   | 1.8                                                  | 0.9                                                       |

| SSTL-18 Class I and II    | Voltage-referenced  | 0.90                                                  | 1.8                                                  | 0.90                                                      |

| SSTL-2 Class I and II     | Voltage-referenced  | 1.25                                                  | 2.5                                                  | 1.25                                                      |

| SSTL-3 Class I and II     | Voltage-referenced  | 1.5                                                   | 3.3                                                  | 1.5                                                       |

| AGP (1× and 2°)           | Voltage-referenced  | 1.32                                                  | 3.3                                                  | N/A                                                       |

| CTT                       | Voltage-referenced  | 1.5                                                   | 3.3                                                  | 1.5                                                       |

#### Notes to Table 2–31:

- (1) This I/O standard is only available on input and output clock pins.

- (2) This I/O standard is only available on output column clock pins.

For more information on I/O standards supported by Stratix devices, see the *Selectable I/O Standards in Stratix & Stratix GX Devices* chapter of the *Stratix Device Handbook, Volume 2*.

Stratix devices contain eight I/O banks in addition to the four enhanced PLL external clock out banks, as shown in Figure 2–70. The four I/O banks on the right and left of the device contain circuitry to support high-speed differential I/O for LVDS, LVPECL, 3.3-V PCML, and HyperTransport inputs and outputs. These banks support all I/O standards listed in Table 2–31 except PCI I/O pins or PCI-X 1.0, GTL, SSTL-18 Class II, and HSTL Class II outputs. The top and bottom I/O banks support all single-ended I/O standards. Additionally, Stratix devices support four enhanced PLL external clock output banks, allowing clock output capabilities such as differential support for SSTL and HSTL. Table 2–32 shows I/O standard support for each I/O bank.

- RapidIO

- HyperTransport

## **Dedicated Circuitry**

Stratix devices support source-synchronous interfacing with LVDS, LVPECL, 3.3-V PCML, or HyperTransport signaling at up to 840 Mbps. Stratix devices can transmit or receive serial channels along with a low-speed or high-speed clock. The receiving device PLL multiplies the clock by a integer factor W (W = 1 through 32). For example, a HyperTransport application where the data rate is 800 Mbps and the clock rate is 400 MHz would require that W be set to 2. The SERDES factor J determines the parallel data width to deserialize from receivers or to serialize for transmitters. The SERDES factor J can be set to 4, 7, 8, or 10 and does not have to equal the PLL clock-multiplication W value. For a J factor of 1, the Stratix device bypasses the SERDES block. For a J factor of 2, the Stratix device bypasses the SERDES block, and the DDR input and output registers are used in the IOE. See Figure 2–73.

R4, R8, and R24 Interconnect 840 Mbps 840 Mbps 8 Data Dedicated Dedicated Local Receiver Transmitter Interconnect Interface Interface rx load en 8× 8× 105 MHz Fast tx\_load\_en PLL Regional or global clock

Figure 2–73. High-Speed Differential I/O Receiver / Transmitter Interface Example

An external pin or global or regional clock can drive the fast PLLs, which can output up to three clocks: two multiplied high-speed differential I/O clocks to drive the SERDES block and/or external pin, and a low-speed clock to drive the logic array.

| Table 4–31       | . CTT I/O Specifications                       |                                           |                        |         |                        |      |

|------------------|------------------------------------------------|-------------------------------------------|------------------------|---------|------------------------|------|

| Symbol           | Parameter                                      | Conditions                                | Minimum                | Typical | Maximum                | Unit |

| $V_{CCIO}$       | Output supply voltage                          |                                           | 2.05                   | 3.3     | 3.6                    | V    |

| $V_{TT}/V_{REF}$ | Termination and input reference voltage        |                                           | 1.35                   | 1.5     | 1.65                   | V    |

| V <sub>IH</sub>  | High-level input voltage                       |                                           | V <sub>REF</sub> + 0.2 |         |                        | V    |

| V <sub>IL</sub>  | Low-level input voltage                        |                                           |                        |         | V <sub>REF</sub> - 0.2 | V    |

| V <sub>OH</sub>  | High-level output voltage                      | $I_{OH} = -8 \text{ mA}$                  | V <sub>REF</sub> + 0.4 |         |                        | V    |

| V <sub>OL</sub>  | Low-level output voltage                       | I <sub>OL</sub> = 8 mA                    |                        |         | V <sub>REF</sub> - 0.4 | V    |

| Io               | Output leakage current (when output is high Z) | GND ≤V <sub>OUT</sub> ≤ V <sub>CCIO</sub> | -10                    |         | 10                     | μΑ   |

| Table 4–32. Bu          | Table 4–32. Bus Hold Parameters                |     |                         |      |      |                 |      |     |      |      |  |  |

|-------------------------|------------------------------------------------|-----|-------------------------|------|------|-----------------|------|-----|------|------|--|--|

|                         |                                                |     | V <sub>CCIO</sub> Level |      |      |                 |      |     |      |      |  |  |

| Parameter               | Conditions                                     | 1.5 | 5 V                     | 1.8  | B V  | 2.5             | 5 V  | 3.5 | 3 V  | Unit |  |  |

|                         |                                                | Min | Max                     | Min  | Max  | Min             | Max  | Min | Max  |      |  |  |

| Low sustaining current  | $V_{IN} > V_{IL}$ (maximum)                    | 25  |                         | 30   |      | 50              |      | 70  |      | μА   |  |  |

| High sustaining current | V <sub>IN</sub> < V <sub>IH</sub><br>(minimum) | -25 |                         | -30  |      | <del>-</del> 50 |      | -70 |      | μА   |  |  |

| Low overdrive current   | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      |     | 160                     |      | 200  |                 | 300  |     | 500  | μА   |  |  |

| High overdrive current  | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      |     | -160                    |      | -200 |                 | -300 |     | -500 | μА   |  |  |

| Bus-hold trip point     |                                                | 0.5 | 1.0                     | 0.68 | 1.07 | 0.7             | 1.7  | 0.8 | 2.0  | V    |  |  |

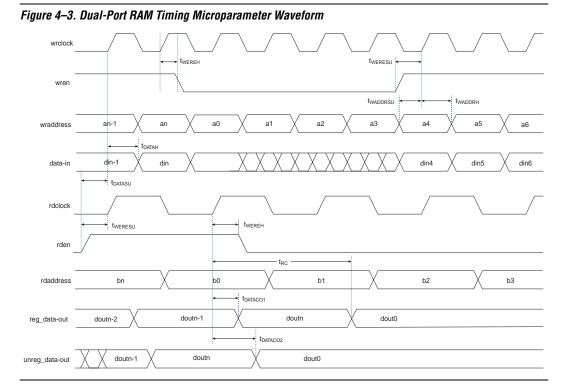

Figure 4–3 shows the TriMatrix memory waveforms for the M512, M4K, and M-RAM timing parameters shown in Tables 4–40 through 4–42.

Internal timing parameters are specified on a speed grade basis independent of device density. Tables 4–44 through 4–50 show the internal timing microparameters for LEs, IOEs, TriMatrix memory structures, DSP blocks, and MultiTrack interconnects.

|                  | Table 4–43. Routing Delay Internal Timing Microparameter<br>Descriptions (Part 1 of 2) |  |  |  |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Symbol           | Symbol Parameter                                                                       |  |  |  |  |  |  |  |  |  |

| t <sub>R4</sub>  | Delay for an R4 line with average loading; covers a distance of four LAB columns.      |  |  |  |  |  |  |  |  |  |

| t <sub>R8</sub>  | Delay for an R8 line with average loading; covers a distance of eight LAB columns.     |  |  |  |  |  |  |  |  |  |

| t <sub>R24</sub> | Delay for an R24 line with average loading; covers a distance of 24 LAB columns.       |  |  |  |  |  |  |  |  |  |

| Table 4–47. DSP Block Internal Timing Microparameters (Part 2 of 2) |       |       |       |       |       |       |       |        |      |  |  |

|---------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--------|------|--|--|

| Chal                                                                | -     | 5     | -     | 6     | -     | -7    |       | -8     |      |  |  |

| Symbol                                                              | Min   | Max   | Min   | Max   | Min   | Max   | Min   | Max    | Unit |  |  |

| t <sub>PIPE2OUTREG2ADD</sub>                                        |       | 2,002 |       | 2,203 |       | 2,533 |       | 2,980  | ps   |  |  |

| t <sub>PIPE2OUTREG4ADD</sub>                                        |       | 2,899 |       | 3,189 |       | 3,667 |       | 4,314  | ps   |  |  |

| t <sub>PD9</sub>                                                    |       | 3,709 |       | 4,081 |       | 4,692 |       | 5,520  | ps   |  |  |

| t <sub>PD18</sub>                                                   |       | 4,795 |       | 5,275 |       | 6,065 |       | 7,135  | ps   |  |  |

| t <sub>PD36</sub>                                                   |       | 7,495 |       | 8,245 |       | 9,481 |       | 11,154 | ps   |  |  |

| t <sub>CLR</sub>                                                    | 450   |       | 500   |       | 575   |       | 676   |        | ps   |  |  |

| t <sub>CLKHL</sub>                                                  | 1,350 |       | 1,500 |       | 1,724 |       | 2,029 |        | ps   |  |  |

| Table 4–48. M512         | Block Intern | al Timing | Micropar | ameters |       |       |       |       |         |

|--------------------------|--------------|-----------|----------|---------|-------|-------|-------|-------|---------|

| Ourseh e l               | -            | 5         | -        | -6      |       | -7    |       | 8     | II.a.iA |

| Symbol                   | Min          | Max       | Min      | Max     | Min   | Max   | Min   | Max   | Unit    |

| t <sub>M512RC</sub>      |              | 3,340     |          | 3,816   |       | 4,387 |       | 5,162 | ps      |

| t <sub>M512WC</sub>      |              | 3,138     |          | 3,590   |       | 4,128 |       | 4,860 | ps      |

| t <sub>M512WERESU</sub>  | 110          |           | 123      |         | 141   |       | 166   |       | ps      |

| t <sub>M512WEREH</sub>   | 34           |           | 38       |         | 43    |       | 51    |       | ps      |

| t <sub>M512CLKENSU</sub> | 215          |           | 215      |         | 247   |       | 290   |       | ps      |

| t <sub>M512CLKENH</sub>  | -70          |           | -70      |         | -81   |       | -95   |       | ps      |

| t <sub>M512DATASU</sub>  | 110          |           | 123      |         | 141   |       | 166   |       | ps      |

| t <sub>M512DATAH</sub>   | 34           |           | 38       |         | 43    |       | 51    |       | ps      |

| t <sub>M512WADDRSU</sub> | 110          |           | 123      |         | 141   |       | 166   |       | ps      |

| t <sub>M512WADDRH</sub>  | 34           |           | 38       |         | 43    |       | 51    |       | ps      |

| t <sub>M512RADDRSU</sub> | 110          |           | 123      |         | 141   |       | 166   |       | ps      |

| t <sub>M512RADDRH</sub>  | 34           |           | 38       |         | 43    |       | 51    |       | ps      |

| t <sub>M512DATACO1</sub> |              | 424       |          | 472     |       | 541   |       | 637   | ps      |

| t <sub>M512DATACO2</sub> |              | 3,366     |          | 3,846   |       | 4,421 |       | 5,203 | ps      |

| t <sub>M512CLKHL</sub>   | 1,000        |           | 1,111    |         | 1,190 |       | 1,400 |       | ps      |

| t <sub>M512CLR</sub>     | 170          |           | 189      |         | 217   |       | 255   |       | ps      |

#### Skew on Input Pins

Table 4–99 shows the package skews that were considered to get the worst case I/O skew value. You can use these values, for example, when calculating the timing budget on the input (read) side of a memory interface.

| Table 4–99. Package Skew on Input Pins         |                      |  |  |  |  |  |  |

|------------------------------------------------|----------------------|--|--|--|--|--|--|

| Package Parameter                              | Worst-Case Skew (ps) |  |  |  |  |  |  |

| Pins in the same I/O bank                      | 50                   |  |  |  |  |  |  |

| Pins in top/bottom (vertical I/O) banks        | 50                   |  |  |  |  |  |  |

| Pins in left/right side (horizontal I/O) banks | 50                   |  |  |  |  |  |  |

| Pins across the entire device                  | 100                  |  |  |  |  |  |  |

#### PLL Counter & Clock Network Skews

Table 4–100 shows the clock skews between different clock outputs from the Stratix device PLL.

| Table 4–100. PLL Counter & Clock Network Skews                                                        |                      |  |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|--|--|--|--|--|

| Parameter                                                                                             | Worst-Case Skew (ps) |  |  |  |  |  |  |  |  |  |

| Clock skew between two external clock outputs driven by the same counter                              | 100                  |  |  |  |  |  |  |  |  |  |

| Clock skew between two external clock outputs driven by the different counters with the same settings | 150                  |  |  |  |  |  |  |  |  |  |

| Dual-purpose PLL dedicated clock output used as I/O pin vs. regular I/O pin                           | 270 (1)              |  |  |  |  |  |  |  |  |  |

| Clock skew between any two outputs of the PLL that drive global clock networks                        | 150                  |  |  |  |  |  |  |  |  |  |

Note to Table 4-100:

(1) The Quartus II software models 270 ps of delay on the PLL dedicated clock output (PLL6\_OUT[3..0]p/n and PLL5\_OUT[3..0]p/n) pins both when used as clocks and when used as I/O pins.

# I/O Timing Measurement Methodology

Different I/O standards require different baseline loading techniques for reporting timing delays. Altera characterizes timing delays with the required termination and loading for each I/O standard. The timing information is specified from the input clock pin up to the output pin of

Tables 4–125 and 4–126 show the high-speed I/O timing for Stratix devices.

| Symbol                                                                                                                                         | Conditions                         | -5 Speed Grade |     |     | -6 Speed Grade |     |     | -7 Speed Grade |     |     | -8 Speed Grade |     |       | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|-----|-----|----------------|-----|-----|----------------|-----|-----|----------------|-----|-------|------|

|                                                                                                                                                |                                    | Min            | Тур | Max   |      |

| f <sub>HSCLK</sub> (Clock<br>frequency)<br>(LVDS,<br>LVPECL,<br>HyperTransport<br>technology)<br>f <sub>HSCLK</sub> = f <sub>HSDR</sub> /<br>W | W = 4 to 30<br>(Serdes used)       | 10             |     | 210 | 10             |     | 210 | 10             |     | 156 | 10             |     | 115.5 | MHz  |

|                                                                                                                                                | W = 2 (Serdes bypass)              | 50             |     | 231 | 50             |     | 231 | 50             |     | 231 | 50             |     | 231   | MHz  |

|                                                                                                                                                | W = 2 (Serdes used)                | 150            |     | 420 | 150            |     | 420 | 150            |     | 312 | 150            |     | 231   | MHz  |

|                                                                                                                                                | W = 1 (Serdes bypass)              | 100            |     | 462 | 100            |     | 462 | 100            |     | 462 | 100            |     | 462   | MHz  |

|                                                                                                                                                | W = 1 (Serdes used)                | 300            |     | 717 | 300            |     | 717 | 300            |     | 624 | 300            |     | 462   | MHz  |

| f <sub>HSDR</sub> Device<br>operation<br>(LVDS,<br>LVPECL,<br>HyperTransport<br>technology)                                                    | J = 10                             | 300            |     | 840 | 300            |     | 840 | 300            |     | 640 | 300            |     | 462   | Mbps |

|                                                                                                                                                | J = 8                              | 300            |     | 840 | 300            |     | 840 | 300            |     | 640 | 300            |     | 462   | Mbps |

|                                                                                                                                                | J = 7                              | 300            |     | 840 | 300            |     | 840 | 300            |     | 640 | 300            |     | 462   | Mbps |

|                                                                                                                                                | J = 4                              | 300            |     | 840 | 300            |     | 840 | 300            |     | 640 | 300            |     | 462   | Mbps |

|                                                                                                                                                | J = 2                              | 100            |     | 462 | 100            |     | 462 | 100            |     | 640 | 100            |     | 462   | Mbps |

|                                                                                                                                                | J = 1 (LVDS<br>and LVPECL<br>only) | 100            |     | 462 | 100            |     | 462 | 100            |     | 640 | 100            |     | 462   | Mbps |

Figure 5-1. Stratix Device Packaging Ordering Information