## Altera - EP1S40F1508C5 Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Active                                                     |

| Number of LABs/CLBs            | -                                                          |

| Number of Logic Elements/Cells | -                                                          |

| Total RAM Bits                 | -                                                          |

| Number of I/O                  | 822                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.425V ~ 1.575V                                            |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 1508-BBGA, FCBGA                                           |

| Supplier Device Package        | 1508-FBGA (30x30)                                          |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=ep1s40f1508c5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Chapter | Date/Version        | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4       |                     | <ul> <li>Updated Table 4–123 on page 4–85 through Table 4–126 on page 4–92.</li> <li>Updated Note 3 in Table 4–123 on page 4–85.</li> <li>Table 4–125 on page 4–88: moved to correct order in chapter, and updated table.</li> <li>Updated Table 4–126 on page 4–92.</li> <li>Updated Table 4–127 on page 4–94.</li> <li>Updated Table 4–128 on page 4–95.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         | April 2004, v3.0    | <ul> <li>Table 4–129 on page 4–96: updated table and added Note 10.</li> <li>Updated Table 4–131 and Table 4–132 on page 4–100.</li> <li>Updated Table 4–110 on page 4–74.</li> <li>Updated Table 4–123 on page 4–85.</li> <li>Updated Table 4–124 on page 4–87. through Table 4–126 on page 4–92.</li> <li>Added Note 10 to Table 4–129 on page 4–96.</li> <li>Moved Table 4–127 on page 4–94 to correct order in the chapter.</li> <li>Updated Table 4–131 on page 4–94 to correct order in the chapter.</li> <li>Updated Table 4–127 on page 4–94 to correct order in the chapter.</li> <li>Updated Table 4–131 on page 4–100 through Table 4–132 on page 4–100.</li> <li>Deleted Table 4–131 on page 4–94 to correct order in the chapter.</li> <li>Updated Table 4–177 on gage 4–94 to correct order in the chapter.</li> <li>Updated Table 4–177 on page 4–94 to correct order in the chapter.</li> <li>Updated Table 4–177 on page 4–94 to correct order in the chapter.</li> <li>Updated Table 4–177 on page 4–94 to correct order in the chapter.</li> <li>Updated Table 4–177 on page 4–94 to correct order in the chapter.</li> <li>Updated Table 4–177 on page 4–94 to correct order in the chapter.</li> <li>Updated Table 4–177 on page 4–94 to correct order in the chapter.</li> <li>Obleted t<sub>XZ</sub> and t<sub>zX</sub> from Figure 4–4.</li> <li>Waveform was added to Figure 4–6.</li> <li>The minimum and maximum duty cycle values in Note 3 of Table 4–8 were moved to a new Table 4–34.</li> <li>Added t<sub>SU_R</sub> and t<sub>SU_C</sub> rows in Table 4–38.</li> <li>Changed Table 4–55 title from "EP1S10 Column Pin Fast Regional Clock External I/O Timing Parameters" to "EP1S10 External I/O Timing on Column Pins Using Fast Regional Clock Networks."</li> <li>Changed values in Tables 4–127 to 4–132.</li> <li>Deleted -5 Speed Grade column in Tables 4–117 to 4–119 and 4–122 to 4–123.</li> <li>Fixed differential waveform in Figure 4–1.</li> <li>Added t<sub>SU</sub> and t<sub>CO_C</sub> rows and made changes to values in t<sub>PRE</sub> and t<sub>CLKHL</sub> rows in Table 4–46.</li> <li>Values changed in the t<sub>SU</sub> and t<sub>H</sub> rows in Table 4</li></ul> |

|         | November 2003, v2.2 | Updated Tables 4–127 through 4–129.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Table 1–5. Stratix FineLine BGA Package Sizes                                                      |         |         |         |           |           |  |

|----------------------------------------------------------------------------------------------------|---------|---------|---------|-----------|-----------|--|

| Dimension                                                                                          | 484 Pin | 672 Pin | 780 Pin | 1,020 Pin | 1,508 Pin |  |

| Pitch (mm)                                                                                         | 1.00    | 1.00    | 1.00    | 1.00      | 1.00      |  |

| Area (mm <sup>2</sup> )                                                                            | 529     | 729     | 841     | 1,089     | 1,600     |  |

| $\begin{array}{l} \text{Length} \times \text{ width} \\ (\text{mm} \times \text{ mm}) \end{array}$ | 23 × 23 | 27 × 27 | 29 × 29 | 33 × 33   | 40 × 40   |  |

Stratix devices are available in up to four speed grades, -5, -6, -7, and -8, with -5 being the fastest. Table 1–6 shows Stratix device speed-grade offerings.

| Table 1–6. Stratix Device Speed Grades |                |                |                            |                            |                            |                              |                              |

|----------------------------------------|----------------|----------------|----------------------------|----------------------------|----------------------------|------------------------------|------------------------------|

| Device                                 | 672-Pin<br>BGA | 956-Pin<br>BGA | 484-Pin<br>FineLine<br>BGA | 672-Pin<br>FineLine<br>BGA | 780-Pin<br>FineLine<br>BGA | 1,020-Pin<br>FineLine<br>BGA | 1,508-Pin<br>FineLine<br>BGA |

| EP1S10                                 | -6, -7         |                | -5, -6, -7                 | -6, -7                     | -5, -6, -7                 |                              |                              |

| EP1S20                                 | -6, -7         |                | -5, -6, -7                 | -6, -7                     | -5, -6, -7                 |                              |                              |

| EP1S25                                 | -6, -7         |                |                            | -6, -7, -8                 | -5, -6, -7                 | -5, -6, -7                   |                              |

| EP1S30                                 |                | -5, -6, -7     |                            |                            | -5, -6, -7, -8             | -5, -6, -7                   |                              |

| EP1S40                                 |                | -5, -6, -7     |                            |                            | -5, -6, -7, -8             | -5, -6, -7                   | -5, -6, -7                   |

| EP1S60                                 |                | -6, -7         |                            |                            |                            | -5, -6, -7                   | -6, -7                       |

| EP1S80                                 |                | -6, -7         |                            |                            |                            | -5, -6, -7                   | -5, -6, -7                   |

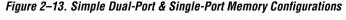

In addition to true dual-port memory, the memory blocks support simple dual-port and single-port RAM. Simple dual-port memory supports a simultaneous read and write and can either read old data before the write occurs or just read the don't care bits. Single-port memory supports non-simultaneous reads and writes, but the q [] port will output the data once it has been written to the memory (if the outputs are not registered) or after the next rising edge of the clock (if the outputs are registered). For more information, see Chapter 2, TriMatrix Embedded Memory Blocks in Stratix & Stratix GX Devices of the *Stratix Device Handbook, Volume 2*. Figure 2–13 shows these different RAM memory port configurations for TriMatrix memory.

Simple Dual-Port Memory

#### Note to Figure 2–13:

Two single-port memory blocks can be implemented in a single M4K block as long as each of the two independent block sizes is equal to or less than half of the M4K block size.

The memory blocks also enable mixed-width data ports for reading and writing to the RAM ports in dual-port RAM configuration. For example, the memory block can be written in ×1 mode at port A and read out in ×16 mode from port B.

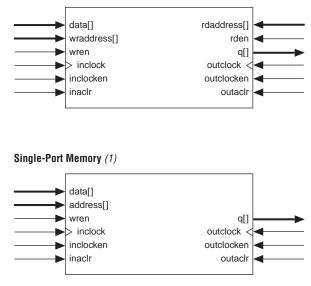

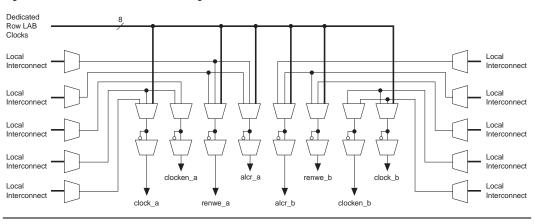

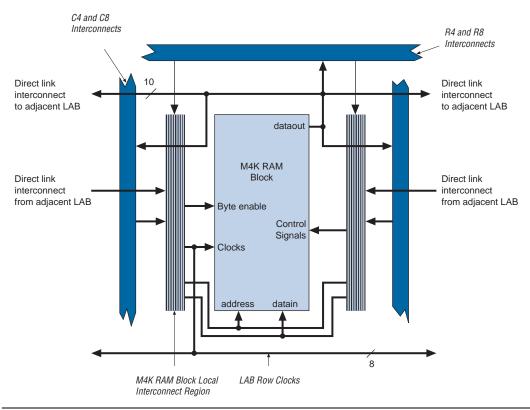

Figure 2–17. M4K RAM Block Control Signals

Figure 2–18. M4K RAM Block LAB Row Interface

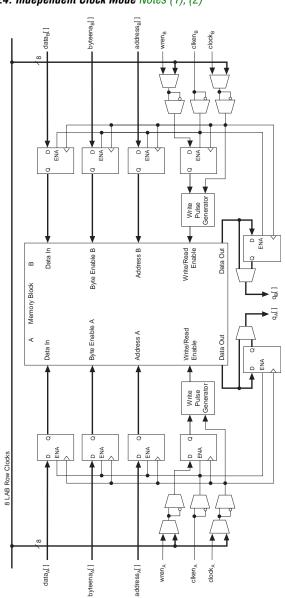

#### Notes to Figure 2–24

- (1) All registers shown have asynchronous clear ports.

- (2) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

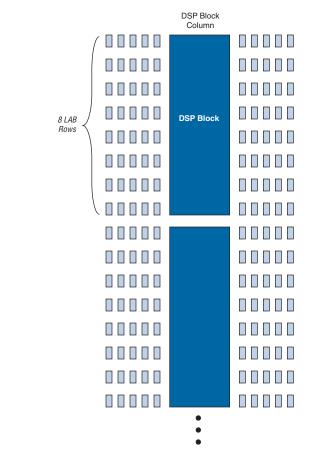

Figure 2–29. DSP Blocks Arranged in Columns

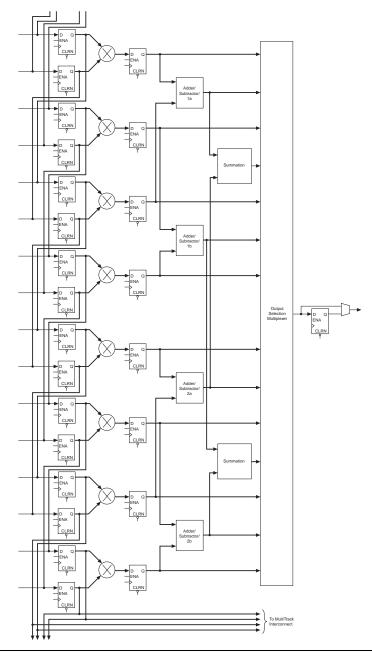

Figure 2–31. DSP Block Diagram for  $9 \times 9$ -Bit Configuration

2–56

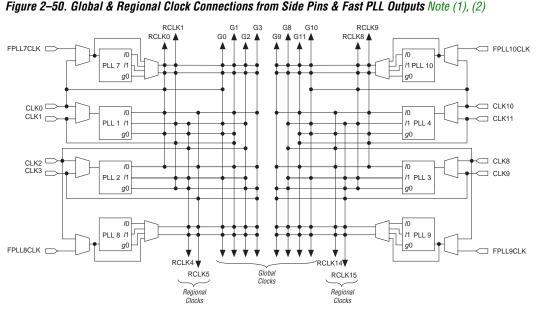

There are 16 dedicated clock pins (CLK [15..0]) to drive either the global or regional clock networks. Four clock pins drive each side of the device, as shown in Figure 2–42. Enhanced and fast PLL outputs can also drive the global and regional clock networks.

## Global Clock Network

These clocks drive throughout the entire device, feeding all device quadrants. The global clock networks can be used as clock sources for all resources within the device—IOEs, LEs, DSP blocks, and all memory blocks. These resources can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin. The global clock networks can also be driven by internal logic for internally generated global clocks and asynchronous clears, clock enables, or other control signals with large fanout. Figure 2–42 shows the 16 dedicated CLK pins driving global clock networks.

Figure 2–50 shows the global and regional clocking from the PLL outputs and the CLK pins.

#### Notes to Figure 2–50:

- (1) PLLs 1 to 4 and 7 to 10 are fast PLLs. PLLs 5, 6, 11, and 12 are enhanced PLLs.

- (2) The global or regional clocks in a fast PLL's quadrant can drive the fast PLL input. A pin or other PLL must drive the global or regional source. The source cannot be driven by internally generated logic before driving the fast PLL.

Figure 2–51 shows the global and regional clocking from enhanced PLL outputs and top CLK pins.

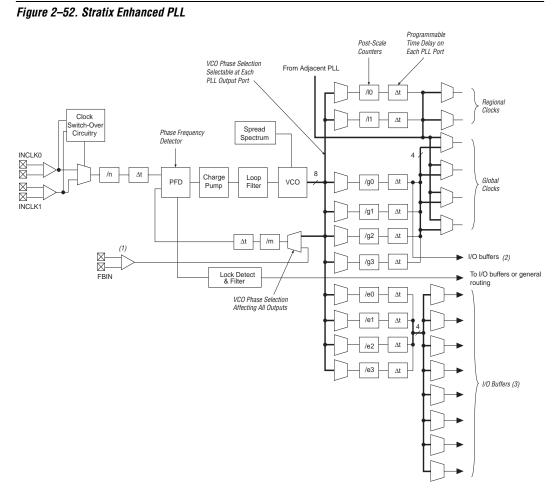

## **Enhanced PLLs**

Stratix devices contain up to four enhanced PLLs with advanced clock management features. Figure 2–52 shows a diagram of the enhanced PLL.

#### Notes to Figure 2–52:

- (1) External feedback is available in PLLs 5 and 6.

- (2) This single-ended external output is available from the *g*0 counter for PLLs 11 and 12.

- (3) These four counters and external outputs are available in PLLs 5 and 6.

- (4) This connection is only available on EP1S40 and larger Stratix devices. For example, PLLs 5 and 11 are adjacent and PLLs 6 and 12 are adjacent. The EP1S40 device in the 780-pin FineLine BGA package does not support PLLs 11 and 12.

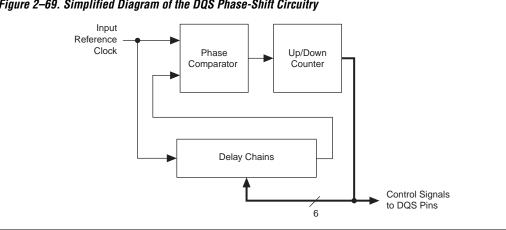

shift by the same degree amount. For example, all 10 DQS pins on the top of the device can be shifted by 90° and all 10 DQS pins on the bottom of the device can be shifted by 72°. The reference circuits require a maximum of 256 system reference clock cycles to set the correct phase on the DQS delay elements. Figure 2-69 illustrates the phase-shift reference circuit control of each DQS delay shift on the top of the device. This same circuit is duplicated on the bottom of the device.

Figure 2–69. Simplified Diagram of the DQS Phase-Shift Circuitry

See the *External Memory Interfaces* chapter in the *Stratix Device Handbook*, Volume 2 for more information on external memory interfaces.

## Programmable Drive Strength

The output buffer for each Stratix device I/O pin has a programmable drive strength control for certain I/O standards. The LVTTL and LVCMOS standard has several levels of drive strength that the user can control. SSTL-3 Class I and II, SSTL-2 Class I and II, HSTL Class I and II, and 3.3-V GTL+ support a minimum setting, the lowest drive strength that guarantees the  $I_{OH}/I_{OL}$  of the standard. Using minimum settings provides signal slew rate control to reduce system noise and signal overshoot.

| Table 2–32. I/O Support by Bank (Part 2 of 2) |                                     |                                     |                                                                 |  |  |

|-----------------------------------------------|-------------------------------------|-------------------------------------|-----------------------------------------------------------------|--|--|

| I/O Standard                                  | Top & Bottom Banks<br>(3, 4, 7 & 8) | Left & Right Banks<br>(1, 2, 5 & 6) | Enhanced PLL External<br>Clock Output Banks<br>(9, 10, 11 & 12) |  |  |

| SSTL-3 Class II                               | $\checkmark$                        | $\checkmark$                        | $\checkmark$                                                    |  |  |

| AGP (1× and 2×)                               | $\checkmark$                        |                                     | ✓                                                               |  |  |

| СТТ                                           | $\checkmark$                        | $\checkmark$                        | ✓                                                               |  |  |

Each I/O bank has its own VCCIO pins. A single device can support 1.5-, 1.8-, 2.5-, and 3.3-V interfaces; each bank can support a different standard independently. Each bank also has dedicated VREF pins to support any one of the voltage-referenced standards (such as SSTL-3) independently.

Each I/O bank can support multiple standards with the same  $V_{CCIO}$  for input and output pins. Each bank can support one voltage-referenced I/O standard. For example, when  $V_{CCIO}$  is 3.3 V, a bank can support LVTTL, LVCMOS, 3.3-V PCI, and SSTL-3 for inputs and outputs.

## **Differential On-Chip Termination**

Stratix devices provide differential on-chip termination (LVDS I/O standard) to reduce reflections and maintain signal integrity. Differential on-chip termination simplifies board design by minimizing the number of external termination resistors required. Termination can be placed inside the package, eliminating small stubs that can still lead to reflections. The internal termination is designed using transistors in the linear region of operation.

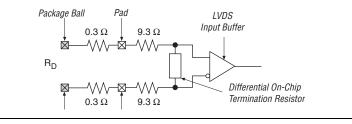

Stratix devices support internal differential termination with a nominal resistance value of 137.5  $\Omega$  for LVDS input receiver buffers. LVPECL signals require an external termination resistor. Figure 2–71 shows the device with differential termination.

However, there is additional resistance present between the device ball and the input of the receiver buffer, as shown in Figure 2–72. This resistance is because of package trace resistance (which can be calculated as the resistance from the package ball to the pad) and the parasitic layout metal routing resistance (which is shown between the pad and the intersection of the on-chip termination and input buffer).

Table 2–35 defines the specification for internal termination resistance for commercial devices.

| Table 2–35. Differential On-Chip Termination |                                            |                     |     |     |     |      |  |

|----------------------------------------------|--------------------------------------------|---------------------|-----|-----|-----|------|--|

| Symbol                                       | Resistance                                 |                     |     |     |     | Unit |  |

| Symbol                                       | Description                                | Conditions          | Min | Тур | Max | Unit |  |

| R <sub>D</sub> (2)                           | Internal differential termination for LVDS | Commercial (1), (3) | 110 | 135 | 165 | W    |  |

|                                              |                                            | Industrial (2), (3) | 100 | 135 | 170 | W    |  |

#### Notes to Table 2–35:

- (1) Data measured over minimum conditions ( $T_j = 0 \text{ C}$ ,  $V_{CCIO} +5\%$ ) and maximum conditions ( $T_j = 85 \text{ C}$ ,  $V_{CCIO} = -5\%$ ).

- (2) Data measured over minimum conditions (T<sub>j</sub> = -40 C, V<sub>CCIO</sub> +5%) and maximum conditions (T<sub>j</sub> = 100 C,  $V_{CCIO} = -5\%$ ).

- (3) LVDS data rate is supported for 840 Mbps using internal differential termination.

## MultiVolt I/O Interface

The Stratix architecture supports the MultiVolt I/O interface feature, which allows Stratix devices in all packages to interface with systems of different supply voltages.

The Stratix VCCINT pins must always be connected to a 1.5-V power supply. With a 1.5-V V<sub>CCINT</sub> level, input pins are 1.5-V, 1.8-V, 2.5-V, and 3.3-V tolerant. The VCCIO pins can be connected to either a 1.5-V, 1.8-V, 2.5-V, or 3.3-V power supply, depending on the output requirements.

| Table 2–41. EP1S80 Differential Channels (Part 2 of 2) Note (1) |                    |                |                    |            |            |            |            |            |            |            |            |

|-----------------------------------------------------------------|--------------------|----------------|--------------------|------------|------------|------------|------------|------------|------------|------------|------------|

|                                                                 | Transmitter/       | Total          | Maximum            | C          | enter F    | ast PLL    | .s         | Corr       | ier Fas    | t PLLs (2  | 2), (3)    |

| Package                                                         | Receiver           | Channels       | Speed<br>(Mbps)    | PLL1       | PLL2       | PLL3       | PLL4       | PLL7       | PLL8       | PLL9       | PLL10      |

| 1,508-pin<br>FineLine                                           | Transmitter<br>(4) | 80 (72)<br>(7) | 840                | 10<br>(10) | 10<br>(10) | 10<br>(10) | 10<br>(10) | 20<br>(8)  | 20<br>(8)  | 20 (8)     | 20 (8)     |

| BGA                                                             |                    |                | 840 <i>(5),(8)</i> | 20<br>(20) | 20<br>(20) | 20<br>(20) | 20<br>(20) | 20<br>(8)  | 20<br>(8)  | 20 (8)     | 20 (8)     |

|                                                                 | Receiver           | 80 (56)<br>(7) | 840                | 20         | 20         | 20         | 20         | 10<br>(14) | 10<br>(14) | 10<br>(14) | 10<br>(14) |

|                                                                 |                    |                | 840 <i>(5),(8)</i> | 40         | 40         | 40         | 40         | 10<br>(14) | 10<br>(14) | 10<br>(14) | 10<br>(14) |

#### Notes to Tables 2–38 through 2–41:

- (1) The first row for each transmitter or receiver reports the number of channels driven directly by the PLL. The second row below it shows the maximum channels a PLL can drive if cross bank channels are used from the adjacent center PLL. For example, in the 780-pin FineLine BGA EP1S30 device, PLL 1 can drive a maximum of 18 transmitter channels at 840 Mbps or a maximum of 35 transmitter channels at 840 Mbps. The Quartus II software may also merge transmitter and receiver PLLs when a receiver is driving a transmitter. In this case, one fast PLL can drive both the maximum numbers of receiver and transmitter channels.

- (2) Some of the channels accessible by the center fast PLL and the channels accessible by the corner fast PLL overlap. Therefore, the total number of channels is not the addition of the number of channels accessible by PLLs 1, 2, 3, and 4 with the number of channels accessible by PLLs 7, 8, 9, and 10. For more information on which channels overlap, see the Stratix device pin-outs at **www.altera.com**.

- (3) The corner fast PLLs in this device support a data rate of 840 Mbps for channels labeled "high" speed in the device pin-outs at www.altera.com.

- (4) The numbers of channels listed include the transmitter clock output (tx\_outclock) channel. An extra data channel can be used if a DDR clock is needed.

- (5) These channels span across two I/O banks per side of the device. When a center PLL clocks channels in the opposite bank on the same side of the device it is called cross-bank PLL support. Both center PLLs can clock cross-bank channels simultaneously if say PLL\_1 is clocking all receiver channels and PLL\_2 is clocking all transmitter channels. You cannot have two adjacent PLLs simultaneously clocking cross-bank receiver channels or two adjacent PLLs simultaneously clocking transmitter channels. Cross-bank allows for all receiver channels on one side of the device to be clocked on one clock while all transmitter channels on the device are clocked on the other center PLL. Crossbank PLLs are supported at full-speed, 840 Mbps. For wire-bond devices, the full-speed is 624 Mbps.

- (6) PLLs 7, 8, 9, and 10 are not available in this device.

- (7) The number in parentheses is the number of slow-speed channels, guaranteed to operate at up to 462 Mbps. These channels are independent of the high-speed differential channels. For the location of these channels, see the device pin-outs at www.altera.com.

- (8) See the Stratix device pin-outs at **www.altera.com**. Channels marked "high" speed are 840 MBps and "low" speed channels are 462 MBps.

The high-speed differential I/O circuitry supports the following high speed I/O interconnect standards and applications:

- UTOPIA IV

- SPI-4 Phase 2 (POS-PHY Level 4)

- SFI-4

- 10G Ethernet XSBI

The transmitter external clock output is transmitted on a data channel. The txclk pin for each bank is located in between data transmitter pins. For ×1 clocks (e.g., 622 Mbps, 622 MHz), the high-speed PLL clock bypasses the SERDES to drive the output pins. For half-rate clocks (e.g., 622 Mbps, 311 MHz) or any other even-numbered factor such as 1/4, 1/7, 1/8, or 1/10, the SERDES automatically generates the clock in the Quartus II software.

For systems that require more than four or eight high-speed differential I/O clock domains, a SERDES bypass implementation is possible using IOEs.

## **Byte Alignment**

For high-speed source synchronous interfaces such as POS-PHY 4, XSBI, RapidIO, and HyperTransport technology, the source synchronous clock rate is not a byte- or SERDES-rate multiple of the data rate. Byte alignment is necessary for these protocols since the source synchronous clock does not provide a byte or word boundary since the clock is one half the data rate, not one eighth. The Stratix device's high-speed differential I/O circuitry provides dedicated data realignment circuitry for usercontrolled byte boundary shifting. This simplifies designs while saving LE resources. An input signal to each fast PLL can stall deserializer parallel data outputs by one bit period. You can use an LE-based state machine to signal the shift of receiver byte boundaries until a specified pattern is detected to indicate byte alignment.

## Power Sequencing & Hot Socketing

Because Stratix devices can be used in a mixed-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. Therefore, the VCCIO and VCCINT power supplies may be powered in any order.

Although you can power up or down the VCCIO and VCCINT power supplies in any sequence, you should not power down any I/O banks that contain configuration pins while leaving other I/O banks powered on. For power up and power down, all supplies (VCCINT and all VCCIO power planes) must be powered up and down within 100 ms of each other. This prevents I/O pins from driving out.

Signals can be driven into Stratix devices before and during power up without damaging the device. In addition, Stratix devices do not drive out during power up. Once operating conditions are reached and the device is configured, Stratix devices operate as specified by the user. For more information, see *Hot Socketing* in the *Selectable I/O Standards in Stratix & Stratix GX Devices* chapter in the *Stratix Device Handbook, Volume 2.*

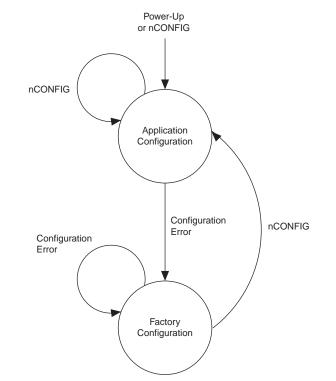

### Local Update Mode

Local update mode is a simplified version of the remote update. This feature is intended for simple systems that need to load a single application configuration immediately upon power up without loading the factory configuration first. Local update designs have only one application configuration to load, so it does not require a factory configuration to determine which application configuration to use. Figure 3–4 shows the transition diagram for local update mode.

## Stratix Automated Single Event Upset (SEU) Detection

Stratix devices offer on-chip circuitry for automated checking of single event upset (SEU) detection. FPGA devices that operate at high elevations or in close proximity to earth's North or South Pole require periodic checks to ensure continued data integrity. The error detection cyclic redundancy check (CRC) feature controlled by the **Device & Pin Options** dialog box in the Quartus II software uses a 32-bit CRC circuit to ensure data reliability and is one of the best options for mitigating SEU.

# 4. DC & Switching Characteristics

### S51004-3.4

# Operating Conditions

Stratix<sup>®</sup> devices are offered in both commercial and industrial grades. Industrial devices are offered in -6 and -7 speed grades and commercial devices are offered in -5 (fastest), -6, -7, and -8 speed grades. This section specifies the operation conditions for operating junction temperature,  $V_{CCINT}$  and  $V_{CCIO}$  voltage levels, and input voltage requirements. The voltage specifications in this section are specified at the pins of the device (and not the power supply). If the device operates outside these ranges, then all DC and AC specifications are not guaranteed. Furthermore, the reliability of the device may be affected. The timing parameters in this chapter apply to both commercial and industrial temperature ranges unless otherwise stated.

Tables 4–1 through 4–8 provide information on absolute maximum ratings.

| Table 4–1. Stratix Device Absolute Maximum Ratings Notes (1), (2) |                            |                         |         |         |      |  |  |

|-------------------------------------------------------------------|----------------------------|-------------------------|---------|---------|------|--|--|

| Symbol                                                            | Parameter                  | Conditions              | Minimum | Maximum | Unit |  |  |

| V <sub>CCINT</sub>                                                | Supply voltage             | With respect to ground  | -0.5    | 2.4     | V    |  |  |

| V <sub>CCIO</sub>                                                 | -                          |                         | -0.5    | 4.6     | V    |  |  |

| VI                                                                | DC input voltage (3)       |                         | -0.5    | 4.6     | V    |  |  |

| I <sub>OUT</sub>                                                  | DC output current, per pin |                         | -25     | 40      | mA   |  |  |

| T <sub>STG</sub>                                                  | Storage temperature        | No bias                 | -65     | 150     | °C   |  |  |

| TJ                                                                | Junction temperature       | BGA packages under bias |         | 135     | °C   |  |  |

| Table 4–2. Stratix Device Recommended Operating Conditions (Part 1 of 2) |                                                     |            |         |         |      |  |

|--------------------------------------------------------------------------|-----------------------------------------------------|------------|---------|---------|------|--|

| Symbol                                                                   | Parameter                                           | Conditions | Minimum | Maximum | Unit |  |

| V <sub>CCINT</sub>                                                       | Supply voltage for internal logic and input buffers | (4)        | 1.425   | 1.575   | V    |  |

Г

| Symbol                   | Parameter                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>M512RC</sub>      | Synchronous read cycle time                                                                                                                                                                                                                                                                                                                                              |

| t <sub>M512WC</sub>      | Synchronous write cycle time                                                                                                                                                                                                                                                                                                                                             |

| t <sub>M512WERESU</sub>  | Write or read enable setup time before clock                                                                                                                                                                                                                                                                                                                             |

| t <sub>M512WEREH</sub>   | Write or read enable hold time after clock                                                                                                                                                                                                                                                                                                                               |

| t <sub>M512CLKENSU</sub> | Clock enable setup time before clock                                                                                                                                                                                                                                                                                                                                     |

| t <sub>M512CLKENH</sub>  | Clock enable hold time after clock                                                                                                                                                                                                                                                                                                                                       |

| t <sub>M512DATASU</sub>  | Data setup time before clock                                                                                                                                                                                                                                                                                                                                             |

| t <sub>M512DATAH</sub>   | Data hold time after clock                                                                                                                                                                                                                                                                                                                                               |

| t <sub>M512WADDRSU</sub> | Write address setup time before clock                                                                                                                                                                                                                                                                                                                                    |

| t <sub>M512WADDRH</sub>  | Write address hold time after clock                                                                                                                                                                                                                                                                                                                                      |

| t <sub>M512RADDRSU</sub> | Read address setup time before clock                                                                                                                                                                                                                                                                                                                                     |

| t <sub>M512RADDRH</sub>  | Read address hold time after clock                                                                                                                                                                                                                                                                                                                                       |

| t <sub>M512DATACO1</sub> | Clock-to-output delay when using output registers                                                                                                                                                                                                                                                                                                                        |

| t <sub>M512DATACO2</sub> | Clock-to-output delay without output registers                                                                                                                                                                                                                                                                                                                           |

| t <sub>M512CLKHL</sub>   | Register minimum clock high or low time. This is a limit on<br>the min time for the clock on the registers in these blocks.<br>The actual performance is dependent upon the internal<br>point-to-point delays in the blocks and may give slower<br>performance as shown in Table 4–36 on page 4–20 and as<br>reported by the timing analyzer in the Quartus II software. |

| t <sub>M512CLB</sub>     | Minimum clear pulse width                                                                                                                                                                                                                                                                                                                                                |

Table 4–41. M4K Block Internal Timing Microparameter Descriptions (Part 1 of 2)

| Symbol                  | Parameter                                    |

|-------------------------|----------------------------------------------|

| t <sub>M4KRC</sub>      | Synchronous read cycle time                  |

| t <sub>M4KWC</sub>      | Synchronous write cycle time                 |

| t <sub>M4KWERESU</sub>  | Write or read enable setup time before clock |

| t <sub>M4KWEREH</sub>   | Write or read enable hold time after clock   |

| t <sub>M4KCLKENSU</sub> | Clock enable setup time before clock         |

| t <sub>M4KCLKENH</sub>  | Clock enable hold time after clock           |

| t <sub>M4KBESU</sub>    | Byte enable setup time before clock          |

| t <sub>M4KBEH</sub>     | Byte enable hold time after clock            |

| t <sub>M4KDATAASU</sub> | A port data setup time before clock          |

| Table 4–104. Stratix I/O Standard Row Pin Input Delay Adders |                |      |                |      |                |      |                |      |      |

|--------------------------------------------------------------|----------------|------|----------------|------|----------------|------|----------------|------|------|

| Parameter                                                    | -5 Speed Grade |      | -6 Speed Grade |      | -7 Speed Grade |      | -8 Speed Grade |      | 11   |

|                                                              | Min            | Max  | Min            | Max  | Min            | Max  | Min            | Max  | Unit |

| LVCMOS                                                       |                | 0    |                | 0    |                | 0    |                | 0    | ps   |

| 3.3-V LVTTL                                                  |                | 0    |                | 0    |                | 0    |                | 0    | ps   |

| 2.5-V LVTTL                                                  |                | 21   |                | 22   |                | 25   |                | 29   | ps   |

| 1.8-V LVTTL                                                  |                | 181  |                | 190  |                | 218  |                | 257  | ps   |

| 1.5-V LVTTL                                                  |                | 300  |                | 315  |                | 362  |                | 426  | ps   |

| GTL+                                                         |                | -152 |                | -160 |                | -184 |                | -216 | ps   |

| CTT                                                          |                | -168 |                | -177 |                | -203 |                | -239 | ps   |

| SSTL-3 Class I                                               |                | -193 |                | -203 |                | -234 |                | -275 | ps   |

| SSTL-3 Class II                                              |                | -193 |                | -203 |                | -234 |                | -275 | ps   |

| SSTL-2 Class I                                               |                | -262 |                | -276 |                | -317 |                | -373 | ps   |

| SSTL-2 Class II                                              |                | -262 |                | -276 |                | -317 |                | -373 | ps   |

| SSTL-18 Class I                                              |                | -105 |                | -111 |                | -127 |                | -150 | ps   |

| SSTL-18 Class II                                             |                | 0    |                | 0    |                | 0    |                | 0    | ps   |

| 1.5-V HSTL Class I                                           |                | -151 |                | -159 |                | -183 |                | -215 | ps   |

| 1.8-V HSTL Class I                                           |                | -126 |                | -133 |                | -153 |                | -179 | ps   |

| LVDS                                                         |                | -149 |                | -157 |                | -180 |                | -212 | ps   |

| LVPECL                                                       |                | -149 |                | -157 |                | -180 |                | -212 | ps   |

| 3.3-V PCML                                                   |                | -65  |                | -69  |                | -79  |                | -93  | ps   |

| HyperTransport                                               |                | 77   |                | -81  |                | -93  |                | -110 | ps   |

Tables 4–131 through 4–133 describe the Stratix device fast PLL specifications.

| Table 4–131. Fast PLL Specifications for -5 & -6 Speed Grade Devices |                                                                                             |       |       |         |  |  |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------|-------|---------|--|--|

| Symbol                                                               | Parameter                                                                                   | Min   | Max   | Unit    |  |  |

| f <sub>IN</sub>                                                      | CLKIN frequency (1), (2), (3)                                                               | 10    | 717   | MHz     |  |  |

| f <sub>INPFD</sub>                                                   | Input frequency to PFD                                                                      | 10    | 500   | MHz     |  |  |

| f <sub>OUT</sub>                                                     | Output frequency for internal global or regional clock (3)                                  | 9.375 | 420   | MHz     |  |  |

| f <sub>OUT_DIFFIO</sub>                                              | Output frequency for external clock<br>driven out on a differential I/O data<br>channel (2) | (5)   | (5)   |         |  |  |

| f <sub>VCO</sub>                                                     | VCO operating frequency                                                                     | 300   | 1,000 | MHz     |  |  |

| t <sub>INDUTY</sub>                                                  | CLKIN duty cycle                                                                            | 40    | 60    | %       |  |  |

| t <sub>INJITTER</sub>                                                | Period jitter for CLKIN pin                                                                 |       | ±200  | ps      |  |  |

| t <sub>DUTY</sub>                                                    | Duty cycle for DFFIO 1× CLKOUT pin (6)                                                      | 45    | 55    | %       |  |  |

| t <sub>JITTER</sub>                                                  | Period jitter for DIFFIO clock out (6)                                                      |       | (5)   | ps      |  |  |

| t <sub>LOCK</sub>                                                    | Time required for PLL to acquire lock                                                       | 10    | 100   | μs      |  |  |

| m                                                                    | Multiplication factors for <i>m</i> counter (6)                                             | 1     | 32    | Integer |  |  |

| <i>I</i> 0, <i>I</i> 1, <i>g</i> 0                                   | Multiplication factors for I0, I1, and g0 counter (7), (8)                                  | 1     | 32    | Integer |  |  |

| t <sub>ARESET</sub>                                                  | Minimum pulse width on areset signal                                                        | 10    |       | ns      |  |  |

| Table 4–132. Fast PLL Specifications for -7 Speed Grades (Part 1 of 2) |                                                                                         |       |      |      |  |  |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|------|------|--|--|

| Symbol                                                                 | Parameter                                                                               | Min   | Max  | Unit |  |  |

| f <sub>IN</sub>                                                        | CLKIN frequency (1), (3)                                                                | 10    | 640  | MHz  |  |  |

| f <sub>INPFD</sub>                                                     | Input frequency to PFD                                                                  | 10    | 500  | MHz  |  |  |

| f <sub>OUT</sub>                                                       | Output frequency for internal global or regional clock (4)                              | 9.375 | 420  | MHz  |  |  |

| f <sub>OUT_DIFFIO</sub>                                                | Output frequency for external clock<br>driven out on a differential I/O data<br>channel | (5)   | (5)  | MHz  |  |  |

| f <sub>VCO</sub>                                                       | VCO operating frequency                                                                 | 300   | 700  | MHz  |  |  |

| t <sub>INDUTY</sub>                                                    | CLKIN duty cycle                                                                        | 40    | 60   | %    |  |  |

| t <sub>INJITTER</sub>                                                  | Period jitter for CLKIN pin                                                             |       | ±200 | ps   |  |  |

| t <sub>DUTY</sub>                                                      | Duty cycle for DFFIO 1× CLKOUT pin (6)                                                  | 45    | 55   | %    |  |  |