Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Obsolete                                                  |

| Number of LABs/CLBs            | 4125                                                      |

| Number of Logic Elements/Cells | 41250                                                     |

| Total RAM Bits                 | 3423744                                                   |

| Number of I/O                  | 822                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.425V ~ 1.575V                                           |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 1508-BBGA, FCBGA                                          |

| Supplier Device Package        | 1508-FBGA, FC (40x40)                                     |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s40f1508c6n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

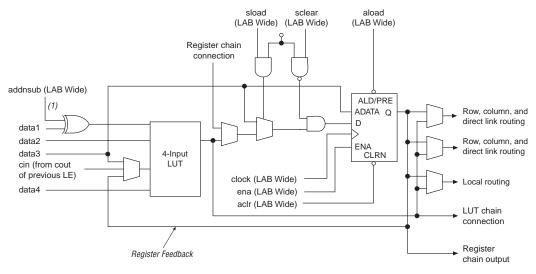

asynchronous preset load, synchronous clear, synchronous load, and clock enable control for the register. These LAB-wide signals are available in all LE modes. The addnsub control signal is allowed in arithmetic mode.

The Quartus II software, in conjunction with parameterized functions such as library of parameterized modules (LPM) functions, automatically chooses the appropriate mode for common functions such as counters, adders, subtractors, and arithmetic functions. If required, you can also create special-purpose functions that specify which LE operating mode to use for optimal performance.

## Normal Mode

The normal mode is suitable for general logic applications and combinatorial functions. In normal mode, four data inputs from the LAB local interconnect are inputs to a four-input LUT (see Figure 2–6). The Quartus II Compiler automatically selects the carry-in or the data3 signal as one of the inputs to the LUT. Each LE can use LUT chain connections to drive its combinatorial output directly to the next LE in the LAB. Asynchronous load data for the register comes from the data3 input of the LE. LEs in normal mode support packed registers.

Figure 2-6. LE in Normal Mode

Note to Figure 2-6:

(1) This signal is only allowed in normal mode if the LE is at the end of an adder/subtractor chain.

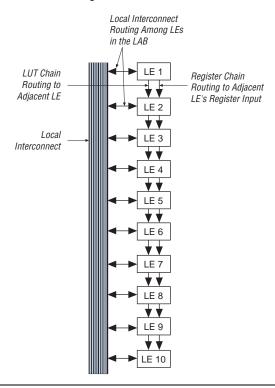

Figure 2-10. LUT Chain & Register Chain Interconnects

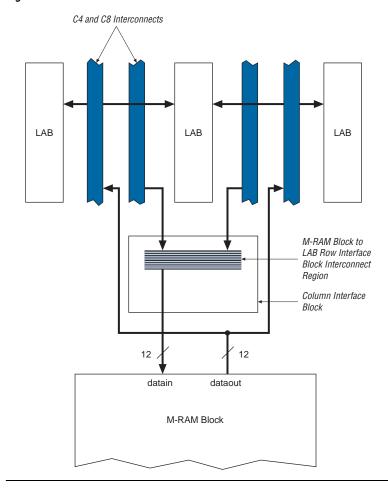

The C4 interconnects span four LABs, M512, or M4K blocks up or down from a source LAB. Every LAB has its own set of C4 interconnects to drive either up or down. Figure 2–11 shows the C4 interconnect connections from an LAB in a column. The C4 interconnects can drive and be driven by all types of architecture blocks, including DSP blocks, TriMatrix memory blocks, and vertical IOEs. For LAB interconnection, a primary LAB or its LAB neighbor can drive a given C4 interconnect. C4 interconnects can drive each other to extend their range as well as drive row interconnects for column-to-column connections.

| Table 2–3. TriMatrix Memory Features (Part 2 of 2) |                                                                         |                                                                                                  |                                                                                                                  |  |  |  |  |  |

|----------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Memory Feature                                     | M512 RAM Block<br>(32 × 18 Bits)                                        | M4K RAM Block<br>(128 × 36 Bits)                                                                 | M-RAM Block<br>(4K × 144 Bits)                                                                                   |  |  |  |  |  |

| Configurations                                     | 512 × 1<br>256 × 2<br>128 × 4<br>64 × 8<br>64 × 9<br>32 × 16<br>32 × 18 | 4K × 1<br>2K × 2<br>1K × 4<br>512 × 8<br>512 × 9<br>256 × 16<br>256 × 18<br>128 × 32<br>128 × 36 | 64K × 8<br>64K × 9<br>32K × 16<br>32K × 18<br>16K × 32<br>16K × 36<br>8K × 64<br>8K × 72<br>4K × 128<br>4K × 144 |  |  |  |  |  |

*Notes to Table 2–3:*

- (1) See Table 4–36 for maximum performance information.

- (2) The M-RAM block does not support memory initializations. However, the M-RAM block can emulate a ROM function using a dual-port RAM bock. The Stratix device must write to the dual-port memory once and then disable the write-enable ports afterwards.

Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

# **Memory Modes**

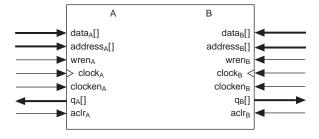

TriMatrix memory blocks include input registers that synchronize writes and output registers to pipeline designs and improve system performance. M4K and M-RAM memory blocks offer a true dual-port mode to support any combination of two-port operations: two reads, two writes, or one read and one write at two different clock frequencies. Figure 2–12 shows true dual-port memory.

Figure 2-12. True Dual-Port Memory Configuration

The memory address depths and output widths can be configured as  $4,096 \times 1, 2,048 \times 2, 1,024 \times 4,512 \times 8$  (or  $512 \times 9$  bits),  $256 \times 16$  (or  $256 \times 18$  bits), and  $128 \times 32$  (or  $128 \times 36$  bits). The  $128 \times 32$ - or 36-bit configuration is not available in the true dual-port mode. Mixed-width configurations are also possible, allowing different read and write widths. Tables 2–5 and 2–6 summarize the possible M4K RAM block configurations.

| Table 2-5. M4 | Table 2–5. M4K RAM Block Configurations (Simple Dual-Port) |            |          |          |          |          |          |             |          |

|---------------|------------------------------------------------------------|------------|----------|----------|----------|----------|----------|-------------|----------|

| Dood Dood     |                                                            | Write Port |          |          |          |          |          |             |          |

| Read Port     | 4K × 1                                                     | 2K × 2     | 1K × 4   | 512 × 8  | 256 × 16 | 128 × 32 | 512 × 9  | 256 × 18    | 128 × 36 |

| 4K × 1        | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |

| 2K × 2        | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | ~        | <b>✓</b> | <b>✓</b> |          |             |          |

| 1K × 4        | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | ~        | <b>✓</b> | <b>✓</b> |          |             |          |

| 512 × 8       | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | ~        | <b>✓</b> | <b>✓</b> |          |             |          |

| 256 × 16      | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | ~        | <b>✓</b> | <b>✓</b> |          |             |          |

| 128 × 32      | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |

| 512 × 9       |                                                            |            |          |          |          |          | <b>✓</b> | <b>✓</b>    | <b>✓</b> |

| 256 × 18      |                                                            |            |          |          |          |          | <b>✓</b> | <b>✓</b>    | <b>✓</b> |

| 128 × 36      |                                                            |            |          |          |          |          | <b>✓</b> | <b>&gt;</b> | <b>✓</b> |

| Table 2–6. M4K RAM | able 2–6. M4K RAM Block Configurations (True Dual-Port) |          |          |          |          |          |          |  |  |  |  |

|--------------------|---------------------------------------------------------|----------|----------|----------|----------|----------|----------|--|--|--|--|

| Don't A            |                                                         | Port B   |          |          |          |          |          |  |  |  |  |

| Port A             | 4K × 1                                                  | 2K × 2   | 1K × 4   | 512 × 8  | 256 × 16 | 512 × 9  | 256 × 18 |  |  |  |  |

| 4K × 1             | <b>✓</b>                                                | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |  |  |  |  |

| 2K × 2             | ✓                                                       | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |  |  |  |

| 1K × 4             | ✓                                                       | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |  |  |  |

| 512 × 8            | ✓                                                       | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |  |  |  |

| 256 × 16           | <b>✓</b>                                                | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |  |  |  |

| 512 × 9            |                                                         |          |          |          |          | <b>✓</b> | <b>✓</b> |  |  |  |  |

| 256 × 18           |                                                         |          |          |          |          | <b>✓</b> | <b>✓</b> |  |  |  |  |

When the M4K RAM block is configured as a shift register block, you can create a shift register up to 4,608 bits ( $w \times m \times n$ ).

Figure 2–23. M-RAM Column Unit Interface to Interconnect

single DSP block can implement two sums or differences from two  $18 \times 18$ -bit multipliers each or four sums or differences from two  $9 \times 9$ -bit multipliers each.

You can use the two-multipliers adder mode for complex multiplications, which are written as:

$$(a+jb)\times(c+jd) = [(a\times c) - (b\times d)] + j\times[(a\times d) + (b\times c)]$$

The two-multipliers adder mode allows a single DSP block to calculate the real part  $[(a \times c) - (b \times d)]$  using one subtractor and the imaginary part  $[(a \times d) + (b \times c)]$  using one adder, for data widths up to 18 bits. Two complex multiplications are possible for data widths up to 9 bits using four adder/subtractor/accumulator blocks. Figure 2–38 shows an 18-bit two-multipliers adder.

Figure 2–38. Two-Multipliers Adder Mode Implementing Complex Multiply

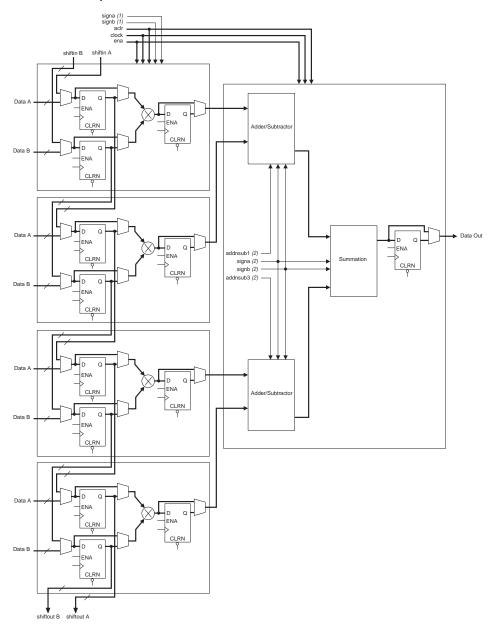

# Four-Multipliers Adder Mode

In the four-multipliers adder mode, the DSP block adds the results of two first -stage adder/subtractor blocks. One sum of four  $18 \times 18$ -bit multipliers or two different sums of two sets of four  $9 \times 9$ -bit multipliers can be implemented in a single DSP block. The product width for each multiplier must be the same size. The four-multipliers adder mode is useful for FIR filter applications. Figure 2–39 shows the four multipliers adder mode.

Figure 2-39. Four-Multipliers Adder Mode

Notes to Figure 2-39:

- (1) These signals are not registered or registered once to match the data path pipeline.

- (2) These signals are not registered, registered once, or registered twice for latency to match the data path pipeline.

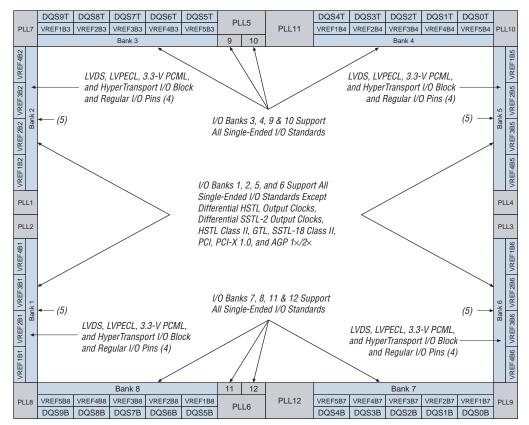

Any of the four external output counters can drive the single-ended or differential clock outputs for PLLs 5 and 6. This means one counter or frequency can drive all output pins available from PLL 5 or PLL 6. Each pair of output pins (four pins total) has dedicated VCC and GND pins to reduce the output clock's overall jitter by providing improved isolation from switching I/O pins.

For PLLs 5 and 6, each pin of a single-ended output pair can either be in phase or 180° out of phase. The clock output pin pairs support the same I/O standards as standard output pins (in the top and bottom banks) as well as LVDS, LVPECL, 3.3-V PCML, HyperTransport technology, differential HSTL, and differential SSTL. Table 2–20 shows which I/O standards the enhanced PLL clock pins support. When in single-ended or differential mode, the two outputs operate off the same power supply. Both outputs use the same standards in single-ended mode to maintain performance. You can also use the external clock output pins as user output pins if external enhanced PLL clocking is not needed.

| Table 2–20. I/O Standards Supported for Enhanced PLL Pins (Part 1 of 2) |          |          |           |        |  |  |  |  |

|-------------------------------------------------------------------------|----------|----------|-----------|--------|--|--|--|--|

| L/O Ctondovd                                                            |          | Input    |           |        |  |  |  |  |

| I/O Standard                                                            | INCLK    | FBIN     | PLLENABLE | EXTCLK |  |  |  |  |

| LVTTL                                                                   | <b>✓</b> | <b>✓</b> | <b>✓</b>  | ✓      |  |  |  |  |

| LVCMOS                                                                  | <b>✓</b> | <b>✓</b> | ✓         | ✓      |  |  |  |  |

| 2.5 V                                                                   | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |

| 1.8 V                                                                   | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |

| 1.5 V                                                                   | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |

| 3.3-V PCI                                                               | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |

| 3.3-V PCI-X 1.0                                                         | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |

| LVPECL                                                                  | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |

| 3.3-V PCML                                                              | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |

| LVDS                                                                    | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |

| HyperTransport technology                                               | <b>✓</b> | <b>✓</b> |           | ✓      |  |  |  |  |

| Differential HSTL                                                       | <b>✓</b> |          |           | ✓      |  |  |  |  |

| Differential SSTL                                                       |          |          |           | ✓      |  |  |  |  |

| 3.3-V GTL                                                               | <b>✓</b> | ✓        |           | ✓      |  |  |  |  |

| 3.3-V GTL+                                                              | <b>✓</b> | ✓        |           | ✓      |  |  |  |  |

| 1.5-V HSTL Class I                                                      | <b>✓</b> | ✓        |           | ✓      |  |  |  |  |

**Figure 2–70. Stratix I/O Banks** Notes (1), (2), (3)

### *Notes to Figure 2–70:*

- (1) Figure 2–70 is a top view of the silicon die. This will correspond to a top-down view for non-flip-chip packages, but will be a reverse view for flip-chip packages.

- (2) Figure 2–70 is a graphic representation only. See the device pin-outs on the web (www.altera.com) and the Quartus II software for exact locations.

- (3) Banks 9 through 12 are enhanced PLL external clock output banks.

- (4) If the high-speed differential I/O pins are not used for high-speed differential signaling, they can support all of the I/O standards except HSTL Class I and II, GTL, SSTL-18 Class II, PCI, PCI-X 1.0, and AGP 1×/2×.

- (5) For guidelines for placing single-ended I/O pads next to differential I/O pads, see the Selectable I/O Standards in Stratix and Stratix GX Devices chapter in the Stratix Device Handbook, Volume 2.

Table 2–32 shows I/O standard support for each I/O bank.

| I/O Standard                      | Top & Bottom Banks<br>(3, 4, 7 & 8) | Left & Right Banks<br>(1, 2, 5 & 6) | Enhanced PLL External<br>Clock Output Banks<br>(9, 10, 11 & 12) |

|-----------------------------------|-------------------------------------|-------------------------------------|-----------------------------------------------------------------|

| LVTTL                             | <b>✓</b>                            | <b>✓</b>                            | <b>✓</b>                                                        |

| LVCMOS                            | ✓                                   | <b>✓</b>                            | <b>✓</b>                                                        |

| 2.5 V                             | ✓                                   | ✓                                   | ✓                                                               |

| 1.8 V                             | ✓                                   | ✓                                   | ✓                                                               |

| 1.5 V                             | ✓                                   | <b>✓</b>                            | <b>✓</b>                                                        |

| 3.3-V PCI                         | <b>✓</b>                            |                                     | <b>✓</b>                                                        |

| 3.3-V PCI-X 1.0                   | <b>✓</b>                            |                                     | <b>✓</b>                                                        |

| LVPECL                            |                                     | <b>✓</b>                            | <b>✓</b>                                                        |

| 3.3-V PCML                        |                                     | <b>✓</b>                            | <b>✓</b>                                                        |

| LVDS                              |                                     | <b>✓</b>                            | <b>✓</b>                                                        |

| HyperTransport technology         |                                     | <b>✓</b>                            | <b>✓</b>                                                        |

| Differential HSTL (clock inputs)  | <b>✓</b>                            | <b>✓</b>                            |                                                                 |

| Differential HSTL (clock outputs) |                                     |                                     | ✓                                                               |

| Differential SSTL (clock outputs) |                                     |                                     | ✓                                                               |

| 3.3-V GTL                         | ✓                                   |                                     | ✓                                                               |

| 3.3-V GTL+                        | ✓                                   | ✓                                   | <b>✓</b>                                                        |

| 1.5-V HSTL Class I                | ✓                                   | ✓                                   | ✓                                                               |

| 1.5-V HSTL Class II               | ✓                                   |                                     | ✓                                                               |

| 1.8-V HSTL Class I                | ✓                                   | ✓                                   | <b>✓</b>                                                        |

| 1.8-V HSTL Class II               | ✓                                   |                                     | ✓                                                               |

| SSTL-18 Class I                   | ✓                                   | ✓                                   | ✓                                                               |

| SSTL-18 Class II                  | ✓                                   |                                     | ✓                                                               |

| SSTL-2 Class I                    | ✓                                   | <b>✓</b>                            | <b>✓</b>                                                        |

| SSTL-2 Class II                   | ✓                                   | ✓                                   | <b>✓</b>                                                        |

| SSTL-3 Class I                    | <b>✓</b>                            | <b>✓</b>                            | <b>✓</b>                                                        |

Figure 4–2. Transmitter Output Waveforms for Differential I/O Standards

# Single-Ended Waveform Positive Channel (p) = $V_{OH}$ $V_{CM}$ Negative Channel (n) = $V_{OL}$ Ground

# Differential Waveform $V_{OD} = 0 \text{ V}$ $V_{OD} = 0 \text{ V}$

Tables 4–10 through 4–33 recommend operating conditions, DC operating conditions, and capacitance for 1.5-V Stratix devices.

| Table 4–10. 3.3-V LVDS I/O Specifications (Part 1 of 2) |                                                 |                                                                                 |         |         |         |      |  |  |  |

|---------------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------|---------|---------|---------|------|--|--|--|

| Symbol                                                  | Parameter                                       | Conditions                                                                      | Minimum | Typical | Maximum | Unit |  |  |  |

| V <sub>CCIO</sub>                                       | I/O supply voltage                              |                                                                                 | 3.135   | 3.3     | 3.465   | V    |  |  |  |

| V <sub>ID</sub> (6)                                     | Input differential voltage swing (single-ended) | $0.1 \text{ V} \leq \text{V}_{\text{CM}} < 1.1 \text{ V}$<br>W = 1  through  10 | 300     |         | 1,000   | mV   |  |  |  |

|                                                         |                                                 | 1.1 V $\leq$ V <sub>CM</sub> $\leq$ 1.6 V $W = 1$                               | 200     |         | 1,000   | mV   |  |  |  |

|                                                         |                                                 | 1.1 V $\leq$ V <sub>CM</sub> $\leq$ 1.6 V<br>W = 2 through 10                   | 100     |         | 1,000   | mV   |  |  |  |

|                                                         |                                                 | 1.6 V < $V_{CM} \le 1.8 \text{ V}$<br>W = 1  through  10                        | 300     |         | 1,000   | mV   |  |  |  |

| Table 4–33. Stratix Device Capacitance Note (5) |                                                                                                                             |         |         |         |      |  |  |  |  |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|------|--|--|--|--|

| Symbol                                          | Parameter                                                                                                                   | Minimum | Typical | Maximum | Unit |  |  |  |  |

| C <sub>IOTB</sub>                               | Input capacitance on I/O pins in I/O banks 3, 4, 7, and 8.                                                                  |         | 11.5    |         | pF   |  |  |  |  |

| C <sub>IOLR</sub>                               | Input capacitance on I/O pins in I/O banks 1, 2, 5, and 6, including high-speed differential receiver and transmitter pins. |         | 8.2     |         | pF   |  |  |  |  |

| C <sub>CLKTB</sub>                              | Input capacitance on top/bottom clock input pins: CLK [4:7] and CLK [12:15].                                                |         | 11.5    |         | pF   |  |  |  |  |

| C <sub>CLKLR</sub>                              | Input capacitance on left/right clock inputs: CLK1, CLK3, CLK8, CLK10.                                                      |         | 7.8     |         | pF   |  |  |  |  |

| C <sub>CLKLR+</sub>                             | Input capacitance on left/right clock inputs: CLK0, CLK2, CLK9, and CLK11.                                                  |         | 4.4     |         | pF   |  |  |  |  |

#### Notes to Tables 4–10 through 4–33:

- (1) When  $tx_outclock$  port of altlvds\_tx megafunction is 717 MHz,  $V_{OD(min)} = 235$  mV on the output clock pin.

- (2) Pin pull-up resistance values will lower if an external source drives the pin higher than V<sub>CCIO</sub>.

- (3) Drive strength is programmable according to the values shown in the *Stratix Architecture* chapter of the *Stratix Device Handbook, Volume 1*.

- (4) V<sub>REF</sub> specifies the center point of the switching range.

- (5) Capacitance is sample-tested only. Capacitance is measured using time-domain reflections (TDR). Measurement accuracy is within ±0.5 pF.

- (6)  $V_{IO}$  and  $V_{CM}$  have multiple ranges and values for J=1 through 10.

# Power Consumption

Altera® offers two ways to calculate power for a design: the Altera web power calculator and the PowerGauge<sup>TM</sup> feature in the Quartus® II software.

The interactive power calculator on the Altera web site is typically used prior to designing the FPGA in order to get a magnitude estimate of the device power. The Quartus II software PowerGauge feature allows you to apply test vectors against your design for more accurate power consumption modeling.

In both cases, these calculations should only be used as an estimation of power, not as a specification.

Stratix devices require a certain amount of power-up current to successfully power up because of the small process geometry on which they are fabricated.

Table 4–34 shows the maximum power-up current ( $I_{CCINT}$ ) required to power a Stratix device. This specification is for commercial operating conditions. Measurements were performed with an isolated Stratix device on the board to characterize the power-up current of an isolated

# **Timing Model**

The DirectDrive<sup>TM</sup> technology and MultiTrack<sup>TM</sup> interconnect ensure predictable performance, accurate simulation, and accurate timing analysis across all Stratix device densities and speed grades. This section describes and specifies the performance, internal, external, and PLL timing specifications.

All specifications are representative of worst-case supply voltage and junction temperature conditions.

# **Preliminary & Final Timing**

Timing models can have either preliminary or final status. The Quartus II software issues an informational message during the design compilation if the timing models are preliminary. Table 4–35 shows the status of the Stratix device timing models.

Preliminary status means the timing model is subject to change. Initially, timing numbers are created using simulation results, process data, and other known parameters. These tests are used to make the preliminary numbers as close to the actual timing parameters as possible.

Final timing numbers are based on actual device operation and testing. These numbers reflect the actual performance of the device under worst-case voltage and junction temperature conditions.

| Table 4–35. Stratix Device Timing Model Status |             |          |  |  |  |  |  |

|------------------------------------------------|-------------|----------|--|--|--|--|--|

| Device                                         | Preliminary | Final    |  |  |  |  |  |

| EP1S10                                         |             | ✓        |  |  |  |  |  |

| EP1S20                                         |             | ✓        |  |  |  |  |  |

| EP1S25                                         |             | ✓        |  |  |  |  |  |

| EP1S30                                         |             | ✓        |  |  |  |  |  |

| EP1S40                                         |             | ✓        |  |  |  |  |  |

| EP1S60                                         |             | ✓        |  |  |  |  |  |

| EP1S80                                         |             | <b>✓</b> |  |  |  |  |  |

| Table 4–50. M-RAM Block Internal Timing Microparameters (Part 2 of 2) |       |       |       |       |       |       |       |       |      |

|-----------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Cumbal                                                                | -     | -5    |       | -6    |       | 7     | -8    |       |      |

| Symbol                                                                | Min   | Max   | Min   | Max   | Min   | Max   | Min   | Max   | Unit |

| t <sub>MRAMBESU</sub>                                                 | 25    |       | 25    |       | 28    |       | 33    |       | ps   |

| t <sub>MRAMBEH</sub>                                                  | 18    |       | 20    |       | 23    |       | 27    |       | ps   |

| t <sub>MRAMDATAASU</sub>                                              | 25    |       | 25    |       | 28    |       | 33    |       | ps   |

| t <sub>MRAMDATAAH</sub>                                               | 18    |       | 20    |       | 23    |       | 27    |       | ps   |

| t <sub>MRAMADDRASU</sub>                                              | 25    |       | 25    |       | 28    |       | 33    |       | ps   |

| t <sub>MRAMADDRAH</sub>                                               | 18    |       | 20    |       | 23    |       | 27    |       | ps   |

| t <sub>MRAMDATABSU</sub>                                              | 25    |       | 25    |       | 28    |       | 33    |       | ps   |

| t <sub>MRAMDATABH</sub>                                               | 18    |       | 20    |       | 23    |       | 27    |       | ps   |

| t <sub>MRAMADDRBSU</sub>                                              | 25    |       | 25    |       | 28    |       | 33    |       | ps   |

| t <sub>MRAMADDRBH</sub>                                               | 18    |       | 20    |       | 23    |       | 27    |       | ps   |

| t <sub>MRAMDATACO1</sub>                                              |       | 1,038 |       | 1,053 |       | 1,210 |       | 1,424 | ps   |

| t <sub>MRAMDATACO2</sub>                                              |       | 4,362 |       | 4,939 |       | 5,678 |       | 6,681 | ps   |

| t <sub>MRAMCLKHL</sub>                                                | 1,000 |       | 1,111 |       | 1,190 |       | 1,400 |       | ps   |

| t <sub>MRAMCLR</sub>                                                  | 135   |       | 150   |       | 172   |       | 202   |       | ps   |

| Table 4-51.        | Table 4–51. Routing Delay Internal Timing Parameters |     |     |     |     |     |     |     |    |    |      |

|--------------------|------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|----|----|------|

| O                  | -5                                                   |     | -5  |     |     | -6  |     | -7  |    | -8 | Unit |

| Symbol             | Min                                                  | Max | Min | Max | Min | Max | Min | Max |    |    |      |

| t <sub>R4</sub>    |                                                      | 268 |     | 295 |     | 339 |     | 390 | ps |    |      |

| t <sub>R8</sub>    |                                                      | 371 |     | 349 |     | 401 |     | 461 | ps |    |      |

| t <sub>R24</sub>   |                                                      | 465 |     | 512 |     | 588 |     | 676 | ps |    |      |

| t <sub>C4</sub>    |                                                      | 440 |     | 484 |     | 557 |     | 641 | ps |    |      |

| t <sub>C8</sub>    |                                                      | 577 |     | 634 |     | 730 |     | 840 | ps |    |      |

| t <sub>C16</sub>   |                                                      | 445 |     | 489 |     | 563 |     | 647 | ps |    |      |

| t <sub>LOCAL</sub> |                                                      | 313 |     | 345 |     | 396 |     | 455 | ps |    |      |

Routing delays vary depending on the load on that specific routing line. The Quartus II software reports the routing delay information when running the timing analysis for a design.

| Table 4–53. Stratix Regional Clock External I/O Ti | iming Parameters (Part 2 |

|----------------------------------------------------|--------------------------|

| <b>of 2)</b> Notes (1), (2)                        |                          |

|                                                    |                          |

| Symbol             | Parameter                                                                                                                              |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>XZPLL</sub> | Synchronous IOE output enable register to output pin disable delay using regional clock fed by Enhanced PLL with default phase setting |

| t <sub>ZXPLL</sub> | Synchronous IOE output enable register to output pin enable delay using regional clock fed by Enhanced PLL with default phase setting  |

### *Notes to Table 4–53:*

- (1) These timing parameters are sample-tested only.

- (2) These timing parameters are for column and row IOE pins. You should use the Quartus II software to verify the external timing for any pin.

Table 4–54 shows the external I/O timing parameters when using global clock networks.

| <b>Table 4–3</b> (2)  | 54. Stratix Global Clock External I/O Timing Parameters Notes (1),                                                                    |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                | Parameter                                                                                                                             |

| t <sub>INSU</sub>     | Setup time for input or bidirectional pin using IOE input register with global clock fed by ${\tt CLK}$ pin                           |

| t <sub>INH</sub>      | Hold time for input or bidirectional pin using IOE input register with global clock fed by ${\tt CLK}$ pin                            |

| t <sub>OUTCO</sub>    | Clock-to-output delay output or bidirectional pin using IOE output register with global clock fed by CLK pin                          |

| t <sub>INSUPLL</sub>  | Setup time for input or bidirectional pin using IOE input register with global clock fed by Enhanced PLL with default phase setting   |

| t <sub>INHPLL</sub>   | Hold time for input or bidirectional pin using IOE input register with global clock fed by Enhanced PLL with default phase setting    |

| t <sub>OUTCOPLL</sub> | Clock-to-output delay output or bidirectional pin using IOE output register with global clock Enhanced PLL with default phase setting |

| t <sub>XZPLL</sub>    | Synchronous IOE output enable register to output pin disable delay using global clock fed by Enhanced PLL with default phase setting  |

| t <sub>ZXPLL</sub>    | Synchronous IOE output enable register to output pin enable delay using global clock fed by Enhanced PLL with default phase setting   |

#### Notes to Table 4-54:

- (1) These timing parameters are sample-tested only.

- (2) These timing parameters are for column and row IOE pins. You should use the Quartus II software to verify the external timing for any pin.

| Table 4-65. I         | Table 4–65. EP1S20 External I/O Timing on Row Pins Using Regional Clock Networks Note (1) |       |                |       |                |       |                |     |      |  |

|-----------------------|-------------------------------------------------------------------------------------------|-------|----------------|-------|----------------|-------|----------------|-----|------|--|

| Davamatav             | -5 Speed Grade                                                                            |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |     | 11   |  |

| Parameter             | Min                                                                                       | Max   | Min            | Max   | Min            | Max   | Min            | Max | Unit |  |

| t <sub>INSU</sub>     | 1.815                                                                                     |       | 1.967          |       | 2.258          |       | NA             |     | ns   |  |

| t <sub>INH</sub>      | 0.000                                                                                     |       | 0.000          |       | 0.000          |       | NA             |     | ns   |  |

| t <sub>OUTCO</sub>    | 2.633                                                                                     | 5.235 | 2.663          | 5.595 | 2.663          | 6.070 | NA             | NA  | ns   |  |

| t <sub>XZ</sub>       | 2.660                                                                                     | 5.289 | 2.660          | 5.651 | 2.660          | 6.138 | NA             | NA  | ns   |  |

| t <sub>ZX</sub>       | 2.660                                                                                     | 5.289 | 2.660          | 5.651 | 2.660          | 6.138 | NA             | NA  | ns   |  |

| t <sub>INSUPLL</sub>  | 1.060                                                                                     |       | 1.112          |       | 1.277          |       | NA             |     | ns   |  |

| t <sub>INHPLL</sub>   | 0.000                                                                                     |       | 0.000          |       | 0.000          |       | NA             |     | ns   |  |

| t <sub>OUTCOPLL</sub> | 1.325                                                                                     | 2.770 | 1.325          | 2.908 | 1.325          | 2.978 | NA             | NA  | ns   |  |

| t <sub>XZPLL</sub>    | 1.352                                                                                     | 2.824 | 1.352          | 2.964 | 1.352          | 3.046 | NA             | NA  | ns   |  |

| t <sub>ZXPLL</sub>    | 1.352                                                                                     | 2.824 | 1.352          | 2.964 | 1.352          | 3.046 | NA             | NA  | ns   |  |

| Table 4–66. I         | Table 4–66. EP1S20 External I/O Timing on Row Pins Using Global Clock Networks Note (1) |       |         |                |       |                |     |                |      |  |

|-----------------------|-----------------------------------------------------------------------------------------|-------|---------|----------------|-------|----------------|-----|----------------|------|--|

| Parameter             | -5 Speed Grade                                                                          |       | -6 Spee | -6 Speed Grade |       | -7 Speed Grade |     | -8 Speed Grade |      |  |

| Parameter             | Min                                                                                     | Max   | Min     | Max            | Min   | Max            | Min | Max            | Unit |  |

| t <sub>INSU</sub>     | 1.742                                                                                   |       | 1.887   |                | 2.170 |                | NA  |                | ns   |  |

| t <sub>INH</sub>      | 0.000                                                                                   |       | 0.000   |                | 0.000 |                | NA  |                | ns   |  |

| t <sub>OUTCO</sub>    | 2.674                                                                                   | 5.308 | 2.674   | 5.675          | 2.674 | 6.158          | NA  | NA             | ns   |  |

| t <sub>XZ</sub>       | 2.701                                                                                   | 5.362 | 2.701   | 5.731          | 2.701 | 6.226          | NA  | NA             | ns   |  |

| t <sub>ZX</sub>       | 2.701                                                                                   | 5.362 | 2.701   | 5.731          | 2.701 | 6.226          | NA  | NA             | ns   |  |

| t <sub>INSUPLL</sub>  | 1.353                                                                                   |       | 1.418   |                | 1.613 |                | NA  |                | ns   |  |

| t <sub>INHPLL</sub>   | 0.000                                                                                   |       | 0.000   |                | 0.000 |                | NA  |                | ns   |  |

| t <sub>OUTCOPLL</sub> | 1.158                                                                                   | 2.447 | 1.158   | 2.602          | 1.158 | 2.642          | NA  | NA             | ns   |  |

| t <sub>XZPLL</sub>    | 1.185                                                                                   | 2.531 | 1.158   | 2.602          | 1.185 | 2.710          | NA  | NA             | ns   |  |

| t <sub>ZXPLL</sub>    | 1.185                                                                                   | 2.531 | 1.158   | 2.602          | 1.185 | 2.710          | NA  | NA             | ns   |  |

*Note to Tables 4–61 to 4–66:*

<sup>(1)</sup> Only EP1S25, EP1S30, and EP1S40 have a speed grade of -8.

Tables 4–105 through 4–108 show the output adder delays associated with column and row I/O pins for both fast and slow slew rates. If an I/O standard is selected other than 3.3-V LVTTL 4mA or LVCMOS 2 mA with a fast slew rate, add the selected delay to the external  $t_{\rm OUTCO}$ ,  $t_{\rm OUTCOPLL}$ ,  $t_{\rm XZ}$ ,  $t_{\rm XZPLL}$ , and  $t_{\rm ZXPLL}$  I/O parameters shown in Table 4–55 on page 4–36 through Table 4–96 on page 4–56.

| Table 4–105.    | Stratix I/O S | Standard          | Output De | lay Adde | rs for Fas     | t Slew Ra | ate on Col     | umn Pins | (Part 1 o      | f 2) |

|-----------------|---------------|-------------------|-----------|----------|----------------|-----------|----------------|----------|----------------|------|

| Donomo          |               | -5 Speed Grade -6 |           | -6 Spee  | -6 Speed Grade |           | -7 Speed Grade |          | -8 Speed Grade |      |

| Parameter       |               | Min               | Max       | Min      | Max            | Min       | Max            | Min      | Max            | Unit |

| LVCMOS          | 2 mA          |                   | 1,895     |          | 1,990          |           | 1,990          |          | 1,990          | ps   |

|                 | 4 mA          |                   | 956       |          | 1,004          |           | 1,004          |          | 1,004          | ps   |

|                 | 8 mA          |                   | 189       |          | 198            |           | 198            |          | 198            | ps   |

|                 | 12 mA         |                   | 0         |          | 0              |           | 0              |          | 0              | ps   |

|                 | 24 mA         |                   | -157      |          | -165           |           | -165           |          | -165           | ps   |

| 3.3-V LVTTL     | 4 mA          |                   | 1,895     |          | 1,990          |           | 1,990          |          | 1,990          | ps   |

|                 | 8 mA          |                   | 1,347     |          | 1,414          |           | 1,414          |          | 1,414          | ps   |

|                 | 12 mA         |                   | 636       |          | 668            |           | 668            |          | 668            | ps   |

|                 | 16 mA         |                   | 561       |          | 589            |           | 589            |          | 589            | ps   |

|                 | 24 mA         |                   | 0         |          | 0              |           | 0              |          | 0              | ps   |

| 2.5-V LVTTL     | 2 mA          |                   | 2,517     |          | 2,643          |           | 2,643          |          | 2,643          | ps   |

|                 | 8 mA          |                   | 834       |          | 875            |           | 875            |          | 875            | ps   |

|                 | 12 mA         |                   | 504       |          | 529            |           | 529            |          | 529            | ps   |

|                 | 16 mA         |                   | 194       |          | 203            |           | 203            |          | 203            | ps   |

| 1.8-V LVTTL     | 2 mA          |                   | 1,304     |          | 1,369          |           | 1,369          |          | 1,369          | ps   |

|                 | 8 mA          |                   | 960       |          | 1,008          |           | 1,008          |          | 1,008          | ps   |

|                 | 12 mA         |                   | 960       |          | 1,008          |           | 1,008          |          | 1,008          | ps   |

| 1.5-V LVTTL     | 2 mA          |                   | 6,680     |          | 7,014          |           | 7,014          |          | 7,014          | ps   |

|                 | 4 mA          |                   | 3,275     |          | 3,439          |           | 3,439          |          | 3,439          | ps   |

|                 | 8 mA          |                   | 1,589     |          | 1,668          |           | 1,668          |          | 1,668          | ps   |

| GTL             |               |                   | 16        |          | 17             |           | 17             |          | 17             | ps   |

| GTL+            |               |                   | 9         |          | 9              |           | 9              |          | 9              | ps   |

| 3.3-V PCI       |               |                   | 50        |          | 52             |           | 52             |          | 52             | ps   |

| 3.3-V PCI-X 1.0 | )             |                   | 50        |          | 52             |           | 52             |          | 52             | ps   |

| Compact PCI     |               |                   | 50        |          | 52             |           | 52             |          | 52             | ps   |

| AGP 1×          |               |                   | 50        |          | 52             |           | 52             |          | 52             | ps   |

| AGP 2×          |               |                   | 1,895     |          | 1,990          |           | 1,990          |          | 1,990          | ps   |

Table 4–116. Stratix Maximum Input Clock Rate for CLK[1, 3, 8, 10] Pins in Flip-Chip Packages

| I/O Standard                  | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------|-------------------|-------------------|-------------------|-------------------|------|

| LVTTL                         | 422               | 422               | 390               | 390               | MHz  |

| 2.5 V                         | 422               | 422               | 390               | 390               | MHz  |

| 1.8 V                         | 422               | 422               | 390               | 390               | MHz  |

| 1.5 V                         | 422               | 422               | 390               | 390               | MHz  |

| LVCMOS                        | 422               | 422               | 390               | 390               | MHz  |

| GTL+                          | 300               | 250               | 200               | 200               | MHz  |

| SSTL-3 Class I                | 400               | 350               | 300               | 300               | MHz  |

| SSTL-3 Class II               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-2 Class I                | 400               | 350               | 300               | 300               | MHz  |

| SSTL-2 Class II               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-18 Class I               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-18 Class II              | 400               | 350               | 300               | 300               | MHz  |

| 1.5-V HSTL Class I            | 400               | 350               | 300               | 300               | MHz  |

| 1.8-V HSTL Class I            | 400               | 350               | 300               | 300               | MHz  |

| СТТ                           | 300               | 250               | 200               | 200               | MHz  |

| Differential 1.5-V HSTL<br>C1 | 400               | 350               | 300               | 300               | MHz  |

| LVPECL (1)                    | 645               | 645               | 640               | 640               | MHz  |

| PCML (1)                      | 300               | 275               | 275               | 275               | MHz  |

| LVDS (1)                      | 645               | 645               | 640               | 640               | MHz  |

| HyperTransport technology (1) | 500               | 500               | 450               | 450               | MHz  |

Table 4–117. Stratix Maximum Input Clock Rate for CLK[7..4] & CLK[15..12] Pins in Wire-Bond Packages (Part 1 of 2)

| I/O Standard | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|--------------|-------------------|-------------------|-------------------|------|

| LVTTL        | 422               | 390               | 390               | MHz  |

| 2.5 V        | 422               | 390               | 390               | MHz  |

| 1.8 V        | 422               | 390               | 390               | MHz  |

| 1.5 V        | 422               | 390               | 390               | MHz  |

| LVCMOS       | 422               | 390               | 390               | MHz  |

| GTL          | 250               | 200               | 200               | MHz  |

Table 4–118. Stratix Maximum Input Clock Rate for CLK[0, 2, 9, 11] Pins & FPLL[10..7]CLK Pins in Wire-Bond Packages (Part 2 of 2)

| I/O Standard                  | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------|-------------------|-------------------|-------------------|------|

| LVCMOS                        | 422               | 390               | 390               | MHz  |

| GTL+                          | 250               | 200               | 200               | MHz  |

| SSTL-3 Class I                | 350               | 300               | 300               | MHz  |

| SSTL-3 Class II               | 350               | 300               | 300               | MHz  |

| SSTL-2 Class I                | 350               | 300               | 300               | MHz  |

| SSTL-2 Class II               | 350               | 300               | 300               | MHz  |

| SSTL-18 Class I               | 350               | 300               | 300               | MHz  |

| SSTL-18 Class II              | 350               | 300               | 300               | MHz  |

| 1.5-V HSTL Class I            | 350               | 300               | 300               | MHz  |

| 1.8-V HSTL Class I            | 350               | 300               | 300               | MHz  |

| CTT                           | 250               | 200               | 200               | MHz  |

| Differential 1.5-V HSTL<br>C1 | 350               | 300               | 300               | MHz  |

| LVPECL (1)                    | 717               | 640               | 640               | MHz  |

| PCML (1)                      | 375               | 350               | 350               | MHz  |

| LVDS (1)                      | 717               | 640               | 640               | MHz  |

| HyperTransport technology (1) | 717               | 640               | 640               | MHz  |

Table 4–119. Stratix Maximum Input Clock Rate for CLK[1, 3, 8, 10] Pins in Wire-Bond Packages (Part 1 of 2)

| I/O Standard    | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-----------------|-------------------|-------------------|-------------------|------|

| LVTTL           | 422               | 390               | 390               | MHz  |

| 2.5 V           | 422               | 390               | 390               | MHz  |

| 1.8 V           | 422               | 390               | 390               | MHz  |

| 1.5 V           | 422               | 390               | 390               | MHz  |

| LVCMOS          | 422               | 390               | 390               | MHz  |

| GTL+            | 250               | 200               | 200               | MHz  |

| SSTL-3 Class I  | 350               | 300               | 300               | MHz  |

| SSTL-3 Class II | 350               | 300               | 300               | MHz  |

| SSTL-2 Class I  | 350               | 300               | 300               | MHz  |

| SSTL-2 Class II | 350               | 300               | 300               | MHz  |

| Table 4–127. Enhanced PLL Specifications for -5 Speed Grades (Part 2 of 2) |                                                                                                                     |     |     |     |      |  |  |  |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|--|--|--|

| Symbol                                                                     | Parameter                                                                                                           | Min | Тур | Max | Unit |  |  |  |

| t <sub>SKEW</sub>                                                          | Clock skew between two external clock outputs driven by the different counters with the same settings               |     | ±75 |     | ps   |  |  |  |

| f <sub>SS</sub>                                                            | Spread spectrum modulation frequency                                                                                | 30  |     | 150 | kHz  |  |  |  |

| % spread                                                                   | Percentage spread for spread spectrum frequency (10)                                                                | 0.4 | 0.5 | 0.6 | %    |  |  |  |

| t <sub>ARESET</sub>                                                        | Minimum pulse width on areset signal                                                                                | 10  |     |     | ns   |  |  |  |

| tareset_recon<br>fig                                                       | Minimum pulse width on the areset signal when using PLL reconfiguration. Reset the PLL after scandataout goes high. | 500 |     |     | ns   |  |  |  |

| Table 4–1.               | 28. Enhanced PLL Specifications for -6                          | Speed C       | irades | (Part 1 of 2)                                              |              |

|--------------------------|-----------------------------------------------------------------|---------------|--------|------------------------------------------------------------|--------------|

| Symbol                   | Parameter                                                       | Min           | Тур    | Max                                                        | Unit         |

| $f_{\text{IN}}$          | Input clock frequency                                           | 3<br>(1), (2) |        | 650                                                        | MHz          |

| f <sub>INPFD</sub>       | Input frequency to PFD                                          | 3             |        | 420                                                        | MHz          |

| f <sub>INDUTY</sub>      | Input clock duty cycle                                          | 40            |        | 60                                                         | %            |

| f <sub>EINDUTY</sub>     | External feedback clock input duty cycle                        | 40            |        | 60                                                         | %            |

| t <sub>INJITTER</sub>    | Input clock period jitter                                       |               |        | ±200 (3)                                                   | ps           |

| t <sub>EINJITTER</sub>   | External feedback clock period jitter                           |               |        | ±200 (3)                                                   | ps           |

| t <sub>FCOMP</sub>       | External feedback clock compensation time (4)                   |               |        | 6                                                          | ns           |

| f <sub>OUT</sub>         | Output frequency for internal global or regional clock          | 0.3           |        | 450                                                        | MHz          |

| f <sub>OUT_EXT</sub>     | Output frequency for external clock (3)                         | 0.3           |        | 500                                                        | MHz          |

| t <sub>OUTDUTY</sub>     | Duty cycle for external clock output (when set to 50%)          | 45            |        | 55                                                         | %            |

| t <sub>JITTER</sub>      | Period jitter for external clock output (6)                     |               |        | ±100 ps for >200-MHz outclk<br>±20 mUI for <200-MHz outclk | ps or<br>mUI |

| t <sub>CONFIG5,6</sub>   | Time required to reconfigure the scan chains for PLLs 5 and 6   |               |        | 289/f <sub>SCANCLK</sub>                                   |              |

| t <sub>CONFIG11,12</sub> | Time required to reconfigure the scan chains for PLLs 11 and 12 |               |        | 193/f <sub>SCANCLK</sub>                                   |              |