Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 4125                                                    |

| Number of Logic Elements/Cells | 41250                                                   |

| Total RAM Bits                 | 3423744                                                 |

| Number of I/O                  | 615                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                         |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 780-BBGA, FCBGA                                         |

| Supplier Device Package        | 780-FBGA (29x29)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s40f780c7 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Chapter | Date/Version         | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4       | October 2003, v2.1   | <ul> <li>Added -8 speed grade information.</li> <li>Updated performance information in Table 4–36.</li> <li>Updated timing information in Tables 4–55 through 4–96.</li> <li>Updated delay information in Tables 4–103 through 4–108.</li> <li>Updated programmable delay information in Tables 4–100 and 4–103.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | July 2003, v2.0      | <ul> <li>Updated clock rates in Tables 4–114 through 4–123.</li> <li>Updated speed grade information in the introduction on page 4-1.</li> <li>Corrected figures 4-1 &amp; 4-2 and Table 4-9 to reflect how VID and VOD are specified.</li> <li>Added note 6 to Table 4-32.</li> <li>Updated Stratix Performance Table 4-35.</li> <li>Updated EP1S60 and EP1S80 timing parameters in Tables 4-82 to 4-93. The Stratix timing models are final for all devices.</li> <li>Updated Stratix IOE programmable delay chains in Tables 4-100 to 4-101.</li> <li>Added single-ended I/O standard output pin delay adders for loading in Table 4-102.</li> <li>Added spec for FPLL[107]CLK pins in Tables 4-104 and 4-107.</li> <li>Updated high-speed I/O specification for J=2 in Tables 4-114 and 4-115.</li> <li>Updated EPLL specification and fast PLL specification in Tables 4-116 to 4-120.</li> </ul> |

| 5       | September 2004, v2.1 | <ul> <li>Updated reference to device pin-outs on page 5-1 to indicate that<br/>device pin-outs are no longer included in this manual and are now<br/>available on the Altera web site.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | April 2003, v1.0     | No new changes in Stratix Device Handbook v2.0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Altera Corporation Section I–7

Stratix devices are available in space-saving FineLine BGA® and ball-grid array (BGA) packages (see Tables 1–3 through 1–5). All Stratix devices support vertical migration within the same package (for example, you can migrate between the EP1S10, EP1S20, and EP1S25 devices in the 672-pin BGA package). Vertical migration means that you can migrate to devices whose dedicated pins, configuration pins, and power pins are the same for a given package across device densities. For I/O pin migration across densities, you must cross-reference the available I/O pins using the device pin-outs for all planned densities of a given package type to identify which I/O pins are migrational. The Quartus® II software can automatically cross reference and place all pins except differential pins for migration when given a device migration list. You must use the pin-outs for each device to verify the differential placement migration. A future version of the Quartus II software will support differential pin migration.

| Table 1-3. | Table 1–3. Stratix Package Options & I/O Pin Counts |                |                            |                            |                            |                              |                              |  |  |  |  |

|------------|-----------------------------------------------------|----------------|----------------------------|----------------------------|----------------------------|------------------------------|------------------------------|--|--|--|--|

| Device     | 672-Pin<br>BGA                                      | 956-Pin<br>BGA | 484-Pin<br>FineLine<br>BGA | 672-Pin<br>FineLine<br>BGA | 780-Pin<br>FineLine<br>BGA | 1,020-Pin<br>FineLine<br>BGA | 1,508-Pin<br>FineLine<br>BGA |  |  |  |  |

| EP1S10     | 345                                                 |                | 335                        | 345                        | 426                        |                              |                              |  |  |  |  |

| EP1S20     | 426                                                 |                | 361                        | 426                        | 586                        |                              |                              |  |  |  |  |

| EP1S25     | 473                                                 |                |                            | 473                        | 597                        | 706                          |                              |  |  |  |  |

| EP1S30     |                                                     | 683            |                            |                            | 597                        | 726                          |                              |  |  |  |  |

| EP1S40     |                                                     | 683            |                            |                            | 615                        | 773                          | 822                          |  |  |  |  |

| EP1S60     |                                                     | 683            |                            |                            |                            | 773                          | 1,022                        |  |  |  |  |

| EP1S80     |                                                     | 683            |                            |                            |                            | 773                          | 1,203                        |  |  |  |  |

#### Note to Table 1-3:

<sup>(1)</sup> All I/O pin counts include 20 dedicated clock input pins (clk [15..0] p, clk0n, clk2n, clk9n, and clk11n) that can be used for data inputs.

| Table 1–4. Stratix BGA Package Sizes |         |         |  |  |  |  |  |  |

|--------------------------------------|---------|---------|--|--|--|--|--|--|

| Dimension                            | 672 Pin | 956 Pin |  |  |  |  |  |  |

| Pitch (mm)                           | 1.27    | 1.27    |  |  |  |  |  |  |

| Area (mm²)                           | 1,225   | 1,600   |  |  |  |  |  |  |

| Length × width (mm × mm)             | 35 × 35 | 40 × 40 |  |  |  |  |  |  |

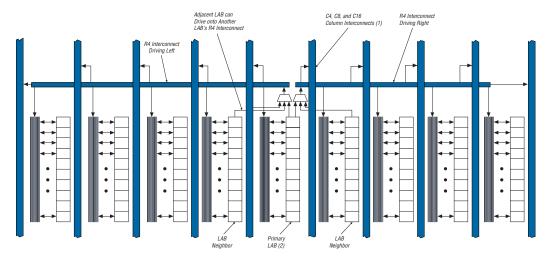

row connections in a four-LAB region. Every LAB has its own set of R4 interconnects to drive either left or right. Figure 2–9 shows R4 interconnect connections from an LAB. R4 interconnects can drive and be driven by DSP blocks and RAM blocks and horizontal IOEs. For LAB interfacing, a primary LAB or LAB neighbor can drive a given R4 interconnect. For R4 interconnects that drive to the right, the primary LAB and right neighbor can drive on to the interconnect. For R4 interconnects that drive to the left, the primary LAB and its left neighbor can drive on to the interconnects can drive other R4 interconnects to extend the range of LABs they can drive. R4 interconnects can also drive C4 and C16 interconnects for connections from one row to another. Additionally, R4 interconnects can drive R24 interconnects.

Figure 2-9. R4 Interconnect Connections

#### *Notes to Figure 2–9:*

- (1) C4 interconnects can drive R4 interconnects.

- (2) This pattern is repeated for every LAB in the LAB row.

The R8 interconnects span eight LABs, M512 or M4K RAM blocks, or DSP blocks to the right or left from a source LAB. These resources are used for fast row connections in an eight-LAB region. Every LAB has its own set of R8 interconnects to drive either left or right. R8 interconnect connections between LABs in a row are similar to the R4 connections shown in Figure 2–9, with the exception that they connect to eight LABs to the right or left, not four. Like R4 interconnects, R8 interconnects can drive and be driven by all types of architecture blocks. R8 interconnects

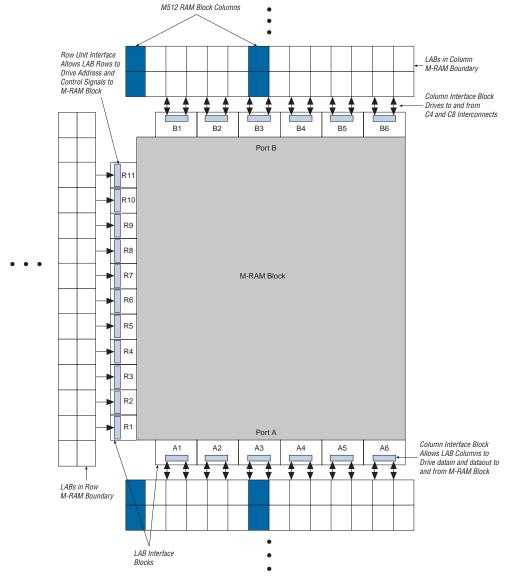

#### M-RAM Block

The largest TriMatrix memory block, the M-RAM block, is useful for applications where a large volume of data must be stored on-chip. Each block contains 589,824 RAM bits (including parity bits). The M-RAM block can be configured in the following modes:

- True dual-port RAM

- Simple dual-port RAM

- Single-port RAM

- FIFO RAM

You cannot use an initialization file to initialize the contents of a M-RAM block. All M-RAM block contents power up to an undefined value. Only synchronous operation is supported in the M-RAM block, so all inputs are registered. Output registers can be bypassed. The memory address and output width can be configured as  $64 \text{K} \times 8$  (or  $64 \text{K} \times 9$  bits),  $32 \text{K} \times 16$  (or  $32 \text{K} \times 18$  bits),  $16 \text{K} \times 32$  (or  $16 \text{K} \times 36$  bits),  $8 \text{K} \times 64$  (or  $8 \text{K} \times 72$  bits), and  $4 \text{K} \times 128$  (or  $4 \text{K} \times 144$  bits). The  $4 \text{K} \times 128$  configuration is unavailable in true dual-port mode because there are a total of 144 data output drivers in the block. Mixed-width configurations are also possible, allowing different read and write widths. Tables 2–8 and 2–9 summarize the possible M-RAM block configurations:

| Table 2–8. M-RAM Block Configurations (Simple Dual-Port) |          |          |          |          |          |  |  |  |  |  |

|----------------------------------------------------------|----------|----------|----------|----------|----------|--|--|--|--|--|

| Write Port                                               |          |          |          |          |          |  |  |  |  |  |

| Read Port                                                | 64K × 9  | 32K × 18 | 16K × 36 | 8K × 72  | 4K × 144 |  |  |  |  |  |

| 64K × 9                                                  | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |  |  |  |  |  |

| 32K × 18                                                 | ✓        | ✓        | ✓        | ✓        |          |  |  |  |  |  |

| 16K × 36                                                 | ✓        | ✓        | ✓        | ✓        |          |  |  |  |  |  |

| 8K × 72                                                  | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |  |  |  |  |  |

| 4K × 144                                                 |          |          |          |          | ✓        |  |  |  |  |  |

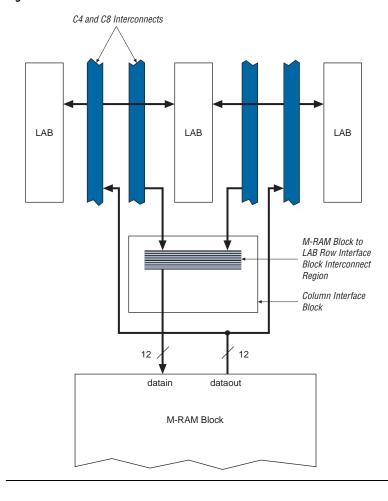

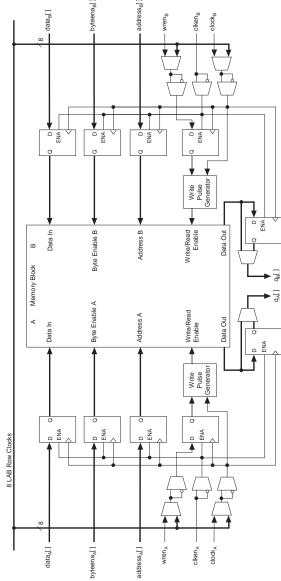

Figure 2–21. Left-Facing M-RAM to Interconnect Interface Notes (1), (2)

*Notes to Figure 2–21:*

- (1) Only R24 and C16 interconnects cross the M-RAM block boundaries.

- (2) The right-facing M-RAM block has interface blocks on the right side, but none on the left. B1 to B6 and A1 to A6 orientation is clipped across the vertical axis for right-facing M-RAM blocks.

Figure 2–23. M-RAM Column Unit Interface to Interconnect

Figure 2–24. Independent Clock Mode Notes (1), (2)

Notes to Figure 2-24

- (1) All registers shown have asynchronous clear ports.

- (2) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

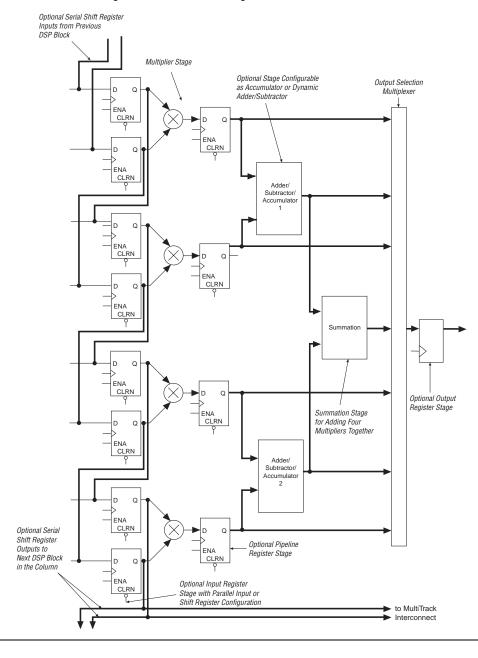

Figure 2–30. DSP Block Diagram for 18 imes 18-Bit Configuration

### Input Registers

A bank of optional input registers is located at the input of each multiplier and multiplicand inputs to the multiplier. When these registers are configured for parallel data inputs, they are driven by regular routing resources. You can use a clock signal, asynchronous clear signal, and a clock enable signal to independently control each set of A and B inputs for each multiplier in the DSP block. You select these control signals from a set of four different clock [3..0], aclr[3..0], and ena[3..0] signals that drive the entire DSP block.

You can also configure the input registers for a shift register application. In this case, the input registers feed the multiplier and drive two dedicated shift output lines:  $\mathtt{shiftoutA}$  and  $\mathtt{shiftoutB}$ . The shift outputs of one multiplier block directly feed the adjacent multiplier block in the same DSP block (or the next DSP block) as shown in Figure 2–33, to form a shift register chain. This chain can terminate in any block, that is, you can create any length of shift register chain up to 224 registers. You can use the input shift registers for FIR filter applications. One set of shift inputs can provide data for a filter, and the other are coefficients that are optionally loaded in serial or parallel. When implementing  $9 \times 9$ - and  $18 \times 18$ -bit multipliers, you do not need to implement external shift registers in LAB LEs. You implement all the filter circuitry within the DSP block and its routing resources, saving LE and general routing resources for general logic. External registers are needed for shift register inputs when using  $36 \times 36$ -bit multipliers.

☐ FPLL9CLK

Figure 2–50. Global & Regional Clock Connections from Side Pins & Fast PLL Outputs Note (1), (2) RCLK1 RCLK9 G1 G3 G8 G10 G2 🛕 RCLK0 ▲ G0 🛕 G9 ▲ G11 ▲ RCLK8 ▲ FPLL7CLK \_ ☐ FPLL10CLK 10 10 PLL 7 /1 /1 PLL 10 *g*0 *g*0 ☐ CLK10 CLK0 [ 10 10 CLK1 □ ☐ CLK11 PLL 1 /1 /1 PLL 4 *g*0 *g*0 □ CLK8 CLK2 CLK3 10 10 /1 PLL 3 PI 1 2 /1 g0 g0

Figure 2–50 shows the global and regional clocking from the PLL outputs and the CLK pins.

*Notes to Figure 2–50:*

FPLL8CLK \_\_

PLL 8 /1

g0

(1) PLLs 1 to 4 and 7 to 10 are fast PLLs. PLLs 5, 6, 11, and 12 are enhanced PLLs.

RCLK4

RCLK5

Regional

Clocks

(2) The global or regional clocks in a fast PLL's quadrant can drive the fast PLL input. A pin or other PLL must drive the global or regional source. The source cannot be driven by internally generated logic before driving the fast PLL.

Global

Clocks

Figure 2–51 shows the global and regional clocking from enhanced PLL outputs and top CLK pins.

RCLK14

RCLK15

Regional

Clocks

/1 PLL 9

During switchover, the PLL VCO continues to run and will either slow down or speed up, generating frequency drift on the PLL outputs. The clock switchover transitions without any glitches. After the switch, there is a finite resynchronization period to lock onto new clock as the VCO ramps up. The exact amount of time it takes for the PLL to relock relates to the PLL configuration and may be adjusted by using the programmable bandwidth feature of the PLL. The specification for the maximum time to relock is  $100~\mu s$ .

For more information on clock switchover, see *AN 313, Implementing Clock Switchover in Stratix & Stratix GX Devices*.

### PLL Reconfiguration

The PLL reconfiguration feature enables system logic to change Stratix device enhanced PLL counters and delay elements without reloading a Programmer Object File (.pof). This provides considerable flexibility for frequency synthesis, allowing real-time PLL frequency and output clock delay variation. You can sweep the PLL output frequencies and clock delay in prototype environments. The PLL reconfiguration feature can also dynamically or intelligently control system clock speeds or  $t_{\rm CO}$  delays in end systems.

Clock delay elements at each PLL output port implement variable delay. Figure 2–54 shows a diagram of the overall dynamic PLL control feature for the counters and the clock delay elements. The configuration time is less than 20 µs for the enhanced PLL using a input shift clock rate of 22 MHz. The charge pump, loop filter components, and phase shifting using VCO phase taps cannot be dynamically adjusted.

shift by the same degree amount. For example, all 10 DQS pins on the top of the device can be shifted by 90° and all 10 DQS pins on the bottom of the device can be shifted by 72°. The reference circuits require a maximum of 256 system reference clock cycles to set the correct phase on the DQS delay elements. Figure 2–69 illustrates the phase-shift reference circuit control of each DQS delay shift on the top of the device. This same circuit is duplicated on the bottom of the device.

Input

Reference

Clock

Phase

Comparator

Up/Down

Counter

Delay Chains

Control Signals to DQS Pins

Figure 2-69. Simplified Diagram of the DQS Phase-Shift Circuitry

See the *External Memory Interfaces* chapter in the *Stratix Device Handbook, Volume 2* for more information on external memory interfaces.

# **Programmable Drive Strength**

The output buffer for each Stratix device I/O pin has a programmable drive strength control for certain I/O standards. The LVTTL and LVCMOS standard has several levels of drive strength that the user can control. SSTL-3 Class I and II, SSTL-2 Class I and II, HSTL Class I and II, and 3.3-V GTL+ support a minimum setting, the lowest drive strength that guarantees the  $\rm I_{OH}/\rm I_{OL}$  of the standard. Using minimum settings provides signal slew rate control to reduce system noise and signal overshoot.

Stratix, Stratix II, Cyclone<sup>®</sup>, and Cyclone II devices must be within the first 17 devices in a JTAG chain. All of these devices have the same JTAG controller. If any of the Stratix, Stratix II, Cyclone, and Cyclone II devices are in the 18th or after they will fail configuration. This does not affect SignalTap II.

For more information on JTAG, see the following documents:

- AN 39: IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices

- Jam Programming & Test Language Specification

# SignalTap II Embedded Logic Analyzer

Stratix devices feature the SignalTap II embedded logic analyzer, which monitors design operation over a period of time through the IEEE Std. 1149.1 (JTAG) circuitry. You can analyze internal logic at speed without bringing internal signals to the I/O pins. This feature is particularly important for advanced packages, such as FineLine BGA® packages, because it can be difficult to add a connection to a pin during the debugging process after a board is designed and manufactured.

# Configuration

The logic, circuitry, and interconnects in the Stratix architecture are configured with CMOS SRAM elements. Altera® devices are reconfigurable. Because every device is tested with a high-coverage production test program, you do not have to perform fault testing and can focus on simulation and design verification.

Stratix devices are configured at system power-up with data stored in an Altera serial configuration device or provided by a system controller. Altera offers in-system programmability (ISP)-capable configuration devices that configure Stratix devices via a serial data stream. Stratix devices can be configured in under 100 ms using 8-bit parallel data at 100 MHz. The Stratix device's optimized interface allows microprocessors to configure it serially or in parallel, and synchronously or asynchronously. The interface also enables microprocessors to treat Stratix devices as memory and configure them by writing to a virtual memory location, making reconfiguration easy. After a Stratix device has been configured, it can be reconfigured in-circuit by resetting the device and loading new data. Real-time changes can be made during system operation, enabling innovative reconfigurable computing applications.

# **Operating Modes**

The Stratix architecture uses SRAM configuration elements that require configuration data to be loaded each time the circuit powers up. The process of physically loading the SRAM data into the device is called configuration. During initialization, which occurs immediately after

While in the factory configuration, the factory-configuration logic performs the following operations:

- Loads a remote update-control register to determine the page address of the new application configuration

- Determines whether to enable a user watchdog timer for the application configuration

- Determines what the watchdog timer setting should be if it is enabled

The user watchdog timer is a counter that must be continually reset within a specific amount of time in the user mode of an application configuration to ensure that valid configuration occurred during a remote update. Only valid application configurations designed for remote update can reset the user watchdog timer in user mode. If a valid application configuration does not reset the user watchdog timer in a specific amount of time, the timer updates a status register and loads the factory configuration. The user watchdog timer is automatically disabled for factory configurations.

If an error occurs in loading the application configuration, the configuration logic writes a status register to specify the cause of the error. Once this occurs, the Stratix device automatically loads the factory configuration, which reads the status register and determines the reason for reconfiguration. Based on the reason, the factory configuration will take appropriate steps and will write the remote update control register to specify the next application configuration page to be loaded.

When the Stratix device successfully loads the application configuration, it enters into user mode. The Stratix device then executes the main application of the user. Intellectual property (IP), such as a Nios® (16-bit ISA) and Nios® II (32-bit ISA) embedded processors, can help the Stratix device determine when remote update is coming. The Nios embedded processor or user logic receives incoming data, writes it to the configuration device, and loads the factory configuration. The factory configuration will read the remote update status register and determine the valid application configuration to load. Figure 3–2 shows the Stratix remote update. Figure 3–3 shows the transition diagram for remote update mode.

| Symbol            | Parameter                                          | Conditions         | Minimum      | Maximum           | Unit |

|-------------------|----------------------------------------------------|--------------------|--------------|-------------------|------|

| V <sub>CCIO</sub> | Supply voltage for output buffers, 3.3-V operation | (4), (5)           | 3.00 (3.135) | 3.60 (3.465)      | V    |

|                   | Supply voltage for output buffers, 2.5-V operation | (4)                | 2.375        | 2.625             | ٧    |

|                   | Supply voltage for output buffers, 1.8-V operation | (4)                | 1.71         | 1.89              | ٧    |

|                   | Supply voltage for output buffers, 1.5-V operation | (4)                | 1.4          | 1.6               | ٧    |

| VI                | Input voltage                                      | (3), (6)           | -0.5         | 4.0               | V    |

| V <sub>O</sub>    | Output voltage                                     |                    | 0            | V <sub>CCIO</sub> | V    |

| TJ                | Operating junction                                 | For commercial use | 0            | 85                | °C   |

|                   | temperature                                        | For industrial use | -40          | 100               | °C   |

| Table 4–3                         | Table 4–3. Stratix Device DC Operating Conditions Note (7) (Part 1 of 2) |                                                              |         |         |         |      |  |  |  |  |  |

|-----------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------|---------|---------|---------|------|--|--|--|--|--|

| Symbol                            | Parameter                                                                | Conditions                                                   | Minimum | Typical | Maximum | Unit |  |  |  |  |  |

| I <sub>I</sub>                    | Input pin leakage current                                                | $V_I = V_{CCIOmax}$ to 0 V (8)                               | -10     |         | 10      | μА   |  |  |  |  |  |

| I <sub>OZ</sub>                   | Tri-stated I/O pin leakage current                                       | V <sub>O</sub> = V <sub>CCIOmax</sub> to 0 V (8)             | -10     |         | 10      | μА   |  |  |  |  |  |

| I <sub>CC0</sub>                  | V <sub>CC</sub> supply current (standby) (All                            | V <sub>I</sub> = ground, no load, no toggling inputs         |         |         |         | mA   |  |  |  |  |  |

| memory blocks in power-down mode) | EP1S10. V <sub>I</sub> = ground, no load, no toggling inputs             |                                                              | 37      |         | mA      |      |  |  |  |  |  |

|                                   |                                                                          | EP1S20. V <sub>I</sub> = ground, no load, no toggling inputs |         | 65      |         | mA   |  |  |  |  |  |

|                                   |                                                                          | EP1S25. V <sub>I</sub> = ground, no load, no toggling inputs |         | 90      |         | mA   |  |  |  |  |  |

|                                   |                                                                          | EP1S30. V <sub>I</sub> = ground, no load, no toggling inputs |         | 114     |         | mA   |  |  |  |  |  |

|                                   |                                                                          | EP1S40. V <sub>I</sub> = ground, no load, no toggling inputs |         | 145     |         | mA   |  |  |  |  |  |

|                                   |                                                                          | EP1S60. V <sub>I</sub> = ground, no load, no toggling inputs |         | 200     |         | mA   |  |  |  |  |  |

|                                   |                                                                          | EP1S80. V <sub>I</sub> = ground, no load, no toggling inputs |         | 277     |         | mA   |  |  |  |  |  |

| Table 4–50. M-RAM Block Internal Timing Microparameters (Part 2 of 2) |       |       |       |       |       |       |       |       |       |  |  |

|-----------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

|                                                                       | -     | -5    |       | -6    |       | 7     | -8    |       | 11-14 |  |  |

| Symbol                                                                | Min   | Max   | Min   | Max   | Min   | Max   | Min   | Max   | Unit  |  |  |

| t <sub>MRAMBESU</sub>                                                 | 25    |       | 25    |       | 28    |       | 33    |       | ps    |  |  |

| t <sub>MRAMBEH</sub>                                                  | 18    |       | 20    |       | 23    |       | 27    |       | ps    |  |  |

| t <sub>MRAMDATAASU</sub>                                              | 25    |       | 25    |       | 28    |       | 33    |       | ps    |  |  |

| t <sub>MRAMDATAAH</sub>                                               | 18    |       | 20    |       | 23    |       | 27    |       | ps    |  |  |

| t <sub>MRAMADDRASU</sub>                                              | 25    |       | 25    |       | 28    |       | 33    |       | ps    |  |  |

| t <sub>MRAMADDRAH</sub>                                               | 18    |       | 20    |       | 23    |       | 27    |       | ps    |  |  |

| t <sub>MRAMDATABSU</sub>                                              | 25    |       | 25    |       | 28    |       | 33    |       | ps    |  |  |

| t <sub>MRAMDATABH</sub>                                               | 18    |       | 20    |       | 23    |       | 27    |       | ps    |  |  |

| t <sub>MRAMADDRBSU</sub>                                              | 25    |       | 25    |       | 28    |       | 33    |       | ps    |  |  |

| t <sub>MRAMADDRBH</sub>                                               | 18    |       | 20    |       | 23    |       | 27    |       | ps    |  |  |

| t <sub>MRAMDATACO1</sub>                                              |       | 1,038 |       | 1,053 |       | 1,210 |       | 1,424 | ps    |  |  |

| t <sub>MRAMDATACO2</sub>                                              |       | 4,362 |       | 4,939 |       | 5,678 |       | 6,681 | ps    |  |  |

| t <sub>MRAMCLKHL</sub>                                                | 1,000 |       | 1,111 |       | 1,190 |       | 1,400 |       | ps    |  |  |

| t <sub>MRAMCLR</sub>                                                  | 135   |       | 150   |       | 172   |       | 202   |       | ps    |  |  |

| Table 4-51.        | Table 4–51. Routing Delay Internal Timing Parameters |     |     |     |     |     |     |     |    |  |  |  |

|--------------------|------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|----|--|--|--|

| O                  |                                                      | -5  | -6  |     |     | -7  |     | -8  |    |  |  |  |

| Symbol             | Min                                                  | Max | Min | Max | Min | Max | Min | Max |    |  |  |  |

| t <sub>R4</sub>    |                                                      | 268 |     | 295 |     | 339 |     | 390 | ps |  |  |  |

| t <sub>R8</sub>    |                                                      | 371 |     | 349 |     | 401 |     | 461 | ps |  |  |  |

| t <sub>R24</sub>   |                                                      | 465 |     | 512 |     | 588 |     | 676 | ps |  |  |  |

| t <sub>C4</sub>    |                                                      | 440 |     | 484 |     | 557 |     | 641 | ps |  |  |  |

| t <sub>C8</sub>    |                                                      | 577 |     | 634 |     | 730 |     | 840 | ps |  |  |  |

| t <sub>C16</sub>   |                                                      | 445 |     | 489 |     | 563 |     | 647 | ps |  |  |  |

| t <sub>LOCAL</sub> |                                                      | 313 |     | 345 |     | 396 |     | 455 | ps |  |  |  |

Routing delays vary depending on the load on that specific routing line. The Quartus II software reports the routing delay information when running the timing analysis for a design.

Table 4–114. Stratix Maximum Input Clock Rate for CLK[7..4] & CLK[15..12] Pins in Flip-Chip Packages (Part 2 of 2)

| I/O Standard                  | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------|-------------------|-------------------|-------------------|-------------------|------|

| LVDS (1)                      | 645               | 645               | 622               | 622               | MHz  |

| HyperTransport technology (1) | 500               | 500               | 450               | 450               | MHz  |

Table 4–115. Stratix Maximum Input Clock Rate for CLK[0, 2, 9, 11] Pins & FPLL[10..7]CLK Pins in Flip-Chip Packages

| I/O Standard                  | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------|-------------------|-------------------|-------------------|-------------------|------|

| LVTTL                         | 422               | 422               | 390               | 390               | MHz  |

| 2.5 V                         | 422               | 422               | 390               | 390               | MHz  |

| 1.8 V                         | 422               | 422               | 390               | 390               | MHz  |

| 1.5 V                         | 422               | 422               | 390               | 390               | MHz  |

| LVCMOS                        | 422               | 422               | 390               | 390               | MHz  |

| GTL+                          | 300               | 250               | 200               | 200               | MHz  |

| SSTL-3 Class I                | 400               | 350               | 300               | 300               | MHz  |

| SSTL-3 Class II               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-2 Class I                | 400               | 350               | 300               | 300               | MHz  |

| SSTL-2 Class II               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-18 Class I               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-18 Class II              | 400               | 350               | 300               | 300               | MHz  |

| 1.5-V HSTL Class I            | 400               | 350               | 300               | 300               | MHz  |

| 1.8-V HSTL Class I            | 400               | 350               | 300               | 300               | MHz  |

| СТТ                           | 300               | 250               | 200               | 200               | MHz  |

| Differential 1.5-V HSTL<br>C1 | 400               | 350               | 300               | 300               | MHz  |

| LVPECL (1)                    | 717               | 717               | 640               | 640               | MHz  |

| PCML (1)                      | 400               | 375               | 350               | 350               | MHz  |

| LVDS (1)                      | 717               | 717               | 640               | 640               | MHz  |

| HyperTransport technology (1) | 717               | 717               | 640               | 640               | MHz  |

# Table 4–123. Stratix Maximum Output Clock Rate (Using I/O Pins) for PLL[1, 2, 3, 4] Pins in Wire-Bond Packages (Part 2 of 2)

| I/O Standard                  | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------|-------------------|-------------------|-------------------|------|

| LVDS (2)                      | 400               | 311               | 311               | MHz  |

| HyperTransport technology (2) | 420               | 400               | 400               | MHz  |

#### Notes to Tables 4-120 through 4-123:

- (1) Differential SSTL-2 outputs are only available on column clock pins.

- (2) These parameters are only available on row I/O pins.

- (3) SSTL-2 in maximum drive strength condition. See Table 4–101 on page 4–62 for more information on exact loading conditions for each I/O standard.

- (4) SSTL-2 in minimum drive strength with  $\leq$ 10pF output load condition.

- (5) SSTL-2 in minimum drive strength with > 10pF output load condition.

- (6) Differential SSTL-2 outputs are only supported on column clock pins.

Tables 4–131 through 4–133 describe the Stratix device fast PLL specifications.

| Symbol                             | Parameter                                                                             | Min   | Max   | Unit    |

|------------------------------------|---------------------------------------------------------------------------------------|-------|-------|---------|

| f <sub>IN</sub>                    | CLKIN frequency (1), (2), (3)                                                         | 10    | 717   | MHz     |

| f <sub>INPFD</sub>                 | Input frequency to PFD                                                                | 10    | 500   | MHz     |

| f <sub>OUT</sub>                   | Output frequency for internal global or regional clock (3)                            | 9.375 | 420   | MHz     |

| f <sub>OUT_DIFFIO</sub>            | Output frequency for external clock driven out on a differential I/O data channel (2) | (5)   | (5)   |         |

| f <sub>VCO</sub>                   | VCO operating frequency                                                               | 300   | 1,000 | MHz     |

| t <sub>INDUTY</sub>                | CLKIN duty cycle                                                                      | 40    | 60    | %       |

| t <sub>INJITTER</sub>              | Period jitter for CLKIN pin                                                           |       | ±200  | ps      |

| t <sub>DUTY</sub>                  | Duty cycle for DFFIO 1× CLKOUT pin (6)                                                | 45    | 55    | %       |

| t <sub>JITTER</sub>                | Period jitter for DIFFIO clock out (6)                                                |       | (5)   | ps      |

| t <sub>LOCK</sub>                  | Time required for PLL to acquire lock                                                 | 10    | 100   | μs      |

| m                                  | Multiplication factors for <i>m</i> counter (6)                                       | 1     | 32    | Integer |

| <i>l</i> 0, <i>l</i> 1, <i>g</i> 0 | Multiplication factors for I0, I1, and g0 counter (7), (8)                            | 1     | 32    | Integer |

| t <sub>ARESET</sub>                | Minimum pulse width on areset signal                                                  | 10    |       | ns      |

| Table 4–132. Fast PLL Specifications for -7 Speed Grades (Part 1 of 2) |                                                                                   |       |      |      |  |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------|------|------|--|

| Symbol                                                                 | Parameter                                                                         | Min   | Max  | Unit |  |

| f <sub>IN</sub>                                                        | CLKIN frequency (1), (3)                                                          | 10    | 640  | MHz  |  |

| f <sub>INPFD</sub>                                                     | Input frequency to PFD                                                            | 10    | 500  | MHz  |  |

| f <sub>OUT</sub>                                                       | Output frequency for internal global or regional clock (4)                        | 9.375 | 420  | MHz  |  |

| fout_diffio                                                            | Output frequency for external clock driven out on a differential I/O data channel | (5)   | (5)  | MHz  |  |

| f <sub>VCO</sub>                                                       | VCO operating frequency                                                           | 300   | 700  | MHz  |  |

| t <sub>INDUTY</sub>                                                    | CLKIN duty cycle                                                                  | 40    | 60   | %    |  |

| t <sub>INJITTER</sub>                                                  | Period jitter for CLKIN pin                                                       |       | ±200 | ps   |  |

| t <sub>DUTY</sub>                                                      | Duty cycle for DFFIO 1× CLKOUT pin (6)                                            | 45    | 55   | %    |  |

| Table 4–133. Fast PLL Specifications for -8 Speed Grades (Part 2 of 2) |                                      |     |     |      |  |

|------------------------------------------------------------------------|--------------------------------------|-----|-----|------|--|

| Symbol                                                                 | Parameter                            | Min | Max | Unit |  |

| t <sub>ARESET</sub>                                                    | Minimum pulse width on areset signal | 10  |     | ns   |  |

#### Notes to Tables 4–131 through 4–133:

- (1) See "Maximum Input & Output Clock Rates" on page 4–76.

- (2) PLLs 7, 8, 9, and 10 in the EP1S80 device support up to 717-MHz input and output.

- (3) Use this equation (f<sub>OUT</sub> = f<sub>IN</sub> \* ml(n × post-scale counter)) in conjunction with the specified f<sub>INPFD</sub> and f<sub>VCO</sub> ranges to determine the allowed PLL settings.

- (4) When using the SERDES, high-speed differential I/O mode supports a maximum output frequency of 210 MHz to the global or regional clocks (that is, the maximum data rate 840 Mbps divided by the smallest SERDES J factor of 4).

- (5) Refer to the section "High-Speed I/O Specification" on page 4–87 for more information.

- (6) This parameter is for high-speed differential I/O mode only.

- (7) These counters have a maximum of 32 if programmed for 50/50 duty cycle. Otherwise, they have a maximum of 16.

- (8) High-speed differential I/O mode supports W = 1 to 16 and J = 4, 7, 8, or 10.

# DLL Specifications

Table 4–134 reports the jitter for the DLL in the DQS phase shift reference circuit.

| Table 4–134. DLL Jitter for DQS Phase Shift Reference Circuit |                 |  |  |

|---------------------------------------------------------------|-----------------|--|--|

| Frequency (MHz)                                               | DLL Jitter (ps) |  |  |

| 197 to 200                                                    | ± 100           |  |  |

| 160 to 196                                                    | ± 300           |  |  |

| 100 to 159                                                    | ± 500           |  |  |

For more information on DLL jitter, see the *DDR SRAM* section in the *Stratix Architecture* chapter of the *Stratix Device Handbook, Volume 1*.

Table 4–135 lists the Stratix DLL low frequency limit for full phase shift across all PVT conditions. The Stratix DLL can be used below these frequencies, but it will not achieve the full phase shift requested across all