Welcome to **E-XFL.COM**

# **Understanding Embedded - FPGAs (Field Programmable Gate Array)**

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 4125                                                    |

| Number of Logic Elements/Cells | 41250                                                   |

| Total RAM Bits                 | 3423744                                                 |

| Number of I/O                  | 615                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                         |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 780-BBGA, FCBGA                                         |

| Supplier Device Package        | 780-FBGA (29x29)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s40f780c8 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Copyright © 2006 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published in

formation and before placing orders for products or services.

I.S. EN ISO 9001

ii Altera Corporation

viii Altera Corporation

## 1. Introduction

\$51001-3.2

### Introduction

The Stratix® family of FPGAs is based on a 1.5-V, 0.13- $\mu$ m, all-layer copper SRAM process, with densities of up to 79,040 logic elements (LEs) and up to 7.5 Mbits of RAM. Stratix devices offer up to 22 digital signal processing (DSP) blocks with up to 176 (9-bit × 9-bit) embedded multipliers, optimized for DSP applications that enable efficient implementation of high-performance filters and multipliers. Stratix devices support various I/O standards and also offer a complete clock management solution with its hierarchical clock structure with up to 420-MHz performance and up to 12 phase-locked loops (PLLs).

The following shows the main sections in the Stratix Device Family Data Sheet:

| Section                                       | Page  |

|-----------------------------------------------|-------|

| Features                                      | 1–2   |

| Functional Description                        | 2–1   |

| Logic Array Blocks                            |       |

| Logic Elements                                |       |

| MultiTrack Interconnect                       |       |

| TriMatrix Memory                              |       |

| Digital Signal Processing Block               |       |

| PLLs & Clock Networks                         |       |

| I/O Structure                                 |       |

| High-Speed Differential I/O Support           |       |

| Power Sequencing & Hot Socketing              | 2–140 |

| IEEE Std. 1149.1 (JTAG) Boundary-Scan Support | 3–1   |

| SignalTap II Embedded Logic Analyzer          |       |

| Configuration                                 |       |

| Temperature Sensing Diode                     |       |

| Operating Conditions                          | 4_1   |

| Power Consumption                             |       |

| Timing Model                                  |       |

| Software                                      | 5–1   |

| Device Pin-Outs                               |       |

| Ordering Information                          |       |

#### **Features**

The Stratix family offers the following features:

- 10,570 to 79,040 LEs; see Table 1–1

- Up to 7,427,520 RAM bits (928,440 bytes) available without reducing logic resources

- TriMatrix<sup>™</sup> memory consisting of three RAM block sizes to implement true dual-port memory and first-in first-out (FIFO) buffers

- High-speed DSP blocks provide dedicated implementation of multipliers (faster than 300 MHz), multiply-accumulate functions, and finite impulse response (FIR) filters

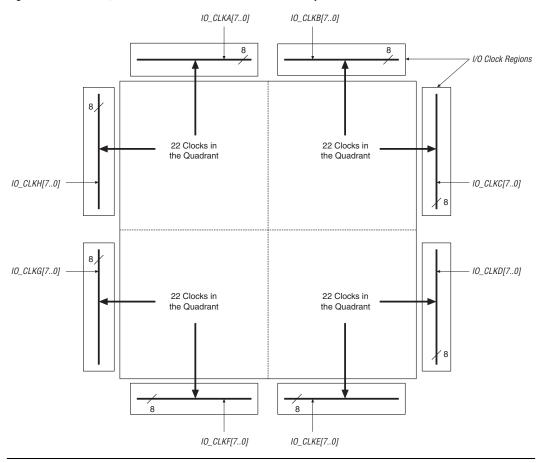

- Up to 16 global clocks with 22 clocking resources per device region

- Up to 12 PLLs (four enhanced PLLs and eight fast PLLs) per device provide spread spectrum, programmable bandwidth, clock switchover, real-time PLL reconfiguration, and advanced multiplication and phase shifting

- Support for numerous single-ended and differential I/O standards

- High-speed differential I/O support on up to 116 channels with up to 80 channels optimized for 840 megabits per second (Mbps)

- Support for high-speed networking and communications bus standards including RapidIO, UTOPIA IV, CSIX, HyperTransport™ technology, 10G Ethernet XSBI, SPI-4 Phase 2 (POS-PHY Level 4), and SFI-4

- Differential on-chip termination support for LVDS

- Support for high-speed external memory, including zero bus turnaround (ZBT) SRAM, quad data rate (QDR and QDRII) SRAM, double data rate (DDR) SDRAM, DDR fast cycle RAM (FCRAM), and single data rate (SDR) SDRAM

- Support for 66-MHz PCI (64 and 32 bit) in -6 and faster speed-grade devices, support for 33-MHz PCI (64 and 32 bit) in -8 and faster speed-grade devices

- Support for 133-MHz PCI-X 1.0 in -5 speed-grade devices

- Support for 100-MHz PCI-X 1.0 in -6 and faster speed-grade devices

- Support for 66-MHz PCI-X 1.0 in -7 speed-grade devices

- Support for multiple intellectual property megafunctions from Altera MegaCore<sup>®</sup> functions and Altera Megafunction Partners Program (AMPP<sup>SM</sup>) megafunctions

- Support for remote configuration updates

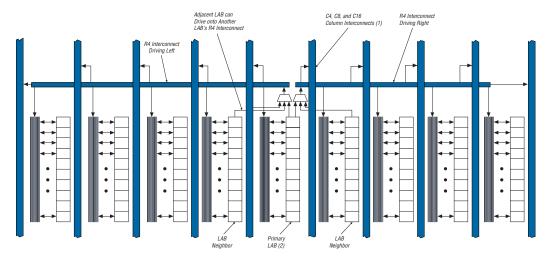

row connections in a four-LAB region. Every LAB has its own set of R4 interconnects to drive either left or right. Figure 2–9 shows R4 interconnect connections from an LAB. R4 interconnects can drive and be driven by DSP blocks and RAM blocks and horizontal IOEs. For LAB interfacing, a primary LAB or LAB neighbor can drive a given R4 interconnect. For R4 interconnects that drive to the right, the primary LAB and right neighbor can drive on to the interconnect. For R4 interconnects that drive to the left, the primary LAB and its left neighbor can drive on to the interconnects can drive other R4 interconnects to extend the range of LABs they can drive. R4 interconnects can also drive C4 and C16 interconnects for connections from one row to another. Additionally, R4 interconnects can drive R24 interconnects.

Figure 2-9. R4 Interconnect Connections

#### *Notes to Figure 2–9:*

- (1) C4 interconnects can drive R4 interconnects.

- (2) This pattern is repeated for every LAB in the LAB row.

The R8 interconnects span eight LABs, M512 or M4K RAM blocks, or DSP blocks to the right or left from a source LAB. These resources are used for fast row connections in an eight-LAB region. Every LAB has its own set of R8 interconnects to drive either left or right. R8 interconnect connections between LABs in a row are similar to the R4 connections shown in Figure 2–9, with the exception that they connect to eight LABs to the right or left, not four. Like R4 interconnects, R8 interconnects can drive and be driven by all types of architecture blocks. R8 interconnects

## TriMatrix Memory

TriMatrix memory consists of three types of RAM blocks: M512, M4K, and M-RAM blocks. Although these memory blocks are different, they can all implement various types of memory with or without parity, including true dual-port, simple dual-port, and single-port RAM, ROM, and FIFO buffers. Table 2–3 shows the size and features of the different RAM blocks.

| Table 2–3. TriMatrix Memory Features (Part 1 of 2) |                                  |                                  |                                |  |  |  |  |  |

|----------------------------------------------------|----------------------------------|----------------------------------|--------------------------------|--|--|--|--|--|

| Memory Feature                                     | M512 RAM Block<br>(32 × 18 Bits) | M4K RAM Block<br>(128 × 36 Bits) | M-RAM Block<br>(4K × 144 Bits) |  |  |  |  |  |

| Maximum performance                                | (1)                              | (1)                              | (1)                            |  |  |  |  |  |

| True dual-port memory                              |                                  | <b>✓</b>                         | <b>✓</b>                       |  |  |  |  |  |

| Simple dual-port memory                            | ✓                                | ~                                | <b>✓</b>                       |  |  |  |  |  |

| Single-port memory                                 | ✓                                | ✓                                | ✓                              |  |  |  |  |  |

| Shift register                                     | ✓                                | ✓                                |                                |  |  |  |  |  |

| ROM                                                | ✓                                | ✓                                | (2)                            |  |  |  |  |  |

| FIFO buffer                                        | ✓                                | ✓                                | ✓                              |  |  |  |  |  |

| Byte enable                                        |                                  | ✓                                | ✓                              |  |  |  |  |  |

| Parity bits                                        | ✓                                | ✓                                | ✓                              |  |  |  |  |  |

| Mixed clock mode                                   | ✓                                | ✓                                | ✓                              |  |  |  |  |  |

| Memory initialization                              | ✓                                | ✓                                |                                |  |  |  |  |  |

| Simple dual-port<br>memory mixed width<br>support  | <b>✓</b>                         | ~                                | ~                              |  |  |  |  |  |

| True dual-port memory mixed width support          |                                  | ~                                | ~                              |  |  |  |  |  |

| Power-up conditions                                | Outputs cleared                  | Outputs cleared                  | Outputs<br>unknown             |  |  |  |  |  |

| Register clears                                    | Input and output registers       | Input and output registers       | Output registers               |  |  |  |  |  |

| Mixed-port read-<br>during-write                   | Unknown<br>output/old data       | Unknown<br>output/old data       | Unknown output                 |  |  |  |  |  |

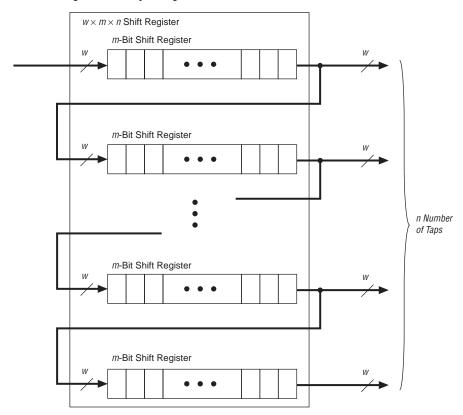

Figure 2-14. Shift Register Memory Configuration

## **Memory Block Size**

TriMatrix memory provides three different memory sizes for efficient application support. The large number of M512 blocks are ideal for designs with many shallow first-in first-out (FIFO) buffers. M4K blocks provide additional resources for channelized functions that do not require large amounts of storage. The M-RAM blocks provide a large single block of RAM ideal for data packet storage. The different-sized blocks allow Stratix devices to efficiently support variable-sized memory in designs.

The Quartus II software automatically partitions the user-defined memory into the embedded memory blocks using the most efficient size combinations. You can also manually assign the memory to a specific block size or a mixture of block sizes.

Table 2–13 shows the number of DSP blocks in each Stratix device.

| Table 2–13. DSP Blocks in Stratix Devices Notes (1), (2) |            |                            |                              |                              |  |  |  |  |  |

|----------------------------------------------------------|------------|----------------------------|------------------------------|------------------------------|--|--|--|--|--|

| Device                                                   | DSP Blocks | Total 9 × 9<br>Multipliers | Total 18 × 18<br>Multipliers | Total 36 × 36<br>Multipliers |  |  |  |  |  |

| EP1S10                                                   | 6          | 48                         | 24                           | 6                            |  |  |  |  |  |

| EP1S20                                                   | 10         | 80                         | 40                           | 10                           |  |  |  |  |  |

| EP1S25                                                   | 10         | 80                         | 40                           | 10                           |  |  |  |  |  |

| EP1S30                                                   | 12         | 96                         | 48                           | 12                           |  |  |  |  |  |

| EP1S40                                                   | 14         | 112                        | 56                           | 14                           |  |  |  |  |  |

| EP1S60                                                   | 18         | 144                        | 72                           | 18                           |  |  |  |  |  |

| EP1S80                                                   | 22         | 176                        | 88                           | 22                           |  |  |  |  |  |

#### *Notes to Table 2–13:*

- (1) Each device has either the number of  $9 \times 9$ -,  $18 \times 18$ -, or  $36 \times 36$ -bit multipliers shown. The total number of multipliers for each device is not the sum of all the multipliers.

- (2) The number of supported multiply functions shown is based on signed/signed or unsigned/unsigned implementations.

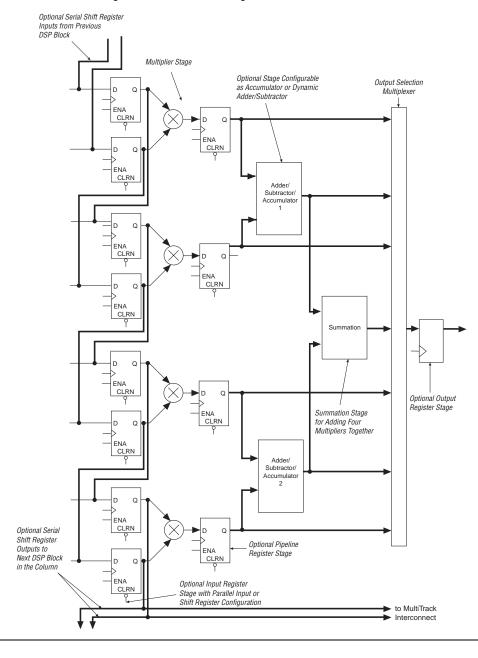

DSP block multipliers can optionally feed an adder/subtractor or accumulator within the block depending on the configuration. This makes routing to LEs easier, saves LE routing resources, and increases performance, because all connections and blocks are within the DSP block. Additionally, the DSP block input registers can efficiently implement shift registers for FIR filter applications.

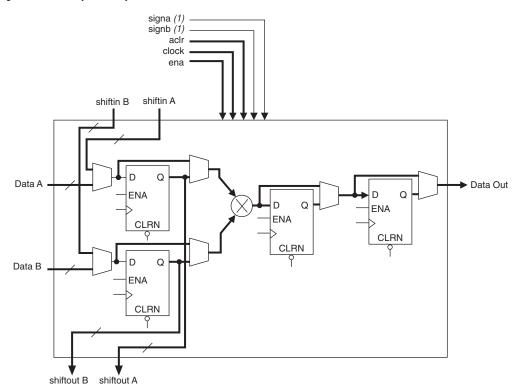

Figure 2–30 shows the top-level diagram of the DSP block configured for  $18 \times 18$ -bit multiplier mode. Figure 2–31 shows the  $9 \times 9$ -bit multiplier configuration of the DSP block.

Figure 2–30. DSP Block Diagram for 18 imes 18-Bit Configuration

Figure 2-35. Simple Multiplier Mode

*Note to Figure 2–35:*

(1) These signals are not registered or registered once to match the data path pipeline.

DSP blocks can also implement one  $36 \times 36$ -bit multiplier in multiplier mode. DSP blocks use four  $18 \times 18$ -bit multipliers combined with dedicated adder and internal shift circuitry to achieve 36-bit multiplication. The input shift register feature is not available for the  $36 \times 36$ -bit multiplier. In  $36 \times 36$ -bit mode, the device can use the register that is normally a multiplier-result-output register as a pipeline stage for the  $36 \times 36$ -bit multiplier. Figure 2–36 shows the  $36 \times 36$ -bit multiply mode.

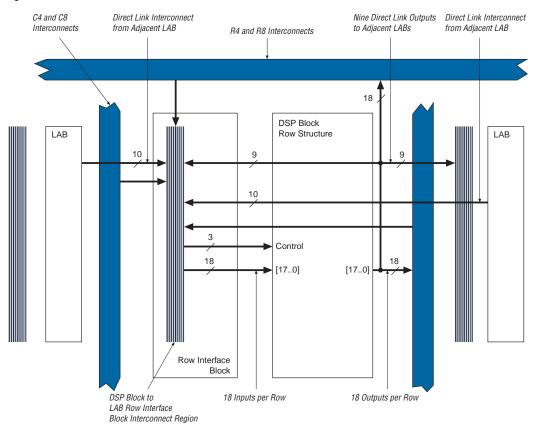

Figure 2-41. DSP Block Interface to Interconnect

A bus of 18 control signals feeds the entire DSP block. These signals include clock[0..3] clocks, aclr[0..3] asynchronous clears, ena[1..4] clock enables, signa, signb signed/unsigned control signals, addnsub1 and addnsub3 addition and subtraction control signals, and accum sload[0..1] accumulator synchronous loads. The

Figure 2-47. EP1S10, EP1S20 & EP1S25 Device I/O Clock Groups

VCO period from up to eight taps for individual fine step selection. Also, each clock output counter can use a unique initial count setting to achieve individual coarse shift selection in steps of one VCO period. The combination of coarse and fine shifts allows phase shifting for the entire input clock period.

The equation to determine the precision of the phase shifting in degrees is:  $45^{\circ}$  ÷ post-scale counter value. Therefore, the maximum step size is  $45^{\circ}$ , and smaller steps are possible depending on the multiplication and division ratio necessary on the output counter port.

This type of phase shift provides the highest precision since it is the least sensitive to process, supply, and temperature variation.

#### **Clock Delay**

In addition to the phase shift feature, the ability to fine tune the  $\Delta t$  clock delay provides advanced time delay shift control on each of the four PLL outputs. There are time delays for each post-scale counter (e, g, or l) from the PLL, the n counter, and m counter. Each of these can shift in 250-ps increments for a range of 3.0 ns. The m delay shifts all outputs earlier in time, while n delay shifts all outputs later in time. Individual delays on post-scale counters (e, g, and l) provide positive delay for each output. Table 2–21 shows the combined delay for each output for normal or zero delay buffer mode where  $\Delta t_e$ ,  $\Delta t_o$ , or  $\Delta t_l$  is unique for each PLL output.

The  $t_{OUTPUT}$  for a single output can range from -3 ns to +6 ns. The total delay shift difference between any two PLL outputs, however, must be less than  $\pm 3$  ns. For example, shifts on two outputs of -1 and +2 ns is allowed, but not -1 and +2.5 ns because these shifts would result in a difference of 3.5 ns. If the design uses external feedback, the  $\Delta t_e$  delay will remove delay from outputs, represented by a negative sign (see Table 2–21). This effect occurs because the  $\Delta t_e$  delay is then part of the feedback loop.

| Table 2–21. Output Clock Delay for Enhanced PLLs                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Normal or Zero Delay Buffer Mode                                                                                                                                                                                                                                | External Feedback Mode                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| $\begin{split} \Delta t_{e \text{OUTPUT}} &= \Delta t_n - \!\!\! \Delta t_m + \Delta t_e \\ \Delta t_{g \text{OUTPUT}} &= \Delta t_n - \!\!\! \Delta t_m + \Delta t_g \\ \Delta t_{l \text{OUTPUT}} &= \Delta t_n - \!\!\! \Delta t_m + \Delta t_l \end{split}$ | $\begin{split} \Delta \mathbf{t}_{\text{OUTPUT}} &= \Delta \mathbf{t}_{n} - \Delta \mathbf{t}_{m} - \Delta \mathbf{t}_{e} \ (1) \\ \Delta \mathbf{t}_{\text{gOUTPUT}} &= \Delta \mathbf{t}_{n} - \Delta \mathbf{t}_{m} + \Delta \mathbf{t}_{g} \\ \Delta \mathbf{t}_{\text{DUTPUT}} &= \Delta \mathbf{t}_{n} - \Delta \mathbf{t}_{m} + \Delta \mathbf{t}_{l} \end{split}$ |  |  |  |  |  |

Note to Table 2-21:

(1)  $\Delta t_e$  removes delay from outputs in external feedback mode.

The variation due to process, voltage, and temperature is about ±15% on the delay settings. PLL reconfiguration can control the clock delay shift elements, but not the VCO phase shift multiplexers, during system operation.

#### Spread-Spectrum Clocking

Stratix device enhanced PLLs use spread-spectrum technology to reduce electromagnetic interference generation from a system by distributing the energy over a broader frequency range. The enhanced PLL typically provides 0.5% down spread modulation using a triangular profile. The modulation frequency is programmable. Enabling spread-spectrum for a PLL affects all of its outputs.

#### Lock Detect

The lock output indicates that there is a stable clock output signal in phase with the reference clock. Without any additional circuitry, the lock signal may toggle as the PLL begins tracking the reference clock. You may need to gate the lock signal for use as a system control. The lock signal from the locked port can drive the logic array or an output pin.

Whenever the PLL loses lock (for example, inclk jitter, clock switchover, PLL reconfiguration, power supply noise, and so on), the PLL must be reset with the areset signal to guarantee correct phase relationship between the PLL output clocks. If the phase relationship between the input clock versus output clock, and between different output clocks from the PLL is not important in the design, then the PLL need not be reset.

See the *Stratix FPGA Errata Sheet* for more information on implementing the gated lock signal in a design.

#### Programmable Duty Cycle

The programmable duty cycle allows enhanced PLLs to generate clock outputs with a variable duty cycle. This feature is supported on each enhanced PLL post-scale counter (*g*0..*g*3, *l*0..*l*3, *e*0..*e*3). The duty cycle setting is achieved by a low and high time count setting for the post-scale dividers. The Quartus II software uses the frequency input and the required multiply or divide rate to determine the duty cycle choices.

#### Advanced Clear & Enable Control

There are several control signals for clearing and enabling PLLs and their outputs. You can use these signals to control PLL resynchronization and gate PLL output clocks for low-power applications.

| Table 2- | Table 2–37. EP1S10, EP1S20 & EP1S25 Device Differential Channels (Part 2 of 2) Note (1) |                 |          |                 |                  |       |    |       |  |  |  |

|----------|-----------------------------------------------------------------------------------------|-----------------|----------|-----------------|------------------|-------|----|-------|--|--|--|

|          |                                                                                         | Transmitter/    | Total    | Maximum         | Center Fast PLLs |       |    |       |  |  |  |

| Device   | Package                                                                                 | Receiver        | Channels | Speed<br>(Mbps) | PLL 1            | PLL 2 |    | PLL 4 |  |  |  |

| EP1S25   | 672-pin FineLine BGA                                                                    | Transmitter (2) | 56       | 624 (4)         | 14               | 14    | 14 | 14    |  |  |  |

|          | 672-pin BGA                                                                             |                 |          | 624 (3)         | 28               | 28    | 28 | 28    |  |  |  |

|          |                                                                                         | Receiver        | 58       | 624 (4)         | 14               | 15    | 15 | 14    |  |  |  |

|          |                                                                                         |                 |          | 624 (3)         | 29               | 29    | 29 | 29    |  |  |  |

|          | 780-pin FineLine BGA                                                                    | Transmitter (2) | 70       | 840 (4)         | 18               | 17    | 17 | 18    |  |  |  |

|          |                                                                                         |                 |          | 840 (3)         | 35               | 35    | 35 | 35    |  |  |  |

|          |                                                                                         | Receiver        | 66       | 840 (4)         | 17               | 16    | 16 | 17    |  |  |  |

|          |                                                                                         |                 |          | 840 (3)         | 33               | 33    | 33 | 33    |  |  |  |

|          | 1,020-pin FineLine                                                                      | Transmitter (2) | 78       | 840 (4)         | 19               | 20    | 20 | 19    |  |  |  |

|          | BGA                                                                                     |                 |          | 840 (3)         | 39               | 39    | 39 | 39    |  |  |  |

|          |                                                                                         | Receiver        | 78       | 840 (4)         | 19               | 20    | 20 | 19    |  |  |  |

|          |                                                                                         |                 |          | 840 (3)         | 39               | 39    | 39 | 39    |  |  |  |

#### Notes to Table 2–37:

- (1) The first row for each transmitter or receiver reports the number of channels driven directly by the PLL. The second row below it shows the maximum channels a PLL can drive if cross bank channels are used from the adjacent center PLL. For example, in the 484-pin FineLine BGA EP1S10 device, PLL 1 can drive a maximum of five channels at 840 Mbps or a maximum of 10 channels at 840 Mbps. The Quartus II software may also merge receiver and transmitter PLLs when a receiver is driving a transmitter. In this case, one fast PLL can drive both the maximum numbers of receiver and transmitter channels.

- (2) The number of channels listed includes the transmitter clock output (tx\_outclock) channel. If the design requires a DDR clock, it can use an extra data channel.

- (3) These channels span across two I/O banks per side of the device. When a center PLL clocks channels in the opposite bank on the same side of the device it is called cross-bank PLL support. Both center PLLs can clock cross-bank channels simultaneously if, for example, PLL\_1 is clocking all receiver channels and PLL\_2 is clocking all transmitter channels. You cannot have two adjacent PLLs simultaneously clocking cross-bank receiver channels or two adjacent PLLs simultaneously clocking transmitter channels. Cross-bank allows for all receiver channels on one side of the device to be clocked on one clock while all transmitter channels on the device are clocked on the other center PLL. Crossbank PLLs are supported at full-speed, 840 Mbps. For wire-bond devices, the full-speed is 624 Mbps.

- (4) These values show the channels available for each PLL without crossing another bank.

When you span two I/O banks using cross-bank support, you can route only two load enable signals total between the PLLs. When you enable rx\_data\_align, you use both rxloadena and txloadena of a PLL. That leaves no loadena for the second PLL.

| Table 4–9. Overshoot Input Voltage with Respect to Duty Cycle (Part 2 of 2) |                        |  |  |  |  |  |

|-----------------------------------------------------------------------------|------------------------|--|--|--|--|--|

| Vin (V)                                                                     | Maximum Duty Cycle (%) |  |  |  |  |  |

| 4.3                                                                         | 30                     |  |  |  |  |  |

| 4.4                                                                         | 17                     |  |  |  |  |  |

| 4.5                                                                         | 10                     |  |  |  |  |  |

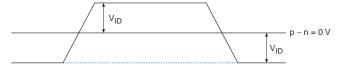

Figures 4–1 and 4–2 show receiver input and transmitter output waveforms, respectively, for all differential I/O standards (LVDS, 3.3-V PCML, LVPECL, and HyperTransport technology).

Figure 4-1. Receiver Input Waveforms for Differential I/O Standards

# Single-Ended Waveform Positive Channel (p) = $V_{IH}$ Negative Channel (n) = $V_{IL}$

#### **Differential Waveform**

| Table 4–20. SSTL-2 Class I Specifications |                             |                                |                         |           |                         |      |  |  |  |

|-------------------------------------------|-----------------------------|--------------------------------|-------------------------|-----------|-------------------------|------|--|--|--|

| Symbol                                    | Parameter                   | Conditions                     | Minimum                 | Typical   | Maximum                 | Unit |  |  |  |

| $V_{\text{CCIO}}$                         | Output supply voltage       |                                | 2.375                   | 2.5       | 2.625                   | ٧    |  |  |  |

| $V_{TT}$                                  | Termination voltage         |                                | V <sub>REF</sub> - 0.04 | $V_{REF}$ | V <sub>REF</sub> + 0.04 | V    |  |  |  |

| $V_{REF}$                                 | Reference voltage           |                                | 1.15                    | 1.25      | 1.35                    | ٧    |  |  |  |

| V <sub>IH(DC)</sub>                       | High-level DC input voltage |                                | V <sub>REF</sub> + 0.18 |           | 3.0                     | V    |  |  |  |

| V <sub>IL(DC)</sub>                       | Low-level DC input voltage  |                                | -0.3                    |           | V <sub>REF</sub> – 0.18 | ٧    |  |  |  |

| V <sub>IH(AC)</sub>                       | High-level AC input voltage |                                | V <sub>REF</sub> + 0.35 |           |                         | V    |  |  |  |

| V <sub>IL(AC)</sub>                       | Low-level AC input voltage  |                                |                         |           | V <sub>REF</sub> - 0.35 | V    |  |  |  |

| V <sub>OH</sub>                           | High-level output voltage   | $I_{OH} = -8.1 \text{ mA}$ (3) | V <sub>TT</sub> + 0.57  |           |                         | V    |  |  |  |

| V <sub>OL</sub>                           | Low-level output voltage    | I <sub>OL</sub> = 8.1 mA (3)   |                         |           | V <sub>TT</sub> – 0.57  | ٧    |  |  |  |

| Table 4–21          | Table 4–21. SSTL-2 Class II Specifications |                                 |                         |           |                         |      |  |  |  |  |  |

|---------------------|--------------------------------------------|---------------------------------|-------------------------|-----------|-------------------------|------|--|--|--|--|--|

| Symbol              | Parameter                                  | Conditions                      | Minimum                 | Typical   | Maximum                 | Unit |  |  |  |  |  |

| V <sub>CCIO</sub>   | Output supply voltage                      |                                 | 2.375                   | 2.5       | 2.625                   | ٧    |  |  |  |  |  |

| V <sub>TT</sub>     | Termination voltage                        |                                 | V <sub>REF</sub> - 0.04 | $V_{REF}$ | V <sub>REF</sub> + 0.04 | V    |  |  |  |  |  |

| V <sub>REF</sub>    | Reference voltage                          |                                 | 1.15                    | 1.25      | 1.35                    | V    |  |  |  |  |  |

| V <sub>IH(DC)</sub> | High-level DC input voltage                |                                 | V <sub>REF</sub> + 0.18 |           | V <sub>CCIO</sub> + 0.3 | V    |  |  |  |  |  |

| V <sub>IL(DC)</sub> | Low-level DC input voltage                 |                                 | -0.3                    |           | V <sub>REF</sub> – 0.18 | V    |  |  |  |  |  |

| V <sub>IH(AC)</sub> | High-level AC input voltage                |                                 | V <sub>REF</sub> + 0.35 |           |                         | V    |  |  |  |  |  |

| V <sub>IL(AC)</sub> | Low-level AC input voltage                 |                                 |                         |           | V <sub>REF</sub> – 0.35 | V    |  |  |  |  |  |

| V <sub>OH</sub>     | High-level output voltage                  | $I_{OH} = -16.4 \text{ mA}$ (3) | V <sub>TT</sub> + 0.76  |           |                         | V    |  |  |  |  |  |

| V <sub>OL</sub>     | Low-level output voltage                   | I <sub>OL</sub> = 16.4 mA (3)   |                         |           | V <sub>TT</sub> – 0.76  | V    |  |  |  |  |  |

| Table 4–22. SSTL-3 Class I Specifications (Part 1 of 2) |                             |            |                         |           |                         |      |  |  |  |  |

|---------------------------------------------------------|-----------------------------|------------|-------------------------|-----------|-------------------------|------|--|--|--|--|

| Symbol                                                  | Parameter                   | Conditions | Minimum                 | Typical   | Maximum                 | Unit |  |  |  |  |

| V <sub>CCIO</sub>                                       | Output supply voltage       |            | 3.0                     | 3.3       | 3.6                     | V    |  |  |  |  |

| V <sub>TT</sub>                                         | Termination voltage         |            | V <sub>REF</sub> - 0.05 | $V_{REF}$ | V <sub>REF</sub> + 0.05 | V    |  |  |  |  |

| V <sub>REF</sub>                                        | Reference voltage           |            | 1.3                     | 1.5       | 1.7                     | V    |  |  |  |  |

| V <sub>IH(DC)</sub>                                     | High-level DC input voltage |            | V <sub>REF</sub> + 0.2  |           | V <sub>CCIO</sub> + 0.3 | V    |  |  |  |  |

| V <sub>IL(DC)</sub>                                     | Low-level DC input voltage  |            | -0.3                    |           | V <sub>REF</sub> - 0.2  | V    |  |  |  |  |

| V <sub>IH(AC)</sub>                                     | High-level AC input voltage |            | V <sub>REF</sub> + 0.4  |           |                         | V    |  |  |  |  |

| Table 4–105. Stratix I/O Standard Output Delay Adders for Fast Slew Rate on Column Pins (Part 2 of 2) |         |          |                |       |                |       |                |       |      |

|-------------------------------------------------------------------------------------------------------|---------|----------|----------------|-------|----------------|-------|----------------|-------|------|

| Dt                                                                                                    | -5 Spee | ed Grade | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | T    |

| Parameter                                                                                             | Min     | Max      | Min            | Max   | Min            | Max   | Min            | Max   | Unit |

| CTT                                                                                                   |         | 973      |                | 1,021 |                | 1,021 |                | 1,021 | ps   |

| SSTL-3 Class I                                                                                        |         | 719      |                | 755   |                | 755   |                | 755   | ps   |

| SSTL-3 Class II                                                                                       |         | 146      |                | 153   |                | 153   |                | 153   | ps   |

| SSTL-2 Class I                                                                                        |         | 678      |                | 712   |                | 712   |                | 712   | ps   |

| SSTL-2 Class II                                                                                       |         | 223      |                | 234   |                | 234   |                | 234   | ps   |

| SSTL-18 Class I                                                                                       |         | 1,032    |                | 1,083 |                | 1,083 |                | 1,083 | ps   |

| SSTL-18 Class II                                                                                      |         | 447      |                | 469   |                | 469   |                | 469   | ps   |

| 1.5-V HSTL Class I                                                                                    |         | 660      |                | 693   |                | 693   |                | 693   | ps   |

| 1.5-V HSTL Class II                                                                                   |         | 537      |                | 564   |                | 564   |                | 564   | ps   |

| 1.8-V HSTL Class I                                                                                    |         | 304      |                | 319   |                | 319   |                | 319   | ps   |

| 1.8-V HSTL Class II                                                                                   |         | 231      |                | 242   |                | 242   |                | 242   | ps   |

| Table 4–106. Stratix I/O Standard Output Delay Adders for Fast Slew Rate on Row Pins (Part 1 of 2) |                |     |         |                |       |                |       |                |       | 2)   |

|----------------------------------------------------------------------------------------------------|----------------|-----|---------|----------------|-------|----------------|-------|----------------|-------|------|

| Рокото                                                                                             | -5 Speed Grade |     | -6 Spee | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       |      |

| Parameter                                                                                          |                | Min | Max     | Min            | Max   | Min            | Max   | Min            | Max   | Unit |

| LVCMOS                                                                                             | 2 mA           |     | 1,518   |                | 1,594 |                | 1,594 |                | 1,594 | ps   |

|                                                                                                    | 4 mA           |     | 746     |                | 783   |                | 783   |                | 783   | ps   |

|                                                                                                    | 8 mA           |     | 96      |                | 100   |                | 100   |                | 100   | ps   |

|                                                                                                    | 12 mA          |     | 0       |                | 0     |                | 0     |                | 0     | ps   |

| 3.3-V LVTTL                                                                                        | 4 mA           |     | 1,518   |                | 1,594 |                | 1,594 |                | 1,594 | ps   |

|                                                                                                    | 8 mA           |     | 1,038   |                | 1,090 |                | 1,090 |                | 1,090 | ps   |

|                                                                                                    | 12 mA          |     | 521     |                | 547   |                | 547   |                | 547   | ps   |

|                                                                                                    | 16 mA          |     | 414     |                | 434   |                | 434   |                | 434   | ps   |

|                                                                                                    | 24 mA          |     | 0       |                | 0     |                | 0     |                | 0     | ps   |

| 2.5-V LVTTL                                                                                        | 2 mA           |     | 2,032   |                | 2,133 |                | 2,133 |                | 2,133 | ps   |

|                                                                                                    | 8 mA           |     | 699     |                | 734   |                | 734   |                | 734   | ps   |

|                                                                                                    | 12 mA          |     | 374     |                | 392   |                | 392   |                | 392   | ps   |

|                                                                                                    | 16 mA          |     | 165     |                | 173   |                | 173   |                | 173   | ps   |

| 1.8-V LVTTL                                                                                        | 2 mA           |     | 3,714   |                | 3,899 |                | 3,899 |                | 3,899 | ps   |

|                                                                                                    | 8 mA           |     | 1,055   |                | 1,107 |                | 1,107 |                | 1,107 | ps   |

|                                                                                                    | 12 mA          |     | 830     |                | 871   |                | 871   |                | 871   | ps   |

## Index

| A                                        | Open-Drain Output 2–120                     |

|------------------------------------------|---------------------------------------------|

| Accumulator 2–63                         | Power Sequencing & Hot Socketing 2–140      |

| Adder/Output Blocks 2–61                 | Programmable Drive Strength 2–119           |

| Adder/Subtractor                         | Programmable Pull-Up Resistor 2–122         |

| 2–63                                     | Simple Multiplier Mode 2–64                 |

| Accumulator                              | Single-Port Mode 2–51                       |

| 2–63                                     | Slew-Rate Control 2–120                     |

| AGP 1x Specifications 4–13               | Two-Multipliers                             |

| AGP 2x Specifications 4–13               | Adder Mode 2–67                             |

| Architecture 2–1                         | Adder Mode Implementing Complex             |

| 36 x 36 Multiply Mode 2–66               | Multiply 2–68                               |

| addnsub Signal 2–8                       |                                             |

| Block Diagram 2–2                        | C                                           |

| Bus Hold 2–121                           |                                             |

| Byte Alignment 2–140                     | Class I Specifications 4–11, 4–12           |

| Carry-Select Chain 2–11                  | Class II Specifications 4–11, 4–12, 4–13    |

| Clear & Preset Logic Control 2–13        | Clocks                                      |

| Combined Resources 2–78                  | Clock Feedback 2–96                         |

| Dedicated Circuitry 2–137                | Clock Multiplication & Division 2–88, 2–101 |

| Device Resources 2–3                     | Clock Switchover                            |

| Device Routing Scheme 2–20               | 2–88                                        |

| Digital Signal Processing Block 2–52     | Delay 2–97                                  |

| Direct Link Connection 2–5               | EP1S10, EP1S20 & EP1S25                     |

| Dynamic Arithmetic Mode 2–10             | Device I/O Clock Groups                     |

| in LE 2–11                               | 2–80                                        |

| Four-Multipliers                         | EP1S25, EP1S20 & EP1S10 Device Fast Clock   |

| Adder Mode 2–68                          | Pin Connections to Fast Regional            |

| Functional Description 2–1               | Clocks 2–77                                 |

| LAB                                      | EP1S30 Device Fast Regional Clock Pin Con-  |

| Interconnects 2–4                        | nections to Fast Regional Clocks 2–78       |

| Logic Array Blocks 2–3                   | EP1S30, EP1S40, EP1S60, EP1S80              |

| Structure 2–4                            | Device I/O Clock Groups                     |

| LE Operating Modes 2–8                   | 2–81                                        |

| Logic Elements 2–6                       | External Clock                              |

| Modes of Operation 2–64                  | Inputs 2–102                                |

| Multiplier Size & Configurations per DSP | Outputs 2–92, 2–103                         |

| block 2–70                               | Outputs for Enhanced PLLs 11 & 12 2–95      |

| Multiply-Accumulator Mode 2–67           | Outputs for PLLs 5 & 6 2–93                 |

| MultiTrack Interconnect 2–14             | Fast Regional Clock External I/O Timing     |

| Normal Mode 2–9                          | Parameters 4–34                             |

| in I F 2_0                               | Fast Regional Clock Network 2–76            |

Altera Corporation Index-1

| Differential HSTL Specifications 4–15<br>DSP        | Parameters 4–39<br>Row Pin                         |

|-----------------------------------------------------|----------------------------------------------------|

| Block Diagram                                       | Fast Regional Clock External I/O Timing            |

| Configuration                                       | Parameters 4–40                                    |

| for 18 x 18-Bit 2–55                                | Global Clock External I/O Timing                   |

| for 9 x 9-Bit 2–56                                  | Parameters 4–41                                    |

| Block Interconnect Interface 2–71                   | Regional Clock External I/O Timing                 |

| Block Interface 2–70                                | Parameters 4–41                                    |

| Block Signal Sources & Destinations 2–73            | EP1S25 Devices                                     |

| Blocks                                              | Column Pin                                         |

| Arranged in Columns 2–53                            | Fast Regional Clock External I/O Timing            |

| in Stratix Devices 2–54                             | Parameters 4–42                                    |

| Input Register Modes 2-60                           | Global Clock External I/O Timing                   |

| Input Registers 2–58                                | Parameters 4–43                                    |

| Multiplier                                          | Regional Clock External I/O Timing                 |

| 2–60                                                | Parameters 4–42                                    |

| Block 2–57                                          | Row Pin                                            |

| Signed Representation 2-60                          | Fast Regional Clock External I/O Timing            |

| Sub-Block 2–57                                      | Parameters 4–43                                    |

| Sub-Blocks Using Input Shift Register               | Global Clock External I/O Timing                   |

| Connections 2–59                                    | Parameters 4–44                                    |

| Pipeline/Post Multiply Register 2–61                | Regional Clock External I/O Timing                 |

|                                                     | Parameters 4–44                                    |

| E                                                   | EP1S30 Devices                                     |

| <b>L</b>                                            | Column Pin                                         |

| EP1S10 Devices                                      | Fast Regional Clock External I/O Timing            |

| Column Pin                                          | Parameters 4–45                                    |

| Fast Regional Clock External I/O Timing             | Global Clock External I/O Timing                   |

| Parameters 4–36                                     | Parameters 4–45                                    |

| Global Clock External I/O Timing<br>Parameters 4–37 | Regional Clock External I/O Timing Parameters 4–45 |

| Regional Clock External I/O Timing                  | Row Pin                                            |

| Parameters 4–36                                     | Fast Regional Clock External I/O Timing            |

| Row Pin                                             | Parameters 4–46                                    |

| Fast Regional Clock External I/O Timing             | Global Clock External I/O Timing                   |

| Parameters 4–37                                     | Parameters 4–47                                    |

| Global Clock External I/O Timing                    | Regional Clock External I/O Timing                 |

| Parameters 4–38                                     | Parameters 4–47                                    |

| Regional Clock External I/O Timing                  | EP1S40 Devices                                     |

| Parameters 4–38                                     | Column Pin                                         |

| EP1S20 Devices                                      | Fast Regional Clock External I/O Timing            |

| Column Pin                                          | Parameters 4–48                                    |

| Fast Regional Clock External I/O Timing             | Global Clock External I/O Timing                   |

| Parameters 4–39                                     | Parameters 4–49                                    |

| Global Clock External I/O Timing                    | Regional Clock External I/O Timing                 |

| Parameters 4–40                                     | Parameters 4–48                                    |

| Regional Clock External I/O Timing                  | Row Pin                                            |

Altera Corporation Index-3