Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 4125                                                     |

| Number of Logic Elements/Cells | 41250                                                    |

| Total RAM Bits                 | 3423744                                                  |

| Number of I/O                  | 615                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 780-BBGA, FCBGA                                          |

| Supplier Device Package        | 780-FBGA (29x29)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s40f780c8n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Introduction

\$51001-3.2

# Introduction

The Stratix® family of FPGAs is based on a 1.5-V, 0.13- $\mu$ m, all-layer copper SRAM process, with densities of up to 79,040 logic elements (LEs) and up to 7.5 Mbits of RAM. Stratix devices offer up to 22 digital signal processing (DSP) blocks with up to 176 (9-bit × 9-bit) embedded multipliers, optimized for DSP applications that enable efficient implementation of high-performance filters and multipliers. Stratix devices support various I/O standards and also offer a complete clock management solution with its hierarchical clock structure with up to 420-MHz performance and up to 12 phase-locked loops (PLLs).

The following shows the main sections in the Stratix Device Family Data Sheet:

| Section                                       | Page  |

|-----------------------------------------------|-------|

| Features                                      | 1–2   |

| Functional Description                        | 2–1   |

| Logic Array Blocks                            |       |

| Logic Elements                                |       |

| MultiTrack Interconnect                       |       |

| TriMatrix Memory                              |       |

| Digital Signal Processing Block               |       |

| PLLs & Clock Networks                         |       |

| I/O Structure                                 |       |

| High-Speed Differential I/O Support           |       |

| Power Sequencing & Hot Socketing              | 2–140 |

| IEEE Std. 1149.1 (JTAG) Boundary-Scan Support | 3–1   |

| SignalTap II Embedded Logic Analyzer          |       |

| Configuration                                 |       |

| Temperature Sensing Diode                     |       |

| Operating Conditions                          | 4_1   |

| Power Consumption                             |       |

| Timing Model                                  |       |

| Software                                      | 5–1   |

| Device Pin-Outs                               |       |

| Ordering Information                          |       |

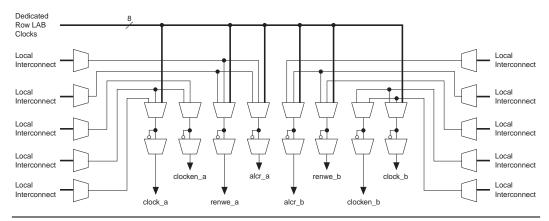

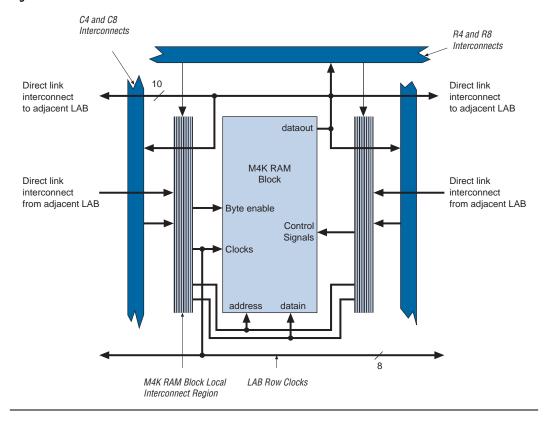

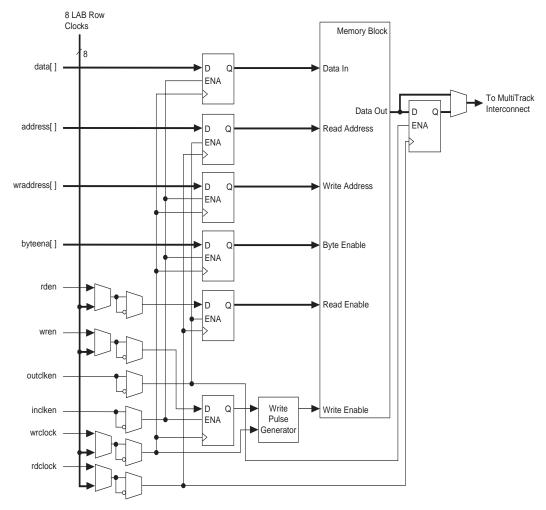

Figure 2-17. M4K RAM Block Control Signals

Figure 2-18. M4K RAM Block LAB Row Interface

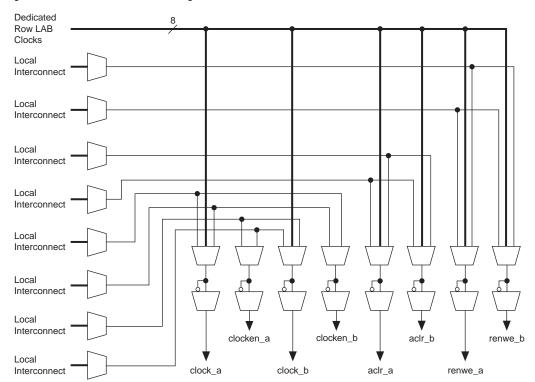

Figure 2-19. M-RAM Block Control Signals

One of the M-RAM block's horizontal sides drive the address and control signal (clock, renwe, byteena, etc.) inputs. Typically, the horizontal side closest to the device perimeter contains the interfaces. The one exception is when two M-RAM blocks are paired next to each other. In this case, the side of the M-RAM block opposite the common side of the two blocks contains the input interface. The top and bottom sides of any M-RAM block contain data input and output interfaces to the logic array. The top side has 72 data inputs and 72 data outputs for port B, and the bottom side has another 72 data inputs and 72 data outputs for port A. Figure 2–20 shows an example floorplan for the EP1S60 device and the location of the M-RAM interfaces.

Figure 2-27. Read/Write Clock Mode in Simple Dual-Port Mode Notes (1), (2)

### Notes to Figure 2-27:

- (1) All registers shown except the rden register have asynchronous clear ports.

- (2) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

Table 2–13 shows the number of DSP blocks in each Stratix device.

| Table 2–13. DSP Blocks in Stratix Devices Notes (1), (2) |            |                            |                              |                              |  |  |  |  |  |  |

|----------------------------------------------------------|------------|----------------------------|------------------------------|------------------------------|--|--|--|--|--|--|

| Device                                                   | DSP Blocks | Total 9 × 9<br>Multipliers | Total 18 × 18<br>Multipliers | Total 36 × 36<br>Multipliers |  |  |  |  |  |  |

| EP1S10                                                   | 6          | 48                         | 24                           | 6                            |  |  |  |  |  |  |

| EP1S20                                                   | 10         | 80                         | 40                           | 10                           |  |  |  |  |  |  |

| EP1S25                                                   | 10         | 80                         | 40                           | 10                           |  |  |  |  |  |  |

| EP1S30                                                   | 12         | 96                         | 48                           | 12                           |  |  |  |  |  |  |

| EP1S40                                                   | 14         | 112                        | 56                           | 14                           |  |  |  |  |  |  |

| EP1S60                                                   | 18         | 144                        | 72                           | 18                           |  |  |  |  |  |  |

| EP1S80                                                   | 22         | 176                        | 88                           | 22                           |  |  |  |  |  |  |

#### *Notes to Table 2–13:*

- (1) Each device has either the number of  $9 \times 9$ -,  $18 \times 18$ -, or  $36 \times 36$ -bit multipliers shown. The total number of multipliers for each device is not the sum of all the multipliers.

- (2) The number of supported multiply functions shown is based on signed/signed or unsigned/unsigned implementations.

DSP block multipliers can optionally feed an adder/subtractor or accumulator within the block depending on the configuration. This makes routing to LEs easier, saves LE routing resources, and increases performance, because all connections and blocks are within the DSP block. Additionally, the DSP block input registers can efficiently implement shift registers for FIR filter applications.

Figure 2–30 shows the top-level diagram of the DSP block configured for  $18 \times 18$ -bit multiplier mode. Figure 2–31 shows the  $9 \times 9$ -bit multiplier configuration of the DSP block.

## Input Registers

A bank of optional input registers is located at the input of each multiplier and multiplicand inputs to the multiplier. When these registers are configured for parallel data inputs, they are driven by regular routing resources. You can use a clock signal, asynchronous clear signal, and a clock enable signal to independently control each set of A and B inputs for each multiplier in the DSP block. You select these control signals from a set of four different clock [3..0], aclr[3..0], and ena[3..0] signals that drive the entire DSP block.

You can also configure the input registers for a shift register application. In this case, the input registers feed the multiplier and drive two dedicated shift output lines:  $\mathtt{shiftoutA}$  and  $\mathtt{shiftoutB}$ . The shift outputs of one multiplier block directly feed the adjacent multiplier block in the same DSP block (or the next DSP block) as shown in Figure 2–33, to form a shift register chain. This chain can terminate in any block, that is, you can create any length of shift register chain up to 224 registers. You can use the input shift registers for FIR filter applications. One set of shift inputs can provide data for a filter, and the other are coefficients that are optionally loaded in serial or parallel. When implementing  $9 \times 9$ - and  $18 \times 18$ -bit multipliers, you do not need to implement external shift registers in LAB LEs. You implement all the filter circuitry within the DSP block and its routing resources, saving LE and general routing resources for general logic. External registers are needed for shift register inputs when using  $36 \times 36$ -bit multipliers.

Accumulator Feedback accum\_sload0 (2) Result A ■ overflow0 Adder/ Subtractor/ addnsub1 (2) Accumulator1 Output Selection Multiplexer Result B signa (2) Summation Output signb (2) Register Block Result C Adder/ addnsub3 (2) Subtractor/ Accumulator2 overflow1 Result D accum\_sload1 (2) Accumulator Feedback

Figure 2–34. Adder/Output Blocks Note (1)

## Notes to Figure 2–34:

- (1) Adder/output block shown in Figure 2–34 is in 18 × 18-bit mode. In 9 × 9-bit mode, there are four adder/subtractor blocks and two summation blocks.

- (2) These signals are either not registered, registered once, or registered twice to match the data path pipeline.

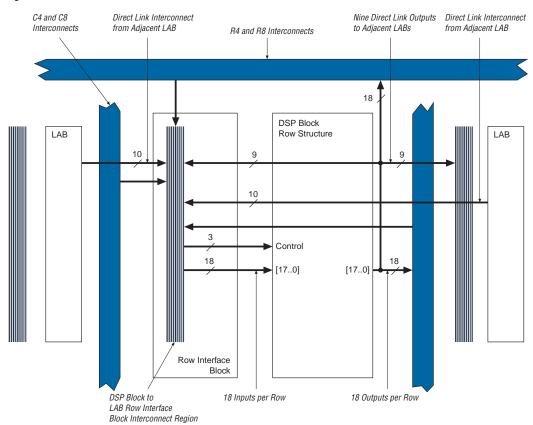

The DSP block is divided into eight block units that interface with eight LAB rows on the left and right. Each block unit can be considered half of an 18 × 18-bit multiplier sub-block with 18 inputs and 18 outputs. A local interconnect region is associated with each DSP block. Like an LAB, this interconnect region can be fed with 10 direct link interconnects from the LAB to the left or right of the DSP block in the same row. All row and column routing resources can access the DSP block's local interconnect region. The outputs also work similarly to LAB outputs as well. Nine outputs from the DSP block can drive to the left LAB through direct link interconnects and nine can drive to the right LAB though direct link interconnects. All 18 outputs can drive to all types of row and column routing. Outputs can drive right- or left-column routing. Figures 2–40 and 2–41 show the DSP block interfaces to LAB rows.

DSP Block OA[17..0] MultiTrack MultiTrack Interconnect \ Interconnect A1[17..0] OB[17..0] B1[17..0] OC[17..0] A2[17..0] OD[17..0] B2[17..0] OE[17..0] A3[17..0] OF[17..0] B3[17..0] OG[17..0] A4[17..0] OH[17..0] ►B4[17..0]

Figure 2-40. DSP Block Interconnect Interface

Figure 2-41. DSP Block Interface to Interconnect

A bus of 18 control signals feeds the entire DSP block. These signals include clock[0..3] clocks, aclr[0..3] asynchronous clears, ena[1..4] clock enables, signa, signb signed/unsigned control signals, addnsub1 and addnsub3 addition and subtraction control signals, and accum sload[0..1] accumulator synchronous loads. The

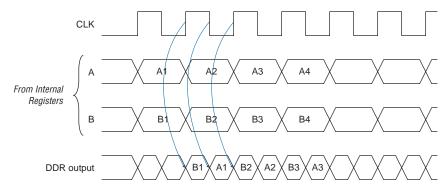

Figure 2-68. Output Timing Diagram in DDR Mode

The Stratix IOE operates in bidirectional DDR mode by combining the DDR input and DDR output configurations. Stratix device I/O pins transfer data on a DDR bidirectional bus to support DDR SDRAM. The negative-edge-clocked OE register holds the OE signal inactive until the falling edge of the clock. This is done to meet DDR SDRAM timing requirements.

# **External RAM Interfacing**

Stratix devices support DDR SDRAM at up to 200 MHz (400-Mbps data rate) through dedicated phase-shift circuitry, QDR and QDRII SRAM interfaces up to 167 MHz, and ZBT SRAM interfaces up to 200 MHz. Stratix devices also provide preliminary support for reduced latency DRAM II (RLDRAM II) at rates up to 200 MHz through the dedicated phase-shift circuitry.

In addition to the required signals for external memory interfacing, Stratix devices offer the optional clock enable signal. By default the Quartus II software sets the clock enable signal high, which tells the output register to update with new values. The output registers hold their own values if the design sets the clock enable signal low. See Figure 2–64.

To find out more about the DDR SDRAM specification, see the JEDEC web site (www.jedec.org). For information on memory controller megafunctions for Stratix devices, see the Altera web site (www.altera.com). See AN 342: Interfacing DDR SDRAM with Stratix & Stratix GX Devices for more information on DDR SDRAM interface in Stratix. Also see AN 349: QDR SRAM Controller Reference Design for Stratix & Stratix GX Devices and AN 329: ZBT SRAM Controller Reference Design for Stratix & Stratix GX Devices.

| Table 2–26. External RAM Support in EP1S60 & EP1S80 Devices |              |                |                          |                |  |  |  |  |  |

|-------------------------------------------------------------|--------------|----------------|--------------------------|----------------|--|--|--|--|--|

| DDD Momory Type                                             | I/O Standard | Maxii          | Maximum Clock Rate (MHz) |                |  |  |  |  |  |

| DDR Memory Type                                             | I/O Standard | -5 Speed Grade | -6 Speed Grade           | -7 Speed Grade |  |  |  |  |  |

| DDR SDRAM (1), (2)                                          | SSTL-2       | 167            | 167                      | 133            |  |  |  |  |  |

| DDR SDRAM - side banks (2), (3)                             | SSTL-2       | 150            | 133                      | 133            |  |  |  |  |  |

| QDR SRAM (4)                                                | 1.5-V HSTL   | 133            | 133                      | 133            |  |  |  |  |  |

| QDRII SRAM (4)                                              | 1.5-V HSTL   | 167            | 167                      | 133            |  |  |  |  |  |

| ZBT SRAM (5)                                                | LVTTL        | 200            | 200                      | 167            |  |  |  |  |  |

#### Notes to Table 2-26:

- (1) These maximum clock rates apply if the Stratix device uses DQS phase-shift circuitry to interface with DDR SDRAM. DQS phase-shift circuitry is only available in the top and bottom I/O banks (I/O banks 3, 4, 7, and 8).

- (2) For more information on DDR SDRAM, see AN 342: Interfacing DDR SDRAM with Stratix & Stratix GX Devices.

- (3) DDR SDRAM is supported on the Stratix device side I/O banks (I/O banks 1, 2, 5, and 6) without dedicated DQS phase-shift circuitry. The read DQS signal is ignored in this mode. Numbers are preliminary.

- (4) For more information on QDR or QDRII SRAM, see AN 349: QDR SRAM Controller Reference Design for Stratix & Stratix GX Devices.

- (5) For more information on ZBT SRAM, see AN 329: ZBT SRAM Controller Reference Design for Stratix & Stratix GX Devices.

In addition to six I/O registers and one input latch in the IOE for interfacing to these high-speed memory interfaces, Stratix devices also have dedicated circuitry for interfacing with DDR SDRAM. In every Stratix device, the I/O banks at the top (I/O banks 3 and 4) and bottom (I/O banks 7 and 8) of the device support DDR SDRAM up to 200 MHz. These pins support DQS signals with DQ bus modes of  $\times 8$ ,  $\times 16$ , or  $\times 32$ .

Table 2–27 shows the number of DQ and DQS buses that are supported per device.

| Table 2–27. DQS & DQ Bus Mode Support (Part 1 of 2) Note (1) |                                              |                        |                         |                         |  |  |  |  |  |

|--------------------------------------------------------------|----------------------------------------------|------------------------|-------------------------|-------------------------|--|--|--|--|--|

| Device                                                       | Package                                      | Number of ×8<br>Groups | Number of ×16<br>Groups | Number of ×32<br>Groups |  |  |  |  |  |

| EP1S10                                                       | 672-pin BGA<br>672-pin FineLine BGA          | 12 (2)                 | 0                       | 0                       |  |  |  |  |  |

|                                                              | 484-pin FineLine BGA<br>780-pin FineLine BGA | 16 (3)                 | 0                       | 4                       |  |  |  |  |  |

| EP1S20                                                       | 484-pin FineLine BGA                         | 18(4)                  | 7 (5)                   | 4                       |  |  |  |  |  |

|                                                              | 672-pin BGA<br>672-pin FineLine BGA          | 16(3)                  | 7 (5)                   | 4                       |  |  |  |  |  |

|                                                              | 780-pin FineLine BGA                         | 20                     | 7 (5)                   | 4                       |  |  |  |  |  |

- 1.8-V HSTL Class I and II

- SSTL-3 Class I and II

- SSTL-2 Class I and II

- SSTL-18 Class I and II

- CTT

Table 2–31 describes the I/O standards supported by Stratix devices.

| Table 2–31. Stratix Supported I/O Standards |                    |                                                       |                                                      |                                                           |  |  |  |  |

|---------------------------------------------|--------------------|-------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------|--|--|--|--|

| I/O Standard                                | Туре               | Input Reference<br>Voltage (V <sub>REF</sub> )<br>(V) | Output Supply<br>Voltage (V <sub>CCIO</sub> )<br>(V) | Board<br>Termination<br>Voltage (V <sub>TT</sub> )<br>(V) |  |  |  |  |

| LVTTL                                       | Single-ended       | N/A                                                   | 3.3                                                  | N/A                                                       |  |  |  |  |

| LVCMOS                                      | Single-ended       | N/A                                                   | 3.3                                                  | N/A                                                       |  |  |  |  |

| 2.5 V                                       | Single-ended       | N/A                                                   | 2.5                                                  | N/A                                                       |  |  |  |  |

| 1.8 V                                       | Single-ended       | N/A                                                   | 1.8                                                  | N/A                                                       |  |  |  |  |

| 1.5 V                                       | Single-ended       | N/A                                                   | 1.5                                                  | N/A                                                       |  |  |  |  |

| 3.3-V PCI                                   | Single-ended       | N/A                                                   | 3.3                                                  | N/A                                                       |  |  |  |  |

| 3.3-V PCI-X 1.0                             | Single-ended       | N/A                                                   | 3.3                                                  | N/A                                                       |  |  |  |  |

| LVDS                                        | Differential       | N/A                                                   | 3.3                                                  | N/A                                                       |  |  |  |  |

| LVPECL                                      | Differential       | N/A                                                   | 3.3                                                  | N/A                                                       |  |  |  |  |

| 3.3-V PCML                                  | Differential       | N/A                                                   | 3.3                                                  | N/A                                                       |  |  |  |  |

| HyperTransport                              | Differential       | N/A                                                   | 2.5                                                  | N/A                                                       |  |  |  |  |

| Differential HSTL (1)                       | Differential       | 0.75                                                  | 1.5                                                  | 0.75                                                      |  |  |  |  |

| Differential SSTL (2)                       | Differential       | 1.25                                                  | 2.5                                                  | 1.25                                                      |  |  |  |  |

| GTL                                         | Voltage-referenced | 0.8                                                   | N/A                                                  | 1.20                                                      |  |  |  |  |

| GTL+                                        | Voltage-referenced | 1.0                                                   | N/A                                                  | 1.5                                                       |  |  |  |  |

| 1.5-V HSTL Class I and II                   | Voltage-referenced | 0.75                                                  | 1.5                                                  | 0.75                                                      |  |  |  |  |

| 1.8-V HSTL Class I and II                   | Voltage-referenced | 0.9                                                   | 1.8                                                  | 0.9                                                       |  |  |  |  |

| SSTL-18 Class I and II                      | Voltage-referenced | 0.90                                                  | 1.8                                                  | 0.90                                                      |  |  |  |  |

| SSTL-2 Class I and II                       | Voltage-referenced | 1.25                                                  | 2.5                                                  | 1.25                                                      |  |  |  |  |

| SSTL-3 Class I and II                       | Voltage-referenced | 1.5                                                   | 3.3                                                  | 1.5                                                       |  |  |  |  |

| AGP (1× and 2°)                             | Voltage-referenced | 1.32                                                  | 3.3                                                  | N/A                                                       |  |  |  |  |

| CTT                                         | Voltage-referenced | 1.5                                                   | 3.3                                                  | 1.5                                                       |  |  |  |  |

#### Notes to Table 2–31:

- (1) This I/O standard is only available on input and output clock pins.

- (2) This I/O standard is only available on output column clock pins.

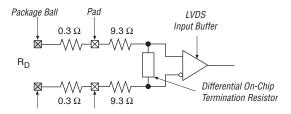

However, there is additional resistance present between the device ball and the input of the receiver buffer, as shown in Figure 2–72. This resistance is because of package trace resistance (which can be calculated as the resistance from the package ball to the pad) and the parasitic layout metal routing resistance (which is shown between the pad and the intersection of the on-chip termination and input buffer).

Figure 2-72. Differential Resistance of LVDS Differential Pin Pair (Rp)

Table 2–35 defines the specification for internal termination resistance for commercial devices.

| Table 2–35. Differential On-Chip Termination |                                            |                     |         |     |     |      |  |  |  |  |

|----------------------------------------------|--------------------------------------------|---------------------|---------|-----|-----|------|--|--|--|--|

| Cumbal                                       | Description                                | Conditions          | Resista |     | ce  | Hnit |  |  |  |  |

| Symbol                                       | Description                                | Collations          | Min     | Тур | Max | Unit |  |  |  |  |

| R <sub>D</sub> (2)                           | Internal differential termination for LVDS | Commercial (1), (3) | 110     | 135 | 165 | W    |  |  |  |  |

|                                              |                                            | Industrial (2), (3) | 100     | 135 | 170 | W    |  |  |  |  |

Notes to Table 2-35:

- (1) Data measured over minimum conditions ( $T_j = 0 \text{ C}$ ,  $V_{\text{CCIO}} + 5\%$ ) and maximum conditions ( $T_j = 85 \text{ C}$ ,  $V_{\text{CCIO}} = -5\%$ ).

- (2) Data measured over minimum conditions ( $T_j = -40$  C,  $V_{CCIO} + 5\%$ ) and maximum conditions ( $T_j = 100$  C,  $V_{CCIO} = -5\%$ ).

- (3) LVDS data rate is supported for 840 Mbps using internal differential termination.

## MultiVolt I/O Interface

The Stratix architecture supports the MultiVolt I/O interface feature, which allows Stratix devices in all packages to interface with systems of different supply voltages.

The Stratix VCCINT pins must always be connected to a 1.5-V power supply. With a 1.5-V  $V_{CCINT}$  level, input pins are 1.5-V, 1.8-V, 2.5-V, and 3.3-V tolerant. The VCCIO pins can be connected to either a 1.5-V, 1.8-V, 2.5-V, or 3.3-V power supply, depending on the output requirements.

| Table 2- | Table 2–37. EP1S10, EP1S20 & EP1S25 Device Differential Channels (Part 2 of 2) Note (1) |                 |          |                 |                  |       |       |       |  |  |

|----------|-----------------------------------------------------------------------------------------|-----------------|----------|-----------------|------------------|-------|-------|-------|--|--|

|          |                                                                                         | Transmitter/    | Total    | Maximum         | Center Fast PLLs |       |       |       |  |  |

| Device   | Package                                                                                 | Receiver        | Channels | Speed<br>(Mbps) | PLL 1            | PLL 2 | PLL 3 | PLL 4 |  |  |

| EP1S25   | 672-pin FineLine BGA                                                                    | Transmitter (2) | 56       | 624 (4)         | 14               | 14    | 14    | 14    |  |  |

|          | 672-pin BGA                                                                             |                 |          | 624 (3)         | 28               | 28    | 28    | 28    |  |  |

|          |                                                                                         | Receiver        | er 58    | 624 (4)         | 14               | 15    | 15    | 14    |  |  |

|          |                                                                                         |                 |          | 624 (3)         | 29               | 29    | 29    | 29    |  |  |

|          | 780-pin FineLine BGA                                                                    | Transmitter (2) | 70       | 840 (4)         | 18               | 17    | 17    | 18    |  |  |

|          |                                                                                         |                 |          | 840 (3)         | 35               | 35    | 35    | 35    |  |  |

|          |                                                                                         | Receiver        | 66       | 840 (4)         | 17               | 16    | 16    | 17    |  |  |

|          |                                                                                         |                 |          | 840 (3)         | 33               | 33    | 33    | 33    |  |  |

|          | 1,020-pin FineLine                                                                      | Transmitter (2) | 78       | 840 (4)         | 19               | 20    | 20    | 19    |  |  |

|          | BGA                                                                                     |                 |          | 840 (3)         | 39               | 39    | 39    | 39    |  |  |

|          |                                                                                         | Receiver        | 78       | 840 (4)         | 19               | 20    | 20    | 19    |  |  |

|          |                                                                                         |                 |          | 840 (3)         | 39               | 39    | 39    | 39    |  |  |

#### Notes to Table 2–37:

- (1) The first row for each transmitter or receiver reports the number of channels driven directly by the PLL. The second row below it shows the maximum channels a PLL can drive if cross bank channels are used from the adjacent center PLL. For example, in the 484-pin FineLine BGA EP1S10 device, PLL 1 can drive a maximum of five channels at 840 Mbps or a maximum of 10 channels at 840 Mbps. The Quartus II software may also merge receiver and transmitter PLLs when a receiver is driving a transmitter. In this case, one fast PLL can drive both the maximum numbers of receiver and transmitter channels.

- (2) The number of channels listed includes the transmitter clock output (tx\_outclock) channel. If the design requires a DDR clock, it can use an extra data channel.

- (3) These channels span across two I/O banks per side of the device. When a center PLL clocks channels in the opposite bank on the same side of the device it is called cross-bank PLL support. Both center PLLs can clock cross-bank channels simultaneously if, for example, PLL\_1 is clocking all receiver channels and PLL\_2 is clocking all transmitter channels. You cannot have two adjacent PLLs simultaneously clocking cross-bank receiver channels or two adjacent PLLs simultaneously clocking transmitter channels. Cross-bank allows for all receiver channels on one side of the device to be clocked on one clock while all transmitter channels on the device are clocked on the other center PLL. Crossbank PLLs are supported at full-speed, 840 Mbps. For wire-bond devices, the full-speed is 624 Mbps.

- (4) These values show the channels available for each PLL without crossing another bank.

When you span two I/O banks using cross-bank support, you can route only two load enable signals total between the PLLs. When you enable rx\_data\_align, you use both rxloadena and txloadena of a PLL. That leaves no loadena for the second PLL.

| Symbol                  | Parameter                                                                   | Conditions                                                                                 | Minimum | Typical | Maximum | Unit |

|-------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------|---------|---------|------|

| V <sub>ICM</sub>        | Input common mode voltage (6)                                               | LVDS<br>$0.3 \text{ V} \leq \text{V}_{\text{ID}} \leq 1.0 \text{ V}$<br>W = 1  through  10 | 100     |         | 1,100   | mV   |

|                         |                                                                             | LVDS<br>$0.3 \text{ V} \leq V_{\text{ID}} \leq 1.0 \text{ V}$<br>W = 1  through  10        | 1,600   | ,       | mV      |      |

|                         |                                                                             | LVDS<br>0.2 V ≤V <sub>ID</sub> ≤1.0 V<br>W = 1                                             | 1,100   |         | 1,600   | mV   |

|                         |                                                                             | LVDS<br>$0.1 \text{ V} \leq V_{\text{ID}} \leq 1.0 \text{ V}$<br>W = 2  through  10        | 1,100   |         | 1,600   | mV   |

| V <sub>OD</sub> (1)     | Output differential voltage (single-ended)                                  | R <sub>L</sub> = 100 Ω                                                                     | 250     | 375     | 550     | mV   |

| Δ V <sub>OD</sub>       | Change in V <sub>OD</sub> between high and low                              | R <sub>L</sub> = 100 Ω                                                                     |         |         | 50      | mV   |

| V <sub>OCM</sub>        | Output common mode voltage                                                  | $R_L = 100 \Omega$                                                                         | 1,125   | 1,200   | 1,375   | mV   |

| $\Delta V_{\text{OCM}}$ | Change in V <sub>OCM</sub> between high and low                             | $R_L = 100 \Omega$                                                                         |         |         | 50      | mV   |

| R <sub>L</sub>          | Receiver differential input discrete resistor (external to Stratix devices) |                                                                                            | 90      | 100     | 110     | Ω    |

|                    | Table 4–43. Routing Delay Internal Timing Microparameter<br>Descriptions (Part 2 of 2)                                                         |  |  |  |  |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Symbol             | Parameter                                                                                                                                      |  |  |  |  |  |  |  |  |

| t <sub>C4</sub>    | Delay for a C4 line with average loading; covers a distance of four LAB rows.                                                                  |  |  |  |  |  |  |  |  |

| t <sub>C8</sub>    | Delay for a C8 line with average loading; covers a distance of eight LAB rows.                                                                 |  |  |  |  |  |  |  |  |

| t <sub>C16</sub>   | Delay for a C16 line with average loading; covers a distance of 16 LAB rows.                                                                   |  |  |  |  |  |  |  |  |

| t <sub>LOCAL</sub> | Local interconnect delay, for connections within a LAB, and for the final routing hop of connections to LABs, DSP blocks, RAM blocks and I/Os. |  |  |  |  |  |  |  |  |

| Table 4–44. LE Internal Timing Microparameters |      |     |      |     |      |     |      |     |      |  |

|------------------------------------------------|------|-----|------|-----|------|-----|------|-----|------|--|

| Dozomotov                                      | -5   |     | -6   |     | -7   |     | -8   |     | 11-4 |  |

| Parameter                                      | Min  | Max | Min  | Max | Min  | Max | Min  | Max | Unit |  |

| t <sub>SU</sub>                                | 10   |     | 10   |     | 11   |     | 13   |     | ps   |  |

| t <sub>H</sub>                                 | 100  |     | 100  |     | 114  |     | 135  |     | ps   |  |

| t <sub>CO</sub>                                |      | 156 |      | 176 |      | 202 |      | 238 | ps   |  |

| t <sub>LUT</sub>                               |      | 366 |      | 459 |      | 527 |      | 621 | ps   |  |

| t <sub>CLR</sub>                               | 100  |     | 100  |     | 114  |     | 135  |     | ps   |  |

| t <sub>PRE</sub>                               | 100  |     | 100  |     | 114  |     | 135  |     | ps   |  |

| t <sub>CLKHL</sub>                             | 1000 |     | 1111 |     | 1190 |     | 1400 |     | ps   |  |

| Table 4–45. IOE Internal TSU Microparameter by Device Density (Part 1 of 2) |                   |     |     |     |     |     |     |     |     |    |

|-----------------------------------------------------------------------------|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|----|

| Device                                                                      | Symbol            | -5  |     | -   | -6  |     | -7  |     | -8  |    |

|                                                                             |                   | Min | Max | Min | Max | Min | Max | Min | Max |    |

| EP1S10                                                                      | t <sub>SU_R</sub> | 76  |     | 80  |     | 80  |     | 80  |     | ps |

|                                                                             | t <sub>SU_C</sub> | 176 |     | 80  |     | 80  |     | 80  |     | ps |

| EP1S20                                                                      | t <sub>SU_R</sub> | 76  |     | 80  |     | 80  |     | 80  |     | ps |

|                                                                             | t <sub>SU_C</sub> | 76  |     | 80  |     | 80  |     | 80  |     | ps |

| EP1S25                                                                      | t <sub>SU_R</sub> | 276 |     | 280 |     | 280 |     | 280 |     | ps |

|                                                                             | t <sub>SU_C</sub> | 276 |     | 280 |     | 280 |     | 280 |     | ps |

| EP1S30                                                                      | t <sub>SU_R</sub> | 76  |     | 80  |     | 80  |     | 80  |     | ps |

|                                                                             | t <sub>SU_C</sub> | 176 |     | 180 |     | 180 |     | 180 |     | ps |

Table 4–52 shows the external I/O timing parameters when using fast regional clock networks.

| <b>Table 4–52. Stratix Fast Regional Clock External I/O Timing Parameters</b> Notes (1), (2) |                                                                                                                      |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Symbol                                                                                       | Parameter                                                                                                            |  |  |  |  |  |  |  |

| t <sub>INSU</sub>                                                                            | Setup time for input or bidirectional pin using IOE input register with fast regional clock fed by FCLK pin          |  |  |  |  |  |  |  |

| t <sub>INH</sub>                                                                             | Hold time for input or bidirectional pin using IOE input register with fast regional clock fed by FCLK pin           |  |  |  |  |  |  |  |

| t <sub>outco</sub>                                                                           | Clock-to-output delay output or bidirectional pin using IOE output register with fast regional clock fed by FCLK pin |  |  |  |  |  |  |  |

| t <sub>XZ</sub>                                                                              | Synchronous IOE output enable register to output pin disable delay using fast regional clock fed by FCLK pin         |  |  |  |  |  |  |  |

| t <sub>ZX</sub>                                                                              | Synchronous IOE output enable register to output pin enable delay using fast regional clock fed by FCLK pin          |  |  |  |  |  |  |  |

Notes to Table 4-52:

- (1) These timing parameters are sample-tested only.

- (2) These timing parameters are for column and row IOE pins. You should use the Quartus II software to verify the external timing for any pin.

Table 4–53 shows the external I/O timing parameters when using regional clock networks.

| Symbol                | Parameter                                                                                                                               |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>INSU</sub>     | Setup time for input or bidirectional pin using IOE input register with regional clock fed by CLK pin                                   |

| t <sub>INH</sub>      | Hold time for input or bidirectional pin using IOE input register with regional clock fed by CLK pin                                    |

| t <sub>OUTCO</sub>    | Clock-to-output delay output or bidirectional pin using IOE output register with regional clock fed by CLK pin                          |

| t <sub>INSUPLL</sub>  | Setup time for input or bidirectional pin using IOE input register with regional clock fed by Enhanced PLL with default phase setting   |

| t <sub>INHPLL</sub>   | Hold time for input or bidirectional pin using IOE input register with regional clock fed by Enhanced PLL with default phase setting    |

| t <sub>OUTCOPLL</sub> | Clock-to-output delay output or bidirectional pin using IOE output register with regional clock Enhanced PLL with default phase setting |

# Stratix External I/O Timing

These timing parameters are for both column IOE and row IOE pins. In EP1S30 devices and above, you can decrease the  $t_{SU}$  time by using the FPLLCLK, but may get positive hold time in EP1S60 and EP1S80 devices. You should use the Quartus II software to verify the external devices for any pin.

Tables 4–55 through 4–60 show the external timing parameters on column and row pins for EP1S10 devices.

| Table 4–55. EP1S10 External I/O Timing on Column Pins Using Fast Regional Clock Networks Note (1) |                |       |                |       |                |       |                |     |      |

|---------------------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-----|------|

| Parameter                                                                                         | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |     |      |

|                                                                                                   | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max | Unit |

| t <sub>INSU</sub>                                                                                 | 2.238          |       | 2.325          |       | 2.668          |       | NA             |     | ns   |

| t <sub>INH</sub>                                                                                  | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns   |

| t <sub>OUTCO</sub>                                                                                | 2.240          | 4.549 | 2.240          | 4.836 | 2.240          | 5.218 | NA             | NA  | ns   |

| t <sub>XZ</sub>                                                                                   | 2.180          | 4.423 | 2.180          | 4.704 | 2.180          | 5.094 | NA             | NA  | ns   |

| t <sub>ZX</sub>                                                                                   | 2.180          | 4.423 | 2.180          | 4.704 | 2.180          | 5.094 | NA             | NA  | ns   |

| Table 4–56. EP1S10 External I/O Timing on Column Pins Using Regional Clock Networks Note (1) |                |       |                |       |         |         |                |    |      |

|----------------------------------------------------------------------------------------------|----------------|-------|----------------|-------|---------|---------|----------------|----|------|

| Parameter                                                                                    | -5 Speed Grade |       | -6 Speed Grade |       | -7 Spee | d Grade | -8 Speed Grade |    |      |

|                                                                                              | Min            | Max   | Min            | Max   | Min     | Max     |                |    | Unit |

| t <sub>INSU</sub>                                                                            | 1.992          |       | 2.054          |       | 2.359   |         | NA             |    | ns   |

| t <sub>INH</sub>                                                                             | 0.000          |       | 0.000          |       | 0.000   |         | NA             |    | ns   |

| t <sub>оитсо</sub>                                                                           | 2.395          | 4.795 | 2.395          | 5.107 | 2.395   | 5.527   | NA             | NA | ns   |

| t <sub>XZ</sub>                                                                              | 2.335          | 4.669 | 2.335          | 4.975 | 2.335   | 5.403   | NA             | NA | ns   |

| t <sub>ZX</sub>                                                                              | 2.335          | 4.669 | 2.335          | 4.975 | 2.335   | 5.403   | NA             | NA | ns   |

| t <sub>INSUPLL</sub>                                                                         | 0.975          |       | 0.985          |       | 1.097   |         | NA             |    | ns   |

| t <sub>INHPLL</sub>                                                                          | 0.000          |       | 0.000          |       | 0.000   |         | NA             | NA | ns   |

| t <sub>OUTCOPLL</sub>                                                                        | 1.262          | 2.636 | 1.262          | 2.680 | 1.262   | 2.769   | NA             | NA | ns   |

| t <sub>XZPLL</sub>                                                                           | 1.202          | 2.510 | 1.202          | 2.548 | 1.202   | 2.645   | NA             | NA | ns   |

| t <sub>ZXPLL</sub>                                                                           | 1.202          | 2.510 | 1.202          | 2.548 | 1.202   | 2.645   | NA             | NA | ns   |

| Table 4–105. Stratix I/O Standard Output Delay Adders for Fast Slew Rate on Column Pins (Part 2 of 2) |                |       |                |       |                |       |                |       |      |

|-------------------------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-------|------|

| Dt                                                                                                    | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       |      |

| Parameter                                                                                             | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max   | Unit |

| CTT                                                                                                   |                | 973   |                | 1,021 |                | 1,021 |                | 1,021 | ps   |

| SSTL-3 Class I                                                                                        |                | 719   |                | 755   |                | 755   |                | 755   | ps   |

| SSTL-3 Class II                                                                                       |                | 146   |                | 153   |                | 153   |                | 153   | ps   |

| SSTL-2 Class I                                                                                        |                | 678   |                | 712   |                | 712   |                | 712   | ps   |

| SSTL-2 Class II                                                                                       |                | 223   |                | 234   |                | 234   |                | 234   | ps   |

| SSTL-18 Class I                                                                                       |                | 1,032 |                | 1,083 |                | 1,083 |                | 1,083 | ps   |

| SSTL-18 Class II                                                                                      |                | 447   |                | 469   |                | 469   |                | 469   | ps   |

| 1.5-V HSTL Class I                                                                                    |                | 660   |                | 693   |                | 693   |                | 693   | ps   |

| 1.5-V HSTL Class II                                                                                   |                | 537   |                | 564   |                | 564   |                | 564   | ps   |

| 1.8-V HSTL Class I                                                                                    |                | 304   |                | 319   |                | 319   |                | 319   | ps   |

| 1.8-V HSTL Class II                                                                                   |                | 231   |                | 242   |                | 242   |                | 242   | ps   |

| Table 4–106. Stratix I/O Standard Output Delay Adders for Fast Slew Rate on Row Pins (Part 1 of 2) |       |                |       |                |       |                |       |                |       |      |

|----------------------------------------------------------------------------------------------------|-------|----------------|-------|----------------|-------|----------------|-------|----------------|-------|------|

| Parameter                                                                                          |       | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | 11:4 |

|                                                                                                    |       | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max   | Unit |

| LVCMOS                                                                                             | 2 mA  |                | 1,518 |                | 1,594 |                | 1,594 |                | 1,594 | ps   |

|                                                                                                    | 4 mA  |                | 746   |                | 783   |                | 783   |                | 783   | ps   |

|                                                                                                    | 8 mA  |                | 96    |                | 100   |                | 100   |                | 100   | ps   |

|                                                                                                    | 12 mA |                | 0     |                | 0     |                | 0     |                | 0     | ps   |

| 3.3-V LVTTL                                                                                        | 4 mA  |                | 1,518 |                | 1,594 |                | 1,594 |                | 1,594 | ps   |

|                                                                                                    | 8 mA  |                | 1,038 |                | 1,090 |                | 1,090 |                | 1,090 | ps   |

|                                                                                                    | 12 mA |                | 521   |                | 547   |                | 547   |                | 547   | ps   |

|                                                                                                    | 16 mA |                | 414   |                | 434   |                | 434   |                | 434   | ps   |

|                                                                                                    | 24 mA |                | 0     |                | 0     |                | 0     |                | 0     | ps   |

| 2.5-V LVTTL                                                                                        | 2 mA  |                | 2,032 |                | 2,133 |                | 2,133 |                | 2,133 | ps   |

|                                                                                                    | 8 mA  |                | 699   |                | 734   |                | 734   |                | 734   | ps   |

|                                                                                                    | 12 mA |                | 374   |                | 392   |                | 392   |                | 392   | ps   |

|                                                                                                    | 16 mA |                | 165   |                | 173   |                | 173   |                | 173   | ps   |

| 1.8-V LVTTL                                                                                        | 2 mA  |                | 3,714 |                | 3,899 |                | 3,899 |                | 3,899 | ps   |

|                                                                                                    | 8 mA  |                | 1,055 |                | 1,107 |                | 1,107 |                | 1,107 | ps   |

|                                                                                                    | 12 mA |                | 830   |                | 871   |                | 871   |                | 871   | ps   |

| Fast Regional Clock External I/O Timing            | I                                                           |

|----------------------------------------------------|-------------------------------------------------------------|

| Parameters 4–49                                    | I/O                                                         |

| Global Clock External I/O Timing                   | Standards                                                   |

| Parameters 4–50 Regional Clock External I/O Timing | 1.5-V 4-14, 4-15                                            |

| Parameters 4–50                                    | I/O Specifications 4–4                                      |

| EP1S60 Devices                                     | 1.8-V                                                       |

| Column Pin                                         | I/O Specifications 4–4                                      |

| Fast Regional Clock External I/O Timing            | 2.5-V                                                       |

| Parameters 4–51                                    | I/O Specifications 4–3                                      |

| Global Clock External I/O Timing                   | 3.3-V 4–13                                                  |

| Parameters 4–52                                    | LVDS I/O Specifications 4–6                                 |

| Regional Clock External I/O Timing                 | PCI Specifications 4–9                                      |

| Parameters 4–51                                    | PCML Specifications 4–8                                     |

| M-RAM                                              | Advanced I/O Standard Support 2–122                         |

| Interface Locations 2–38                           | Column I/O Block Connection to the                          |

| Row Pin                                            | Interconnect 2–107                                          |

| Fast Regional Clock External I/O Timing            | Column Pin                                                  |

| Parameters 4–52                                    | Input Delay Adders 4–66                                     |

| Global Clock External I/O Timing                   | Control Signal Selection per IOE 2–109                      |

| Parameters 4–53                                    | CTT I/O Specifications 4–16                                 |

| Regional Clock External I/O Timing                 | Differential LVDS Input On-Chip                             |

| Parameters 4–53                                    | Termination 2–128                                           |

| EP1S80 Devices                                     | External I/O Delay Parameters 4–66                          |

| Column Pin                                         | GTL+ I/O Specifications 4–10<br>High-Speed Differential I/O |

| Fast Regional Clock External I/O Timing            | Support 2–130                                               |

| Parameters 4–54                                    | HyperTransport Technology                                   |

| Global Clock External I/O Timing                   | Specifications 4–9                                          |

| Parameters 4–55                                    | I/O Banks 2–125                                             |

| Regional Clock External I/O Timing                 | I/O Structure 2–104                                         |

| Parameters 4–54                                    | I/O Support by Bank 2–126                                   |

| Global Clock External I/O Timing                   | IOE Structure 2–105                                         |

| Parameters 4–56                                    | LVCMOS Specifications 4–3                                   |

| Row Pin                                            | LVDS Performance on Fast PLL                                |

| Fast Regional Clock External I/O Timing            | Input 2–103                                                 |

| Parameters 4–55                                    | LVPECL Specifications 4–8                                   |

| Regional Clock External I/O Timing                 | LVTTL Specifications 4–3                                    |

| Parameters 4–56                                    | MultiVolt I/O Interface 2–129                               |

|                                                    | MultiVolt I/O Support 2–130                                 |

| H                                                  | Output Delay Adders for Fast Slew Rate                      |

| HSTL                                               | on Column Pins 4–68                                         |

| Class I Specifications 4–14, 4–15                  | Output Delay Adders for Fast Slew Rate                      |

| Class II Specifications 4–14, 4–15                 | on Row Pins 4–69                                            |

| Ciass II Specifications 4-14, 4-15                 | Output Delay Adders for Slow Slew Rate                      |

|                                                    | on Column Pins 4–70                                         |

|                                                    | Package Options & I/O Pin Counts 1–4                        |

|                                                    | Receiver Input Waveforms for Differential                   |

Index-4 Altera Corporation