### Altera - EP1S60B956C6 Datasheet

Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Active                                                    |

| Number of LABs/CLBs            | 5712                                                      |

| Number of Logic Elements/Cells | 57120                                                     |

| Total RAM Bits                 | 5215104                                                   |

| Number of I/O                  | 683                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.425V ~ 1.575V                                           |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 956-BBGA, FCBGA                                           |

| Supplier Device Package        | 956-BGA (40x40)                                           |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=ep1s60b956c6 |

|                                |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Copyright © 2006 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make

changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# **About This Handbook**

This handbook provides comprehensive information about the Altera® Stratix family of devices.

### How to Find You can find more information in the following ways: Information The Adobe Acrobat Find feature, which searches the text of a PDF document. Click the binoculars toolbar icon to open the Find dialog box. Acrobat bookmarks, which serve as an additional table of contents in PDF documents. Thumbnail icons, which provide miniature previews of each page, provide a link to the pages. Numerous links, shown in green text, which allow you to jump to related information.

# How to Contact Altera

For the most up-to-date information about Altera products, go to the Altera world-wide web site at www.altera.com. For technical support on this product, go to www.altera.com/mysupport. For additional information about Altera products, consult the sources shown below.

| Information Type               | USA & Canada                                                   | All Other Locations                                                    |

|--------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------|

| Technical support              | www.altera.com/mysupport/                                      | www.altera.com/mysupport/                                              |

|                                | (800) 800-EPLD (3753)<br>(7:00 a.m. to 5:00 p.m. Pacific Time) | +1 408-544-8767<br>7:00 a.m. to 5:00 p.m. (GMT -8:00)<br>Pacific Time  |

| Product literature             | www.altera.com                                                 | www.altera.com                                                         |

| Altera literature services     | literature@altera.com                                          | literature@altera.com                                                  |

| Non-technical customer service | (800) 767-3753                                                 | + 1 408-544-7000<br>7:00 a.m. to 5:00 p.m. (GMT -8:00)<br>Pacific Time |

| FTP site                       | ftp.altera.com                                                 | ftp.altera.com                                                         |

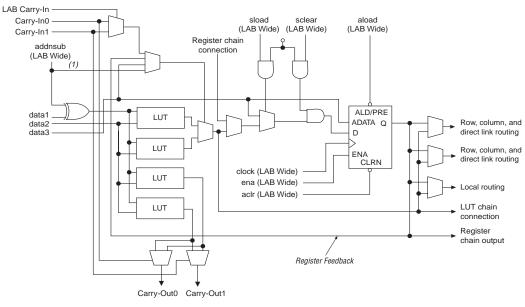

Figure 2–7. LE in Dynamic Arithmetic Mode

*Note to Figure 2–7:*(1) The addnsub signal is tied to the carry input for the first LE of a carry chain only.

### Carry-Select Chain

The carry-select chain provides a very fast carry-select function between LEs in arithmetic mode. The carry-select chain uses the redundant carry calculation to increase the speed of carry functions. The LE is configured to calculate outputs for a possible carry-in of 1 and carry-in of 0 in parallel. The carry-in0 and carry-in1 signals from a lower-order bit feed forward into the higher-order bit via the parallel carry chain and feed into both the LUT and the next portion of the carry chain. Carry-select chains can begin in any LE within an LAB.

The speed advantage of the carry-select chain is in the parallel precomputation of carry chains. Since the LAB carry-in selects the precomputed carry chain, not every LE is in the critical path. Only the propagation delay between LAB carry-in generation (LE 5 and LE 10) are now part of the critical path. This feature allows the Stratix architecture to implement high-speed counters, adders, multipliers, parity functions, and comparators of arbitrary width.

| Table 2–2. Strat            | ix De        | vice F         | Routin             | ng Scl                   | heme            |                 |                  |                 |                 |                  |              |                |               |             |            |            |         |

|-----------------------------|--------------|----------------|--------------------|--------------------------|-----------------|-----------------|------------------|-----------------|-----------------|------------------|--------------|----------------|---------------|-------------|------------|------------|---------|

|                             |              |                |                    |                          |                 |                 |                  | Des             | stinat          | ion              |              |                |               |             |            |            |         |

| Source                      | LUT Chain    | Register Chain | Local Interconnect | Direct Link Interconnect | R4 Interconnect | R8 Interconnect | R24 Interconnect | C4 Interconnect | C8 Interconnect | C16 Interconnect | TE           | M512 RAM Block | M4K RAM Block | M-RAM Block | DSP Blocks | Column IOE | Row IOE |

| LUT Chain                   |              |                |                    |                          |                 |                 |                  |                 |                 |                  | $\checkmark$ |                |               |             |            |            |         |

| Register Chain              |              |                |                    |                          |                 |                 |                  |                 |                 |                  | $\checkmark$ |                |               |             |            |            |         |

| Local<br>Interconnect       |              |                |                    |                          |                 |                 |                  |                 |                 |                  | ~            | ~              | ~             | ~           | ~          | ~          | ~       |

| Direct Link<br>Interconnect |              |                | ~                  |                          |                 |                 |                  |                 |                 |                  |              |                |               |             |            |            |         |

| R4 Interconnect             |              |                | ~                  |                          | $\checkmark$    |                 | $\checkmark$     | $\checkmark$    |                 | ~                |              |                |               |             |            |            |         |

| R8 Interconnect             |              |                | >                  |                          |                 | $\checkmark$    |                  |                 | >               |                  |              |                |               |             |            |            |         |

| R24<br>Interconnect         |              |                |                    |                          | ~               |                 | ~                | ~               |                 | >                |              |                |               |             |            |            |         |

| C4 Interconnect             |              |                | $\checkmark$       |                          | $\checkmark$    |                 |                  | $\checkmark$    |                 |                  |              |                |               |             |            |            |         |

| C8 Interconnect             |              |                | ~                  |                          |                 | $\checkmark$    |                  |                 | ~               |                  |              |                |               |             |            |            |         |

| C16<br>Interconnect         |              |                |                    |                          | ~               |                 | ~                | ~               |                 | ~                |              |                |               |             |            |            |         |

| LE                          | $\checkmark$ | $\checkmark$   | $\checkmark$       | ~                        | >               | <               |                  | <               | ~               |                  |              |                |               |             |            |            |         |

| M512 RAM<br>Block           |              |                | ~                  | ~                        | ~               | ~               |                  | ~               | ~               |                  |              |                |               |             |            |            |         |

| M4K RAM Block               |              |                | $\checkmark$       | $\checkmark$             | >               | <               |                  | <               | ~               |                  |              |                |               |             |            |            |         |

| M-RAM Block                 |              |                |                    |                          |                 |                 |                  | $\checkmark$    | $\checkmark$    |                  |              |                |               |             |            |            |         |

| DSP Blocks                  |              |                | $\checkmark$       | $\checkmark$             | $\checkmark$    | $\checkmark$    |                  | $\checkmark$    | $\checkmark$    |                  |              |                |               |             |            |            |         |

| Column IOE                  |              |                |                    | $\checkmark$             |                 |                 |                  | $\checkmark$    | $\checkmark$    | $\checkmark$     |              |                |               |             |            |            |         |

| Row IOE                     |              |                |                    | $\checkmark$             |                 | $\checkmark$    | $\checkmark$     | $\checkmark$    | $\checkmark$    | $\checkmark$     |              |                |               |             |            |            |         |

Table 2–2 shows the Stratix device's routing scheme.

### M-RAM Block

The largest TriMatrix memory block, the M-RAM block, is useful for applications where a large volume of data must be stored on-chip. Each block contains 589,824 RAM bits (including parity bits). The M-RAM block can be configured in the following modes:

- True dual-port RAM

- Simple dual-port RAM

- Single-port RAM

- FIFO RAM

You cannot use an initialization file to initialize the contents of a M-RAM block. All M-RAM block contents power up to an undefined value. Only synchronous operation is supported in the M-RAM block, so all inputs are registered. Output registers can be bypassed. The memory address and output width can be configured as  $64K \times 8$  (or  $64K \times 9$  bits),  $32K \times 16$  (or  $32K \times 18$  bits),  $16K \times 32$  (or  $16K \times 36$  bits),  $8K \times 64$  (or  $8K \times 72$  bits), and  $4K \times 128$  (or  $4K \times 144$  bits). The  $4K \times 128$  configuration is unavailable in true dual-port mode because there are a total of 144 data output drivers in the block. Mixed-width configurations are also possible, allowing different read and write widths. Tables 2–8 and 2–9 summarize the possible M-RAM block configurations:

| Table 2–8. M         | Table 2–8. M-RAM Block Configurations (Simple Dual-Port) |              |              |              |              |  |  |  |  |  |

|----------------------|----------------------------------------------------------|--------------|--------------|--------------|--------------|--|--|--|--|--|

| Read Port Write Port |                                                          |              |              |              |              |  |  |  |  |  |

| Reau Port            | 64K × 9                                                  | 32K × 18     | 16K × 36     | 8K × 72      | 4K × 144     |  |  |  |  |  |

| 64K × 9              | ~                                                        | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |  |  |  |  |  |

| 32K × 18             | ~                                                        | $\checkmark$ | $\checkmark$ | ~            |              |  |  |  |  |  |

| 16K × 36             | ~                                                        | ~            | $\checkmark$ | ~            |              |  |  |  |  |  |

| 8K × 72              | ~                                                        | ~            | $\checkmark$ | ~            |              |  |  |  |  |  |

| 4K × 144             |                                                          |              |              |              | $\checkmark$ |  |  |  |  |  |

## **Independent Clock Mode**

The memory blocks implement independent clock mode for true dualport memory. In this mode, a separate clock is available for each port (ports A and B). Clock A controls all registers on the port A side, while clock B controls all registers on the port B side. Each port, A and B, also supports independent clock enables and asynchronous clear signals for port A and B registers. Figure 2–24 shows a TriMatrix memory block in independent clock mode.

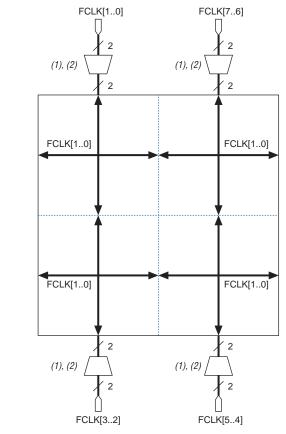

# *Figure 2–44. EP1S25, EP1S20 & EP1S10 Device Fast Clock Pin Connections to Fast Regional Clocks*

### Notes to Figure 2–44:

- (1) This is a set of two multiplexers.

- (2) In addition to the FCLK pin inputs, there is also an input from the I/O interconnect.

| Control | Signal | s |

|---------|--------|---|

|         |        |   |

The fast PLL has the same lock output, pllenable input, and areset input control signals as the enhanced PLL.

If the input clock stops and causes the PLL to lose lock, then the PLL must be reset for correct phase shift operation.

For more information on high-speed differential I/O support, see "High-Speed Differential I/O Support" on page 2–130.

# I/O Structure

IOEs provide many features, including:

- Dedicated differential and single-ended I/O buffers

- 3.3-V, 64-bit, 66-MHz PCI compliance

- 3.3-V, 64-bit, 133-MHz PCI-X 1.0 compliance

- Joint Test Action Group (JTAG) boundary-scan test (BST) support

- Differential on-chip termination for LVDS I/O standard

- Programmable pull-up during configuration

- Output drive strength control

- Slew-rate control

- Tri-state buffers

- Bus-hold circuitry

- Programmable pull-up resistors

- Programmable input and output delays

- Open-drain outputs

- DQ and DQS I/O pins

- Double-data rate (DDR) Registers

The IOE in Stratix devices contains a bidirectional I/O buffer, six registers, and a latch for a complete embedded bidirectional single data rate or DDR transfer. Figure 2–59 shows the Stratix IOE structure. The IOE contains two input registers (plus a latch), two output registers, and two output enable registers. The design can use both input registers and the latch to capture DDR input and both output registers to drive DDR outputs. Additionally, the design can use the output enable (OE) register for fast clock-to-output enable timing. The negative edge-clocked OE register is used for DDR SDRAM interfacing. The Quartus II software automatically duplicates a single OE register that controls multiple output or bidirectional pins.

## **Programmable Pull-Up Resistor**

Each Stratix device I/O pin provides an optional programmable pull-up resistor during user mode. If this feature is enabled for an I/O pin, the pull-up resistor (typically 25 k $\Omega$ ) weakly holds the output to the V<sub>CCIO</sub> level of the output pin's bank. Table 2–30 shows which pin types support the weak pull-up resistor feature.

| Table 2–30. Programmable We | eak Pull-Up Resistor Support       |

|-----------------------------|------------------------------------|

| Pin Type                    | Programmable Weak Pull-Up Resistor |

| I/O pins                    | ✓                                  |

| CLK[150]                    |                                    |

| FCLK                        | ~                                  |

| FPLL[710]CLK                |                                    |

| Configuration pins          |                                    |

| JTAG pins                   | ✓ (1)                              |

Note to Table 2–30:

(1) TDO pins do not support programmable weak pull-up resistors.

## Advanced I/O Standard Support

Stratix device IOEs support the following I/O standards:

- LVTTL

- LVCMOS

- 1.5 V

- 1.8 V

- 2.5 V

- 3.3-V PCI

- 3.3-V PCI-X 1.0

- 3.3-V AGP (1× and 2×)

- LVDS

- LVPECL

- **3.3-V PCML**

- HyperTransport

- Differential HSTL (on input/output clocks only)

- Differential SSTL (on output column clock pins only)

- GTL/GTL+

- 1.5-V HSTL Class I and II

| Table 2-40.                  | EP1S60 Diffe    | rential Chai      | nnels (Part 2       | ? of 2)    | lote (1)   |            |            |                           |            |            |        |

|------------------------------|-----------------|-------------------|---------------------|------------|------------|------------|------------|---------------------------|------------|------------|--------|

|                              | Transmitter/    | Total<br>Channels | Maximum             | C          | enter F    | ast PLI    | _S         | Corner Fast PLLs (2), (3) |            |            |        |

| Package                      | Receiver        |                   | Speed<br>(Mbps)     | PLL1       | PLL2       | PLL3       | PLL4       | PLL7                      | PLL8       | PLL9       | PLL10  |

| 1,020-pin<br>FineLine<br>BGA | Transmitter (4) | 80 (12)<br>(7)    | 840                 | 12<br>(2)  | 10<br>(4)  | 10<br>(4)  | 12<br>(2)  | 20                        | 20         | 20         | 20     |

|                              |                 |                   | 840 <i>(5), (8)</i> | 22<br>(6)  | 22<br>(6)  | 22<br>(6)  | 22<br>(6)  | 20                        | 20         | 20         | 20     |

|                              | Receiver        | 80 (10)<br>(7)    | 840                 | 20         | 20         | 20         | 20         | 12<br>(8)                 | 10<br>(10) | 10<br>(10) | 12 (8) |

|                              |                 |                   | 840 <i>(5), (8)</i> | 40         | 40         | 40         | 40         | 12<br>(8)                 | 10<br>(10) | 10<br>(10) | 12 (8) |

| 1,508-pin<br>FineLine<br>BGA | Transmitter (4) | 80 (36)<br>(7)    | 840                 | 12<br>(8)  | 10<br>(10) | 10<br>(10) | 12<br>(8)  | 20                        | 20         | 20         | 20     |

|                              |                 |                   | 840 <i>(5),(8)</i>  | 22<br>(18) | 22<br>(18) | 22<br>(18) | 22<br>(18) | 20                        | 20         | 20         | 20     |

|                              | Receiver        | 80 (36)<br>(7)    | 840                 | 20         | 20         | 20         | 20         | 12<br>(8)                 | 10<br>(10) | 10<br>(10) | 12 (8) |

|                              |                 |                   | 840 <i>(5),(8)</i>  | 40         | 40         | 40         | 40         | 12<br>(8)                 | 10<br>(10) | 10<br>(10) | 12 (8) |

| Table 2–41.                  | Table 2–41. EP1S80 Differential Channels (Part 1 of 2) Note (1) |                |                 |           |           |           |           |                           |           |        |        |  |  |

|------------------------------|-----------------------------------------------------------------|----------------|-----------------|-----------|-----------|-----------|-----------|---------------------------|-----------|--------|--------|--|--|

|                              | Transmitter/                                                    | Total          | Maximum         | C         | enter F   | ast PLI   | .s        | Corner Fast PLLs (2), (3) |           |        |        |  |  |

| Package                      | Receiver                                                        | Channels       | Speed<br>(Mbps) | PLL1      | PLL2      | PLL3      | PLL4      | PLL7                      | PLL8      | PLL9   | PLL10  |  |  |

| 956-pin                      | Transmitter                                                     | 80 (40)        | 840             | 10        | 10        | 10        | 10        | 20                        | 20        | 20     | 20     |  |  |

| BGA (4)<br>Recei             | (4)                                                             | (7)            | 840 (5),(8)     | 20        | 20        | 20        | 20        | 20                        | 20        | 20     | 20     |  |  |

|                              | Receiver                                                        | 80             | 840             | 20        | 20        | 20        | 20        | 10                        | 10        | 10     | 10     |  |  |

|                              |                                                                 |                | 840 (5),(8)     | 40        | 40        | 40        | 40        | 10                        | 10        | 10     | 10     |  |  |

| 1,020-pin<br>FineLine<br>BGA | Transmitter (4)                                                 | 92 (12)<br>(7) | 840             | 10<br>(2) | 10<br>(4) | 10<br>(4) | 10<br>(2) | 20                        | 20        | 20     | 20     |  |  |

|                              |                                                                 |                | 840 (5),(8)     | 20<br>(6) | 20<br>(6) | 20<br>(6) | 20<br>(6) | 20                        | 20        | 20     | 20     |  |  |

|                              | Receiver                                                        | 90 (10)<br>(7) | 840             | 20        | 20        | 20        | 20        | 10<br>(2)                 | 10<br>(3) | 10 (3) | 10 (2) |  |  |

|                              |                                                                 |                | 840 (5),(8)     | 40        | 40        | 40        | 40        | 10<br>(2)                 | 10<br>(3) | 10 (3) | 10 (2) |  |  |

| Table 2–41.                  | Table 2–41. EP1S80 Differential Channels (Part 2 of 2) Note (1) |                |                    |                  |            |            |            |                           |            |            |            |  |  |

|------------------------------|-----------------------------------------------------------------|----------------|--------------------|------------------|------------|------------|------------|---------------------------|------------|------------|------------|--|--|

|                              | Transmitter/                                                    | Total          | Maximum            | Center Fast PLLs |            |            |            | Corner Fast PLLs (2), (3) |            |            |            |  |  |

| Package                      | Receiver                                                        | Channels       | Speed<br>(Mbps)    | PLL1             | PLL2       | PLL3       | PLL4       | PLL7                      | PLL8       | PLL9       | PLL10      |  |  |

| 1,508-pin<br>FineLine<br>BGA | Transmitter<br>(4)                                              | 80 (72)<br>(7) | 840                | 10<br>(10)       | 10<br>(10) | 10<br>(10) | 10<br>(10) | 20<br>(8)                 | 20<br>(8)  | 20 (8)     | 20 (8)     |  |  |

|                              |                                                                 |                | 840 <i>(5),(8)</i> | 20<br>(20)       | 20<br>(20) | 20<br>(20) | 20<br>(20) | 20<br>(8)                 | 20<br>(8)  | 20 (8)     | 20 (8)     |  |  |

|                              | Receiver                                                        | 80 (56)<br>(7) | 840                | 20               | 20         | 20         | 20         | 10<br>(14)                | 10<br>(14) | 10<br>(14) | 10<br>(14) |  |  |

|                              |                                                                 |                | 840 <i>(5),(8)</i> | 40               | 40         | 40         | 40         | 10<br>(14)                | 10<br>(14) | 10<br>(14) | 10<br>(14) |  |  |

#### *Notes to Tables* 2–38 *through* 2–41:

- (1) The first row for each transmitter or receiver reports the number of channels driven directly by the PLL. The second row below it shows the maximum channels a PLL can drive if cross bank channels are used from the adjacent center PLL. For example, in the 780-pin FineLine BGA EP1S30 device, PLL 1 can drive a maximum of 18 transmitter channels at 840 Mbps or a maximum of 35 transmitter channels at 840 Mbps. The Quartus II software may also merge transmitter and receiver PLLs when a receiver is driving a transmitter. In this case, one fast PLL can drive both the maximum numbers of receiver and transmitter channels.

- (2) Some of the channels accessible by the center fast PLL and the channels accessible by the corner fast PLL overlap. Therefore, the total number of channels is not the addition of the number of channels accessible by PLLs 1, 2, 3, and 4 with the number of channels accessible by PLLs 7, 8, 9, and 10. For more information on which channels overlap, see the Stratix device pin-outs at **www.altera.com**.

- (3) The corner fast PLLs in this device support a data rate of 840 Mbps for channels labeled "high" speed in the device pin-outs at www.altera.com.

- (4) The numbers of channels listed include the transmitter clock output (tx\_outclock) channel. An extra data channel can be used if a DDR clock is needed.

- (5) These channels span across two I/O banks per side of the device. When a center PLL clocks channels in the opposite bank on the same side of the device it is called cross-bank PLL support. Both center PLLs can clock cross-bank channels simultaneously if say PLL\_1 is clocking all receiver channels and PLL\_2 is clocking all transmitter channels. You cannot have two adjacent PLLs simultaneously clocking cross-bank receiver channels or two adjacent PLLs simultaneously clocking transmitter channels. Cross-bank allows for all receiver channels on one side of the device to be clocked on one clock while all transmitter channels on the device are clocked on the other center PLL. Crossbank PLLs are supported at full-speed, 840 Mbps. For wire-bond devices, the full-speed is 624 Mbps.

- (6) PLLs 7, 8, 9, and 10 are not available in this device.

- (7) The number in parentheses is the number of slow-speed channels, guaranteed to operate at up to 462 Mbps. These channels are independent of the high-speed differential channels. For the location of these channels, see the device pin-outs at www.altera.com.

- (8) See the Stratix device pin-outs at **www.altera.com**. Channels marked "high" speed are 840 MBps and "low" speed channels are 462 MBps.

The high-speed differential I/O circuitry supports the following high speed I/O interconnect standards and applications:

- UTOPIA IV

- SPI-4 Phase 2 (POS-PHY Level 4)

- SFI-4

- 10G Ethernet XSBI

| Quanta            | Devementer                                         | Oanditiana                                         | Min in                                          | Mawimum           | 11   |

|-------------------|----------------------------------------------------|----------------------------------------------------|-------------------------------------------------|-------------------|------|

| Symbol            | Parameter                                          | Conditions                                         | Minimum                                         | Maximum           | Unit |

| V <sub>CCIO</sub> | Supply voltage for output buffers, 3.3-V operation | (4), (5)                                           | 3.00 (3.135)                                    | 3.60 (3.465)      | V    |

|                   | Supply voltage for output buffers, 2.5-V operation | (4)                                                | 2.375         2.625           1.71         1.89 | V                 |      |

|                   | Supply voltage for output buffers, 1.8-V operation | (4)                                                | 1.71                                            |                   | V    |

|                   | Supply voltage for output buffers, 1.5-V operation | V operation     Image for output       (4)     1.4 | 1.6                                             | V                 |      |

| VI                | Input voltage                                      | (3), (6)                                           | -0.5                                            | 4.0               | V    |

| Vo                | Output voltage                                     |                                                    | 0                                               | V <sub>CCIO</sub> | V    |

| TJ                | Operating junction                                 | For commercial use                                 | 0                                               | 85                | °C   |

|                   | temperature                                        | For industrial use                                 | -40                                             | 100               | °C   |

| Table 4–3        | . Stratix Device DC O                               | perating Conditions Note (7                          | ") (Part 1 of 2) |         |         |      |

|------------------|-----------------------------------------------------|------------------------------------------------------|------------------|---------|---------|------|

| Symbol           | Parameter                                           | Conditions                                           | Minimum          | Typical | Maximum | Unit |

| l <sub>l</sub>   | Input pin leakage<br>current                        | $V_{I} = V_{CCIOmax}$ to 0 V (8)                     | -10              |         | 10      | μA   |

| I <sub>OZ</sub>  | Tri-stated I/O pin<br>leakage current               | $V_{O} = V_{CCIOmax}$ to 0 V (8)                     | -10              |         | 10      | μA   |

| I <sub>CC0</sub> | V <sub>CC</sub> supply current<br>(standby) (All    | V <sub>I</sub> = ground, no load, no toggling inputs |                  |         |         | mA   |

|                  | memory blocks in<br>power-down mode)                | EP1S10. $V_1$ = ground, no load, no toggling inputs  |                  | 37      |         | mA   |

|                  |                                                     | EP1S20. $V_1$ = ground, no load, no toggling inputs  |                  | 65      |         | mA   |

|                  |                                                     | EP1S25. $V_1$ = ground, no load, no toggling inputs  |                  | 90      |         | mA   |

|                  |                                                     | EP1S30. $V_1$ = ground, no load, no toggling inputs  |                  | 114     |         | mA   |

|                  |                                                     | EP1S40. $V_1$ = ground, no load, no toggling inputs  |                  | 145     |         | mA   |

|                  | EP1S60. $V_1$ = ground, no load, no toggling inputs |                                                      | 200              |         | mA      |      |

|                  |                                                     | EP1S80. $V_1$ = ground, no load, no toggling inputs  |                  | 277     |         | mA   |

4–2

| Table 4–3. Stratix Device DC Operating Conditions Note (7) (Part 2 of 2) |                                  |                                        |         |         |         |      |  |  |  |  |

|--------------------------------------------------------------------------|----------------------------------|----------------------------------------|---------|---------|---------|------|--|--|--|--|

| Symbol                                                                   | Parameter                        | Conditions                             | Minimum | Typical | Maximum | Unit |  |  |  |  |

| R <sub>CONF</sub>                                                        | Value of I/O pin pull-           | V <sub>CCIO</sub> = 3.0 V (9)          | 20      |         | 50      | kΩ   |  |  |  |  |

|                                                                          | up resistor before<br>and during | V <sub>CCIO</sub> = 2.375 V <i>(9)</i> | 30      |         | 80      | kΩ   |  |  |  |  |

|                                                                          | configuration                    | V <sub>CCIO</sub> = 1.71 V <i>(9)</i>  | 60      |         | 150     | kΩ   |  |  |  |  |

| Table 4–4. LVTTL Specifications |                           |                                               |         |         |      |  |  |  |

|---------------------------------|---------------------------|-----------------------------------------------|---------|---------|------|--|--|--|

| Symbol                          | Parameter                 | Conditions                                    | Minimum | Maximum | Unit |  |  |  |

| V <sub>CCIO</sub>               | Output supply voltage     |                                               | 3.0     | 3.6     | V    |  |  |  |

| V <sub>IH</sub>                 | High-level input voltage  |                                               | 1.7     | 4.1     | V    |  |  |  |

| V <sub>IL</sub>                 | Low-level input voltage   |                                               | -0.5    | 0.7     | V    |  |  |  |

| V <sub>OH</sub>                 | High-level output voltage | $I_{OH} = -4 \text{ to } -24 \text{ mA} (10)$ | 2.4     |         | V    |  |  |  |

| V <sub>OL</sub>                 | Low-level output voltage  | I <sub>OL</sub> = 4 to 24 mA <i>(10)</i>      |         | 0.45    | V    |  |  |  |

| Table 4–5. LVCMOS Specifications |                           |                                                       |                         |         |      |  |  |  |

|----------------------------------|---------------------------|-------------------------------------------------------|-------------------------|---------|------|--|--|--|

| Symbol                           | Parameter                 | Conditions                                            | Minimum                 | Maximum | Unit |  |  |  |

| V <sub>CCIO</sub>                | Output supply voltage     |                                                       | 3.0                     | 3.6     | V    |  |  |  |

| V <sub>IH</sub>                  | High-level input voltage  |                                                       | 1.7                     | 4.1     | V    |  |  |  |

| V <sub>IL</sub>                  | Low-level input voltage   |                                                       | -0.5                    | 0.7     | V    |  |  |  |

| V <sub>OH</sub>                  | High-level output voltage | V <sub>CCIO</sub> = 3.0,<br>I <sub>OH</sub> = -0.1 mA | V <sub>CCIO</sub> - 0.2 |         | V    |  |  |  |

| V <sub>OL</sub>                  | Low-level output voltage  | V <sub>CCIO</sub> = 3.0,<br>I <sub>OL</sub> = 0.1 mA  |                         | 0.2     | V    |  |  |  |

| Table 4–6. 2.5-V I/O Specifications |                           |                                    |         |         |      |  |  |  |

|-------------------------------------|---------------------------|------------------------------------|---------|---------|------|--|--|--|

| Symbol                              | Parameter                 | Conditions                         | Minimum | Maximum | Unit |  |  |  |

| V <sub>CCIO</sub>                   | Output supply voltage     |                                    | 2.375   | 2.625   | V    |  |  |  |

| V <sub>IH</sub>                     | High-level input voltage  |                                    | 1.7     | 4.1     | V    |  |  |  |

| V <sub>IL</sub>                     | Low-level input voltage   |                                    | -0.5    | 0.7     | V    |  |  |  |

| V <sub>OH</sub>                     | High-level output voltage | I <sub>OH</sub> = -1 mA (10)       | 2.0     |         | V    |  |  |  |

| V <sub>OL</sub>                     | Low-level output voltage  | I <sub>OL</sub> = 1 mA <i>(10)</i> |         | 0.4     | V    |  |  |  |

| Table 4–13                         | Table 4–13. HyperTransport Technology Specifications |                        |         |         |         |      |  |  |  |

|------------------------------------|------------------------------------------------------|------------------------|---------|---------|---------|------|--|--|--|

| Symbol                             | Parameter                                            | Conditions             | Minimum | Typical | Maximum | Unit |  |  |  |

| V <sub>CCIO</sub>                  | I/O supply voltage                                   |                        | 2.375   | 2.5     | 2.625   | V    |  |  |  |

| V <sub>ID</sub> (peak-<br>to-peak) | Input differential voltage swing (single-ended)      |                        | 300     |         | 900     | mV   |  |  |  |

| V <sub>ICM</sub>                   | Input common mode voltage                            |                        | 300     |         | 900     | mV   |  |  |  |

| V <sub>OD</sub>                    | Output differential voltage (single-ended)           | R <sub>L</sub> = 100 Ω | 380     | 485     | 820     | mV   |  |  |  |

| $\Delta V_{OD}$                    | Change in V <sub>OD</sub> between high and low       | R <sub>L</sub> = 100 Ω |         |         | 50      | mV   |  |  |  |

| V <sub>OCM</sub>                   | Output common mode voltage                           | R <sub>L</sub> = 100 Ω | 440     | 650     | 780     | mV   |  |  |  |

| $\Delta V_{OCM}$                   | Change in V <sub>OCM</sub> between high and low      | R <sub>L</sub> = 100 Ω |         |         | 50      | mV   |  |  |  |

| RL                                 | Receiver differential input resistor                 |                        | 90      | 100     | 110     | Ω    |  |  |  |

| Table 4–14. 3.3-V PCI Specifications |                           |                             |                       |         |                             |      |  |  |

|--------------------------------------|---------------------------|-----------------------------|-----------------------|---------|-----------------------------|------|--|--|

| Symbol                               | Parameter                 | Conditions                  | Minimum               | Typical | Maximum                     | Unit |  |  |

| V <sub>CCIO</sub>                    | Output supply voltage     |                             | 3.0                   | 3.3     | 3.6                         | V    |  |  |

| V <sub>IH</sub>                      | High-level input voltage  |                             | $0.5 \times V_{CCIO}$ |         | V <sub>CCIO</sub> + 0.5     | V    |  |  |

| V <sub>IL</sub>                      | Low-level input voltage   |                             | -0.5                  |         | 0.3 	imes V <sub>CCIO</sub> | V    |  |  |

| V <sub>OH</sub>                      | High-level output voltage | I <sub>OUT</sub> = -500 μA  | $0.9 \times V_{CCIO}$ |         |                             | V    |  |  |

| V <sub>OL</sub>                      | Low-level output voltage  | I <sub>OUT</sub> = 1,500 μA |                       |         | $0.1 	imes V_{CCIO}$        | V    |  |  |

| Symbol              | Parameter                   | Conditions                          | Minimum                 | Typical   | Maximum                 | Unit |

|---------------------|-----------------------------|-------------------------------------|-------------------------|-----------|-------------------------|------|

| V <sub>CCIO</sub>   | Output supply voltage       |                                     | 2.375                   | 2.5       | 2.625                   | V    |

| V <sub>TT</sub>     | Termination voltage         |                                     | $V_{REF} - 0.04$        | $V_{REF}$ | V <sub>REF</sub> + 0.04 | V    |

| V <sub>REF</sub>    | Reference voltage           |                                     | 1.15                    | 1.25      | 1.35                    | V    |

| V <sub>IH(DC)</sub> | High-level DC input voltage |                                     | V <sub>REF</sub> + 0.18 |           | 3.0                     | V    |

| V <sub>IL(DC)</sub> | Low-level DC input voltage  |                                     | -0.3                    |           | $V_{REF} - 0.18$        | V    |

| V <sub>IH(AC)</sub> | High-level AC input voltage |                                     | V <sub>REF</sub> + 0.35 |           |                         | V    |

| V <sub>IL(AC)</sub> | Low-level AC input voltage  |                                     |                         |           | $V_{REF} - 0.35$        | V    |

| V <sub>OH</sub>     | High-level output voltage   | I <sub>OH</sub> = -8.1 mA<br>(3)    | V <sub>TT</sub> + 0.57  |           |                         | V    |

| V <sub>OL</sub>     | Low-level output voltage    | I <sub>OL</sub> = 8.1 mA <i>(3)</i> |                         |           | V <sub>TT</sub> – 0.57  | V    |

| Table 4–21. SSTL-2 Class II Specifications |                             |                                      |                         |                  |                         |      |  |  |

|--------------------------------------------|-----------------------------|--------------------------------------|-------------------------|------------------|-------------------------|------|--|--|

| Symbol                                     | Parameter                   | Conditions                           | Minimum                 | Typical          | Maximum                 | Unit |  |  |

| V <sub>CCIO</sub>                          | Output supply voltage       |                                      | 2.375                   | 2.5              | 2.625                   | V    |  |  |

| V <sub>TT</sub>                            | Termination voltage         |                                      | $V_{\text{REF}} - 0.04$ | V <sub>REF</sub> | V <sub>REF</sub> + 0.04 | V    |  |  |

| V <sub>REF</sub>                           | Reference voltage           |                                      | 1.15                    | 1.25             | 1.35                    | V    |  |  |

| V <sub>IH(DC)</sub>                        | High-level DC input voltage |                                      | V <sub>REF</sub> + 0.18 |                  | $V_{CCIO} + 0.3$        | V    |  |  |

| V <sub>IL(DC)</sub>                        | Low-level DC input voltage  |                                      | -0.3                    |                  | V <sub>REF</sub> - 0.18 | V    |  |  |

| V <sub>IH(AC)</sub>                        | High-level AC input voltage |                                      | V <sub>REF</sub> + 0.35 |                  |                         | V    |  |  |

| V <sub>IL(AC)</sub>                        | Low-level AC input voltage  |                                      |                         |                  | $V_{REF} - 0.35$        | V    |  |  |

| V <sub>OH</sub>                            | High-level output voltage   | I <sub>OH</sub> = -16.4 mA<br>(3)    | V <sub>TT</sub> + 0.76  |                  |                         | V    |  |  |

| V <sub>OL</sub>                            | Low-level output voltage    | I <sub>OL</sub> = 16.4 mA <i>(3)</i> |                         |                  | V <sub>TT</sub> – 0.76  | V    |  |  |

| Table 4–22. SSTL-3 Class I Specifications (Part 1 of 2) |                             |            |                         |                  |                         |      |  |  |  |

|---------------------------------------------------------|-----------------------------|------------|-------------------------|------------------|-------------------------|------|--|--|--|

| Symbol                                                  | Parameter                   | Conditions | Minimum                 | Typical          | Maximum                 | Unit |  |  |  |

| V <sub>CCIO</sub>                                       | Output supply voltage       |            | 3.0                     | 3.3              | 3.6                     | V    |  |  |  |

| V <sub>TT</sub>                                         | Termination voltage         |            | $V_{\text{REF}} - 0.05$ | V <sub>REF</sub> | V <sub>REF</sub> + 0.05 | V    |  |  |  |

| V <sub>REF</sub>                                        | Reference voltage           |            | 1.3                     | 1.5              | 1.7                     | V    |  |  |  |

| V <sub>IH(DC)</sub>                                     | High-level DC input voltage |            | V <sub>REF</sub> + 0.2  |                  | $V_{CCIO} + 0.3$        | V    |  |  |  |

| V <sub>IL(DC)</sub>                                     | Low-level DC input voltage  |            | -0.3                    |                  | V <sub>REF</sub> - 0.2  | V    |  |  |  |

| V <sub>IH(AC)</sub>                                     | High-level AC input voltage |            | V <sub>REF</sub> + 0.4  |                  |                         | V    |  |  |  |

| Table 4–89. l         | Table 4–89. EP1S60 External I/O Timing on Row Pins Using Regional Clock Networks Note (1) |         |         |                      |       |         |         |         |      |  |

|-----------------------|-------------------------------------------------------------------------------------------|---------|---------|----------------------|-------|---------|---------|---------|------|--|

| Doromotor             | -5 Spee                                                                                   | d Grade | -6 Spee | -6 Speed Grade -7 Sp |       | d Grade | -8 Spee | d Grade | Unit |  |

| Parameter             | Min                                                                                       | Max     | Min     | Max                  | Min   | Max     | Min     | Max     | Unit |  |

| t <sub>INSU</sub>     | 2.775                                                                                     |         | 2.990   |                      | 3.407 |         | NA      |         | ns   |  |

| t <sub>INH</sub>      | 0.000                                                                                     |         | 0.000   |                      | 0.000 |         | NA      |         | ns   |  |

| t <sub>OUTCO</sub>    | 2.867                                                                                     | 5.644   | 2.867   | 6.057                | 2.867 | 6.600   | NA      | NA      | ns   |  |

| t <sub>XZ</sub>       | 2.894                                                                                     | 5.698   | 2.894   | 6.113                | 2.894 | 6.668   | NA      | NA      | ns   |  |

| t <sub>ZX</sub>       | 2.894                                                                                     | 5.698   | 2.894   | 6.113                | 2.894 | 6.668   | NA      | NA      | ns   |  |

| t <sub>INSUPLL</sub>  | 1.523                                                                                     |         | 1.577   |                      | 1.791 |         | NA      |         | ns   |  |

| t <sub>INHPLL</sub>   | 0.000                                                                                     |         | 0.000   |                      | 0.000 |         | NA      |         | ns   |  |

| t <sub>OUTCOPLL</sub> | 1.174                                                                                     | 2.507   | 1.174   | 2.643                | 1.174 | 2.664   | NA      | NA      | ns   |  |

| t <sub>XZPLL</sub>    | 1.201                                                                                     | 2.561   | 1.201   | 2.699                | 1.201 | 2.732   | NA      | NA      | ns   |  |

| t <sub>ZXPLL</sub>    | 1.201                                                                                     | 2.561   | 1.201   | 2.699                | 1.201 | 2.732   | NA      | NA      | ns   |  |

|                       | -5 Speed Grade |       | -6 Spee | -6 Speed Grade -7 Speed Gra |       | d Grade | e -8 Speed Grade |     |      |

|-----------------------|----------------|-------|---------|-----------------------------|-------|---------|------------------|-----|------|

| Parameter             | Min            | Max   | Min     | Max                         | Min   | Max     | Min              | Max | Unit |

| t <sub>INSU</sub>     | 2.232          |       | 2.393   |                             | 2.721 |         | NA               |     | ns   |

| t <sub>INH</sub>      | 0.000          |       | 0.000   |                             | 0.000 |         | NA               |     | ns   |

| t <sub>outco</sub>    | 3.182          | 6.187 | 3.182   | 6.654                       | 3.182 | 7.286   | NA               | NA  | ns   |

| t <sub>XZ</sub>       | 3.209          | 6.241 | 3.209   | 6.710                       | 3.209 | 7.354   | NA               | NA  | ns   |

| t <sub>ZX</sub>       | 3.209          | 6.241 | 3.209   | 6.710                       | 3.209 | 7.354   | NA               | NA  | ns   |

| t <sub>INSUPLL</sub>  | 1.651          |       | 1.612   |                             | 1.833 |         | NA               |     | ns   |

| t <sub>INHPLL</sub>   | 0.000          |       | 0.000   |                             | 0.000 |         | NA               |     | ns   |

| t <sub>OUTCOPLL</sub> | 1.154          | 2.469 | 1.154   | 2.608                       | 1.154 | 2.622   | NA               | NA  | ns   |

| t <sub>XZPLL</sub>    | 1.181          | 2.523 | 1.181   | 2.664                       | 1.181 | 2.690   | NA               | NA  | ns   |

| t <sub>ZXPLL</sub>    | 1.181          | 2.523 | 1.181   | 2.664                       | 1.181 | 2.690   | NA               | NA  | ns   |

*Note to Tables* 4–85 *to* 4–90:

(1) Only EP1S25, EP1S30, and EP1S40 devices have the -8 speed grade.

| I/O Standard                     | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|----------------------------------|-------------------|-------------------|-------------------|------|

| GTL+                             | 250               | 200               | 200               | MHz  |

| SSTL-3 Class I                   | 300               | 250               | 250               | MHz  |

| SSTL-3 Class II                  | 300               | 250               | 250               | MHz  |

| SSTL-2 Class I                   | 300               | 250               | 250               | MHz  |

| SSTL-2 Class II                  | 300               | 250               | 250               | MHz  |

| SSTL-18 Class I                  | 300               | 250               | 250               | MHz  |

| SSTL-18 Class II                 | 300               | 250               | 250               | MHz  |

| 1.5-V HSTL Class I               | 300               | 180               | 180               | MHz  |

| 1.5-V HSTL Class II              | 300               | 180               | 180               | MHz  |

| 1.8-V HSTL Class I               | 300               | 180               | 180               | MHz  |

| 1.8-V HSTL Class II              | 300               | 180               | 180               | MHz  |

| 3.3-V PCI                        | 422               | 390               | 390               | MHz  |

| 3.3-V PCI-X 1.0                  | 422               | 390               | 390               | MHz  |

| Compact PCI                      | 422               | 390               | 390               | MHz  |

| AGP 1×                           | 422               | 390               | 390               | MHz  |

| AGP 2×                           | 422               | 390               | 390               | MHz  |

| CTT                              | 250               | 180               | 180               | MHz  |

| Differential 1.5-V HSTL<br>C1    | 300               | 180               | 180               | MHz  |

| LVPECL (1)                       | 422               | 400               | 400               | MHz  |

| PCML (1)                         | 215               | 200               | 200               | MHz  |

| LVDS (1)                         | 422               | 400               | 400               | MHz  |

| HyperTransport<br>technology (1) | 422               | 400               | 400               | MHz  |

Table 4–117. Stratix Maximum Input Clock Rate for CLK[7..4] & CLK[15..12]

Pins in Wire-Bond Packages (Part 2 of 2)

Table 4–118. Stratix Maximum Input Clock Rate for CLK[0, 2, 9, 11] Pins &

FPLL[10..7]CLK Pins in Wire-Bond Packages (Part 1 of 2)

| I/O Standard | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|--------------|-------------------|-------------------|-------------------|------|

| LVTTL        | 422               | 390               | 390               | MHz  |

| 2.5 V        | 422               | 390               | 390               | MHz  |

| 1.8 V        | 422               | 390               | 390               | MHz  |

| 1.5 V        | 422               | 390               | 390               | MHz  |

# PLL Specifications

Tables 4–127 through 4–129 describe the Stratix device enhanced PLL specifications.

| Symbol                   | Parameter                                                                                                             | Min           | Тур | Max                                                                      | Unit         |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------|-----|--------------------------------------------------------------------------|--------------|

| f <sub>IN</sub>          | Input clock frequency                                                                                                 | 3<br>(1), (2) |     | 684                                                                      | MHz          |

| f <sub>INPFD</sub>       | Input frequency to PFD                                                                                                | 3             |     | 420                                                                      | MHz          |

| f <sub>INDUTY</sub>      | Input clock duty cycle                                                                                                | 40            |     | 60                                                                       | %            |

| f <sub>EINDUTY</sub>     | External feedback clock input duty cycle                                                                              | 40            |     | 60                                                                       | %            |

| t <sub>INJITTER</sub>    | Input clock period jitter                                                                                             |               |     | ±200 <i>(3)</i>                                                          | ps           |

| t <sub>EINJITTER</sub>   | External feedback clock period jitter                                                                                 |               |     | ±200 (3)                                                                 | ps           |

| t <sub>FCOMP</sub>       | External feedback clock compensation time (4)                                                                         |               |     | 6                                                                        | ns           |

| f <sub>OUT</sub>         | Output frequency for internal global<br>or regional clock                                                             | 0.3           |     | 500                                                                      | MHz          |

| f <sub>OUT_EXT</sub>     | Output frequency for external clock (3)                                                                               | 0.3           |     | 526                                                                      | MHz          |

| toutduty                 | Duty cycle for external clock output (when set to 50%)                                                                | 45            |     | 55                                                                       | %            |

| t <sub>JITTER</sub>      | Period jitter for external clock output (6)                                                                           |               |     | <pre>±100 ps for &gt;200-MHz outclk ±20 mUI for &lt;200-MHz outclk</pre> | ps or<br>mUI |

| t <sub>CONFIG5,6</sub>   | Time required to reconfigure the scan chains for PLLs 5 and 6                                                         |               |     | 289/f <sub>SCANCLK</sub>                                                 |              |

| t <sub>CONFIG11,12</sub> | Time required to reconfigure the scan chains for PLLs 11 and 12                                                       |               |     | 193/f <sub>SCANCLK</sub>                                                 |              |

| t <sub>SCANCLK</sub>     | scanclk frequency (5)                                                                                                 |               |     | 22                                                                       | MHz          |

| t <sub>DLOCK</sub>       | Time required to lock dynamically<br>(after switchover or reconfiguring<br>any non-post-scale<br>counters/delays) (7) |               |     | 100                                                                      | μs           |

| t <sub>LOCK</sub>        | Time required to lock from end of device configuration                                                                | 10            |     | 400                                                                      | μs           |

| f <sub>VCO</sub>         | PLL internal VCO operating range                                                                                      | 300           |     | 800 (8)                                                                  | MHz          |

| t <sub>LSKEW</sub>       | Clock skew between two external<br>clock outputs driven by the same<br>counter                                        |               | ±50 |                                                                          | ps           |

| Table 4–133. Fast PLL Specifications for -8 Speed Grades (Part 2 of 2) |                                      |     |     |      |  |  |

|------------------------------------------------------------------------|--------------------------------------|-----|-----|------|--|--|

| Symbol                                                                 | Parameter                            | Min | Мах | Unit |  |  |

| t <sub>ARESET</sub>                                                    | Minimum pulse width on areset signal | 10  |     | ns   |  |  |

#### Notes to Tables 4–131 through 4–133:

(1) See "Maximum Input & Output Clock Rates" on page 4–76.

- (2) PLLs 7, 8, 9, and 10 in the EP1S80 device support up to 717-MHz input and output.

- (3) Use this equation ( $f_{OUT} = f_{IN} * ml(n \times \text{post-scale counter})$ ) in conjunction with the specified  $f_{INPFD}$  and  $f_{VCO}$  ranges to determine the allowed PLL settings.

- (4) When using the SERDES, high-speed differential I/O mode supports a maximum output frequency of 210 MHz to the global or regional clocks (that is, the maximum data rate 840 Mbps divided by the smallest SERDES J factor of 4).

- (5) Refer to the section "High-Speed I/O Specification" on page 4-87 for more information.

- (6) This parameter is for high-speed differential I/O mode only.

- (7) These counters have a maximum of 32 if programmed for 50/50 duty cycle. Otherwise, they have a maximum of 16.

- (8) High-speed differential I/O mode supports W = 1 to 16 and J = 4, 7, 8, or 10.

# DLL Specifications

Table 4–134 reports the jitter for the DLL in the DQS phase shift reference circuit.

| Table 4–134. DLL Jitter for DQS Phase Shift Reference Circuit |                 |  |  |  |

|---------------------------------------------------------------|-----------------|--|--|--|

| Frequency (MHz)                                               | DLL Jitter (ps) |  |  |  |

| 197 to 200                                                    | ± 100           |  |  |  |

| 160 to 196                                                    | ± 300           |  |  |  |

| 100 to 159                                                    | ± 500           |  |  |  |

•••

For more information on DLL jitter, see the *DDR SRAM* section in the *Stratix Architecture* chapter of the *Stratix Device Handbook, Volume* 1.

Table 4–135 lists the Stratix DLL low frequency limit for full phase shift across all PVT conditions. The Stratix DLL can be used below these frequencies, but it will not achieve the full phase shift requested across all

Global & Hierarchical Clocking 2-73 Global & Regional Clock Connections from Side Pins & Fast PLL Outputs 2-85 from Top Clock Pins & Enhanced PLL Outputs 2-86 Global Clock External I/O Timing Parameters 4-35 Global Clock Network 2–74 Global Clocking 2-75 Independent Clock Mode 2-44 Input/Output Clock Mode 2 - 46Simple Dual-Port Mode 2–48 True Dual-Port Mode 2-47 Maximum Input & Output Clock Rates 4–76 Maximum Input Clock Rate for CLK (0, 2, 9, 11) Pins in Flip-Chip Packages 4–77 Wire-Bond Packages 4-79 (1, 3, 8, 10) Pins in Flip-Chip Packages 4–78 Wire-Bond Packages 4-80 (7..4) & CLK(15..12) Pins in Flip-Chip Packages 4–76 Wire-Bond Packages 4–78 Maximum Output Clock Rate for PLL (1, 2, 3, 4) Pins in Flip-Chip Packages 4–83 Wire-Bond Packages 4-85 (5, 6, 11, 12) Pins in Flip-Chip

Packages 4-81 Wire-Bond Packages 4–84 Phase & Delay Shifting 2–96 Phase Delay 2-96 PLL Clock Networks 2-73 Read/Write Clock Mode 2 - 49in Simple Dual-Port Mode 2-50 Regional Clock 2–75 External I/O Timing Parameters 4–34 Regional Clock Bus 2–79 Regional Clock Network 2–75 Spread-Spectrum Clocking 2-98 Configuration 3–5 32-Bit IDCODE 3-3 and Testing 3-1 Data Sources for Configuration 3-7 Local Update Mode 3–12 Local Update Transition Diagram 3–12 Operating Modes 3-5 Partial Reconfiguration 3–7 Remote Update 3–8 Remote Update Transition Diagram 3–11 Schemes 3-7 SignalTap II Embedded Logic Analyzer 3–5 Stratix FPGAs with JRunner 3-7 Control Signals 2–104

## D

DC Switching Absolute Maximum Ratings 4–1 Bus Hold Parameters 4–16 Capacitance 4–17 DC & Switching Characteristics 4–1 External Timing Parameters 4–33 Operating Conditions 4–1 Performance 4–20 Power Consumption 4–17 Recommended Operating Conditions 4–1 DDR Double-Data Rate I/O Pins 2–111 Device Features EP1S10, EP1S20, EP1S25, EP1S30, 1–3 EP1S40, EP1S60, EP1S80, 1–3