Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

## Details

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Active                                                    |

| Number of LABs/CLBs            | 5712                                                      |

| Number of Logic Elements/Cells | 57120                                                     |

| Total RAM Bits                 | 5215104                                                   |

| Number of I/O                  | 683                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.425V ~ 1.575V                                           |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                        |

| Package / Case                 | 956-BBGA, FCBGA                                           |

| Supplier Device Package        | 956-BGA (40x40)                                           |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=ep1s60b956i7 |

|                                |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Chapter | Date/Version | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4       |              | <ul> <li>Table 4–48 on page 4–30: added rows t<sub>M512CLKSENSU</sub> and t<sub>M512CLKENH</sub>, and updated symbol names.</li> <li>Updated power-up current (ICCINT) required to power a Stratix device on page 4–17.</li> <li>Updated Table 4–37 on page 4–22 through Table 4–43 on page 4–27.</li> <li>Table 4–49 on page 4–31: added rows t<sub>M4KCLKENSU</sub>, t<sub>M4KCLKENH</sub>, t<sub>M4KBESU</sub>, and t<sub>M4KBEH</sub> deleted rows t<sub>M4KRADDRASU</sub> and t<sub>M4KRADDRH</sub>, and updated symbol names.</li> <li>Table 4–50 on page 4–31: added rows t<sub>M4RADDRASU</sub> and t<sub>M4KRADDRH</sub>, and updated symbol names.</li> <li>Table 4–50 on page 4–34: updated table, deleted "Conditions" column, and added rows t<sub>X2</sub> and t<sub>2X</sub>.</li> <li>Table 4–52 on page 4–34: updated table, deleted "Conditions" column, and added rows t<sub>X2</sub> and t<sub>2X</sub>.</li> <li>Table 4–52 on page 4–34: updated table, deleted "Conditions" column, and added rows t<sub>X2</sub> and t<sub>2X</sub>.</li> <li>Table 4–53 on page 4–34: updated table and added rows t<sub>XZPLL</sub> and t<sub>ZXPLL</sub>.</li> <li>Updated Note 2 in Table 4–53 on page 4–35.</li> <li>Deleted Note 2 in Table 4–55 on page 4–36.</li> <li>Deleted Note 2 from Table 4–55 on page 4–36 through Table 4–66 on page 4–56. Added rows t<sub>XZ</sub>, T<sub>XX</sub>, T<sub>XZPLL</sub>, and T<sub>ZXPLL</sub>.</li> <li>Updated Table 4–55 on page 4–36 through Table 4–66 on page 4–56. Added rows t<sub>XZ</sub>, T<sub>XX</sub>, T<sub>XZPLL</sub>, and T<sub>ZXPLL</sub>.</li> <li>Added Note 4 to Table 4–57 on page 4–36 through Table 4–84 on page 4–50.</li> <li>Added note 2 from Table 4–67 on page 4–42 through Table 4–84 on page 4–50.</li> <li>Added note 2 from Table 4–67 on page 4–42 through Table 4–84 on page 4–50.</li> <li>Added note 4 to Table 4–101 on page 4–62.</li> <li>Table 4–102 on page 4–64: updated table and added Note 4.</li> <li>Updated Table 4–103 on page 4–64.</li> <li>Updated Table 4–103 on page 4–66 through Table 4–110 on page 4–50.</li> <li>Added Note 4 to Table 4–109 on page 4–66.</li> <li>Added Note 4 to Table 4–109 on page 4–66 through Table 4–110 on page 4–74.</li> <li>Updated Table 4–103 on page 4–66 through Table 4–110 on page 4–74.</li> <li>Updated Table</li></ul> |

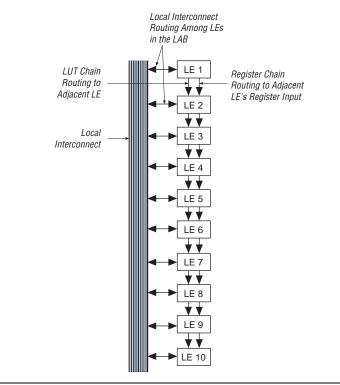

Figure 2–10. LUT Chain & Register Chain Interconnects

The C4 interconnects span four LABs, M512, or M4K blocks up or down from a source LAB. Every LAB has its own set of C4 interconnects to drive either up or down. Figure 2–11 shows the C4 interconnect connections from an LAB in a column. The C4 interconnects can drive and be driven by all types of architecture blocks, including DSP blocks, TriMatrix memory blocks, and vertical IOEs. For LAB interconnection, a primary LAB or its LAB neighbor can drive a given C4 interconnect. C4 interconnects can drive each other to extend their range as well as drive row interconnects for column-to-column connections.

| able 2–11. M-RAM Combined Byte Selection for ×144 Mode Notes (1), (2) |             |

|-----------------------------------------------------------------------|-------------|

| byteena[150]                                                          | datain ×144 |

| [0] = 1                                                               | [80]        |

| [1] = 1                                                               | [179]       |

| [2] = 1                                                               | [2618]      |

| [3] = 1                                                               | [3527]      |

| [4] = 1                                                               | [4436]      |

| [5] = 1                                                               | [5345]      |

| [6] = 1                                                               | [6254]      |

| [7] = 1                                                               | [7163]      |

| [8] = 1                                                               | [8072]      |

| [9] = 1                                                               | [8981]      |

| [10] = 1                                                              | [9890]      |

| [11] = 1                                                              | [10799]     |

| [12] = 1                                                              | [116108]    |

| [13] = 1                                                              | [125117]    |

| [14] = 1                                                              | [134126]    |

| [15] = 1                                                              | [143135]    |

Notes to Tables 2–10 and 2–11:

(1) Any combination of byte enables is possible.

(2) Byte enables can be used in the same manner with 8-bit words, i.e., in  $\times 16$ ,  $\times 32$ ,  $\times 64$ , and  $\times 128$  modes.

Similar to all RAM blocks, M-RAM blocks can have different clocks on their inputs and outputs. All input registers—renwe, datain, address, and byte enable registers—are clocked together from either of the two clocks feeding the block. The output register can be bypassed. The eight labclk signals or local interconnect can drive the control signals for the A and B ports of the M-RAM block. LEs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals as shown in Figure 2–19.

blocks facing to the left, and another 10 possible from the right adjacent LABs for M-RAM blocks facing to the right. For column interfacing, every M-RAM column unit connects to the right and left column lines, allowing each M-RAM column unit to communicate directly with three columns of LABs. Figures 2–21 through 2–23 show the interface between the M-RAM block and the logic array.

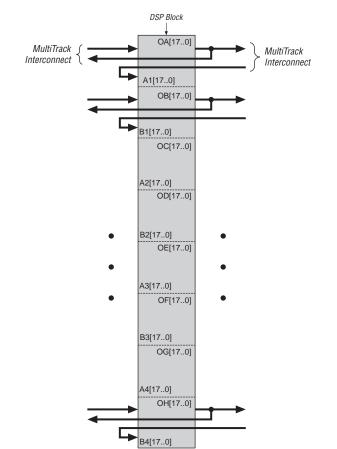

The DSP block is divided into eight block units that interface with eight LAB rows on the left and right. Each block unit can be considered half of an  $18 \times 18$ -bit multiplier sub-block with 18 inputs and 18 outputs. A local interconnect region is associated with each DSP block. Like an LAB, this interconnect region can be fed with 10 direct link interconnects from the LAB to the left or right of the DSP block in the same row. All row and column routing resources can access the DSP block's local interconnect region. The outputs also work similarly to LAB outputs as well. Nine outputs from the DSP block can drive to the left LAB through direct link interconnects and nine can drive to the right LAB through direct link interconnects. All 18 outputs can drive to all types of row and column routing. Outputs can drive right- or left-column routing. Figures 2–40 and 2–41 show the DSP block interfaces to LAB rows.

#### Figure 2–40. DSP Block Interconnect Interface

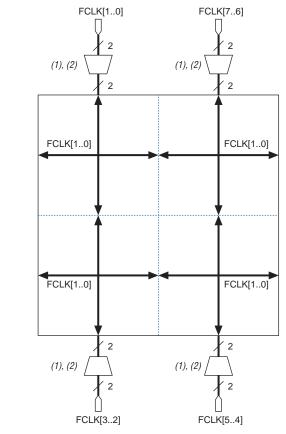

## *Figure 2–44. EP1S25, EP1S20 & EP1S10 Device Fast Clock Pin Connections to Fast Regional Clocks*

#### Notes to Figure 2–44:

- (1) This is a set of two multiplexers.

- (2) In addition to the FCLK pin inputs, there is also an input from the I/O interconnect.

Any of the four external output counters can drive the single-ended or differential clock outputs for PLLs 5 and 6. This means one counter or frequency can drive all output pins available from PLL 5 or PLL 6. Each pair of output pins (four pins total) has dedicated VCC and GND pins to reduce the output clock's overall jitter by providing improved isolation from switching I/O pins.

For PLLs 5 and 6, each pin of a single-ended output pair can either be in phase or 180° out of phase. The clock output pin pairs support the same I/O standards as standard output pins (in the top and bottom banks) as well as LVDS, LVPECL, 3.3-V PCML, HyperTransport technology, differential HSTL, and differential SSTL. Table 2–20 shows which I/O standards the enhanced PLL clock pins support. When in single-ended or differential mode, the two outputs operate off the same power supply. Both outputs use the same standards in single-ended mode to maintain performance. You can also use the external clock output pins as user output pins if external enhanced PLL clocking is not needed.

| Table 2–20. I/O Standards Supported for Enhanced PLL Pins (Part 1 of 2) |                      |              |              |              |  |

|-------------------------------------------------------------------------|----------------------|--------------|--------------|--------------|--|

|                                                                         | Input                |              |              | Output       |  |

| I/O Standard                                                            | INCLK                | FBIN         | PLLENABLE    | EXTCLK       |  |

| LVTTL                                                                   | ~                    | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |

| LVCMOS                                                                  | ~                    | $\checkmark$ | ~            | $\checkmark$ |  |

| 2.5 V                                                                   | ~                    | $\checkmark$ |              | $\checkmark$ |  |

| 1.8 V                                                                   | ~                    | $\checkmark$ |              | $\checkmark$ |  |

| 1.5 V                                                                   | ~                    | $\checkmark$ |              | $\checkmark$ |  |

| 3.3-V PCI                                                               | ~                    | $\checkmark$ |              | $\checkmark$ |  |

| 3.3-V PCI-X 1.0                                                         | ~                    | $\checkmark$ |              | $\checkmark$ |  |

| LVPECL                                                                  | ~                    | $\checkmark$ |              | $\checkmark$ |  |

| 3.3-V PCML                                                              | ~                    | $\checkmark$ |              | $\checkmark$ |  |

| LVDS                                                                    | ~                    | $\checkmark$ |              | $\checkmark$ |  |

| HyperTransport technology                                               | <ul> <li></li> </ul> | $\checkmark$ |              | $\checkmark$ |  |

| Differential HSTL                                                       | ~                    |              |              | $\checkmark$ |  |

| Differential SSTL                                                       |                      |              |              | $\checkmark$ |  |

| 3.3-V GTL                                                               | <ul> <li></li> </ul> | $\checkmark$ |              | $\checkmark$ |  |

| 3.3-V GTL+                                                              | <ul> <li></li> </ul> | $\checkmark$ |              | $\checkmark$ |  |

| 1.5-V HSTL Class I                                                      | <ul> <li></li> </ul> | $\checkmark$ |              | $\checkmark$ |  |

| Table 2–22. Fast PLL Port I/O Standards (Part 2 of 2) |              |           |  |

|-------------------------------------------------------|--------------|-----------|--|

| I/O Standard                                          | Input        |           |  |

|                                                       | INCLK        | PLLENABLE |  |

| SSTL-2 Class II                                       | $\checkmark$ |           |  |

| SSTL-3 Class I                                        | ~            |           |  |

| SSTL-3 Class II                                       | $\checkmark$ |           |  |

| AGP (1 $\times$ and 2 $\times$ )                      |              |           |  |

| СТТ                                                   | ~            |           |  |

Table 2–23 shows the performance on each of the fast PLL clock inputs when using LVDS, LVPECL, 3.3-V PCML, or HyperTransport technology.

| Table 2–23. LVDS Performance on Fast PLL Input                         |        |  |

|------------------------------------------------------------------------|--------|--|

| Fast PLL Clock Input Maximum Input Frequency (MHz)                     |        |  |

| CLK0, CLK2, CLK9, CLK11,<br>FPLL7CLK, FPLL8CLK, FPLL9CLK,<br>FPLL10CLK | 717(1) |  |

| CLK1, CLK3, CLK8, CLK10                                                | 645    |  |

*Note to Table 2–23:*

(1) See the chapter *DC* & *Switching Characteristics* of the *Stratix Device Handbook*, *Volume 1* for more information.

## External Clock Outputs

Each fast PLL supports differential or single-ended outputs for sourcesynchronous transmitters or for general-purpose external clocks. There are no dedicated external clock output pins. Any I/O pin can be driven by the fast PLL global or regional outputs as an external output pin. The I/O standards supported by any particular bank determines what standards are possible for an external clock output driven by the fast PLL in that bank.

## Phase Shifting

Stratix device fast PLLs have advanced clock shift capability that enables programmable phase shifts. You can enter a phase shift (in degrees or time units) for each PLL clock output port or for all outputs together in one shift. You can perform phase shifting in time units with a resolution range of 125 to 416.66 ps. This resolution is a function of the VCO period, with the finest step being equal to an eighth (×0.125) of the VCO period.

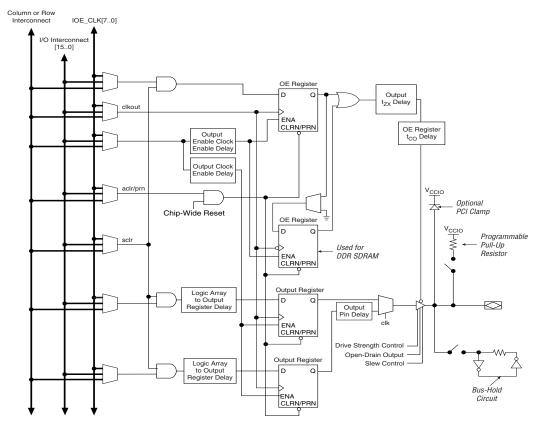

Figure 2–67. Stratix IOE in DDR Output I/O Configuration Notes (1), (2)

#### Notes to Figure 2–67:

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) The tristate is by default active high. It can, however, be designed to be active low.

| Table 2–26. External RAM Support in EP1S60 & EP1S80 Devices |              |                          |                |                |

|-------------------------------------------------------------|--------------|--------------------------|----------------|----------------|

|                                                             | I/O Standard | Maximum Clock Rate (MHz) |                |                |

| DDR Memory Type                                             |              | -5 Speed Grade           | -6 Speed Grade | -7 Speed Grade |

| DDR SDRAM (1), (2)                                          | SSTL-2       | 167                      | 167            | 133            |

| DDR SDRAM - side banks (2), (3)                             | SSTL-2       | 150                      | 133            | 133            |

| QDR SRAM (4)                                                | 1.5-V HSTL   | 133                      | 133            | 133            |

| QDRII SRAM (4)                                              | 1.5-V HSTL   | 167                      | 167            | 133            |

| ZBT SRAM (5)                                                | LVTTL        | 200                      | 200            | 167            |

Table 2–26. External RAM Support in EP1S60 & EP1S80 Devices

Notes to Table 2–26:

These maximum clock rates apply if the Stratix device uses DQS phase-shift circuitry to interface with DDR SDRAM. DQS phase-shift circuitry is only available in the top and bottom I/O banks (I/O banks 3, 4, 7, and 8).

(2) For more information on DDR SDRAM, see AN 342: Interfacing DDR SDRAM with Stratix & Stratix GX Devices.

(3) DDR SDRAM is supported on the Stratix device side I/O banks (I/O banks 1, 2, 5, and 6) without dedicated DQS phase-shift circuitry. The read DQS signal is ignored in this mode. Numbers are preliminary.

(4) For more information on QDR or QDRII SRAM, see AN 349: QDR SRAM Controller Reference Design for Stratix & Stratix GX Devices.

(5) For more information on ZBT SRAM, see AN 329: ZBT SRAM Controller Reference Design for Stratix & Stratix GX Devices.

In addition to six I/O registers and one input latch in the IOE for interfacing to these high-speed memory interfaces, Stratix devices also have dedicated circuitry for interfacing with DDR SDRAM. In every Stratix device, the I/O banks at the top (I/O banks 3 and 4) and bottom (I/O banks 7 and 8) of the device support DDR SDRAM up to 200 MHz. These pins support DQS signals with DQ bus modes of ×8, ×16, or ×32.

Table 2–27 shows the number of DQ and DQS buses that are supported per device.

| Table 2–27. DQS & DQ Bus Mode Support     (Part 1 of 2) Note (1) |                                              |                        |                         |                         |

|------------------------------------------------------------------|----------------------------------------------|------------------------|-------------------------|-------------------------|

| Device                                                           | Package                                      | Number of ×8<br>Groups | Number of ×16<br>Groups | Number of ×32<br>Groups |

| EP1S10                                                           | 672-pin BGA<br>672-pin FineLine BGA          | 12 (2)                 | 0                       | 0                       |

|                                                                  | 484-pin FineLine BGA<br>780-pin FineLine BGA | 16 <i>(3)</i>          | 0                       | 4                       |

| EP1S20                                                           | 484-pin FineLine BGA                         | 18(4)                  | 7 (5)                   | 4                       |

|                                                                  | 672-pin BGA<br>672-pin FineLine BGA          | 16 <i>(3)</i>          | 7 (5)                   | 4                       |

|                                                                  | 780-pin FineLine BGA                         | 20                     | 7 (5)                   | 4                       |

| Table 2–27. DQS & DQ Bus Mode Support       (Part 2 of 2) Note (1) |                                                                 |                        |                         |                         |

|--------------------------------------------------------------------|-----------------------------------------------------------------|------------------------|-------------------------|-------------------------|

| Device                                                             | Package                                                         | Number of ×8<br>Groups | Number of ×16<br>Groups | Number of ×32<br>Groups |

| EP1S25                                                             | 672-pin BGA<br>672-pin FineLine BGA                             | 16 <i>(3)</i>          | 8                       | 4                       |

|                                                                    | 780-pin FineLine BGA<br>1,020-pin FineLine BGA                  | 20                     | 8                       | 4                       |

| EP1S30                                                             | 956-pin BGA<br>780-pin FineLine BGA<br>1,020-pin FineLine BGA   | 20                     | 8                       | 4                       |

| EP1S40                                                             | 956-pin BGA<br>1,020-pin FineLine BGA<br>1,508-pin FineLine BGA | 20                     | 8                       | 4                       |

| EP1S60                                                             | 956-pin BGA<br>1,020-pin FineLine BGA<br>1,508-pin FineLine BGA | 20                     | 8                       | 4                       |

| EP1S80                                                             | 956-pin BGA<br>1,508-pin FineLine BGA<br>1,923-pin FineLine BGA | 20                     | 8                       | 4                       |

#### Notes to Table 2–27:

See the Selectable I/O Standards in Stratix & Stratix GX Devices chapter in the Stratix Device Handbook, Volume 2 for V<sub>REF</sub> guidelines.

(2) These packages have six groups in I/O banks 3 and 4 and six groups in I/O banks 7 and 8.

(3) These packages have eight groups in I/O banks 3 and 4 and eight groups in I/O banks 7 and 8.

(4) This package has nine groups in I/O banks 3 and 4 and nine groups in I/O banks 7 and 8.

(5) These packages have three groups in I/O banks 3 and 4 and four groups in I/O banks 7 and 8.

A compensated delay element on each DQS pin automatically aligns input DQS synchronization signals with the data window of their corresponding DQ data signals. The DQS signals drive a local DQS bus in the top and bottom I/O banks. This DQS bus is an additional resource to the I/O clocks and is used to clock DQ input registers with the DQS signal.

Two separate single phase-shifting reference circuits are located on the top and bottom of the Stratix device. Each circuit is driven by a system reference clock through the CLK pins that is the same frequency as the DQS signal. Clock pins CLK [15..12] p feed the phase-shift circuitry on the top of the device and clock pins CLK [7..4] p feed the phase-shift circuitry on the bottom of the device. The phase-shifting reference circuit on the top of the device controls the compensated delay elements for all 10 DQS pins located at the top of the device. The phase-shifting reference circuit on the bottom of the device controls the compensated delay elements for all 10 DQS pins located on the bottom of the device. All 10 delay elements (DQS signals) on either the top or bottom of the device.

I/O pin has an individual slew-rate control, allowing you to specify the slew rate on a pin-by-pin basis. The slew-rate control affects both the rising and falling edges.

## **Bus Hold**

Each Stratix device I/O pin provides an optional bus-hold feature. The bus-hold circuitry can weakly hold the signal on an I/O pin at its last-driven state. Since the bus-hold feature holds the last-driven state of the pin until the next input signal is present, an external pull-up or pull-down resistor is not needed to hold a signal level when the bus is tri-stated.

Table 2–29 shows bus hold support for different pin types.

| Table 2–29. Bus Hold Support |              |

|------------------------------|--------------|

| Pin Type                     | Bus Hold     |

| I/O pins                     | $\checkmark$ |

| CLK[150]                     |              |

| CLK[0,1,2,3,8,9,10,11]       |              |

| FCLK                         | $\checkmark$ |

| FPLL[710]CLK                 |              |

The bus-hold circuitry also pulls undriven pins away from the input threshold voltage where noise can cause unintended high-frequency switching. You can select this feature individually for each I/O pin. The bus-hold output drives no higher than  $V_{\rm CCIO}$  to prevent overdriving signals. If the bus-hold feature is enabled, the programmable pull-up option cannot be used. Disable the bus-hold feature when using opendrain outputs with the GTL+ I/O standard or when the I/O pin has been configured for differential signals.

The bus-hold circuitry uses a resistor with a nominal resistance ( $R_{BH}$ ) of approximately 7 k $\Omega$ to weakly pull the signal level to the last-driven state. See the *DC* & *Switching Characteristics* chapter of the *Stratix Device Handbook, Volume 1* for the specific sustaining current driven through this resistor and overdrive current used to identify the next-driven input level. This information is provided for each V<sub>CCIO</sub> voltage level.

The bus-hold circuitry is active only after configuration. When going into user mode, the bus-hold circuit captures the value on the pin present at the end of configuration.

| Symbol                       | Parameter                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>SU</sub>              | Input, pipeline, and output register setup time before clock                                                                                                                                                                                                                                                                                                             |

| t <sub>H</sub>               | Input, pipeline, and output register hold time after clock                                                                                                                                                                                                                                                                                                               |

| t <sub>co</sub>              | Input, pipeline, and output register clock-to-output delay                                                                                                                                                                                                                                                                                                               |

| t <sub>INREG2PIPE9</sub>     | Input Register to DSP Block pipeline register in $9 \times 9$ -bit mode                                                                                                                                                                                                                                                                                                  |

| t <sub>INREG2PIPE18</sub>    | Input Register to DSP Block pipeline register in $18 \times 18$ -bit mode                                                                                                                                                                                                                                                                                                |

| t <sub>PIPE2OUTREG2ADD</sub> | DSP Block Pipeline Register to output register delay in Two-<br>Multipliers Adder mode                                                                                                                                                                                                                                                                                   |

| t <sub>PIPE2OUTREG4ADD</sub> | DSP Block Pipeline Register to output register delay in Four-<br>Multipliers Adder mode                                                                                                                                                                                                                                                                                  |

| t <sub>PD9</sub>             | Combinatorial input to output delay for $9 \times 9$                                                                                                                                                                                                                                                                                                                     |

| t <sub>PD18</sub>            | Combinatorial input to output delay for $18 \times 18$                                                                                                                                                                                                                                                                                                                   |

| t <sub>PD36</sub>            | Combinatorial input to output delay for $36 \times 36$                                                                                                                                                                                                                                                                                                                   |

| t <sub>CLR</sub>             | Minimum clear pulse width                                                                                                                                                                                                                                                                                                                                                |

| t <sub>CLKHL</sub>           | Register minimum clock high or low time. This is a limit on<br>the min time for the clock on the registers in these blocks.<br>The actual performance is dependent upon the internal<br>point-to-point delays in the blocks and may give slower<br>performance as shown in Table 4–36 on page 4–20 and as<br>reported by the timing analyzer in the Quartus II software. |

Altera Corporation January 2006

# Table 4–43. Routing Delay Internal Timing Microparameter Descriptions (Part 2 of 2)

| Symbol             | Parameter                                                                                                                                      |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>C4</sub>    | Delay for a C4 line with average loading; covers a distance of four LAB rows.                                                                  |

| t <sub>C8</sub>    | Delay for a C8 line with average loading; covers a distance of eight LAB rows.                                                                 |

| t <sub>C16</sub>   | Delay for a C16 line with average loading; covers a distance of 16 LAB rows.                                                                   |

| t <sub>LOCAL</sub> | Local interconnect delay, for connections within a LAB, and for the final routing hop of connections to LABs, DSP blocks, RAM blocks and I/Os. |

| Parameter          | -    | 5   | -    | 6   | -    | 7   |      | 8   | Unit |

|--------------------|------|-----|------|-----|------|-----|------|-----|------|

|                    | Min  | Max | Min  | Max | Min  | Max | Min  | Max |      |

| t <sub>SU</sub>    | 10   |     | 10   |     | 11   |     | 13   |     | ps   |

| t <sub>H</sub>     | 100  |     | 100  |     | 114  |     | 135  |     | ps   |

| t <sub>co</sub>    |      | 156 |      | 176 |      | 202 |      | 238 | ps   |

| t <sub>LUT</sub>   |      | 366 |      | 459 |      | 527 |      | 621 | ps   |

| t <sub>CLR</sub>   | 100  |     | 100  |     | 114  |     | 135  |     | ps   |

| t <sub>PRE</sub>   | 100  |     | 100  |     | 114  |     | 135  |     | ps   |

| t <sub>CLKHL</sub> | 1000 |     | 1111 |     | 1190 |     | 1400 |     | ps   |

| Table 4–45. IOE Internal TSU Microparameter by Device Density (Part 1 of 2) |                   |     |     |     |     |     |     |     |     |    |

|-----------------------------------------------------------------------------|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|----|

| Device                                                                      |                   | -   | -5  |     | -6  |     | -7  |     | -8  |    |

|                                                                             | Symbol            | Min | Max | Min | Max | Min | Max | Min | Max |    |

| EP1S10                                                                      | t <sub>SU_R</sub> | 76  |     | 80  |     | 80  |     | 80  |     | ps |

|                                                                             | t <sub>SU_C</sub> | 176 |     | 80  |     | 80  |     | 80  |     | ps |

| EP1S20                                                                      | t <sub>SU_R</sub> | 76  |     | 80  |     | 80  |     | 80  |     | ps |

|                                                                             | t <sub>SU_C</sub> | 76  |     | 80  |     | 80  |     | 80  |     | ps |

| EP1S25                                                                      | t <sub>SU_R</sub> | 276 |     | 280 |     | 280 |     | 280 |     | ps |

|                                                                             | t <sub>su_c</sub> | 276 |     | 280 |     | 280 |     | 280 |     | ps |

| EP1S30                                                                      | t <sub>SU_R</sub> | 76  |     | 80  |     | 80  |     | 80  |     | ps |

|                                                                             | t <sub>SU_C</sub> | 176 |     | 180 |     | 180 |     | 180 |     | ps |

**Table 4–53. Stratix Regional Clock External I/O Timing Parameters (Part 2 of 2)** Notes (1), (2)

| Symbol Parameter   |                                                                                                                                           |  |  |  |  |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| t <sub>XZPLL</sub> | Synchronous IOE output enable register to output pin disable delay<br>using regional clock fed by Enhanced PLL with default phase setting |  |  |  |  |  |  |

| t <sub>ZXPLL</sub> | Synchronous IOE output enable register to output pin enable delay<br>using regional clock fed by Enhanced PLL with default phase setting  |  |  |  |  |  |  |

Notes to Table 4–53:

- (1) These timing parameters are sample-tested only.

- (2) These timing parameters are for column and row IOE pins. You should use the Quartus II software to verify the external timing for any pin.

Table 4–54 shows the external I/O timing parameters when using global clock networks.

| <b>Table 4-3</b><br>(2) | 54. Stratix Global Clock External I/O Timing Parameters Notes (1),                                                                    |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                  | Parameter                                                                                                                             |

| t <sub>INSU</sub>       | Setup time for input or bidirectional pin using IOE input register with global clock fed by ${\tt CLK}\xspace$ pin                    |

| t <sub>INH</sub>        | Hold time for input or bidirectional pin using IOE input register with global clock fed by CLK pin                                    |

| t <sub>outco</sub>      | Clock-to-output delay output or bidirectional pin using IOE output register with global clock fed by CLK pin                          |

| t <sub>INSUPLL</sub>    | Setup time for input or bidirectional pin using IOE input register with global clock fed by Enhanced PLL with default phase setting   |

| t <sub>INHPLL</sub>     | Hold time for input or bidirectional pin using IOE input register with global clock fed by Enhanced PLL with default phase setting    |

| t <sub>OUTCOPLL</sub>   | Clock-to-output delay output or bidirectional pin using IOE output register with global clock Enhanced PLL with default phase setting |

| t <sub>XZPLL</sub>      | Synchronous IOE output enable register to output pin disable delay using global clock fed by Enhanced PLL with default phase setting  |

| t <sub>ZXPLL</sub>      | Synchronous IOE output enable register to output pin enable delay using global clock fed by Enhanced PLL with default phase setting   |

#### Notes to Table 4–54:

- (1) These timing parameters are sample-tested only.

- (2) These timing parameters are for column and row IOE pins. You should use the Quartus II software to verify the external timing for any pin.

| Table 4–59. l         | Table 4–59. EP1S10 External I/O Timing on Row Pins Using Regional Clock Networks Note (1) |         |         |                |       |                |     |                |      |  |  |

|-----------------------|-------------------------------------------------------------------------------------------|---------|---------|----------------|-------|----------------|-----|----------------|------|--|--|

| Parameter             | -5 Spee                                                                                   | d Grade | -6 Spee | -6 Speed Grade |       | -7 Speed Grade |     | -8 Speed Grade |      |  |  |

|                       | Min                                                                                       | Max     | Min     | Max            | Min   | Max            | Min | Max            | Unit |  |  |

| t <sub>INSU</sub>     | 2.161                                                                                     |         | 2.336   |                | 2.685 |                | NA  |                | ns   |  |  |

| t <sub>INH</sub>      | 0.000                                                                                     |         | 0.000   |                | 0.000 |                | NA  |                | ns   |  |  |

| t <sub>outco</sub>    | 2.434                                                                                     | 4.889   | 2.434   | 5.226          | 2.434 | 5.643          | NA  | NA             | ns   |  |  |

| t <sub>XZ</sub>       | 2.461                                                                                     | 4.493   | 2.461   | 5.282          | 2.461 | 5.711          | NA  | NA             | ns   |  |  |

| t <sub>zx</sub>       | 2.461                                                                                     | 4.493   | 2.461   | 5.282          | 2.461 | 5.711          | NA  | NA             | ns   |  |  |

| t <sub>INSUPLL</sub>  | 1.057                                                                                     |         | 1.172   |                | 1.315 |                | NA  |                | ns   |  |  |

| t <sub>INHPLL</sub>   | 0.000                                                                                     |         | 0.000   |                | 0.000 |                | NA  |                | ns   |  |  |

| t <sub>OUTCOPLL</sub> | 1.327                                                                                     | 2.773   | 1.327   | 2.848          | 1.327 | 2.940          | NA  | NA             | ns   |  |  |

| t <sub>XZPLL</sub>    | 1.354                                                                                     | 2.827   | 1.354   | 2.904          | 1.354 | 3.008          | NA  | NA             | ns   |  |  |

| t <sub>ZXPLL</sub>    | 1.354                                                                                     | 2.827   | 1.354   | 2.904          | 1.354 | 3.008          | NA  | NA             | ns   |  |  |

| Table 4–60. I         | Table 4–60. EP1S10 External I/O Timing on Row Pins Using Global Clock Networks Note (1) |         |         |                |       |         |         |          |      |  |  |

|-----------------------|-----------------------------------------------------------------------------------------|---------|---------|----------------|-------|---------|---------|----------|------|--|--|

| Parameter             | -5 Spee                                                                                 | d Grade | -6 Spee | -6 Speed Grade |       | d Grade | -8 Spee | ed Grade | Unit |  |  |

|                       | Min                                                                                     | Max     | Min     | Max            | Min   | Max     | Min     | Max      | Unit |  |  |

| t <sub>INSU</sub>     | 1.787                                                                                   |         | 1.944   |                | 2.232 |         | NA      |          | ns   |  |  |

| t <sub>INH</sub>      | 0.000                                                                                   |         | 0.000   |                | 0.000 |         | NA      |          | ns   |  |  |

| t <sub>OUTCO</sub>    | 2.647                                                                                   | 5.263   | 2.647   | 5.618          | 2.647 | 6.069   | NA      | NA       | ns   |  |  |

| t <sub>xz</sub>       | 2.674                                                                                   | 5.317   | 2.674   | 5.674          | 2.674 | 6.164   | NA      | NA       | ns   |  |  |

| t <sub>ZX</sub>       | 2.674                                                                                   | 5.317   | 2.674   | 5.674          | 2.674 | 6.164   | NA      | NA       | ns   |  |  |

| t <sub>INSUPLL</sub>  | 1.371                                                                                   |         | 1.1472  |                | 1.654 |         | NA      |          | ns   |  |  |

| t <sub>INHPLL</sub>   | 0.000                                                                                   |         | 0.000   |                | 0.000 |         | NA      |          | ns   |  |  |

| t <sub>OUTCOPLL</sub> | 1.144                                                                                   | 2.459   | 1.144   | 2.548          | 1.144 | 2.601   | NA      | NA       | ns   |  |  |

| t <sub>XZPLL</sub>    | 1.171                                                                                   | 2.513   | 1.171   | 2.604          | 1.171 | 2.669   | NA      | NA       | ns   |  |  |

| t <sup>ZXPLL</sup>    | 1.171                                                                                   | 2.513   | 1.171   | 2.604          | 1.171 | 2.669   | NA      | NA       | ns   |  |  |

*Note to Tables* 4–55 *to* 4–60:

(1) Only EP1S25, EP1S30, and EP1S40 have speed grade of -8.

| Table 4–65. l         | Table 4–65. EP1S20 External I/O Timing on Row Pins Using Regional Clock Networks Note (1) |         |         |         |         |         |         |         |      |  |  |

|-----------------------|-------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|------|--|--|

| Parameter             | -5 Spee                                                                                   | d Grade | -6 Spee | d Grade | -7 Spee | d Grade | -8 Spee | d Grade | Unit |  |  |

|                       | Min                                                                                       | Max     | Min     | Max     | Min     | Max     | Min     | Max     | Unit |  |  |

| t <sub>INSU</sub>     | 1.815                                                                                     |         | 1.967   |         | 2.258   |         | NA      |         | ns   |  |  |

| t <sub>INH</sub>      | 0.000                                                                                     |         | 0.000   |         | 0.000   |         | NA      |         | ns   |  |  |

| t <sub>outco</sub>    | 2.633                                                                                     | 5.235   | 2.663   | 5.595   | 2.663   | 6.070   | NA      | NA      | ns   |  |  |

| t <sub>xz</sub>       | 2.660                                                                                     | 5.289   | 2.660   | 5.651   | 2.660   | 6.138   | NA      | NA      | ns   |  |  |

| t <sub>ZX</sub>       | 2.660                                                                                     | 5.289   | 2.660   | 5.651   | 2.660   | 6.138   | NA      | NA      | ns   |  |  |

| t <sub>INSUPLL</sub>  | 1.060                                                                                     |         | 1.112   |         | 1.277   |         | NA      |         | ns   |  |  |

| t <sub>INHPLL</sub>   | 0.000                                                                                     |         | 0.000   |         | 0.000   |         | NA      |         | ns   |  |  |

| t <sub>OUTCOPLL</sub> | 1.325                                                                                     | 2.770   | 1.325   | 2.908   | 1.325   | 2.978   | NA      | NA      | ns   |  |  |

| t <sub>XZPLL</sub>    | 1.352                                                                                     | 2.824   | 1.352   | 2.964   | 1.352   | 3.046   | NA      | NA      | ns   |  |  |

| t <sub>ZXPLL</sub>    | 1.352                                                                                     | 2.824   | 1.352   | 2.964   | 1.352   | 3.046   | NA      | NA      | ns   |  |  |

| Table 4–66. I         | Table 4–66. EP1S20 External I/O Timing on Row Pins Using Global Clock Networks Note (1) |         |         |                |       |         |         |          |      |  |  |

|-----------------------|-----------------------------------------------------------------------------------------|---------|---------|----------------|-------|---------|---------|----------|------|--|--|

| Parameter             | -5 Spee                                                                                 | d Grade | -6 Spee | -6 Speed Grade |       | d Grade | -8 Spee | ed Grade | Unit |  |  |

|                       | Min                                                                                     | Max     | Min     | Max            | Min   | Max     | Min     | Max      | Unit |  |  |

| t <sub>INSU</sub>     | 1.742                                                                                   |         | 1.887   |                | 2.170 |         | NA      |          | ns   |  |  |

| t <sub>INH</sub>      | 0.000                                                                                   |         | 0.000   |                | 0.000 |         | NA      |          | ns   |  |  |

| t <sub>outco</sub>    | 2.674                                                                                   | 5.308   | 2.674   | 5.675          | 2.674 | 6.158   | NA      | NA       | ns   |  |  |

| t <sub>XZ</sub>       | 2.701                                                                                   | 5.362   | 2.701   | 5.731          | 2.701 | 6.226   | NA      | NA       | ns   |  |  |

| t <sub>zx</sub>       | 2.701                                                                                   | 5.362   | 2.701   | 5.731          | 2.701 | 6.226   | NA      | NA       | ns   |  |  |

| t <sub>INSUPLL</sub>  | 1.353                                                                                   |         | 1.418   |                | 1.613 |         | NA      |          | ns   |  |  |

| t <sub>INHPLL</sub>   | 0.000                                                                                   |         | 0.000   |                | 0.000 |         | NA      |          | ns   |  |  |

| t <sub>OUTCOPLL</sub> | 1.158                                                                                   | 2.447   | 1.158   | 2.602          | 1.158 | 2.642   | NA      | NA       | ns   |  |  |

| t <sub>XZPLL</sub>    | 1.185                                                                                   | 2.531   | 1.158   | 2.602          | 1.185 | 2.710   | NA      | NA       | ns   |  |  |

| t <sub>ZXPLL</sub>    | 1.185                                                                                   | 2.531   | 1.158   | 2.602          | 1.185 | 2.710   | NA      | NA       | ns   |  |  |

*Note to Tables* 4–61 *to* 4–66:

(1) Only EP1S25, EP1S30, and EP1S40 have a speed grade of -8.

| Table 4–83. I         | Table 4–83. EP1S40 External I/O Timing on Row Pins Using Regional Clock Networks |         |         |                |       |                |       |                |      |  |  |

|-----------------------|----------------------------------------------------------------------------------|---------|---------|----------------|-------|----------------|-------|----------------|------|--|--|

| Parameter             | -5 Spee                                                                          | d Grade | -6 Spee | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |      |  |  |

|                       | Min                                                                              | Max     | Min     | Max            | Min   | Max            | Min   | Max            | Unit |  |  |

| t <sub>INSU</sub>     | 2.349                                                                            |         | 2.526   |                | 2.898 |                | 2.952 |                | ns   |  |  |

| t <sub>INH</sub>      | 0.000                                                                            |         | 0.000   |                | 0.000 |                | 0.000 |                | ns   |  |  |

| t <sub>outco</sub>    | 2.725                                                                            | 5.381   | 2.725   | 5.784          | 2.725 | 6.290          | 2.725 | 7.426          | ns   |  |  |

| t <sub>XZ</sub>       | 2.752                                                                            | 5.435   | 2.752   | 5.840          | 2.752 | 6.358          | 2.936 | 7.508          | ns   |  |  |

| t <sub>ZX</sub>       | 2.752                                                                            | 5.435   | 2.752   | 5.840          | 2.752 | 6.358          | 2.936 | 7.508          | ns   |  |  |

| t <sub>INSUPLL</sub>  | 1.328                                                                            |         | 1.322   |                | 1.605 |                | 1.883 |                | ns   |  |  |

| t <sub>INHPLL</sub>   | 0.000                                                                            |         | 0.000   |                | 0.000 |                | 0.000 |                | ns   |  |  |

| t <sub>OUTCOPLL</sub> | 1.169                                                                            | 2.502   | 1.169   | 2.698          | 1.169 | 2.650          | 1.169 | 2.691          | ns   |  |  |

| t <sub>XZPLL</sub>    | 1.196                                                                            | 2.556   | 1.196   | 2.754          | 1.196 | 2.718          | 1.196 | 2.773          | ns   |  |  |

| t <sub>ZXPLL</sub>    | 1.196                                                                            | 2.556   | 1.196   | 2.754          | 1.196 | 2.718          | 1.196 | 2.773          | ns   |  |  |

| Table 4–84. l         | Table 4–84. EP1S40 External I/O Timing on Row Pins Using Global Clock Networks |         |         |                |       |                |       |                |      |  |  |

|-----------------------|--------------------------------------------------------------------------------|---------|---------|----------------|-------|----------------|-------|----------------|------|--|--|

| Parameter             | -5 Spee                                                                        | d Grade | -6 Spee | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |      |  |  |

|                       | Min                                                                            | Max     | Min     | Max            | Min   | Max            | Min   | Max            | Unit |  |  |

| t <sub>INSU</sub>     | 2.020                                                                          |         | 2.171   |                | 2.491 |                | 2.898 |                | ns   |  |  |

| t <sub>INH</sub>      | 0.000                                                                          |         | 0.000   |                | 0.000 |                | 0.000 |                | ns   |  |  |

| t <sub>оитсо</sub>    | 2.912                                                                          | 5.710   | 2.912   | 6.139          | 2.912 | 6.697          | 2.931 | 7.480          | ns   |  |  |

| t <sub>xz</sub>       | 2.939                                                                          | 5.764   | 2.939   | 6.195          | 2.939 | 6.765          | 2.958 | 7.562          | ns   |  |  |

| t <sub>ZX</sub>       | 2.939                                                                          | 5.764   | 2.939   | 6.195          | 2.939 | 6.765          | 2.958 | 7.562          | ns   |  |  |

| t <sub>INSUPLL</sub>  | 1.370                                                                          |         | 1.368   |                | 1.654 |                | 1.881 |                | ns   |  |  |

| t <sub>INHPLL</sub>   | 0.000                                                                          |         | 0.000   |                | 0.000 |                | 0.000 |                | ns   |  |  |

| t <sub>OUTCOPLL</sub> | 1.144                                                                          | 2.460   | 1.144   | 2.652          | 1.144 | 2.601          | 1.170 | 2.693          | ns   |  |  |

| t <sub>XZPLL</sub>    | 1.171                                                                          | 2.514   | 1.171   | 2.708          | 1.171 | 2.669          | 1.197 | 2.775          | ns   |  |  |

| t <sub>ZXPLL</sub>    | 1.171                                                                          | 2.514   | 1.171   | 2.708          | 1.171 | 2.669          | 1.197 | 2.775          | ns   |  |  |

| Table 4–123. Stratix Ma<br>2, 3, 4] Pins in Wire-Bo | • |  |  | 0 Pins) for PLL[1, |  |  |  |  |  |

|-----------------------------------------------------|---|--|--|--------------------|--|--|--|--|--|

| I/O Standard -6 Speed -7 Speed -8 Speed             |   |  |  |                    |  |  |  |  |  |

| I/O Standard                     | Grade | Grade | Grade | Unit |

|----------------------------------|-------|-------|-------|------|

| LVDS (2)                         | 400   | 311   | 311   | MHz  |

| HyperTransport<br>technology (2) | 420   | 400   | 400   | MHz  |

Notes to Tables 4–120 through 4–123:

- (1) Differential SSTL-2 outputs are only available on column clock pins.

- (2) These parameters are only available on row I/O pins.

- (3) SSTL-2 in maximum drive strength condition. See Table 4–101 on page 4–62 for more information on exact loading conditions for each I/O standard.

- (4) SSTL-2 in minimum drive strength with  $\leq 10$  pF output load condition.

- (5) SSTL-2 in minimum drive strength with > 10pF output load condition.

- (6) Differential SSTL-2 outputs are only supported on column clock pins.

| Symbol            | Conditions                                                                   | -5 Speed Grade |     |      | -6 Speed Grade |     |      | -7 Speed Grade |     |      | -8 Speed Grade |     |      | Unit |

|-------------------|------------------------------------------------------------------------------|----------------|-----|------|----------------|-----|------|----------------|-----|------|----------------|-----|------|------|

|                   |                                                                              | Min            | Тур | Max  | Unit |

| t <sub>DUTY</sub> | LVDS ( $J = 2$<br>through 10)                                                | 47.5           | 50  | 52.5 | 47.5           | 50  | 52.5 | 47.5           | 50  | 52.5 | 47.5           | 50  | 52.5 | %    |

|                   | LVDS ( <i>J</i> = 1)<br>and LVPECL,<br>PCML,<br>HyperTransport<br>technology | 45             | 50  | 55   | 45             | 50  | 55   | 45             | 50  | 55   | 45             | 50  | 55   | %    |

| t <sub>LOCK</sub> | All                                                                          |                |     | 100  |                |     | 100  |                |     | 100  |                |     | 100  | μs   |

Notes to Table 4–125:

(1) When J = 4, 7, 8, and 10, the SERDES block is used.

(2) When J = 2 or J = 1, the SERDES is bypassed.