Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Obsolete                                                  |

| Number of LABs/CLBs            | 5712                                                      |

| Number of Logic Elements/Cells | 57120                                                     |

| Total RAM Bits                 | 5215104                                                   |

| Number of I/O                  | 773                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.425V ~ 1.575V                                           |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 1020-BBGA                                                 |

| Supplier Device Package        | 1020-FBGA (33x33)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s60f1020c6n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| DSP Block Interface                                                                                                                                                                                                                                                                                                                                              | 2–70                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| PLLs & Clock Networks                                                                                                                                                                                                                                                                                                                                            |                                           |

| Global & Hierarchical Clocking                                                                                                                                                                                                                                                                                                                                   | 2–73                                      |

| Enhanced & Fast PLLs                                                                                                                                                                                                                                                                                                                                             |                                           |

| Enhanced PLLs                                                                                                                                                                                                                                                                                                                                                    |                                           |

| Fast PLLs                                                                                                                                                                                                                                                                                                                                                        | 2–100                                     |

| I/O Structure                                                                                                                                                                                                                                                                                                                                                    | 2–104                                     |

| Double-Data Rate I/O Pins                                                                                                                                                                                                                                                                                                                                        |                                           |

| External RAM Interfacing                                                                                                                                                                                                                                                                                                                                         |                                           |

| Programmable Drive Strength                                                                                                                                                                                                                                                                                                                                      |                                           |

| Open-Drain Output                                                                                                                                                                                                                                                                                                                                                | 2–120                                     |

| Slew-Rate Control                                                                                                                                                                                                                                                                                                                                                | 2–120                                     |

| Bus Hold                                                                                                                                                                                                                                                                                                                                                         |                                           |

| Programmable Pull-Up Resistor                                                                                                                                                                                                                                                                                                                                    |                                           |

| Advanced I/O Standard Support                                                                                                                                                                                                                                                                                                                                    |                                           |

| Differential On-Chip Termination                                                                                                                                                                                                                                                                                                                                 |                                           |

| MultiVolt I/O Interface                                                                                                                                                                                                                                                                                                                                          |                                           |

| High-Speed Differential I/O Support                                                                                                                                                                                                                                                                                                                              |                                           |

| Dedicated Circuitry                                                                                                                                                                                                                                                                                                                                              |                                           |

| Byte Alignment                                                                                                                                                                                                                                                                                                                                                   |                                           |

| Power Sequencing & Hot Socketing                                                                                                                                                                                                                                                                                                                                 |                                           |

| IEEE Std. 1149.1 (JTAG) Boundary-Scan Support SignalTap II Embedded Logic Analyzer Configuration Operating Modes Configuring Stratix FPGAs with JRunner Configuration Schemes Partial Reconfiguration Remote Update Configuration Modes Stratix Automated Single Event Upset (SEU) Detection Custom-Built Circuitry Software Interface Temperature Sensing Diode | 3–5 3–5 3–5 3–7 3–7 3–7 3–7 3–8 3–12 3–13 |

| Chapter 4. DC & Switching Characteristics  Operating Conditions Power Consumption Timing Model Preliminary & Final Timing                                                                                                                                                                                                                                        | 4–17<br>4–19                              |

| Performance                                                                                                                                                                                                                                                                                                                                                      |                                           |

| Internal Timing Parameters                                                                                                                                                                                                                                                                                                                                       |                                           |

| External Timing Parameters                                                                                                                                                                                                                                                                                                                                       |                                           |

| Stratix External I/O Timing                                                                                                                                                                                                                                                                                                                                      |                                           |

| I/O Timing Measurement Methodology                                                                                                                                                                                                                                                                                                                               |                                           |

| External I/O Delay Parameters                                                                                                                                                                                                                                                                                                                                    |                                           |

#### 2. Stratix Architecture

\$51002-3.2

# Functional Description

Stratix® devices contain a two-dimensional row- and column-based architecture to implement custom logic. A series of column and row interconnects of varying length and speed provide signal interconnects between logic array blocks (LABs), memory block structures, and DSP blocks.

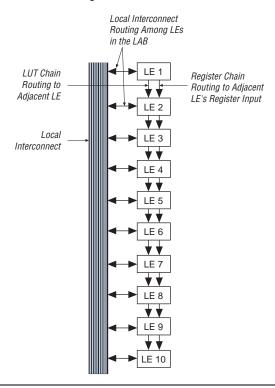

The logic array consists of LABs, with 10 logic elements (LEs) in each LAB. An LE is a small unit of logic providing efficient implementation of user logic functions. LABs are grouped into rows and columns across the device.

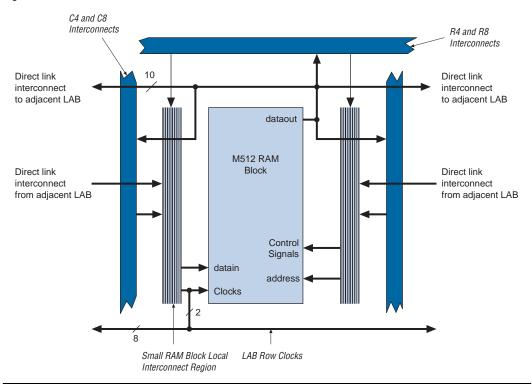

M512 RAM blocks are simple dual-port memory blocks with 512 bits plus parity (576 bits). These blocks provide dedicated simple dual-port or single-port memory up to 18-bits wide at up to 318 MHz. M512 blocks are grouped into columns across the device in between certain LABs.

M4K RAM blocks are true dual-port memory blocks with 4K bits plus parity (4,608 bits). These blocks provide dedicated true dual-port, simple dual-port, or single-port memory up to 36-bits wide at up to 291 MHz. These blocks are grouped into columns across the device in between certain LABs.

M-RAM blocks are true dual-port memory blocks with 512K bits plus parity (589,824 bits). These blocks provide dedicated true dual-port, simple dual-port, or single-port memory up to 144-bits wide at up to 269 MHz. Several M-RAM blocks are located individually or in pairs within the device's logic array.

Digital signal processing (DSP) blocks can implement up to either eight full-precision  $9\times 9$ -bit multipliers, four full-precision  $18\times 18$ -bit multipliers, or one full-precision  $36\times 36$ -bit multiplier with add or subtract features. These blocks also contain 18-bit input shift registers for digital signal processing applications, including FIR and infinite impulse response (IIR) filters. DSP blocks are grouped into two columns in each device.

Each Stratix device I/O pin is fed by an I/O element (IOE) located at the end of LAB rows and columns around the periphery of the device. I/O pins support numerous single-ended and differential I/O standards. Each IOE contains a bidirectional I/O buffer and six registers for registering input, output, and output-enable signals. When used with

Direct link interconnect from

left LAB, TriMatrix memory

block, DSP block, or IOE output

Direct link interconnect from

right LAB, TriMatrix memory

block, DSP block, or IOE output

Direct link interconnect from

right LAB, TriMatrix memory

block, DSP block, or IOE output

Direct link interconnect from

right LAB, TriMatrix memory

block, DSP block, or IOE output

Figure 2-3. Direct Link Connection

#### **LAB Control Signals**

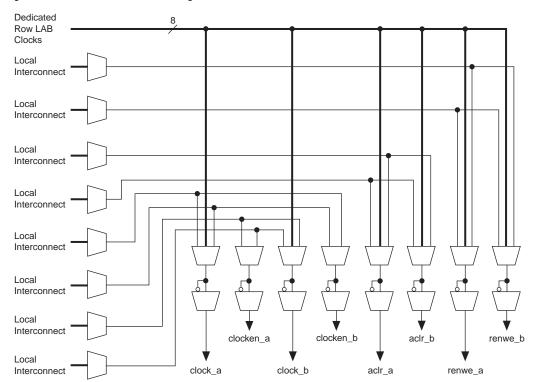

Each LAB contains dedicated logic for driving control signals to its LEs. The control signals include two clocks, two clock enables, two asynchronous clears, synchronous clear, asynchronous preset/load, synchronous load, and add/subtract control signals. This gives a maximum of 10 control signals at a time. Although synchronous load and clear signals are generally used when implementing counters, they can also be used with other functions.

Each LAB can use two clocks and two clock enable signals. Each LAB's clock and clock enable signals are linked. For example, any LE in a particular LAB using the labclk1 signal will also use labclkena1. If the LAB uses both the rising and falling edges of a clock, it also uses both LAB-wide clock signals. De-asserting the clock enable signal will turn off the LAB-wide clock.

Each LAB can use two asynchronous clear signals and an asynchronous load/preset signal. The asynchronous load acts as a preset when the asynchronous load data input is tied high.

asynchronous load, and clear signals. An asynchronous clear signal takes precedence if both signals are asserted simultaneously. Each LAB supports up to two clears and one preset signal.

In addition to the clear and preset ports, Stratix devices provide a chip-wide reset pin (DEV\_CLRn) that resets all registers in the device. An option set before compilation in the Quartus II software controls this pin. This chip-wide reset overrides all other control signals.

### MultiTrack Interconnect

In the Stratix architecture, connections between LEs, TriMatrix memory, DSP blocks, and device I/O pins are provided by the MultiTrack interconnect structure with DirectDrive technology. The MultiTrack interconnect consists of continuous, performance-optimized routing lines of different lengths and speeds used for inter- and intra-design block connectivity. The Quartus II Compiler automatically places critical design paths on faster interconnects to improve design performance.

DirectDrive technology is a deterministic routing technology that ensures identical routing resource usage for any function regardless of placement within the device. The MultiTrack interconnect and DirectDrive technology simplify the integration stage of block-based designing by eliminating the re-optimization cycles that typically follow design changes and additions.

The MultiTrack interconnect consists of row and column interconnects that span fixed distances. A routing structure with fixed length resources for all devices allows predictable and repeatable performance when migrating through different device densities. Dedicated row interconnects route signals to and from LABs, DSP blocks, and TriMatrix memory within the same row. These row resources include:

- Direct link interconnects between LABs and adjacent blocks.

- R4 interconnects traversing four blocks to the right or left.

- R8 interconnects traversing eight blocks to the right or left.

- R24 row interconnects for high-speed access across the length of the device.

The direct link interconnect allows an LAB, DSP block, or TriMatrix memory block to drive into the local interconnect of its left and right neighbors and then back into itself. Only one side of a M-RAM block interfaces with direct link and row interconnects. This provides fast communication between adjacent LABs and/or blocks without using row interconnect resources.

The R4 interconnects span four LABs, three LABs and one M512 RAM block, two LABs and one M4K RAM block, or two LABs and one DSP block to the right or left of a source LAB. These resources are used for fast

Figure 2-10. LUT Chain & Register Chain Interconnects

The C4 interconnects span four LABs, M512, or M4K blocks up or down from a source LAB. Every LAB has its own set of C4 interconnects to drive either up or down. Figure 2–11 shows the C4 interconnect connections from an LAB in a column. The C4 interconnects can drive and be driven by all types of architecture blocks, including DSP blocks, TriMatrix memory blocks, and vertical IOEs. For LAB interconnection, a primary LAB or its LAB neighbor can drive a given C4 interconnect. C4 interconnects can drive each other to extend their range as well as drive row interconnects for column-to-column connections.

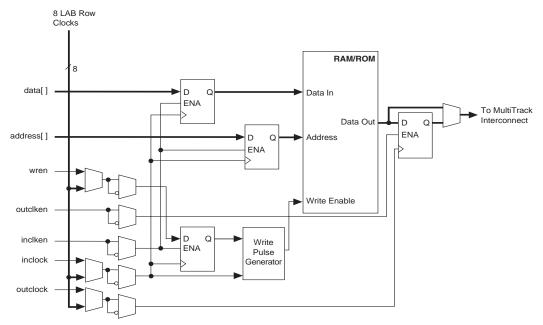

M512 RAM blocks can have different clocks on its inputs and outputs. The wren, datain, and write address registers are all clocked together from one of the two clocks feeding the block. The read address, rden, and output registers can be clocked by either of the two clocks driving the block. This allows the RAM block to operate in read/write or input/output clock modes. Only the output register can be bypassed. The eight labelk signals or local interconnect can drive the inclock, outclock, wren, rden, inclr, and outclr signals. Because of the advanced interconnect between the LAB and M512 RAM blocks, LEs can also control the wren and rden signals and the RAM clock, clock enable, and asynchronous clear signals. Figure 2–15 shows the M512 RAM block control signal generation logic.

The RAM blocks within Stratix devices have local interconnects to allow LEs and interconnects to drive into RAM blocks. The M512 RAM block local interconnect is driven by the R4, R8, C4, C8, and direct link interconnects from adjacent LABs. The M512 RAM blocks can communicate with LABs on either the left or right side through these row interconnects or with LAB columns on the left or right side with the column interconnects. Up to 10 direct link input connections to the M512 RAM block are possible from the left adjacent LABs and another 10 possible from the right adjacent LAB. M512 RAM outputs can also connect to left and right LABs through 10 direct link interconnects. The M512 RAM block has equal opportunity for access and performance to and from LABs on either its left or right side. Figure 2–16 shows the M512 RAM block to logic array interface.

Figure 2-16. M512 RAM Block LAB Row Interface

#### M4K RAM Blocks

The M4K RAM block includes support for true dual-port RAM. The M4K RAM block is used to implement buffers for a wide variety of applications such as storing processor code, implementing lookup schemes, and implementing larger memory applications. Each block contains 4,608 RAM bits (including parity bits). M4K RAM blocks can be configured in the following modes:

- True dual-port RAM

- Simple dual-port RAM

- Single-port RAM

- FIFO

- ROM

- Shift register

When configured as RAM or ROM, you can use an initialization file to pre-load the memory contents.

Figure 2-19. M-RAM Block Control Signals

One of the M-RAM block's horizontal sides drive the address and control signal (clock, renwe, byteena, etc.) inputs. Typically, the horizontal side closest to the device perimeter contains the interfaces. The one exception is when two M-RAM blocks are paired next to each other. In this case, the side of the M-RAM block opposite the common side of the two blocks contains the input interface. The top and bottom sides of any M-RAM block contain data input and output interfaces to the logic array. The top side has 72 data inputs and 72 data outputs for port B, and the bottom side has another 72 data inputs and 72 data outputs for port A. Figure 2–20 shows an example floorplan for the EP1S60 device and the location of the M-RAM interfaces.

#### **Single-Port Mode**

The memory blocks also support single-port mode, used when simultaneous reads and writes are not required. See Figure 2–28. A single block in a memory block can support up to two single-port mode RAM blocks in the M4K RAM blocks if each RAM block is less than or equal to 2K bits in size.

Figure 2–28. Single-Port Mode Note (1)

Note to Figure 2-28:

(1) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

The DSP block consists of the following elements:

- Multiplier block

- Adder/output block

#### **Multiplier Block**

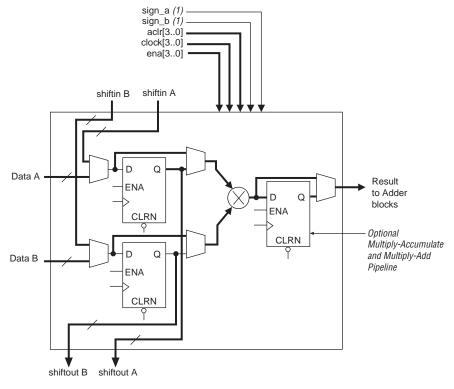

The DSP block multiplier block consists of the input registers, a multiplier, and pipeline register for pipelining multiply-accumulate and multiply-add/subtract functions as shown in Figure 2–32.

Figure 2-32. Multiplier Sub-Block within Stratix DSP Block

Note to Figure 2-32:

(1) These signals can be unregistered or registered once to match data path pipelines if required.

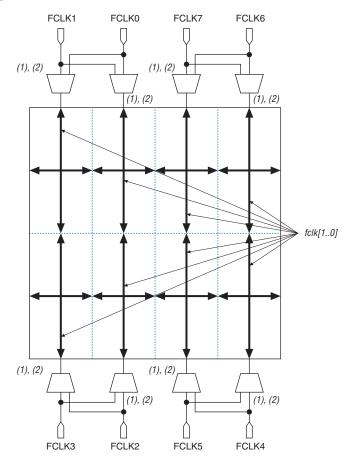

Figure 2–45. EP1S30 Device Fast Regional Clock Pin Connections to Fast Regional Clocks

Notes to Figure 2-45:

- (1) This is a set of two multiplexers.

- (2) In addition to the FCLK pin inputs, there is also an input from the I/O interconnect.

#### Combined Resources

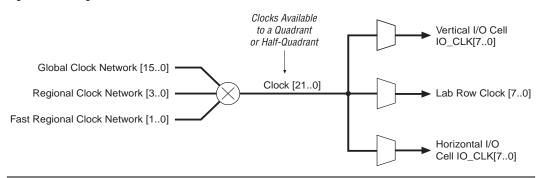

Within each region, there are 22 distinct dedicated clocking resources consisting of 16 global clock lines, four regional clock lines, and two fast regional clock lines. Multiplexers are used with these clocks to form eight bit busses to drive LAB row clocks, column IOE clocks, or row IOE clocks. Another multiplexer is used at the LAB level to select two of the eight row clocks to feed the LE registers within the LAB. See Figure 2–46.

Figure 2-46. Regional Clock Bus

IOE clocks have horizontal and vertical block regions that are clocked by eight I/O clock signals chosen from the 22 quadrant or half-quadrant clock resources. Figures 2–47 and 2–48 show the quadrant and half-quadrant relationship to the I/O clock regions, respectively. The vertical regions (column pins) have less clock delay than the horizontal regions (row pins).

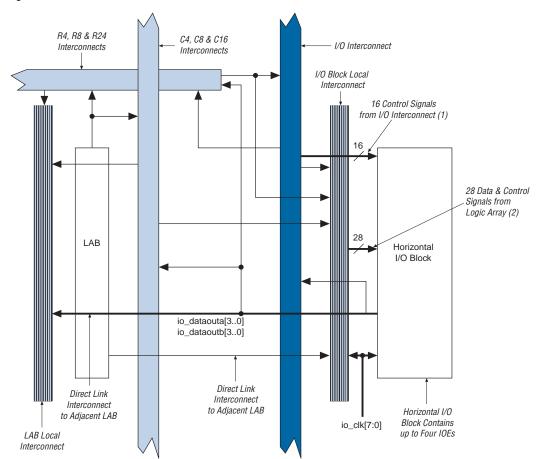

Figure 2-60. Row I/O Block Connection to the Interconnect

#### *Notes to Figure 2–60:*

- (1) The 16 control signals are composed of four output enables io\_boe[3..0], four clock enables io\_boe[3..0], four clocks io\_clk[3..0], and four clear signals io\_bclr[3..0].

- (2) The 28 data and control signals consist of eight data out lines: four lines each for DDR applications io\_dataouta[3..0] and io\_dataoutb[3..0], four output enables io\_coe[3..0], four input clock enables io\_cce\_in[3..0], four output clock enables io\_cce\_out[3..0], four clocks io\_cclk[3..0], and four clear signals io\_cclr[3..0].

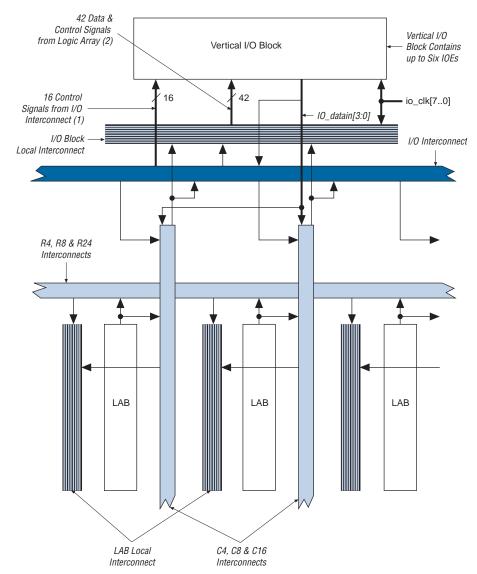

Figure 2-61. Column I/O Block Connection to the Interconnect

#### Notes to Figure 2-61:

- (1) The 16 control signals are composed of four output enables io\_boe[3..0], four clock enables io\_boe[3..0], four clocks io\_bclk[3..0], and four clear signals io\_bclr[3..0].

- (2) The 42 data and control signals consist of 12 data out lines; six lines each for DDR applications io\_dataouta[5..0] and io\_dataoutb[5..0], six output enables io\_coe[5..0], six input clock enables io\_cce\_in[5..0], six output clock enables io\_cce\_out[5..0], six clocks io\_cclk[5..0], and six clear signals io cclr[5..0].

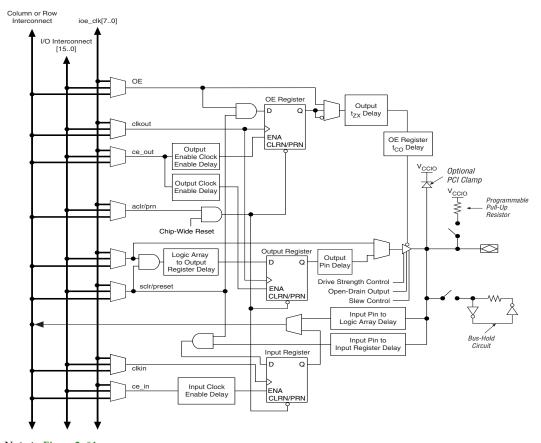

Figure 2–64. Stratix IOE in Bidirectional I/O Configuration Note (1)

Note to Figure 2-64:

(1) All input signals to the IOE can be inverted at the IOE.

The Stratix device IOE includes programmable delays that can be activated to ensure zero hold times, input IOE register-to-logic array register transfers, or logic array-to-output IOE register transfers.

A path in which a pin directly drives a register may require the delay to ensure zero hold time, whereas a path in which a pin drives a register through combinatorial logic may not require the delay. Programmable delays exist for decreasing input-pin-to-logic-array and IOE input register delays. The Quartus II Compiler can program these delays to automatically minimize setup time while providing a zero hold time. Programmable delays can increase the register-to-pin delays for output

The only way you can use the rx\_data\_align is if one of the following is true:

- The receiver PLL is only clocking receive channels (no resources for the transmitter)

- If all channels can fit in one I/O bank

| Table 2-38            | . EP1S30 Diffe  | erential Cha            | nnels Note      | (1)       |           |           |           |                           |      |      |        |

|-----------------------|-----------------|-------------------------|-----------------|-----------|-----------|-----------|-----------|---------------------------|------|------|--------|

|                       | Transmitter     | Total                   | Maximum         | C         | enter F   | ast PLI   | _S        | Corner Fast PLLs (2), (3) |      |      |        |

| Package               | /Receiver       | Channels                | Speed<br>(Mbps) | PLL1      | PLL2      | PLL3      | PLL4      | PLL7                      | PLL8 | PLL9 | PLL10  |

| 780-pin               | Transmitter     | 70                      | 840             | 18        | 17        | 17        | 18        | (6)                       | (6)  | (6)  | (6)    |

| FineLine<br>BGA       | (4)             |                         | 840 (5)         | 35        | 35        | 35        | 35        | (6)                       | (6)  | (6)  | (6)    |

|                       | Receiver        | 66                      | 840             | 17        | 16        | 16        | 17        | (6)                       | (6)  | (6)  | (6)    |

|                       |                 |                         | 840 (5)         | 33        | 33        | 33        | 33        | (6)                       | (6)  | (6)  | (6)    |

| 956-pin               | Transmitter     | 80                      | 840             | 19        | 20        | 20        | 19        | 20                        | 20   | 20   | 20     |

| BGA                   | (4)             |                         | 840 (5)         | 39        | 39        | 39        | 39        | 20                        | 20   | 20   | 20     |

|                       | Receiver        | 80                      | 840             | 20        | 20        | 20        | 20        | 19                        | 20   | 20   | 19     |

|                       |                 |                         | 840 (5)         | 40        | 40        | 40        | 40        | 19                        | 20   | 20   | 19     |

| 1,020-pin<br>FineLine | Transmitter (4) | 80 (2) (7)              | 840             | 19<br>(1) | 20        | 20        | 19<br>(1) | 20                        | 20   | 20   | 20     |

| BGA                   |                 |                         | 840 (5),(8)     | 39<br>(1) | 39<br>(1) | 39<br>(1) | 39<br>(1) | 20                        | 20   | 20   | 20     |

|                       | Receiver        | eiver 80 (2) <i>(7)</i> | 840             | 20        | 20        | 20        | 20        | 19 (1)                    | 20   | 20   | 19 (1) |

|                       |                 |                         | 840 (5),(8)     | 40        | 40        | 40        | 40        | 19 (1)                    | 20   | 20   | 19 (1) |

| Table 2-39      | Table 2–39. EP1S40 Differential Channels (Part 1 of 2) Note (1) |          |                 |      |      |      |      |      |                           |      |       |  |

|-----------------|-----------------------------------------------------------------|----------|-----------------|------|------|------|------|------|---------------------------|------|-------|--|

| Dookogo         | Transmitter/ Tota                                               |          | Maximum         |      |      |      |      |      | Corner Fast PLLs (2), (3) |      |       |  |

| Package         | Receiver                                                        | Channels | Speed<br>(Mbps) | PLL1 | PLL2 | PLL3 | PLL4 | PLL7 | PLL8                      | PLL9 | PLL10 |  |

| 780-pin         |                                                                 | 68       | 840             | 18   | 16   | 16   | 18   | (6)  | (6)                       | (6)  | (6)   |  |

| FineLine<br>BGA | (4)                                                             |          | 840 (5)         | 34   | 34   | 34   | 34   | (6)  | (6)                       | (6)  | (6)   |  |

|                 | Receiver                                                        | 66       | 840             | 17   | 16   | 16   | 17   | (6)  | (6)                       | (6)  | (6)   |  |

|                 |                                                                 |          | 840 (5)         | 33   | 33   | 33   | 33   | (6)  | (6)                       | (6)  | (6)   |  |

- RapidIO

- HyperTransport

#### **Dedicated Circuitry**

Stratix devices support source-synchronous interfacing with LVDS, LVPECL, 3.3-V PCML, or HyperTransport signaling at up to 840 Mbps. Stratix devices can transmit or receive serial channels along with a low-speed or high-speed clock. The receiving device PLL multiplies the clock by a integer factor W (W = 1 through 32). For example, a HyperTransport application where the data rate is 800 Mbps and the clock rate is 400 MHz would require that W be set to 2. The SERDES factor J determines the parallel data width to deserialize from receivers or to serialize for transmitters. The SERDES factor J can be set to 4, 7, 8, or 10 and does not have to equal the PLL clock-multiplication W value. For a J factor of 1, the Stratix device bypasses the SERDES block. For a J factor of 2, the Stratix device bypasses the SERDES block, and the DDR input and output registers are used in the IOE. See Figure 2–73.

R4, R8, and R24 Interconnect 840 Mbps 840 Mbps 8 Data Dedicated Dedicated Local Receiver Transmitter Interconnect Interface Interface rx load en 8× 8× 105 MHz Fast tx\_load\_en PLL Regional or global clock

Figure 2–73. High-Speed Differential I/O Receiver / Transmitter Interface Example

An external pin or global or regional clock can drive the fast PLLs, which can output up to three clocks: two multiplied high-speed differential I/O clocks to drive the SERDES block and/or external pin, and a low-speed clock to drive the logic array.

| Symbol            | Parameter                 | Conditions                  | Minimum                    | Typical | Maximum                     | Unit |

|-------------------|---------------------------|-----------------------------|----------------------------|---------|-----------------------------|------|

| V <sub>CCIO</sub> | Output supply voltage     |                             | 3.0                        |         | 3.6                         | V    |

| V <sub>IH</sub>   | High-level input voltage  |                             | 0.5 ×<br>V <sub>CCIO</sub> |         | V <sub>CCIO</sub> + 0.5     | V    |

| V <sub>IL</sub>   | Low-level input voltage   |                             | -0.5                       |         | 0.35 ×<br>V <sub>CCIO</sub> | V    |

| V <sub>IPU</sub>  | Input pull-up voltage     |                             | 0.7 ×<br>V <sub>CCIO</sub> |         |                             | V    |

| V <sub>OH</sub>   | High-level output voltage | $I_{OUT} = -500 \mu A$      | 0.9 ×<br>V <sub>CCIO</sub> |         |                             | V    |

| V <sub>OL</sub>   | Low-level output voltage  | I <sub>OUT</sub> = 1,500 μA |                            |         | 0.1 ×<br>V <sub>CCIO</sub>  | V    |

| Table 4–16.      | Table 4–16. GTL+ I/O Specifications |                             |                        |         |                        |      |  |  |  |  |  |

|------------------|-------------------------------------|-----------------------------|------------------------|---------|------------------------|------|--|--|--|--|--|

| Symbol           | Parameter                           | Conditions                  | Minimum                | Typical | Maximum                | Unit |  |  |  |  |  |

| $V_{TT}$         | Termination voltage                 |                             | 1.35                   | 1.5     | 1.65                   | V    |  |  |  |  |  |

| V <sub>REF</sub> | Reference voltage                   |                             | 0.88                   | 1.0     | 1.12                   | V    |  |  |  |  |  |

| V <sub>IH</sub>  | High-level input voltage            |                             | V <sub>REF</sub> + 0.1 |         |                        | V    |  |  |  |  |  |

| V <sub>IL</sub>  | Low-level input voltage             |                             |                        |         | V <sub>REF</sub> - 0.1 | V    |  |  |  |  |  |

| V <sub>OL</sub>  | Low-level output voltage            | I <sub>OL</sub> = 34 mA (3) |                        |         | 0.65                   | V    |  |  |  |  |  |

| Table 4–17. GTL I/O Specifications |                          |                             |                         |         |                         |      |  |  |  |  |

|------------------------------------|--------------------------|-----------------------------|-------------------------|---------|-------------------------|------|--|--|--|--|

| Symbol                             | Parameter                | Conditions                  | Minimum                 | Typical | Maximum                 | Unit |  |  |  |  |

| $V_{TT}$                           | Termination voltage      |                             | 1.14                    | 1.2     | 1.26                    | V    |  |  |  |  |

| $V_{REF}$                          | Reference voltage        |                             | 0.74                    | 0.8     | 0.86                    | V    |  |  |  |  |

| V <sub>IH</sub>                    | High-level input voltage |                             | V <sub>REF</sub> + 0.05 |         |                         | V    |  |  |  |  |

| V <sub>IL</sub>                    | Low-level input voltage  |                             |                         |         | V <sub>REF</sub> – 0.05 | V    |  |  |  |  |

| V <sub>OL</sub>                    | Low-level output voltage | I <sub>OL</sub> = 40 mA (3) |                         |         | 0.4                     | V    |  |  |  |  |

#### **Performance**

Table 4–36 shows Stratix performance for some common designs. All performance values were obtained with Quartus II software compilation of LPM, or MegaCore $^{\rm @}$  functions for the FIR and FFT designs.

| Table 4-36                       | . Stratix Performance (              | Part 1 | of 2) Notes | 5 (1), (2)    |                      |                      |                      |                      |       |

|----------------------------------|--------------------------------------|--------|-------------|---------------|----------------------|----------------------|----------------------|----------------------|-------|

|                                  |                                      | F      | Resources L | Jsed          |                      | P                    | erforman             | ce                   |       |

| ļ                                | Applications                         |        |             | DSP<br>Blocks | -5<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade | Units |

| LE                               | 16-to-1 multiplexer (1)              | 22     | 0           | 0             | 407.83               | 324.56               | 288.68               | 228.67               | MHz   |

|                                  | 32-to-1 multiplexer (3)              | 46     | 0           | 0             | 318.26               | 255.29               | 242.89               | 185.18               | MHz   |

|                                  | 16-bit counter                       | 16     | 0           | 0             | 422.11               | 422.11               | 390.01               | 348.67               | MHz   |

|                                  | 64-bit counter                       | 64     | 0           | 0             | 321.85               | 290.52               | 261.23               | 220.5                | MHz   |

| TriMatrix<br>memory              | Simple dual-port RAM 32 × 18 bit     | 0      | 1           | 0             | 317.76               | 277.62               | 241.48               | 205.21               | MHz   |

| M512 block                       | FIFO 32 × 18 bit                     | 30     | 1           | 0             | 319.18               | 278.86               | 242.54               | 206.14               | MHz   |

| TriMatrix<br>memory<br>M4K block | Simple dual-port RAM<br>128 × 36 bit | 0      | 1           | 0             | 290.86               | 255.55               | 222.27               | 188.89               | MHz   |

|                                  | True dual-port RAM<br>128 × 18 bit   | 0      | 1           | 0             | 290.86               | 255.55               | 222.27               | 188.89               | MHz   |

|                                  | FIFO 128 × 36 bit                    | 34     | 1           | 0             | 290.86               | 255.55               | 222.27               | 188.89               | MHz   |

| TriMatrix memory                 | Single port<br>RAM 4K × 144 bit      | 1      | 1           | 0             | 255.95               | 223.06               | 194.06               | 164.93               | MHz   |

| M-RAM<br>block                   | Simple dual-port<br>RAM 4K × 144 bit | 0      | 1           | 0             | 255.95               | 233.06               | 194.06               | 164.93               | MHz   |

|                                  | True dual-port<br>RAM 4K × 144 bit   | 0      | 1           | 0             | 255.95               | 233.06               | 194.06               | 164.93               | MHz   |

|                                  | Single port<br>RAM 8K × 72 bit       | 0      | 1           | 0             | 278.94               | 243.19               | 211.59               | 179.82               | MHz   |

|                                  | Simple dual-port<br>RAM 8K × 72 bit  | 0      | 1           | 0             | 255.95               | 223.06               | 194.06               | 164.93               | MHz   |

|                                  | True dual-port<br>RAM 8K × 72 bit    | 0      | 1           | 0             | 255.95               | 223.06               | 194.06               | 164.93               | MHz   |

|                                  | Single port<br>RAM 16K × 36 bit      | 0      | 1           | 0             | 280.66               | 254.32               | 221.28               | 188.00               | MHz   |

|                                  | Simple dual-port<br>RAM 16K × 36 bit | 0      | 1           | 0             | 269.83               | 237.69               | 206.82               | 175.74               | MHz   |

| Parameter                   |       | -5 Spee | ed Grade | -6 Spee | -6 Speed Grade |     | ed Grade | -8 Speed Grade |       | Unit  |

|-----------------------------|-------|---------|----------|---------|----------------|-----|----------|----------------|-------|-------|

| Falalli                     | GIGI  | Min     | Max      | Min     | Max            | Min | Max      | Min            | Max   | Uiiit |

| 1.5-V LVTTL                 | 2 mA  |         | 5,460    |         | 5,733          |     | 5,733    |                | 5,733 | ps    |

|                             | 4 mA  |         | 2,690    |         | 2,824          |     | 2,824    |                | 2,824 | ps    |

|                             | 8 mA  |         | 1,398    |         | 1,468          |     | 1,468    |                | 1,468 | ps    |

| GTL+                        |       |         | 6        |         | 6              |     | 6        |                | 6     | ps    |

| CTT                         |       |         | 845      |         | 887            |     | 887      |                | 887   | ps    |

| SSTL-3 Class                | I     |         | 638      |         | 670            |     | 670      |                | 670   | ps    |

| SSTL-3 Class                | II    |         | 144      |         | 151            |     | 151      |                | 151   | ps    |

| SSTL-2 Class                | I     |         | 604      |         | 634            |     | 634      |                | 634   | ps    |

| SSTL-2 Class                | II    |         | 211      |         | 221            |     | 221      |                | 221   | ps    |

| SSTL-18 Class               | s I   |         | 955      |         | 1,002          |     | 1,002    |                | 1,002 | ps    |

| 1.5-V HSTL CI               | ass I |         | 733      |         | 769            |     | 769      |                | 769   | ps    |

| 1.8-V HSTL CI               | ass I |         | 372      |         | 390            |     | 390      |                | 390   | ps    |

| LVDS                        |       |         | -196     |         | -206           |     | -206     |                | -206  | ps    |

| LVPECL                      |       |         | -148     |         | -156           |     | -156     |                | -156  | ps    |

| PCML                        |       |         | -147     |         | -155           |     | -155     |                | -155  | ps    |

| HyperTranspor<br>technology | t     |         | -93      |         | -98            |     | -98      |                | -98   | ps    |

Note to Table 4–103 through 4–106:

<sup>(1)</sup> These parameters are only available on row I/O pins.

| Table 4–107. Stratix I/O Standard Output Delay Adders for Slow Slew Rate on Column Pins (Part 1 of 2) |       |         |         |         |         |         |         |         |         |       |

|-------------------------------------------------------------------------------------------------------|-------|---------|---------|---------|---------|---------|---------|---------|---------|-------|

|                                                                                                       |       | -5 Spee | d Grade | -6 Spee | d Grade | -7 Spee | d Grade | -8 Spee | d Grade | llmit |

| Parame                                                                                                | eler  | Min     | Max     | Min     | Max     | Min     | Max     | Min     | Max     | Unit  |

| LVCMOS                                                                                                | 2 mA  |         | 1,822   |         | 1,913   |         | 1,913   |         | 1,913   | ps    |

|                                                                                                       | 4 mA  |         | 684     |         | 718     |         | 718     |         | 718     | ps    |

|                                                                                                       | 8 mA  |         | 233     |         | 245     |         | 245     |         | 245     | ps    |

|                                                                                                       | 12 mA |         | 1       |         | 1       |         | 1       |         | 1       | ps    |

|                                                                                                       | 24 mA |         | -608    |         | -638    |         | -638    |         | -638    | ps    |