Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 5712                                                     |

| Number of Logic Elements/Cells | 57120                                                    |

| Total RAM Bits                 | 5215104                                                  |

| Number of I/O                  | 773                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 1020-BBGA                                                |

| Supplier Device Package        | 1020-FBGA (33x33)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s60f1020c7 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Section I. Stratix Device Family Data Sheet

This section provides the data sheet specifications for Stratix® devices. They contain feature definitions of the internal architecture, configuration and JTAG boundary-scan testing information, DC operating conditions, AC timing parameters, a reference to power consumption, and ordering information for Stratix devices.

This section contains the following chapters:

- Chapter 1, Introduction

- Chapter 2, Stratix Architecture

- Chapter 3, Configuration & Testing

- Chapter 4, DC & Switching Characteristics

- Chapter 5, Reference & Ordering Information

#### **Revision History**

The table below shows the revision history for Chapters 1 through 5.

| Chapter | Date/Version         | Changes Made                                                                                                                                                                                                                                                                                                                     |

|---------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | July 2005, v3.2      | Minor content changes.                                                                                                                                                                                                                                                                                                           |

|         | September 2004, v3.1 | Updated Table 1–6 on page 1–5.                                                                                                                                                                                                                                                                                                   |

|         | April 2004, v3.0     | <ul> <li>Main section page numbers changed on first page.</li> <li>Changed PCI-X to PCI-X 1.0 in "Features" on page 1–2.</li> <li>Global change from SignalTap to SignalTap II.</li> <li>The DSP blocks in "Features" on page 1–2 provide dedicated implementation of multipliers that are now "faster than 300 MHz."</li> </ul> |

|         | January 2004, v2.2   | Updated -5 speed grade device information in Table 1-6.                                                                                                                                                                                                                                                                          |

|         | October 2003, v2.1   | Add -8 speed grade device information.                                                                                                                                                                                                                                                                                           |

|         | July 2003, v2.0      | Format changes throughout chapter.                                                                                                                                                                                                                                                                                               |

Altera Corporation Section I–1

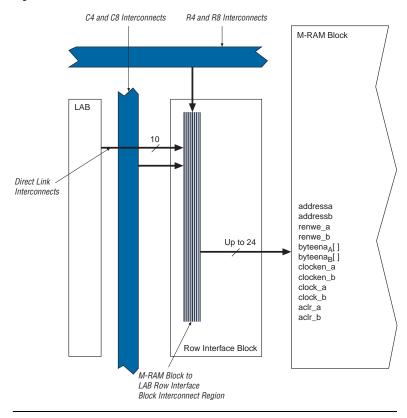

Figure 2–22. M-RAM Row Unit Interface to Interconnect

### Digital Signal Processing Block

The most commonly used DSP functions are finite impulse response (FIR) filters, complex FIR filters, infinite impulse response (IIR) filters, fast Fourier transform (FFT) functions, direct cosine transform (DCT) functions, and correlators. All of these blocks have the same fundamental building block: the multiplier. Additionally, some applications need specialized operations such as multiply-add and multiply-accumulate operations. Stratix devices provide DSP blocks to meet the arithmetic requirements of these functions.

Each Stratix device has two columns of DSP blocks to efficiently implement DSP functions faster than LE-based implementations. Larger Stratix devices have more DSP blocks per column (see Table 2–13). Each DSP block can be configured to support up to:

- Eight 9 × 9-bit multipliers

- Four 18 × 18-bit multipliers

- One 36 × 36-bit multiplier

As indicated, the Stratix DSP block can support one  $36 \times 36$ -bit multiplier in a single DSP block. This is true for any matched sign multiplications (either unsigned by unsigned or signed by signed), but the capabilities for dynamic and mixed sign multiplications are handled differently. The following list provides the largest functions that can fit into a single DSP block.

- 36 × 36-bit unsigned by unsigned multiplication

- 36 × 36-bit signed by signed multiplication

- 35 × 36-bit unsigned by signed multiplication

- 36 × 35-bit signed by unsigned multiplication

- 36 × 35-bit signed by dynamic sign multiplication

- 35 × 36-bit dynamic sign by signed multiplication

- 35 × 36-bit unsigned by dynamic sign multiplication

- 36 × 35-bit dynamic sign by unsigned multiplication

- 35 x 35-bit dynamic sign multiplication when the sign controls for each operand are different

- $36 \times 36$ -bit dynamic sign multiplication when the same sign control is used for both operands

This list only shows functions that can fit into a single DSP block. Multiple DSP blocks can support larger multiplication functions.

Figure 2–29 shows one of the columns with surrounding LAB rows.

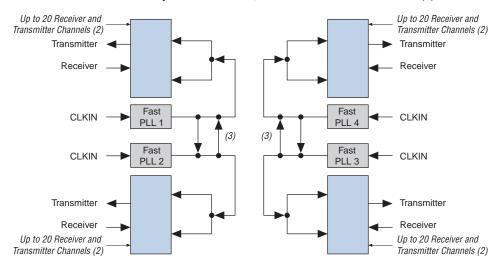

*Note to Figure 2–42:*

(1) The corner fast PLLs can also be driven through the global or regional clock networks. The global or regional clock input to the fast PLL can be driven by an output from another PLL, a pin-driven global or regional clock, or internallygenerated global signals.

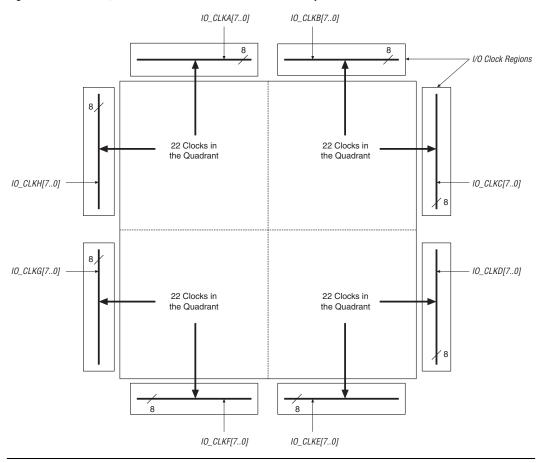

#### Regional Clock Network

There are four regional clock networks within each quadrant of the Stratix device that are driven by the same dedicated CLK[15..0] input pins or from PLL outputs. From a top view of the silicon, RCLK [0..3] are in the top left quadrant, RCLK[8..11] are in the top-right quadrant, RCLK[4..7] are in the bottom-left quadrant, and RCLK[12..15] are in the bottom-right quadrant. The regional clock networks only pertain to the quadrant they drive into. The regional clock networks provide the lowest clock delay and skew for logic contained within a single quadrant. RCLK cannot be driven by internal logic. The CLK clock pins symmetrically drive the RCLK networks within a particular quadrant, as shown in Figure 2–43. See Figures 2–50 and 2–51 for RCLK connections from PLLs and CLK pins.

Figure 2-47. EP1S10, EP1S20 & EP1S25 Device I/O Clock Groups

☐ FPLL9CLK

Figure 2–50. Global & Regional Clock Connections from Side Pins & Fast PLL Outputs Note (1), (2) RCLK1 RCLK9 G1 G3 G8 G10 G2 🛕 RCLK0 ▲ G0 🛕 G9 ▲ G11 ▲ RCLK8 ▲ FPLL7CLK \_ ☐ FPLL10CLK 10 10 PLL 7 /1 /1 PLL 10 *g*0 *g*0 ☐ CLK10 CLK0 [ 10 10 CLK1 □ ☐ CLK11 PLL 1 /1 /1 PLL 4 *g*0 *g*0 □ CLK8 CLK2 CLK3 10 10 /1 PLL 3 PII 2 /1 g0 g0

Figure 2–50 shows the global and regional clocking from the PLL outputs and the CLK pins.

*Notes to Figure 2–50:*

FPLL8CLK \_\_

PLL 8 /1

g0

(1) PLLs 1 to 4 and 7 to 10 are fast PLLs. PLLs 5, 6, 11, and 12 are enhanced PLLs.

RCLK4

RCLK5

Regional

Clocks

(2) The global or regional clocks in a fast PLL's quadrant can drive the fast PLL input. A pin or other PLL must drive the global or regional source. The source cannot be driven by internally generated logic before driving the fast PLL.

Global

Clocks

Figure 2–51 shows the global and regional clocking from enhanced PLL outputs and top CLK pins.

RCLK14

RCLK15

Regional

Clocks

/1 PLL 9

PLL5\_OUT[3..0] CLK14 (1) PLL5\_FB CLK15(2) CLK12 (1) CLK13 (2) E[0..3] PLL 5 PLL 11 L0 L1 G0 G1 G2 G3 G0 G1 G2 G3 L0 L1 → PLL11\_OUT ► RCLK10 ► RCLK11 Regional RCLK2 ◀ Clocks RCLK3 G12 G13 G14 G15 Global Clocks G4 G5 G6 Regional 5 RCLK6 Clocks RCLK7 ◀ RCLK12 RCLK13 → PLL12\_OUT L0 L1 G0 G1 G2 G3 G0 G1 G2 G3 L0 L1 PLL 6 PLL 12 PLL6\_OUT[3..0] PLL6\_FB \(^ CLK6 (1) CLK7 (2) CLK4 (1) CLK5(2)

Figure 2–51. Global & Regional Clock Connections from Top Clock Pins & Enhanced PLL Outputs Note (1)

#### Notes to Figure 2-51:

- (1) PLLs 1 to 4 and 7 to 10 are fast PLLs. PLLs 5, 6, 11, and 12 are enhanced PLLs.

- (2) CLK4, CLK6, CLK12, and CLK14 feed the corresponding PLL's inclk0 port.

- (3) CLK5, CLK7, CLK13, and CLK15 feed the corresponding PLL's inclk1 port.

- (4) The EP1S40 device in the 780-pin FineLine BGA package does not support PLLs 11 and 12.

#### Clock Feedback

The following four feedback modes in Stratix device enhanced PLLs allow multiplication and/or phase and delay shifting:

- Zero delay buffer: The external clock output pin is phase-aligned with the clock input pin for zero delay. Altera recommends using the same I/O standard on the input clock and the output clocks for optimum performance.

- External feedback: The external feedback input pin, FBIN, is phase-aligned with the clock input, CLK, pin. Aligning these clocks allows you to remove clock delay and skew between devices. This mode is only possible for PLLs 5 and 6. PLLs 5 and 6 each support feedback for one of the dedicated external outputs, either one single-ended or one differential pair. In this mode, one *e* counter feeds back to the PLL FBIN input, becoming part of the feedback loop. Altera recommends using the same I/O standard on the input clock, the FBIN pin, and the output clocks for optimum performance.

- Normal mode: If an internal clock is used in this mode, it is phasealigned to the input clock pin. The external clock output pin will have a phase delay relative to the clock input pin if connected in this mode. You define which internal clock output from the PLL should be phase-aligned to the internal clock pin.

- No compensation: In this mode, the PLL will not compensate for any clock networks or external clock outputs.

#### Phase & Delay Shifting

Stratix device enhanced PLLs provide advanced programmable phase and clock delay shifting. These parameters are set in the Quartus II software.

#### Phase Delay

The Quartus II software automatically sets the phase taps and counter settings according to the phase shift entry. You enter a desired phase shift and the Quartus II software automatically sets the closest setting achievable. This type of phase shift is not reconfigurable during system operation. For phase shifting, enter a phase shift (in degrees or time units) for each PLL clock output port or for all outputs together in one shift. You can select phase-shifting values in time units with a resolution of 156.25 to 416.66 ps. This resolution is a function of frequency input and the multiplication and division factors (that is, it is a function of the VCO period), with the finest step being equal to an eighth (×0.125) of the VCO period. Each clock output counter can choose a different phase of the

#### External Clock Inputs

Each fast PLL supports single-ended or differential inputs for source synchronous transmitters or for general-purpose use. Source-synchronous receivers support differential clock inputs. The fast PLL inputs are fed by CLK [0..3], CLK [8..11], and FPLL [7..10] CLK pins, as shown in Figure 2–50 on page 2–85.

Table 2–22 shows the I/O standards supported by fast PLL input pins.

| Table 2–22. Fast PLL Port I/O Stan | dards (Part 1 of 2) |           |

|------------------------------------|---------------------|-----------|

| I/O Ctondovd                       | li li               | nput      |

| I/O Standard                       | INCLK               | PLLENABLE |

| LVTTL                              | ✓                   | ✓         |

| LVCMOS                             | ✓                   | ✓         |

| 2.5 V                              | ✓                   |           |

| 1.8 V                              | ✓                   |           |

| 1.5 V                              | ✓                   |           |

| 3.3-V PCI                          |                     |           |

| 3.3-V PCI-X 1.0                    |                     |           |

| LVPECL                             | <b>✓</b>            |           |

| 3.3-V PCML                         | <b>✓</b>            |           |

| LVDS                               | ✓                   |           |

| HyperTransport technology          | ✓                   |           |

| Differential HSTL                  | ✓                   |           |

| Differential SSTL                  |                     |           |

| 3.3-V GTL                          |                     |           |

| 3.3-V GTL+                         | ✓                   |           |

| 1.5-V HSTL Class I                 | ✓                   |           |

| 1.5-V HSTL Class II                |                     |           |

| 1.8-V HSTL Class I                 | ✓                   |           |

| 1.8-V HSTL Class II                |                     |           |

| SSTL-18 Class I                    | <b>✓</b>            |           |

| SSTL-18 Class II                   |                     |           |

| SSTL-2 Class I                     | ✓                   |           |

- 1.8-V HSTL Class I and II

- SSTL-3 Class I and II

- SSTL-2 Class I and II

- SSTL-18 Class I and II

- CTT

Table 2–31 describes the I/O standards supported by Stratix devices.

| Table 2–31. Stratix Supp  | orted I/O Standards |                                                       |                                                      |                                                           |

|---------------------------|---------------------|-------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------|

| I/O Standard              | Туре                | Input Reference<br>Voltage (V <sub>REF</sub> )<br>(V) | Output Supply<br>Voltage (V <sub>CCIO</sub> )<br>(V) | Board<br>Termination<br>Voltage (V <sub>TT</sub> )<br>(V) |

| LVTTL                     | Single-ended        | N/A                                                   | 3.3                                                  | N/A                                                       |

| LVCMOS                    | Single-ended        | N/A                                                   | 3.3                                                  | N/A                                                       |

| 2.5 V                     | Single-ended        | N/A                                                   | 2.5                                                  | N/A                                                       |

| 1.8 V                     | Single-ended        | N/A                                                   | 1.8                                                  | N/A                                                       |

| 1.5 V                     | Single-ended        | N/A                                                   | 1.5                                                  | N/A                                                       |

| 3.3-V PCI                 | Single-ended        | N/A                                                   | 3.3                                                  | N/A                                                       |

| 3.3-V PCI-X 1.0           | Single-ended        | N/A                                                   | 3.3                                                  | N/A                                                       |

| LVDS                      | Differential        | N/A                                                   | 3.3                                                  | N/A                                                       |

| LVPECL                    | Differential        | N/A                                                   | 3.3                                                  | N/A                                                       |

| 3.3-V PCML                | Differential        | N/A                                                   | 3.3                                                  | N/A                                                       |

| HyperTransport            | Differential        | N/A                                                   | 2.5                                                  | N/A                                                       |

| Differential HSTL (1)     | Differential        | 0.75                                                  | 1.5                                                  | 0.75                                                      |

| Differential SSTL (2)     | Differential        | 1.25                                                  | 2.5                                                  | 1.25                                                      |

| GTL                       | Voltage-referenced  | 0.8                                                   | N/A                                                  | 1.20                                                      |

| GTL+                      | Voltage-referenced  | 1.0                                                   | N/A                                                  | 1.5                                                       |

| 1.5-V HSTL Class I and II | Voltage-referenced  | 0.75                                                  | 1.5                                                  | 0.75                                                      |

| 1.8-V HSTL Class I and II | Voltage-referenced  | 0.9                                                   | 1.8                                                  | 0.9                                                       |

| SSTL-18 Class I and II    | Voltage-referenced  | 0.90                                                  | 1.8                                                  | 0.90                                                      |

| SSTL-2 Class I and II     | Voltage-referenced  | 1.25                                                  | 2.5                                                  | 1.25                                                      |

| SSTL-3 Class I and II     | Voltage-referenced  | 1.5                                                   | 3.3                                                  | 1.5                                                       |

| AGP (1× and 2°)           | Voltage-referenced  | 1.32                                                  | 3.3                                                  | N/A                                                       |

| CTT                       | Voltage-referenced  | 1.5                                                   | 3.3                                                  | 1.5                                                       |

#### Notes to Table 2–31:

- (1) This I/O standard is only available on input and output clock pins.

- (2) This I/O standard is only available on output column clock pins.

The Quartus II MegaWizard® Plug-In Manager only allows the implementation of up to 20 receiver or 20 transmitter channels for each fast PLL. These channels operate at up to 840 Mbps. The receiver and transmitter channels are interleaved such that each I/O bank on the left and right side of the device has one receiver channel and one transmitter channel per LAB row. Figure 2–74 shows the fast PLL and channel layout in EP1S10, EP1S20, and EP1S25 devices. Figure 2–75 shows the fast PLL and channel layout in the EP1S30 to EP1S80 devices.

Figure 2-74. Fast PLL & Channel Layout in the EP1S10, EP1S20 or EP1S25 Devices Note (1)

#### Notes to Figure 2-74:

- Wire-bond packages support up to 624 Mbps.

- (2) See Table 2–41 for the number of channels each device supports.

- (3) There is a multiplexer here to select the PLL clock source. If a PLL uses this multiplexer to clock channels outside of its bank quadrant, those clocked channels support up to 840 Mbps for "high" speed channels and 462 Mbps for "low" speed channels, as labeled in the device pin-outs at www.altera.com.

#### **Configuring Stratix FPGAs with JRunner**

JRunner is a software driver that configures Altera FPGAs, including Stratix FPGAs, through the ByteBlaster II or ByteBlasterMV cables in JTAG mode. The programming input file supported is in Raw Binary File (.rbf) format. JRunner also requires a Chain Description File (.cdf) generated by the Quartus II software. JRunner is targeted for embedded JTAG configuration. The source code is developed for the Windows NT operating system (OS), but can be customized to run on other platforms. For more information on the JRunner software driver, see the JRunner Software Driver: An Embedded Solution to the JTAG Configuration White Paper and the source files on the Altera web site (www.altera.com).

#### **Configuration Schemes**

You can load the configuration data for a Stratix device with one of five configuration schemes (see Table 3–5), chosen on the basis of the target application. You can use a configuration device, intelligent controller, or the JTAG port to configure a Stratix device. A configuration device can automatically configure a Stratix device at system power-up.

Multiple Stratix devices can be configured in any of five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.

| Table 3–5. Data Sources for Configuration |                                                                                                                     |  |  |  |  |  |  |  |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Configuration Scheme                      | Data Source                                                                                                         |  |  |  |  |  |  |  |

| Configuration device                      | Enhanced or EPC2 configuration device                                                                               |  |  |  |  |  |  |  |

| Passive serial (PS)                       | MasterBlaster, ByteBlasterMV, or ByteBlaster II download cable or serial data source                                |  |  |  |  |  |  |  |

| Passive parallel asynchronous (PPA)       | Parallel data source                                                                                                |  |  |  |  |  |  |  |

| Fast passive parallel                     | Parallel data source                                                                                                |  |  |  |  |  |  |  |

| JTAG                                      | MasterBlaster, ByteBlasterMV, or ByteBlaster II download cable, a microprocessor with a Jam or JBC file, or JRunner |  |  |  |  |  |  |  |

#### **Partial Reconfiguration**

The enhanced PLLs within the Stratix device family support partial reconfiguration of their multiply, divide, and time delay settings without reconfiguring the entire device. You can use either serial data from the logic array or regular I/O pins to program the PLL's counter settings in a serial chain. This option provides considerable flexibility for frequency

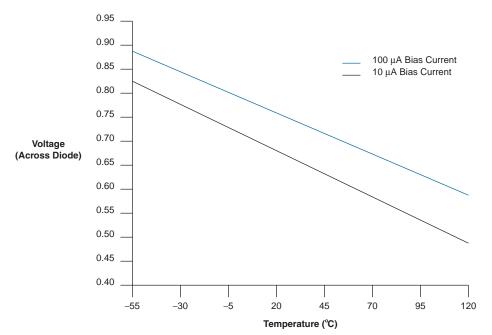

The temperature-sensing diode works for the entire operating range shown in Figure 3–6.

Figure 3-6. Temperature vs. Temperature-Sensing Diode Voltage

| Table 4–20. SSTL-2 Class I Specifications |                             |                                |                         |           |                         |      |  |  |  |  |

|-------------------------------------------|-----------------------------|--------------------------------|-------------------------|-----------|-------------------------|------|--|--|--|--|

| Symbol                                    | Parameter Conditions        |                                | Minimum                 | Typical   | Maximum                 | Unit |  |  |  |  |

| $V_{\text{CCIO}}$                         | Output supply voltage       |                                | 2.375                   | 2.5       | 2.625                   | ٧    |  |  |  |  |

| $V_{TT}$                                  | Termination voltage         |                                | V <sub>REF</sub> - 0.04 | $V_{REF}$ | V <sub>REF</sub> + 0.04 | V    |  |  |  |  |

| $V_{REF}$                                 | Reference voltage           |                                | 1.15                    | 1.25      | 1.35                    | ٧    |  |  |  |  |

| V <sub>IH(DC)</sub>                       | High-level DC input voltage |                                | V <sub>REF</sub> + 0.18 |           | 3.0                     | V    |  |  |  |  |

| V <sub>IL(DC)</sub>                       | Low-level DC input voltage  |                                | -0.3                    |           | V <sub>REF</sub> – 0.18 | ٧    |  |  |  |  |

| V <sub>IH(AC)</sub>                       | High-level AC input voltage |                                | V <sub>REF</sub> + 0.35 |           |                         | V    |  |  |  |  |

| V <sub>IL(AC)</sub>                       | Low-level AC input voltage  |                                |                         |           | V <sub>REF</sub> - 0.35 | V    |  |  |  |  |

| V <sub>OH</sub>                           | High-level output voltage   | $I_{OH} = -8.1 \text{ mA}$ (3) | V <sub>TT</sub> + 0.57  |           |                         | V    |  |  |  |  |

| V <sub>OL</sub>                           | Low-level output voltage    | I <sub>OL</sub> = 8.1 mA (3)   |                         |           | V <sub>TT</sub> – 0.57  | ٧    |  |  |  |  |

| Table 4–21          | . SSTL-2 Class II Specification | ons                             |                         |           |                         |      |

|---------------------|---------------------------------|---------------------------------|-------------------------|-----------|-------------------------|------|

| Symbol              | Parameter                       | Conditions                      | Minimum                 | Typical   | Maximum                 | Unit |

| V <sub>CCIO</sub>   | Output supply voltage           |                                 | 2.375                   | 2.5       | 2.625                   | ٧    |

| V <sub>TT</sub>     | Termination voltage             |                                 | V <sub>REF</sub> - 0.04 | $V_{REF}$ | V <sub>REF</sub> + 0.04 | V    |

| V <sub>REF</sub>    | Reference voltage               |                                 | 1.15                    | 1.25      | 1.35                    | V    |

| V <sub>IH(DC)</sub> | High-level DC input voltage     |                                 | V <sub>REF</sub> + 0.18 |           | V <sub>CCIO</sub> + 0.3 | V    |

| V <sub>IL(DC)</sub> | Low-level DC input voltage      |                                 | -0.3                    |           | V <sub>REF</sub> – 0.18 | V    |

| V <sub>IH(AC)</sub> | High-level AC input voltage     |                                 | V <sub>REF</sub> + 0.35 |           |                         | V    |

| V <sub>IL(AC)</sub> | Low-level AC input voltage      |                                 |                         |           | V <sub>REF</sub> – 0.35 | V    |

| V <sub>OH</sub>     | High-level output voltage       | $I_{OH} = -16.4 \text{ mA}$ (3) | V <sub>TT</sub> + 0.76  |           |                         | V    |

| V <sub>OL</sub>     | Low-level output voltage        | I <sub>OL</sub> = 16.4 mA (3)   |                         |           | V <sub>TT</sub> – 0.76  | V    |

| Table 4-22          | Table 4–22. SSTL-3 Class I Specifications (Part 1 of 2) |            |                         |           |                         |      |  |  |  |  |  |

|---------------------|---------------------------------------------------------|------------|-------------------------|-----------|-------------------------|------|--|--|--|--|--|

| Symbol              | Parameter                                               | Conditions | Minimum                 | Typical   | Maximum                 | Unit |  |  |  |  |  |

| V <sub>CCIO</sub>   | Output supply voltage                                   |            | 3.0                     | 3.3       | 3.6                     | V    |  |  |  |  |  |

| V <sub>TT</sub>     | Termination voltage                                     |            | V <sub>REF</sub> - 0.05 | $V_{REF}$ | V <sub>REF</sub> + 0.05 | V    |  |  |  |  |  |

| V <sub>REF</sub>    | Reference voltage                                       |            | 1.3                     | 1.5       | 1.7                     | V    |  |  |  |  |  |

| V <sub>IH(DC)</sub> | High-level DC input voltage                             |            | V <sub>REF</sub> + 0.2  |           | V <sub>CCIO</sub> + 0.3 | V    |  |  |  |  |  |

| V <sub>IL(DC)</sub> | Low-level DC input voltage                              |            | -0.3                    |           | V <sub>REF</sub> - 0.2  | V    |  |  |  |  |  |

| V <sub>IH(AC)</sub> | High-level AC input voltage                             |            | V <sub>REF</sub> + 0.4  |           |                         | V    |  |  |  |  |  |

| Table 4-47. DSP BI           | Table 4–47. DSP Block Internal Timing Microparameters (Part 2 of 2) |       |       |       |       |       |       |        |      |  |

|------------------------------|---------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--------|------|--|

| Symbol                       | -                                                                   | -5    |       | -6    |       | -7    |       | -8     |      |  |

|                              | Min                                                                 | Max   | Min   | Max   | Min   | Max   | Min   | Max    | Unit |  |

| t <sub>PIPE2OUTREG2ADD</sub> |                                                                     | 2,002 |       | 2,203 |       | 2,533 |       | 2,980  | ps   |  |

| t <sub>PIPE2OUTREG4ADD</sub> |                                                                     | 2,899 |       | 3,189 |       | 3,667 |       | 4,314  | ps   |  |

| t <sub>PD9</sub>             |                                                                     | 3,709 |       | 4,081 |       | 4,692 |       | 5,520  | ps   |  |

| t <sub>PD18</sub>            |                                                                     | 4,795 |       | 5,275 |       | 6,065 |       | 7,135  | ps   |  |

| t <sub>PD36</sub>            |                                                                     | 7,495 |       | 8,245 |       | 9,481 |       | 11,154 | ps   |  |

| t <sub>CLR</sub>             | 450                                                                 |       | 500   |       | 575   |       | 676   |        | ps   |  |

| t <sub>CLKHL</sub>           | 1,350                                                               |       | 1,500 |       | 1,724 |       | 2,029 |        | ps   |  |

| Table 4–48. M512         | Block Intern | al Timing | Micropar | ameters |       |       |       |       |      |

|--------------------------|--------------|-----------|----------|---------|-------|-------|-------|-------|------|

| Ourseh e l               | -            | -5        |          | 6       | -7    |       | -     | 8     |      |

| Symbol                   | Min          | Max       | Min      | Max     | Min   | Max   | Min   | Max   | Unit |

| t <sub>M512RC</sub>      |              | 3,340     |          | 3,816   |       | 4,387 |       | 5,162 | ps   |

| t <sub>M512WC</sub>      |              | 3,138     |          | 3,590   |       | 4,128 |       | 4,860 | ps   |

| t <sub>M512WERESU</sub>  | 110          |           | 123      |         | 141   |       | 166   |       | ps   |

| t <sub>M512WEREH</sub>   | 34           |           | 38       |         | 43    |       | 51    |       | ps   |

| t <sub>M512CLKENSU</sub> | 215          |           | 215      |         | 247   |       | 290   |       | ps   |

| t <sub>M512CLKENH</sub>  | -70          |           | -70      |         | -81   |       | -95   |       | ps   |

| t <sub>M512DATASU</sub>  | 110          |           | 123      |         | 141   |       | 166   |       | ps   |

| t <sub>M512DATAH</sub>   | 34           |           | 38       |         | 43    |       | 51    |       | ps   |

| t <sub>M512WADDRSU</sub> | 110          |           | 123      |         | 141   |       | 166   |       | ps   |

| t <sub>M512WADDRH</sub>  | 34           |           | 38       |         | 43    |       | 51    |       | ps   |

| t <sub>M512RADDRSU</sub> | 110          |           | 123      |         | 141   |       | 166   |       | ps   |

| t <sub>M512RADDRH</sub>  | 34           |           | 38       |         | 43    |       | 51    |       | ps   |

| t <sub>M512DATACO1</sub> |              | 424       |          | 472     |       | 541   |       | 637   | ps   |

| t <sub>M512DATACO2</sub> |              | 3,366     |          | 3,846   |       | 4,421 |       | 5,203 | ps   |

| t <sub>M512CLKHL</sub>   | 1,000        |           | 1,111    |         | 1,190 |       | 1,400 |       | ps   |

| t <sub>M512CLR</sub>     | 170          |           | 189      |         | 217   |       | 255   |       | ps   |

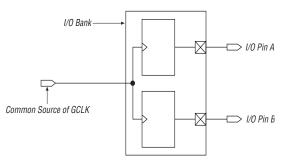

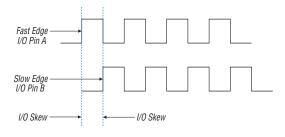

#### Definition of I/O Skew

I/O skew is defined as the absolute value of the worst-case difference in clock-to-out times ( $t_{\rm CO}$ ) between any two output registers fed by a common clock source.

I/O bank skew is made up of the following components:

- Clock network skews: This is the difference between the arrival times of the clock at the clock input port of the two IOE registers.

- Package skews: This is the package trace length differences between (I/O pad A to I/O pin A) and (I/O pad B to I/O pin B).

Figure 4–5 shows an example of two IOE registers located in the same bank, being fed by a common clock source. The clock can come from an input pin or from a PLL output.

Figure 4-5. I/O Skew within an I/O Bank

| Paramo                      | ator  | -5 Spee | ed Grade | -6 Spee | ed Grade | -7 Spee | d Grade | -8 Spee | ed Grade | Unit |

|-----------------------------|-------|---------|----------|---------|----------|---------|---------|---------|----------|------|

| Falalli                     | 5161  | Min     | Max      | Min     | Max      | Min     | Max     | Min     | Max      | Unit |

| 1.5-V LVTTL                 | 2 mA  |         | 5,460    |         | 5,733    |         | 5,733   |         | 5,733    | ps   |

|                             | 4 mA  |         | 2,690    |         | 2,824    |         | 2,824   |         | 2,824    | ps   |

|                             | 8 mA  |         | 1,398    |         | 1,468    |         | 1,468   |         | 1,468    | ps   |

| GTL+                        |       |         | 6        |         | 6        |         | 6       |         | 6        | ps   |

| CTT                         |       |         | 845      |         | 887      |         | 887     |         | 887      | ps   |

| SSTL-3 Class                |       |         | 638      |         | 670      |         | 670     |         | 670      | ps   |

| SSTL-3 Class                | II    |         | 144      |         | 151      |         | 151     |         | 151      | ps   |

| SSTL-2 Class                | I     |         | 604      |         | 634      |         | 634     |         | 634      | ps   |

| SSTL-2 Class                | II    |         | 211      |         | 221      |         | 221     |         | 221      | ps   |

| SSTL-18 Class               | s I   |         | 955      |         | 1,002    |         | 1,002   |         | 1,002    | ps   |

| 1.5-V HSTL CI               | ass I |         | 733      |         | 769      |         | 769     |         | 769      | ps   |

| 1.8-V HSTL CI               | ass I |         | 372      |         | 390      |         | 390     |         | 390      | ps   |

| LVDS                        |       |         | -196     |         | -206     |         | -206    |         | -206     | ps   |

| LVPECL                      |       |         | -148     |         | -156     |         | -156    |         | -156     | ps   |

| PCML                        |       |         | -147     |         | -155     |         | -155    |         | -155     | ps   |

| HyperTranspor<br>technology | t     |         | -93      |         | -98      |         | -98     |         | -98      | ps   |

Note to Table 4–103 through 4–106:

<sup>(1)</sup> These parameters are only available on row I/O pins.

| Table 4–107. Stratix I/O Standard Output Delay Adders for Slow Slew Rate on Column Pins (Part 1 of 2) |       |         |         |         |         |         |         |         |         | of 2) |

|-------------------------------------------------------------------------------------------------------|-------|---------|---------|---------|---------|---------|---------|---------|---------|-------|

|                                                                                                       |       | -5 Spee | d Grade | -6 Spee | d Grade | -7 Spee | d Grade | -8 Spee | d Grade | llmit |

| Parame                                                                                                | eler  | Min     | Max     | Min     | Max     | Min     | Max     | Min Max |         | Unit  |

| LVCMOS                                                                                                | 2 mA  |         | 1,822   |         | 1,913   |         | 1,913   |         | 1,913   | ps    |

|                                                                                                       | 4 mA  |         | 684     |         | 718     |         | 718     |         | 718     | ps    |

|                                                                                                       | 8 mA  |         | 233     |         | 245     |         | 245     |         | 245     | ps    |

|                                                                                                       | 12 mA |         | 1       |         | 1       |         | 1       |         | 1       | ps    |

|                                                                                                       | 24 mA |         | -608    |         | -638    |         | -638    |         | -638    | ps    |

Table 4–120. Stratix Maximum Output Clock Rate for PLL[5, 6, 11, 12] Pins in Flip-Chip Packages (Part 2 of 2)

| I/O Standard                        | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------------|-------------------|-------------------|-------------------|-------------------|------|

| SSTL-2 Class II (3)                 | 200               | 200               | 167               | 167               | MHz  |

| SSTL-2 Class II (4)                 | 200               | 200               | 167               | 167               | MHz  |

| SSTL-2 Class II (5)                 | 150               | 134               | 134               | 134               | MHz  |

| SSTL-18 Class I                     | 150               | 133               | 133               | 133               | MHz  |

| SSTL-18 Class II                    | 150               | 133               | 133               | 133               | MHz  |

| 1.5-V HSTL Class I                  | 250               | 225               | 200               | 200               | MHz  |

| 1.5-V HSTL Class II                 | 225               | 200               | 200               | 200               | MHz  |

| 1.8-V HSTL Class I                  | 250               | 225               | 200               | 200               | MHz  |

| 1.8-V HSTL Class II                 | 225               | 200               | 200               | 200               | MHz  |

| 3.3-V PCI                           | 350               | 300               | 250               | 250               | MHz  |

| 3.3-V PCI-X 1.0                     | 350               | 300               | 250               | 250               | MHz  |

| Compact PCI                         | 350               | 300               | 250               | 250               | MHz  |

| AGP 1×                              | 350               | 300               | 250               | 250               | MHz  |

| AGP 2×                              | 350               | 300               | 250               | 250               | MHz  |

| CTT                                 | 200               | 200               | 200               | 200               | MHz  |

| Differential 1.5-V HSTL<br>C1       | 225               | 200               | 200               | 200               | MHz  |

| Differential 1.8-V HSTL<br>Class I  | 250               | 225               | 200               | 200               | MHz  |

| Differential 1.8-V HSTL<br>Class II | 225               | 200               | 200               | 200               | MHz  |

| Differential SSTL-2 (6)             | 200               | 200               | 167               | 167               | MHz  |

| LVPECL (2)                          | 500               | 500               | 500               | 500               | MHz  |

| PCML (2)                            | 350               | 350               | 350               | 350               | MHz  |

| LVDS (2)                            | 500               | 500               | 500               | 500               | MHz  |

| HyperTransport technology (2)       | 350               | 350               | 350               | 350               | MHz  |

Table 4–122. Stratix Maximum Output Clock Rate for PLL[5, 6, 11, 12] Pins in Wire-Bond Packages (Part 1 of 2)

| I/O Standard                        | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------------|-------------------|-------------------|-------------------|------|

| LVTTL                               | 175               | 150               | 150               | MHz  |

| 2.5 V                               | 175               | 150               | 150               | MHz  |

| 1.8 V                               | 175               | 150               | 150               | MHz  |

| 1.5 V                               | 175               | 150               | 150               | MHz  |

| LVCMOS                              | 175               | 150               | 150               | MHz  |

| GTL                                 | 125               | 100               | 100               | MHz  |

| GTL+                                | 125               | 100               | 100               | MHz  |

| SSTL-3 Class I                      | 110               | 90                | 90                | MHz  |

| SSTL-3 Class II                     | 133               | 125               | 125               | MHz  |

| SSTL-2 Class I                      | 166               | 133               | 133               | MHz  |

| SSTL-2 Class II                     | 133               | 100               | 100               | MHz  |

| SSTL-18 Class I                     | 110               | 100               | 100               | MHz  |

| SSTL-18 Class II                    | 110               | 100               | 100               | MHz  |

| 1.5-V HSTL Class I                  | 167               | 167               | 167               | MHz  |

| 1.5-V HSTL Class II                 | 167               | 133               | 133               | MHz  |

| 1.8-V HSTL Class I                  | 167               | 167               | 167               | MHz  |

| 1.8-V HSTL Class II                 | 167               | 133               | 133               | MHz  |

| 3.3-V PCI                           | 167               | 167               | 167               | MHz  |

| 3.3-V PCI-X 1.0                     | 167               | 133               | 133               | MHz  |

| Compact PCI                         | 175               | 150               | 150               | MHz  |

| AGP 1×                              | 175               | 150               | 150               | MHz  |

| AGP 2×                              | 175               | 150               | 150               | MHz  |

| СТТ                                 | 125               | 100               | 100               | MHz  |

| Differential 1.5-V HSTL<br>C1       | 167               | 133               | 133               | MHz  |

| Differential 1.8-V HSTL<br>Class I  | 167               | 167               | 167               | MHz  |

| Differential 1.8-V HSTL<br>Class II | 167               | 133               | 133               | MHz  |

| Differential SSTL-2 (1)             | 110               | 100               | 100               | MHz  |

| LVPECL (2)                          | 311               | 275               | 275               | MHz  |

| PCML (2)                            | 250               | 200               | 200               | MHz  |

| Differential HSTL Specifications 4–15<br>DSP        | Parameters 4–39<br>Row Pin                         |

|-----------------------------------------------------|----------------------------------------------------|

| Block Diagram                                       | Fast Regional Clock External I/O Timing            |

| Configuration                                       | Parameters 4–40                                    |

| for 18 x 18-Bit 2–55                                | Global Clock External I/O Timing                   |

| for 9 x 9-Bit 2–56                                  | Parameters 4–41                                    |

| Block Interconnect Interface 2–71                   | Regional Clock External I/O Timing                 |

| Block Interface 2–70                                | Parameters 4–41                                    |

| Block Signal Sources & Destinations 2–73            | EP1S25 Devices                                     |

| Blocks                                              | Column Pin                                         |

| Arranged in Columns 2–53                            | Fast Regional Clock External I/O Timing            |

| in Stratix Devices 2–54                             | Parameters 4–42                                    |

| Input Register Modes 2-60                           | Global Clock External I/O Timing                   |

| Input Registers 2–58                                | Parameters 4–43                                    |

| Multiplier                                          | Regional Clock External I/O Timing                 |

| 2–60                                                | Parameters 4–42                                    |

| Block 2–57                                          | Row Pin                                            |

| Signed Representation 2-60                          | Fast Regional Clock External I/O Timing            |

| Sub-Block 2–57                                      | Parameters 4–43                                    |

| Sub-Blocks Using Input Shift Register               | Global Clock External I/O Timing                   |

| Connections 2–59                                    | Parameters 4–44                                    |

| Pipeline/Post Multiply Register 2–61                | Regional Clock External I/O Timing                 |

|                                                     | Parameters 4–44                                    |

| E                                                   | EP1S30 Devices                                     |

| <b>L</b>                                            | Column Pin                                         |

| EP1S10 Devices                                      | Fast Regional Clock External I/O Timing            |

| Column Pin                                          | Parameters 4–45                                    |

| Fast Regional Clock External I/O Timing             | Global Clock External I/O Timing                   |

| Parameters 4–36                                     | Parameters 4–45                                    |

| Global Clock External I/O Timing<br>Parameters 4–37 | Regional Clock External I/O Timing Parameters 4–45 |

| Regional Clock External I/O Timing                  | Row Pin                                            |

| Parameters 4–36                                     | Fast Regional Clock External I/O Timing            |

| Row Pin                                             | Parameters 4–46                                    |

| Fast Regional Clock External I/O Timing             | Global Clock External I/O Timing                   |

| Parameters 4–37                                     | Parameters 4–47                                    |

| Global Clock External I/O Timing                    | Regional Clock External I/O Timing                 |

| Parameters 4–38                                     | Parameters 4–47                                    |

| Regional Clock External I/O Timing                  | EP1S40 Devices                                     |

| Parameters 4–38                                     | Column Pin                                         |

| EP1S20 Devices                                      | Fast Regional Clock External I/O Timing            |

| Column Pin                                          | Parameters 4–48                                    |

| Fast Regional Clock External I/O Timing             | Global Clock External I/O Timing                   |

| Parameters 4–39                                     | Parameters 4–49                                    |

| Global Clock External I/O Timing                    | Regional Clock External I/O Timing                 |

| Parameters 4–40                                     | Parameters 4–48                                    |

| Regional Clock External I/O Timing                  | Row Pin                                            |

Altera Corporation Index-3